一种emmc芯片随机写入速率优化实现方法

技术领域:

:1.本发明属于数据存储

技术领域:

:,涉及一种emmc芯片随机写入速率优化实现方法。

背景技术:

::2.为了满足平板、手机等电子器件移动性的需求,在轻薄、低功耗的前置要求下,emmc(embeddedmultimediacard,嵌入式多媒体控制器)诞生了。所以emmc接口是用iopin来定义的,这样接口简单,功耗低;另外emmc对于苹果ipad、安卓平板电脑、手机的作用也是巨大的,平板和手机都比较小,所以emmc是把控制器和nand颗粒封装在一个package里面,这也造成emmc不能放很多nand颗粒,容量比较低。3.总结emmc特点就是功耗低,容量小,随机读写性能相对较差;4.作为芯片的其中一种数据交互方式,随机读写主要是相对于顺序读写提出来的,从字面意义上来理解,如果说顺序读写是在读写过程之中遵循先后顺序,每次存取数据请求的地址都是连续的。那么随机读写就是不遵循固定的先后顺序,在进行读写操作的时候,能够任意切换到某个位置上对数据进行读写操作。5.以顺序写入的方式做类比来说明随机写入的问题。简单地讲,如果顺序写入的数据是按照从位置1、2、3、4这样顺序的一个个写下去的,那么,相连的数据之间地址上也会是连续的,并且emmc的逻辑块地址directeba与物理块地址phyeba是相等,具备较快的数据传输速率。然而随机写入的方式,数据写入的位置是不固定的。例如在写完第一个数据之后,下一个数据的位置可能是在第一个数据地址再间隔一段的位置,而再下一个数据的写入位置又可能会出现在前几个数据之间,造成的结果就是数据之间是十分割裂的,其directeba与phyeba之间并不相等。也因为每次写入的地址跳跃等问题,数据写入速率十分缓慢,这也是随机写入的缺点,更加耗时。技术实现要素:6.为解决上述问题,本发明提出了一种emmc芯片随机写入速率优化实现方法,包括以下步骤:7.s1,对emmc芯片进行数据写入;8.s2,对写入方式进行判断;9.s3,如是随机写入,则写入额外配置区域;10.如是顺序写入,则写入用户区域;11.s4,根据映射关系表在数据前附加标签;12.s5,合并数据写入用户区域。13.优选地,所述对写入方式进行判断具体为当写入的数据扇区的数量等于或超过n时,判定为顺序写入;当写入的数据扇区的数量小于n时,判定为随机写入,其中n为32。14.优选地,所述映射关系表中每4个字节的逻辑地址对应4个字节的物理地址。15.优选地,所述emmc芯片被分为m个区域,每个区域中用1bit数据表示顺序写入和随机写入。16.优选地,所述每个区域中用1bit数据为0时表示顺序写入,为1时表示随机写入。17.优选地,所述标签的大小为4kb。18.优选地,所述标签的组成依次为逻辑地址、物理地址、数据扇区数量、标签数量、标签标记和总检验位。19.优选地,所述额外配置区域的构成为依次设置的标签和随机数据,以此类推重复。20.本发明有益效果至少包括:21.1)为了能提升emmc芯片在随机写入数据时的速率,本发明通过将原来相对割裂的随机数据,组合成顺序连续的数据进行写入,使得传输速率本来比较慢的随机写入方式能够像顺序写入一样具备比较高的传输速率;22.2)随机数据之间相对位置关系,通过附加tag的方式,提供了从logicaleba到phyeba的映射关系来保证最终写入到存储中的数据之间,不会因此出现错位关系;23.3)针对顺序写入占据大多数的数据传输方式,这种将随机写入统合成顺序写入方式的做法能够有效地提高随机数据写入的速率。附图说明24.图1为本发明实施例的emmc芯片随机写入速率优化实现方法的emmc的数据排列示意图;25.图2为本发明实施例的emmc芯片随机写入速率优化实现方法的步骤流程图;26.图3为本发明实施例的emmc芯片随机写入速率优化实现方法的顺序写入和随机写入示意图;27.图4为本发明实施例的emmc芯片随机写入速率优化实现方法的映射关系表示意图;28.图5为本发明实施例的emmc芯片随机写入速率优化实现方法的标签构成示意图;29.图6为本发明实施例的emmc芯片随机写入速率优化实现方法的随机写入对比图。具体实施方式30.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。31.相反,本发明涵盖任何由权利要求定义的在本发明的精髓和范围上做的替代、修改、等效方法以及方案。进一步,为了使公众对本发明有更好的了解,在下文对本发明的细节描述中,详尽描述了一些特定的细节部分。对本领域技术人员来说没有这些细节部分的描述也可以完全理解本发明。32.参见图1,从emmc数据排列可以看出,emmc中存在正常的用户区域userarea以及固定的额外配置fixedop(overprovisioning),一般而言,用户正常查看数据的位置是位于userarea处。33.而本发明优化的思路则是,将需要进行随机写入的数据通过顺序写入的方式写到op区域进行顺序化的组合到一起,最后让硬件在闲置情况下将这一部分数据合并到用户区域。34.参见图2,为本发明的方法流程图,包括:s1,对emmc芯片进行数据写入;35.s2,对写入方式进行判断;36.s3,如是随机写入,则写入额外配置区域;37.如是顺序写入,则写入用户区域;38.s4,根据映射关系表在数据前附加标签;39.s5,合并数据写入用户区域。40.参见图3,以通道0所连接的emmc0举例说明:设置的顺序写入和随机写入的判断条件是,当需要写入的sector(数据扇区),大小为512个字节,sector数量等于或超过32个时,认为写入的数据是顺序的,当sector数量小于32个时,认为数据是随机写入的,用来模拟顺序写入和随机写入的情况。lba英文全称为logicblockaddress,与directeba同样是逻辑块地址,但是二者之间是有区别的。以图1为例,数据写入过程中,为了使数据写入能够均衡,使用多个通道写入不同的emmc中,因此写入满一定块大小以后需要切换到不同channel(通道)进行。lba针对是多通道下的数据的逻辑块地址,而directeba则是具体针对某一个通道,例如channel0中,数据写入的逻辑块首地址。41.可以看到,图3中第一次写入位置为lba为32的情况下,64k的sector数据大小对应的sector计数数量为128,因为单个sector的大小为512个字节,这里的64k其实指代的是总的sector大小,1k的数据相当于两个sector计数,而我们用来判断是否有随机数据的依据,是sector的计数数量,也就是sectorcount是否大于32,所以这里的sector数量为128。另外,这里选择64k大小的sector扇区大小只是为了举例说明,所设定的大于随机与顺序写入阈值关系的值,所以是顺序写入,直接将数据写入到userarea的对应lba位置就行,这是因为顺序写入的时候directeba和phyeba是相同的,而第二次,lba为34,但是因为sector数量为4,所以是随机写入,这种情况下,我们是将数据写入到op区域,即额外配置区域。需要注意的是,因为lba是34,针对同一个directeba而言,还缺少前面的32和33的数据以及后面的一部分数据,所以需要从用户区域userarea位置将剩下的数据拷贝到op区域,这样保证了op区域的数据才是最新的有效数据。第三次的写入与第二次类似,这次则是将数据追加在第二次写入数据的后面,保证了随机数据在op区域内都是顺序的。42.参见图4为映射关系表mappingtable中directeba与phyeba的映射关系示意图,要如何保证这些被组合成顺序方式的随机数据在回写到userarea区域的顺序是正确的呢?故关于directeba与phyeba之间是存在一张总的映射关系表mappingtable来提供位置关系的。针对顺序写入,directeba与phyeba之间是相等的,而对于随机写入,二者则并不相等。43.可以看到,关于地址的表示是需要4个bytes的,为了缩减映射表的大小。我们将整个emmc分为了32个区域region(这个容量依赖于所选择的emmc本身的容量而变化,以一个具备4个emmc的256g的盘为例,单个emmc的容量为64g,所以切分为32个region以后每个region大小为2g),每个区域仅使用bit0来表示该区域是顺序写入的,bit1表示该区域是存在随机写入的,因此,对于那些顺序写入占大多数,随机写入表示少的情况,对于顺序写入的映射关系,利用顺序写入的directeba和phyeba之间相等的特性,我们仅需用1bit的数据0替代原来的4bytes,而随机写入的映射关系,则是通过bit=1的情况表明是随机写入以后,从而再去找mappingtable(mappingtable的组成就是像上述图4所描述的那样,每4个bytes的emmc逻辑地址对应4个bytes的emmc物理地址,完整的映射表就是由这样的一系列映射关系组所组成的。保证了我们在写入数据的时候,通过emmc逻辑地址,依靠映射表将数据写入正确的物理地址位置。)这张总表,通过这种方式可以有效提高查表的效率。44.接下来,最为关键。就是需要给写在op区域的随机数据提供必要的directeba信息了,如前述,对于随机写入而言,它的directeba与phyeba之间并不相等,所以需要有一个映射关系表,只有添加了这一部分信息才能保证掉电情况下也不会丢失随机写入数据的关于directeba与phyeba的映射关系,从而保证随机数据能够正确回写到emmc原来的逻辑块位置。45.参见图5为随机写入数据的tag及其构成。其中纵向额外配置区的构成,这4部分内容其实可以看成是两个部分,因为其系列构成都是一个大小为4kb的randomwritetag加上一组随机数据,所以后面和一部分其实和前面是一样的概念,只不过后者tag的具体内容与随机数据与前半部分并不一致而已。46.然后,关于randomwritetag,他的构成内容就是横向标签所展示出的这一部分。大小一共是4kb。构成上依次为:1)directeba就是emmc的逻辑地址、2)phyeba则是emmc的物理地址、3)sectorcount如上面提示的,是对写入的sata命令中sector计数的数量,也是证明后续跟随发送的数据包含随机数据(这个数量会大于32的阈值)、4)tagcount是为了保证所顺序串接的随机数据之间的前后关系不会紊乱,因为是将随机数据串接成顺序的形式进行写入,后面的数据理应是追加而不是覆盖前方的数据,所以tag的不同也能看出随机数据的先后关系、5)tagflag以及checksum这些是为了保证写入时候数据的正确性,因为任何数据写入的时候,各式各样的干扰都可能会造成写入数据出错的问题,数据错位或者是1写成0,0写成1,这些都会导致数据写入出错,检验和checksum便是为了能够在写入数据出错的时候提供校验而附加的校验位。47.然后就是dataofrandomcmd,这部分便是需要顺序化串接写入的随机数据。48.参见图5中的oparea,需要在每次写入随机数据之前,给写入的数据添加一个tag,tag记录了关于随机写入的映射信息。这样一来就能够保证,虽然将需要随机写入的信息通过组合到一起顺序地写入,但是最终存储到userarea处的数据内容能够保证不会出现错位的情况。而且需要注意的是,在写之前,是需要对op区域进行trim(擦除)的,优化之后的随机写入方式参见图6。49.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。当前第1页12当前第1页12

技术领域:

:1.本发明属于数据存储

技术领域:

:,涉及一种emmc芯片随机写入速率优化实现方法。

背景技术:

::2.为了满足平板、手机等电子器件移动性的需求,在轻薄、低功耗的前置要求下,emmc(embeddedmultimediacard,嵌入式多媒体控制器)诞生了。所以emmc接口是用iopin来定义的,这样接口简单,功耗低;另外emmc对于苹果ipad、安卓平板电脑、手机的作用也是巨大的,平板和手机都比较小,所以emmc是把控制器和nand颗粒封装在一个package里面,这也造成emmc不能放很多nand颗粒,容量比较低。3.总结emmc特点就是功耗低,容量小,随机读写性能相对较差;4.作为芯片的其中一种数据交互方式,随机读写主要是相对于顺序读写提出来的,从字面意义上来理解,如果说顺序读写是在读写过程之中遵循先后顺序,每次存取数据请求的地址都是连续的。那么随机读写就是不遵循固定的先后顺序,在进行读写操作的时候,能够任意切换到某个位置上对数据进行读写操作。5.以顺序写入的方式做类比来说明随机写入的问题。简单地讲,如果顺序写入的数据是按照从位置1、2、3、4这样顺序的一个个写下去的,那么,相连的数据之间地址上也会是连续的,并且emmc的逻辑块地址directeba与物理块地址phyeba是相等,具备较快的数据传输速率。然而随机写入的方式,数据写入的位置是不固定的。例如在写完第一个数据之后,下一个数据的位置可能是在第一个数据地址再间隔一段的位置,而再下一个数据的写入位置又可能会出现在前几个数据之间,造成的结果就是数据之间是十分割裂的,其directeba与phyeba之间并不相等。也因为每次写入的地址跳跃等问题,数据写入速率十分缓慢,这也是随机写入的缺点,更加耗时。技术实现要素:6.为解决上述问题,本发明提出了一种emmc芯片随机写入速率优化实现方法,包括以下步骤:7.s1,对emmc芯片进行数据写入;8.s2,对写入方式进行判断;9.s3,如是随机写入,则写入额外配置区域;10.如是顺序写入,则写入用户区域;11.s4,根据映射关系表在数据前附加标签;12.s5,合并数据写入用户区域。13.优选地,所述对写入方式进行判断具体为当写入的数据扇区的数量等于或超过n时,判定为顺序写入;当写入的数据扇区的数量小于n时,判定为随机写入,其中n为32。14.优选地,所述映射关系表中每4个字节的逻辑地址对应4个字节的物理地址。15.优选地,所述emmc芯片被分为m个区域,每个区域中用1bit数据表示顺序写入和随机写入。16.优选地,所述每个区域中用1bit数据为0时表示顺序写入,为1时表示随机写入。17.优选地,所述标签的大小为4kb。18.优选地,所述标签的组成依次为逻辑地址、物理地址、数据扇区数量、标签数量、标签标记和总检验位。19.优选地,所述额外配置区域的构成为依次设置的标签和随机数据,以此类推重复。20.本发明有益效果至少包括:21.1)为了能提升emmc芯片在随机写入数据时的速率,本发明通过将原来相对割裂的随机数据,组合成顺序连续的数据进行写入,使得传输速率本来比较慢的随机写入方式能够像顺序写入一样具备比较高的传输速率;22.2)随机数据之间相对位置关系,通过附加tag的方式,提供了从logicaleba到phyeba的映射关系来保证最终写入到存储中的数据之间,不会因此出现错位关系;23.3)针对顺序写入占据大多数的数据传输方式,这种将随机写入统合成顺序写入方式的做法能够有效地提高随机数据写入的速率。附图说明24.图1为本发明实施例的emmc芯片随机写入速率优化实现方法的emmc的数据排列示意图;25.图2为本发明实施例的emmc芯片随机写入速率优化实现方法的步骤流程图;26.图3为本发明实施例的emmc芯片随机写入速率优化实现方法的顺序写入和随机写入示意图;27.图4为本发明实施例的emmc芯片随机写入速率优化实现方法的映射关系表示意图;28.图5为本发明实施例的emmc芯片随机写入速率优化实现方法的标签构成示意图;29.图6为本发明实施例的emmc芯片随机写入速率优化实现方法的随机写入对比图。具体实施方式30.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。31.相反,本发明涵盖任何由权利要求定义的在本发明的精髓和范围上做的替代、修改、等效方法以及方案。进一步,为了使公众对本发明有更好的了解,在下文对本发明的细节描述中,详尽描述了一些特定的细节部分。对本领域技术人员来说没有这些细节部分的描述也可以完全理解本发明。32.参见图1,从emmc数据排列可以看出,emmc中存在正常的用户区域userarea以及固定的额外配置fixedop(overprovisioning),一般而言,用户正常查看数据的位置是位于userarea处。33.而本发明优化的思路则是,将需要进行随机写入的数据通过顺序写入的方式写到op区域进行顺序化的组合到一起,最后让硬件在闲置情况下将这一部分数据合并到用户区域。34.参见图2,为本发明的方法流程图,包括:s1,对emmc芯片进行数据写入;35.s2,对写入方式进行判断;36.s3,如是随机写入,则写入额外配置区域;37.如是顺序写入,则写入用户区域;38.s4,根据映射关系表在数据前附加标签;39.s5,合并数据写入用户区域。40.参见图3,以通道0所连接的emmc0举例说明:设置的顺序写入和随机写入的判断条件是,当需要写入的sector(数据扇区),大小为512个字节,sector数量等于或超过32个时,认为写入的数据是顺序的,当sector数量小于32个时,认为数据是随机写入的,用来模拟顺序写入和随机写入的情况。lba英文全称为logicblockaddress,与directeba同样是逻辑块地址,但是二者之间是有区别的。以图1为例,数据写入过程中,为了使数据写入能够均衡,使用多个通道写入不同的emmc中,因此写入满一定块大小以后需要切换到不同channel(通道)进行。lba针对是多通道下的数据的逻辑块地址,而directeba则是具体针对某一个通道,例如channel0中,数据写入的逻辑块首地址。41.可以看到,图3中第一次写入位置为lba为32的情况下,64k的sector数据大小对应的sector计数数量为128,因为单个sector的大小为512个字节,这里的64k其实指代的是总的sector大小,1k的数据相当于两个sector计数,而我们用来判断是否有随机数据的依据,是sector的计数数量,也就是sectorcount是否大于32,所以这里的sector数量为128。另外,这里选择64k大小的sector扇区大小只是为了举例说明,所设定的大于随机与顺序写入阈值关系的值,所以是顺序写入,直接将数据写入到userarea的对应lba位置就行,这是因为顺序写入的时候directeba和phyeba是相同的,而第二次,lba为34,但是因为sector数量为4,所以是随机写入,这种情况下,我们是将数据写入到op区域,即额外配置区域。需要注意的是,因为lba是34,针对同一个directeba而言,还缺少前面的32和33的数据以及后面的一部分数据,所以需要从用户区域userarea位置将剩下的数据拷贝到op区域,这样保证了op区域的数据才是最新的有效数据。第三次的写入与第二次类似,这次则是将数据追加在第二次写入数据的后面,保证了随机数据在op区域内都是顺序的。42.参见图4为映射关系表mappingtable中directeba与phyeba的映射关系示意图,要如何保证这些被组合成顺序方式的随机数据在回写到userarea区域的顺序是正确的呢?故关于directeba与phyeba之间是存在一张总的映射关系表mappingtable来提供位置关系的。针对顺序写入,directeba与phyeba之间是相等的,而对于随机写入,二者则并不相等。43.可以看到,关于地址的表示是需要4个bytes的,为了缩减映射表的大小。我们将整个emmc分为了32个区域region(这个容量依赖于所选择的emmc本身的容量而变化,以一个具备4个emmc的256g的盘为例,单个emmc的容量为64g,所以切分为32个region以后每个region大小为2g),每个区域仅使用bit0来表示该区域是顺序写入的,bit1表示该区域是存在随机写入的,因此,对于那些顺序写入占大多数,随机写入表示少的情况,对于顺序写入的映射关系,利用顺序写入的directeba和phyeba之间相等的特性,我们仅需用1bit的数据0替代原来的4bytes,而随机写入的映射关系,则是通过bit=1的情况表明是随机写入以后,从而再去找mappingtable(mappingtable的组成就是像上述图4所描述的那样,每4个bytes的emmc逻辑地址对应4个bytes的emmc物理地址,完整的映射表就是由这样的一系列映射关系组所组成的。保证了我们在写入数据的时候,通过emmc逻辑地址,依靠映射表将数据写入正确的物理地址位置。)这张总表,通过这种方式可以有效提高查表的效率。44.接下来,最为关键。就是需要给写在op区域的随机数据提供必要的directeba信息了,如前述,对于随机写入而言,它的directeba与phyeba之间并不相等,所以需要有一个映射关系表,只有添加了这一部分信息才能保证掉电情况下也不会丢失随机写入数据的关于directeba与phyeba的映射关系,从而保证随机数据能够正确回写到emmc原来的逻辑块位置。45.参见图5为随机写入数据的tag及其构成。其中纵向额外配置区的构成,这4部分内容其实可以看成是两个部分,因为其系列构成都是一个大小为4kb的randomwritetag加上一组随机数据,所以后面和一部分其实和前面是一样的概念,只不过后者tag的具体内容与随机数据与前半部分并不一致而已。46.然后,关于randomwritetag,他的构成内容就是横向标签所展示出的这一部分。大小一共是4kb。构成上依次为:1)directeba就是emmc的逻辑地址、2)phyeba则是emmc的物理地址、3)sectorcount如上面提示的,是对写入的sata命令中sector计数的数量,也是证明后续跟随发送的数据包含随机数据(这个数量会大于32的阈值)、4)tagcount是为了保证所顺序串接的随机数据之间的前后关系不会紊乱,因为是将随机数据串接成顺序的形式进行写入,后面的数据理应是追加而不是覆盖前方的数据,所以tag的不同也能看出随机数据的先后关系、5)tagflag以及checksum这些是为了保证写入时候数据的正确性,因为任何数据写入的时候,各式各样的干扰都可能会造成写入数据出错的问题,数据错位或者是1写成0,0写成1,这些都会导致数据写入出错,检验和checksum便是为了能够在写入数据出错的时候提供校验而附加的校验位。47.然后就是dataofrandomcmd,这部分便是需要顺序化串接写入的随机数据。48.参见图5中的oparea,需要在每次写入随机数据之前,给写入的数据添加一个tag,tag记录了关于随机写入的映射信息。这样一来就能够保证,虽然将需要随机写入的信息通过组合到一起顺序地写入,但是最终存储到userarea处的数据内容能够保证不会出现错位的情况。而且需要注意的是,在写之前,是需要对op区域进行trim(擦除)的,优化之后的随机写入方式参见图6。49.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。当前第1页12当前第1页12

再多了解一些

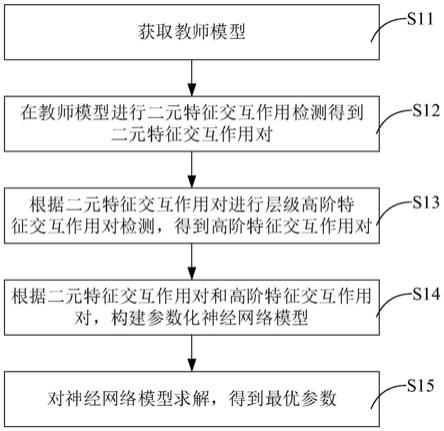

本文用于企业家、创业者技术爱好者查询,结果仅供参考。