1.本公开一般地涉及数据处理领域。更具体地,本公开涉及一种集成电路装置、电子设备、板卡和计算方法。

背景技术:

2.随着人工智能领域的发展,大规模神经网络涉及的运算数据量越来越大,对存储量的要求越来越高,例如反向传播中的卷积权重梯度等运算。在现有运算方式中,通常利用中央处理器(“cpu”)或者图像处理单元(“gpu”)等处理器进行运算。然而,即使采用并行计算的方式,由于处理器受制于内部寄存器资源的容量限制,庞大的数据运算量可能会导致处理器与外部存储设备之间产生大量的数据交互,从而降低设备的运算及处理效率。由于输入/输出(“i/o”)总线的带宽有限,由此可能会出现严重的i/o瓶颈问题,因此极大地降低了并行运算效率。另外,不仅i/o总线的带宽限制会成为性能的瓶颈,而且处理器与外部存储设备间大量的i/o访存量也会造成较大的计算和功耗开销。

技术实现要素:

3.为了至少解决在上文中所提到的技术问题,本公开提供了可以减少与外部存储设备的数据传输量,最大程度地降低总线带宽限制带来的i/o瓶颈问题的解决方案。具体地,本公开在如下的多个方面中提供前述的解决方案。

4.在第一方面中,本公开提供了一种集成电路装置,包括:

5.数据接口,其配置用于在所述集成电路装置和外部存储器之间传递数据;

6.存储单元,其配置成:

7.经由所述数据接口从所述外部存储器获取第一数据并发送至多个计算单元;以及

8.存储从多个计算单元处接收到的多个计算结果;

9.多个计算单元,其中每个计算单元配置成:

10.从所述存储单元处接收来自于所述外部存储器的第一数据;以及根据所述第一数据和预先存储的第二数据进行计算以得到计算结果,并将所述计算结果发送至所述存储单元。

11.在第二方面中,本公开提供了一种电子设备,包括前述及其稍后描述的多个实施例的集成电路装置。

12.在第三方面中,本公开提供了一种板卡,包括根据前述及其稍后描述的多个实施例的集成电路装置。

13.在第三方面中,本公开提供了一种使用集成电路装置来执行计算的方法,其中所述集成电路装置包括数据接口、存储单元和多个计算单元,所述数据接口用于在所述集成电路装置和外部存储器之间传递数据,存储单元用于经由所述数据接口从所述外部存储器获取第一数据并发送至多个计算单元;所述方法包括在每个计算单元处执行以下操作:

14.从所述存储单元处接收来自于所述外部存储器的第一数据;

15.根据所述第一数据和预先存储的第二数据进行计算以得到计算结果;以及

16.将所述计算结果发送至所述存储单元,以使其进行存储。

17.通过利用本公开上述的集成电路装置、电子设备、板卡和计算方法,可以将接收到的数据(例如上述第一数据)和计算出的结果(例如上述计算结果)均可存储在存储单元中,从而使得在调用以上数据和结果进行相应操作时只需与存储单元交互而无需与外部存储器交互。因此,本公开方案可减少集成电路装置通过i/o总线与外部存储器进行数据交互的数据吞吐量,从而克服i/o总线带宽瓶颈的问题,进而可以提升集成电路装置、电子设备或板卡的整体性能。

附图说明

18.通过参考附图阅读下文的详细描述,本公开示例性实施方式的上述以及其他目的、特征和优点将变得易于理解。在附图中,以示例性而非限制性的方式示出了本公开的若干实施方式,并且相同或对应的标号表示相同或对应的部分,其中:

19.图1是示出根据本公开实施例的板卡的结构图;

20.图2是示出根据本公开实施例的集成电路装置的结构图;

21.图3是示出根据本公开实施例的单核计算装置的内部结构示意图;

22.图4是示出根据本公开实施例的多核计算装置的内部结构示意图;

23.图5是示出根据本公开实施例的处理器核的内部结构示意图;

24.图6是示出根据本公开实施例的一种集成电路装置的结构示意图;

25.图7是示出根据本公开实施例的集成电路装置的数据传送示意图;

26.图8是示出根据本公开实施例的一种计算单元的示意架构图;

27.图9是示出根据本公开实施例的一种从计算单元的示意架构图;

28.图10是示出根据本公开实施例的另一种集成电路装置的结构示意图;以及

29.图11是示出根据本公开实施例的使用集成电路装置来执行计算的方法的简化流程图。

具体实施方式

30.下面将结合本公开实施例中的附图,对本公开实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本公开一部分实施例,而不是全部的实施例。基于本公开中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本公开公开的方案保护的范围。

31.下面结合附图来详细描述本公开的具体实施方式。

32.图1是示出根据本公开实施例的一种板卡10的结构示意图。可以理解的是图1所示结构和组成仅仅是一种示例,其并不用于在任何方面对本公开的方案进行限制。

33.如图1所示,板卡10包括芯片101,其可以是一种系统级芯片(system on chip,soc),也即本公开上下文中所描述的片上系统。在一个实施场景中,其可以集成有一个或多个组合处理装置。前述组合处理装置可以是一种人工智能运算单元,用以支持各类深度学习和机器学习算法,满足计算机视觉、语音、自然语言处理、数据挖掘等领域复杂场景下的智能处理需求,特别是深度学习技术大量应用在云端智能领域。云端智能应用的一个显著

特点是输入数据量大,对平台的存储能力和计算能力有很高的要求,而本实施例的板卡10适用在云端智能应用,具有庞大的片外存储、片上存储和强大的计算能力。

34.进一步如图中所示,芯片101通过对外接口装置102与外部设备103相连接。根据不同的应用场景,外部设备103例如可以是服务器、计算机、摄像头、显示器、鼠标、键盘、网卡或wifi接口等。待处理的数据可以由外部设备103通过对外接口装置102传递至芯片101。芯片101的计算结果可以经由对外接口装置102传送回外部设备103。根据不同的应用场景,对外接口装置102可以具有不同的接口形式,例如pcie接口等。

35.板卡10还可以包括用于存储数据的存储器件104,其包括一个或多个存储单元105。存储器件104通过总线与控制器件106和芯片101进行连接和数据传输。板卡10中的控制器件106可以配置用于对芯片101的状态进行调控。为此,在一个应用场景中,控制器件106可以包括单片机(micro controller unit,mcu)。

36.图2是示出根据上述实施例的芯片101中的组合处理装置的结构图。如图2中所示,组合处理装置20可以包括计算装置201、接口装置202、处理装置203和动态随机存取存储器(dynamic random access memory,dram)dram 204。

37.计算装置201可以配置成执行用户指定的操作,主要实现为单核智能处理器或者多核智能处理器。在一些操作中,其可以用于执行深度学习或机器学习方面的计算,并且还可以通过接口装置202与处理装置203进行交互,以共同完成用户指定的操作。在本公开的方案中,计算装置可以配置成执行经优化的神经网络模型的各类任务,例如本公开稍后将要描述的各种操作。

38.接口装置202可以用于在计算装置201与处理装置203间传输数据和控制指令。例如,计算装置201可以经由接口装置202从处理装置203中获取输入数据,写入计算装置201片上的存储装置。进一步,计算装置201可以经由接口装置202从处理装置203中获取控制指令,写入计算装置201片上的控制缓存中。替代地或可选地,接口装置202也可以读取计算装置201的存储装置中的数据并传输给处理装置203。

39.处理装置203作为通用的处理装置,执行包括但不限于数据搬运、对计算装置201的开启和/或停止等基本控制。根据实现方式的不同,处理装置203可以是中央处理器(central processing unit,cpu)、图形处理器(graphics processing unit,gpu)或其他通用和/或专用处理器中的一种或多种类型的处理器,这些处理器包括但不限于数字信号处理器(digital signal processor,dsp)、专用集成电路(application specific integrated circuit,asic)、现场可编程门阵列(field

‑

programmable gate array,fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件等,并且其数目可以根据实际需要来确定。如前所述,仅就本公开的计算装置201而言,其可以视为具有单核结构或者同构多核结构。然而,当将计算装置201和处理装置203整合共同考虑时,二者视为形成异构多核结构。根据本公开的方案,当处理装置203实施为通用处理器时,其可以执行用于优化神经网络模型的编译操作,以便将神经网络模型编译成由计算装置可执行的二进制指令序列。

40.dram 204用以存储待处理的数据,为ddr内存,大小通常为16g或更大,用于保存计算装置201和/或处理装置203的数据。

41.图3示出了计算装置201为单核的内部结构示意图。单核计算装置301用以处理计

531/wram 532与dram 204的访存;mvdma 534则用以控制nram 531/wram 532与存储单元(sram)408的访存。

48.回到图4,存储核407主要用以存储和通信,即存储处理器核406间的共享数据或中间结果、以及执行集群405与dram 204之间的通信、集群405间彼此的通信、处理器核406间彼此的通信等。在其他实施例中,存储核407可以具有标量运算的能力,用以执行标量运算。

49.存储核407可以包括静态随机存取存储器(static random

‑

access memory,sram)408、广播总线409、集群直接内存访问模块(cluster direct memory access,cdma)410及全局直接内存访问模块(global direct memory access,gdma)411。在一个实施场景中,sram 408可以承担高性能数据中转站的角色。由此,在同一个集群405内不同处理器核406之间所复用的数据不需要通过处理器核406各自向dram 204获得,而是经sram 408在处理器核406间中转。进一步,存储核407仅需要将复用的数据从sram 408迅速分发给多个处理器核406即可,从而可以提高核间通信效率,并显著减少片上片外的输入/输出访问。

50.广播总线409、cdma 410及gdma 411则分别用来执行处理器核406间的通信、集群405间的通信和集群405与dram 204的数据传输。以下将分别说明。

51.广播总线409用以完成集群405内各处理器核406间的高速通信,此实施例的广播总线409支持核间通信方式包括单播、多播与广播。单播是指点对点(例如单一处理器核至单一处理器核)的数据传输,多播是将一份数据从sram 408传输到特定几个处理器核406的通信方式,而广播则是将一份数据从sram 408传输到所有处理器核406的通信方式,属于多播的一种特例。

52.cdma 410用以控制在同一个计算装置201内不同集群405间的sram 408的访存。gdma 411与外部存储控制器401协同,用以控制集群405的sram 408到dram 204的访存,或是将数据自dram 204读取至sram 408中。从前述可知,dram 204与nram 431或wram 432间的通信可以经由2种方式来实现。第一种方式是通过iodam 433直接和dram 204与nram 431或wram 432通信;第二种方式是先经由gdma 411使得数据在dram 204与sram 408间传输,再经过mvdma 534使得数据在sram 408与nram 431或wram 432间传输。尽管第二种方式可能需要更多的元件参与且数据流较长,但实际上在部分实施例中,第二种方式的带宽远大于第一种方式,因此通过第二种方式来执行dram 204与nram 431或wram 432间的通信可能更为有效。可以理解的是,这里所描述的数据传输方式仅仅是示例性的,并且本领域技术人员根据本公开的教导,也可以根据硬件的具体布置来灵活地选择和适用各种数据传输方式。

53.在其他的实施例中,gdma 411的功能和iodma 533的功能可以整合在同一部件中。尽管本公开为了方便描述,将gdma 411和iodma 533视为不同的部件,然而对于本领域技术人员来说,只要其实现的功能以及达到的技术效果与本公开类似,即属于本公开的保护范围。进一步地,gdma 411的功能、iodma 533的功能、cdma 410的功能、mvdma 534的功能也可以由同一部件来实现。

54.根据上述结合各实施例的描述,本领域技术人员可以理解本公开也公开了一种电子设备或装置,其可以包括一个或多个上述板卡、一个或多个上述芯片和/或一个或多个上述组合处理装置。

55.根据不同的应用场景,本公开的电子设备或装置可以包括服务器、云端服务器、服

务器集群、数据处理装置、机器人、电脑、打印机、扫描仪、平板电脑、智能终端、pc设备、物联网终端、移动终端、手机、行车记录仪、导航仪、传感器、摄像头、相机、摄像机、投影仪、手表、耳机、移动存储、可穿戴设备、视觉终端、自动驾驶终端、交通工具、家用电器、和/或医疗设备。所述交通工具包括飞机、轮船和/或车辆;所述家用电器包括电视、空调、微波炉、冰箱、电饭煲、加湿器、洗衣机、电灯、燃气灶、油烟机;所述医疗设备包括核磁共振仪、b超仪和/或心电图仪。本公开的电子设备或装置还可以被应用于互联网、物联网、数据中心、能源、交通、公共管理、制造、教育、电网、电信、金融、零售、工地、医疗等领域。

56.进一步,本公开的电子设备或装置还可以用于云端、边缘端、终端等与人工智能、大数据和/或云计算相关的应用场景中。在一个或多个实施例中,根据本公开方案的电子设备或装置可以应用于云端设备(例如云端服务器),而功耗小的电子设备或装置可以应用于终端设备和/或边缘端设备(例如智能手机或摄像头)。在一个或多个实施例中,云端设备的硬件信息和终端设备和/或边缘端设备的硬件信息相互兼容,从而可以根据终端设备和/或边缘端设备的硬件信息,从云端设备的硬件资源中匹配出合适的硬件资源来模拟终端设备和/或边缘端设备的硬件资源,以便完成端云一体或云边端一体的统一管理、调度和协同工作。

57.以上结合图1

‑

图5对本公开的硬件架构及其内部结构进行了详细的描述。可以理解的是上述描述仅仅是示例性的而非限制性的。根据不同的应用场景和硬件规格,本领域技术人员也可以对本公开的板卡及其内部结构进行改变,而这些改变依然落入本公开的保护范围内。下面将对本公开的方案进行详细地描述。

58.图6是示出根据本公开实施例的一种集成电路装置600的结构示意图。为了说明集成电路装置600和外部存储器之间的关系,图6中还示出了外部存储器606。如图6中所示,集成电路装置600可以包括数据接口601、存储单元602和多个计算单元。多个计算单元例如可以为图6中所示的计算单元603、计算单元604

…

计算单元605。数据接口601可以配置用于在集成电路装置600和外部存储器606之间传递数据。在一个应用场景中,可以使用直接存储器访问(direct memory access,“dma”)接口作为前述的数据接口601,以便将外部存储器606的数据通过存储单元602发送至上述多个计算单元。

59.在一个实施例中,上述存储单元602可以配置成经由数据接口601从外部存储器606获取第一数据并发送至上述多个计算单元,并且其还可以存储从上述多个计算单元处接收到的多个计算结果。

60.基于不同的应用场景,上述计算单元的数目可以为大于或等于2的任一正整数,例如2个、3个或5个等,以便满足不同应用场景的运算需求。例如,当系统中有3个节点需要获取相应计算结果时,可以设置计算单元的数目为3,以通过该3个计算单元分别计算上述的3个节点的相应计算结果。与此同理,当系统中有5个节点需要获取相应计算结果时,则可设置5个计算单元。

61.在一个实施例中,上述多个计算单元中的每个计算单元可以配置成从存储单元602处接收来自于外部存储器606的第一数据。进一步,所述每个计算单元还可配置成根据第一数据和预先存储的第二数据进行计算以得到计算结果,并将计算结果发送至存储单元602。

62.上述的第一数据例如可以包括神经网络中的神经元数据,第二数据例如可以包括

神经网络中的权值。进一步,第一数据和第二数据可以为向量、矩阵、多维(三维或四维及以上)数据。根据不同的数据结构(例如不同的数据摆放规则),本公开的第一数据和/或第二数据可以各自包括一个或多个数据块。在一个运算场景中,当本公开的集成电路装置用于矩阵计算时,第一数据和/或第二数据还可以是矩阵中一定大小的分块,以用于矩阵的分块并行计算。

63.在一个实施场景中,上述每个计算单元可以基于不同应用场景的需求,根据第一数据和预先存储的第二数据进行相应的计算任务以得到计算结果。计算任务例如可以为人工智能领域(例如神经网络)中所涉及的卷积运算、矩阵乘矩阵运算、矩阵乘向量运算、偏置运算、全连接运算、gemm运算、gemv运算、激活运算中的一种或任意组合。

64.为了更好地理解本公开的集成电路装置如何进行运算,下面以图7中所示的集成电路装置700为例来说明本公开实施例的数据处理方法。为了描述简便,图7中仅示例性地示出了集成电路装置700包括三个计算单元的情况。如图7中所示,三个计算单元分别为计算单元703、计算单元704和计算单元705。

65.假定集成电路装置700执行神经网络的相关计算,并且神经网络的输入数据为ina,其存储于外部存储器例如外部存储器706中。计算单元703中预先存储有第二数据b1,计算单元704中预先存储有第二数据b2,并且计算单元705中预先存储有第二数据b3。在执行运算的初始阶段,外部存储器706可以将输入数据ina经由数据接口701发送至存储单元702,作为用于向上述多个计算单元发送的第一数据。

66.计算单元703在获得第一数据ina后,可以根据第一数据ina和计算单元703中的第二数据b1执行相应计算任务(如卷积运算),得到计算结果c1。计算单元704在获得第一数据ina后,可以根据第一数据ina和计算单元704中的第二数据b2执行相应的计算任务(如矩阵乘矩阵运算),得到计算结果c2。与上述两个计算单元同理,计算单元705可以根据第一数据ina和其中预先存储的第二数据b3执行相应的计算任务(如gemm运算),得到计算结果c3。本领域技术人员可以理解的是,上述每个计算单元中所执行的计算任务仅仅是示例性的而非限制性的,基于应用场景的不同,其还可执行前文所列举的其他计算任务,此处不再赘述。

67.由上述描述可见,本公开的集成电路装置可以将第一数据发送至存储单元并由其分别向多个计算单元进行发送,以供其进行计算。因此,可以减少集成电路装置通过i/o总线与外部存储器进行数据交互的数据吞吐量,从而克服i/o总线带宽的瓶颈问题。另外,本公开方案中的各个计算单元可并行执行数据接收以及数据计算,因此可保证每个计算单元的计算速度,从而保证集成电路装置的数据处理效率。

68.上述计算单元703、704和705在计算出计算结果c1、c2和c3后,还可进一步将这些计算结果发送至存储单元702进行存储,从而便于后续通过计算结果进行其他操作(例如计算)。可见,该种方式使得在调用计算结果时也只需与存储单元进行数据交互即可,从而减少了集成电路装置通过i/o总线与外部存储器进行数据交互的数据吞吐量,进一步克服i/o总线带宽瓶颈的问题。

69.通过上述描述可见,在本公开的集成电路装置中,接收到的数据(例如上述第一数据)和计算出的结果(例如上述计算结果)均可存储在存储单元中,从而使得在调用以上数据和结果进行相应操作时只需与存储单元交互而无需与外部存储器交互。因此,本公开方案可减少集成电路装置通过i/o总线与外部存储器进行数据交互的数据吞吐量,从而克服

了i/o总线带宽瓶颈的问题。

70.在一个实施例中,上述每个计算单元可以包括主计算单元和多个从计算单元。基于此,主计算单元可以配置成从上述存储单元处接收前述第一数据,将第一数据划分成多个第一子数据后分别发送至对应的多个从计算单元。在一个实施场景中,第一子数据的划分数目可与该计算单元所包含的从计算单元的数目相关联,例如第一子数据的划分数目可与该计算单元所包含的从计算单元的数目相等,从而使得每个从计算单元可以分配到第一子数据以进行后续计算。

71.另外,上述主计算单元还可以配置成从对应的多个从计算单元处接收中间结果,根据多个中间结果计算得到前述计算结果并发送至前述存储单元,以便其存储。对应地,每个从计算单元可以配置成根据上述第一子数据和预先存储的第二子数据进行计算以得到上述中间结果,并将该中间结果发送至上述主计算单元。此处的第二子数据为对该计算单元中预先存储的第二数据进行划分所形成的多个子数据中之一,并且第二数据划分形成的子数据的数目可与该计算单元所包含的从计算单元的数目相关联。例如第二数据划分形成的子数据的数目可与该计算单元所包含的从计算单元的数目相等,以便每个从计算单元可以分配到第二子数据并根据其进行相应计算。

72.为了进一步说明计算单元的架构及功能,下面将以图8中所示的计算单元800为例来进行详细描述。由图8可以看出,计算单元800可以包括主计算单元801和多个从计算单元。多个从计算单元例如可以为图8中所示的从计算单元802、从计算单元803

…

从计算单元804。从计算单元的数目可以根据不同应用场景的需求设定为不同的数目,例如可以为2个、4个或5个等,本公开实施例对此不作限制。

73.基于此,主计算单元801可以配置成从前述存储单元处接收第一数据。例如计算单元800为上述图7中的计算单元703时,则其可以从存储单元702处接收第一数据ina。在接收到第一数据ina后,主计算单元801可以将其划分为与从计算单元的数目相等的多个第一子数据a11、a12

…

a13。接着,主计算单元801可以将多个第一子数据a11、a12

…

a13分别发送至从计算单元802、从计算单元803

…

从计算单元804。

74.假定计算单元800中预先存储的第二数据为b1。基于对第一数据ina的划分,相应地,也可以将第二数据b1划分为与从计算单元的数目相等的多个第二子数据b11、b12

…

b13,并将它们分别存储于对应的从计算单元中。在本实施例中,设定将第二子数据b11存储于从计算单元802,将第二子数据b12存储于从计算单元803

…

,将第二子数据b13存储于从计算单元804。

75.在执行完上述数据划分和传送等操作后,从计算单元802可以根据第一子数据a11和第二子数据b11执行相应的计算子任务,得到中间结果c11。从计算单元803可以根据第一子数据a12和第二子数据b12执行相应的计算子任务,得到中间结果c12。以此类推,从计算单元804可以根据第一子数据a13和第二子数据b13执行相应的计算子任务,得到中间结果c13。在得到多个中间结果后,从计算单元802、从计算单元803

…

从计算单元804可以将对应的中间结果c11、c12

…

c13发送至主计算单元801。接着,主计算单元801可以根据多个中间结果c11、c12

…

c13计算(例如求和计算)得到计算结果c1并可进一步将该计算结果c1发送至存储单元(例如图7中的存储单元702)中进行存储,以便后续操作使用。

76.根据上述描述可见,由于每个计算单元的中间结果也可以存储于该计算单元中而

无需存储于外部存储器中,从而可以减少集成电路装置与外部存储器之间的数据交换,进而可以降低由于外部带宽限制而导致的i/o瓶颈。另外,由于将计算单元的计算任务划分为多个计算子任务,并分别由主计算单元和多个从计算单元执行,从而提高了数据的处理效率。

77.进一步,为了便于进行例如上述中间结果等数据的存储,在一个实施例中,上述每个计算单元还可以分别包括一个存储单元。该存储单元可以存储从主计算单元处接收到的中间结果。另外,除了可以存储中间结果外,存储单元还可以存储计算单元接收到的第一数据、预先存储的第二数据、对第一数据划分形成的多个第一子数据、对第二数据划分形成的多个第二子数据以及计算出的计算结果等,而上述第一数据、多个第一子数据以及计算结果均可由主计算单元处接收。

78.上文结合附图描述了计算单元的架构及数据处理流程。本公开方案还可根据上述计算单元的架构来类似地构建上述从计算单元的内部架构。例如,上述多个从计算单元中的每个也可以包括主计算子单元和多个从计算子单元。基于此,主计算子单元可以配置成从对应的主计算单元处接收前述第一子数据,将第一子数据划分成多个第一原子数据后分别发送至对应的多个从计算子单元。在一个实施场景中,第一原子数据的划分数目可与该从计算单元所包含的从计算子单元的数目相关联,例如第一原子数据的划分数目可与该从计算单元所包含的从计算子单元的数目相等,从而使得每个从计算子单元可以分配到第一原子数据以进行后续计算。

79.另外,上述主计算子单元还可以配置成从对应的多个从计算子单元处接收中间子结果,根据多个所述中间子结果计算得到前述中间结果并将其发送至对应的主计算单元,以便其根据该中间结果计算得到最终的计算结果。此处对应的主计算单元为向该主计算子单元发送第一子数据的主计算单元。对应地,每个从计算子单元可以配置成根据上述第一原子数据和预先存储的第二原子数据进行计算以得到上述中间子结果,并将该中间子结果发送至上述主计算子单元。此处的第二原子数据为对该从计算单元中预先存储的第二子数据进行划分所形成的多个原子数据中之一,并且第二子数据划分形成的原子数据的数目可与该从计算单元中所包含的从计算子单元的数目相关联。例如第二子数据划分形成的原子数据的数目可与该从计算单元中所包含的从计算子单元的数目相等,以便每个从计算子单元可以分配到第二原子数据,并根据其进行相应计算。

80.为了进一步说明从计算单元的架构及功能,下面将以图9中示出的从计算单元900为例来进行详细描述。由图9可以看出,从计算单元900可以包括主计算子单元901和多个从计算子单元。多个从计算单元例如可以为图9中所示的多个从计算子单元902、从计算子单元903

…

从计算子单元904。从计算子单元的数目可以根据不同应用场景的需求设定为不同的数目,例如可以为2个、4个或6个等,本公开实施例对此不作限制。

81.基于此,所述主计算子单元901可以配置成从对应的主计算单元处接收所述第一子数据。例如,从计算单元900为上述图8中的从计算单元802时,则其可以从主计算单元801处接收第一子数据a11。在接收到第一子数据a11后,主计算子单元901可以按照类似于前述计算单元的数据处理方式将所述第一子数据a11划分为与从计算子单元的数目相等的多个第一原子数据a111、a112

…

a113。接着,主计算子单元901可以将多个第一原子数据a111、a112

…

a113分别发送至多个从计算子单元902、从计算子单元903

…

从计算子单元904。

82.假定从计算单元900中预先存储的第二子数据为b11。基于对第一子数据a11的划分,可以将第二子数据b11划分为与从计算子单元的数目相等的多个第二原子数据b111、b112

…

b113,并将它们分别存储于对应的从计算子单元中。在本实施例中,设定将第二原子数据b111存储于从计算子单元902,将第二原子数据b112存储于从计算子单元903

…

,将第二原子数据b113存储于从计算子单元904。

83.在执行完上述数据划分和传送等操作后,从计算子单元902可以根据第一原子数据a111和第二原子数据b111执行相应的计算子任务,得到中间子结果c111。从计算子单元903可以根据第一原子数据a112和第二原子数据b112执行相应的计算子任务,得到中间子结果c112。以此类推,从计算子单元904可以根据第一原子数据a113和第二原子数据b113执行相应的计算子任务,得到中间子结果c113。在得到多个中间子结果后,从计算子单元902、从计算子单元903

…

从计算子单元904可以分别将对应的中间子结果c111、c112

…

c113发送至主计算子单元901。接着,主计算子单元901可以根据多个中间子结果c111、c112

…

c113计算得到中间结果c11并可进一步将该中间结果c11发送至对应的主计算单元(例如上述的主计算单元801),以便根据其进行计算得到最终的计算结果(例如c1)。

84.根据上述描述可见,由于本公开的每个从计算单元的中间子结果也可以存储于该从计算单元中而无需存储于外部存储器中,从而可以减少集成电路装置与外部存储器之间的数据交换,进而可以降低由于外部带宽限制而导致的i/o瓶颈。另外,由于将从计算单元的计算子任务进一步划分为多个二级计算子任务,并分别由主计算子单元和多个从计算子单元执行,从而提高了数据的处理效率。

85.进一步,为了便于进行例如上述中间子结果等数据的存储,在一个实施例中,上述每个从计算单元还可以分别包括一个存储单元。该存储单元可以存储从主计算子单元处接收到的中间子结果。另外,除了可以存储中间子结果外,存储单元还可以存储从计算单元接收到的第一子数据、预先存储的第二子数据、对第一子数据划分形成的多个第一原子数据、对第二子数据划分形成的多个第二原子数据以及计算出的中间结果等,而上述第一子数据、多个第一原子数据以及中间结果均可由主计算子单元处接收。

86.前文中结合各实施例对计算单元的各种数据处理进行了描述。在一个实施例中,为了实现可靠的数据处理,集成电路装置还可以包括控制单元。在一个实施例中,控制单元可以配置成控制每个计算单元中的主计算单元与多个从计算单元之间的信息交互以及主计算单元和/或多个从计算单元的数据计算。图10是示出根据本公开实施例的另一种集成电路装置1000的结构示意图。由图10可以看出,该实施例中的集成电路装置1000可以包括存储单元1001、多个计算单元以及控制单元1005。多个计算单元例如可以为图10中所示的计算单元1002、计算单元1003

…

计算单元1004。本实施例中的存储单元1001和计算单元的架构以及功能等可参照前述实施例,此处不再赘述。

87.在一个实施例中,控制单元1005可以配置成控制计算单元1002、计算单元1003

…

计算单元1004中的主计算单元与多个从计算单元之间的信息交互以及这些计算单元中的主计算单元和/或多个从计算单元的数据计算。为了描述简便,本实施例中仅以对计算单元1002的控制为例进行说明。对于计算单元1002,控制单元1005可以控制计算单元1002中的主计算单元1010将接收到的第一数据划分成多个第一子数据并将它们分别发送至从计算单元1011、从计算单元1012

…

从计算单元1013。另外,控制单元1005还可以控制主计算单元

1010从上述多个从计算单元处接收中间结果,并根据多个中间结果计算得到计算结果。

88.进一步,控制单元1005还可以控制从计算单元1011、从计算单元1012

…

从计算单元1013根据接收到的第一子数据和预先存储的第二子数据进行计算得到中间结果,并控制将中间结果发送至主计算单元1010。由此可见,通过控制单元的控制可使计算单元内部进行可靠的信息交互以及数据计算,从而保证计算单元的可靠数据处理。

89.进一步,为了保证计算单元和存储单元两者之间的信息交互,以实现可靠的数据读取和存储,在一个实施例中,上述控制单元还可以配置成控制每个计算单元中的主计算单元从存储单元处接收第一数据以及将计算结果发送至存储单元。仍以图10中的计算单元1002为例来说,控制单元1005还可配置成控制该计算单元1002中的主计算单元1010从存储单元1001处接收第一数据以及将计算结果发送至存储单元1001,从而保证计算单元1002和存储单元1001两者之间进行可靠的数据读取和存储。

90.上述实施例中仅示例性地列举了控制单元的部分控制功能,在另一些实施例中,该控制单元还可控制计算单元的主计算单元与多个从计算单元之间的其他信息交互、数据计算以及与其他设备(例如存储单元)之间的数据读取和存储,从而进一步保证计算单元的可靠数据处理以及与外部设备之间可靠的数据读取和存储。

91.为了计算不同节点处(例如不同的第一数据输出通道上)的计算结果,在一个实施例中,多个计算单元中的每个可分别位于不同的第一数据输出通道上,以使所述多个计算单元之间不复用第二数据。基于此,本公开方案可以利用第一数据和各个数据输出通道(第一数据输出通道)上的第二数据进行计算以得到不同数据输出通道上的计算结果。假设计算神经网络中不同神经元输出通道上的神经元输出数据,并且设置第一数据为神经元数据,第二数据为与各个神经元输出通道对应的权值。在该情况下,多个计算单元可以分别根据接收到的神经元数据和各个神经元输出通道的对应权值进行计算,从而得到不同神经元输出通道上的神经元输出数据。由此可见,本公开的方案可用于计算具有多个数据输出通道的系统中的多个输出数据。

92.正如上述实施例中所提到的,本公开方案中第一数据可以为神经网络的神经元数据,第二数据可以为神经网络的权值。基于此,多个计算单元中的每个还可配置成根据神经元数据和预先存储的权值进行卷积计算以得到所述计算结果,从而满足相应应用场景的需求。由此可知,针对不同的应用场景,多个计算单元中的每个还可配置成根据神经元数据和预先存储的权值进行其他计算以得到所述计算结果,此处的其他计算例如可以为前文所提到的神经网络中所涉及的矩阵乘矩阵运算、矩阵乘向量运算、偏置运算、全连接运算、gemm运算、gemv运算、激活运算中的一种或任意组合,此处不再详述。

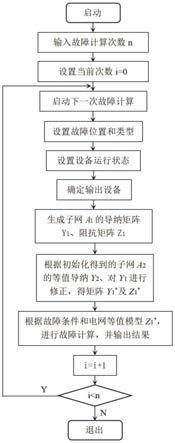

93.图11是示出根据本公开实施例的使用集成电路装置来执行计算的方法的简化流程图。根据前文的描述,可以理解这里的集成电路装置可以是结合前述各实施例所描述的集成电路装置,其具有所示出的内部连接关系并且支持附加的各类操作。

94.如图11所示,方法1100可以包括在步骤s1101处,从前述存储单元处接收来自于外部存储器的第一数据。接着,方法1100执行步骤s1102,根据第一数据和预先存储的第二数据进行计算以得到计算结果。最后,方法1100执行步骤s1103,将该计算结果发送至上述存储单元,以使其进行存储。

95.以上为了简明的目的,仅结合图11描述了本公开的计算方法。本领域技术人员根

据本公开的公开内容也可以想到本方法可以包括更多的步骤,并且这些步骤的执行可以实现前文结合各实施例所描述的本公开的各类操作,此处不再赘述。

96.需要说明的是,为了简明的目的,本公开将一些方法及其实施例表述为一系列的动作及其组合,但是本领域技术人员可以理解本公开的方案并不受所描述的动作的顺序限制。因此,依据本公开的公开或教导,本领域技术人员可以理解其中的某些步骤可以采用其他顺序来执行或者同时执行。进一步,本领域技术人员可以理解本公开所描述的实施例可以视为可选实施例,即其中所涉及的动作或模块对于本公开某个或某些方案的实现并不一定是必需的。另外,根据方案的不同,本公开对一些实施例的描述也各有侧重。鉴于此,本领域技术人员可以理解本公开某个实施例中没有详述的部分,也可以参见其他实施例的相关描述。

97.在具体实现方面,基于本公开的公开和教导,本领域技术人员可以理解本公开所公开的若干实施例也可以通过本文未公开的其他方式来实现。例如,就前文所述的电子设备或装置实施例中的各个单元来说,本文在考虑了逻辑功能的基础上对其进行划分,而实际实现时也可以有另外的划分方式。又例如,可以将多个单元或组件结合或者集成到另一个系统,或者对单元或组件中的一些特征或功能进行选择性地禁用。就不同单元或组件之间的连接关系而言,前文结合附图所讨论的连接可以是单元或组件之间的直接或间接耦合。在一些场景中,前述的直接或间接耦合涉及利用接口的通信连接,其中通信接口可以支持电性、光学、声学、磁性或其它形式的信号传输。

98.在本公开中,作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元示出的部件可以是或者也可以不是物理单元。前述部件或单元可以位于同一位置或者分布到多个网络单元上。另外,根据实际的需要,可以选择其中的部分或者全部单元来实现本公开实施例所述方案的目的。另外,在一些场景中,本公开实施例中的多个单元可以集成于一个单元中或者各个单元物理上单独存在。

99.在一些实现场景中,上述集成的单元可以采用软件程序模块的形式来实现。如果以软件程序模块的形式实现并作为独立的产品销售或使用时,所述集成的单元可以存储在计算机可读取存储器中。基于此,当本公开的方案以软件产品(例如计算机可读存储介质)的形式体现时,该软件产品可以存储在存储器中,其可以包括若干指令用以使得计算机设备(例如个人计算机、服务器或者网络设备等)执行本公开实施例所述方法的部分或全部步骤。前述的存储器可以包括但不限于u盘、闪存盘、只读存储器(read only memory,rom)、随机存取存储器(random access memory,ram)、移动硬盘、磁碟或者光盘等各种可以存储程序代码的介质。

100.在另外一些实现场景中,上述集成的单元也可以采用硬件的形式实现,即为具体的硬件电路,其可以包括数字电路和/或模拟电路等。电路的硬件结构的物理实现可以包括但不限于物理器件,而物理器件可以包括但不限于晶体管或忆阻器等器件。鉴于此,本文所述的各类装置(例如计算装置或处理装置)可以通过适当的硬件处理器来实现,例如cpu、gpu、fpga、dsp和asic等。进一步,前述的所述存储单元或存储装置可以是任意适当的存储介质(包括磁存储介质或磁光存储介质等),其例如可以是可变电阻式存储器(resistive random access memory,rram)、动态随机存取存储器(dynamic random access memory,dram)、静态随机存取存储器(static random access memory,sram)、增强动态随机存取存

储器(enhanced dynamic random access memory,edram)、高带宽存储器(high bandwidth memory,hbm)、混合存储器立方体(hybrid memory cube,hmc)、rom和ram等。

101.依据以下条款可更好地理解前述内容:

102.条款1、一种集成电路装置,包括:

103.数据接口,其配置用于在所述集成电路装置和外部存储器之间传递数据;

104.存储单元,其配置成:

105.经由所述数据接口从所述外部存储器获取第一数据并发送至多个计算单元;以及

106.存储从多个计算单元处接收到的多个计算结果;

107.多个计算单元,其中每个计算单元配置成:

108.从所述存储单元处接收来自于所述外部存储器的第一数据;以及根据所述第一数据和预先存储的第二数据进行计算以得到计算结果,并将所述计算结果发送至所述存储单元。

109.条款2、根据条款1所述的集成电路装置,其中每个计算单元包括主计算单元和多个从计算单元,其中:

110.主计算单元配置成:

111.从所述存储单元处接收所述第一数据;

112.将所述第一数据划分成多个第一子数据后分别发送至对应的多个从计算单元,其中所述第一子数据的划分数目与该计算单元所包含的从计算单元的数目相关联;

113.从对应的多个从计算单元处接收中间结果;以及

114.根据多个所述中间结果计算得到所述计算结果并发送至所述存储单元;

115.每个从计算单元配置成:

116.根据所述第一子数据和预先存储的第二子数据进行计算以得到所述中间结果,其中所述第二子数据为对该计算单元中预先存储的所述第二数据进行划分所形成的多个子数据中之一,并且所述第二数据划分形成的子数据的数目与该计算单元所包含的从计算单元的数目相关联;以及

117.将所述中间结果发送至所述主计算单元。

118.条款3、根据条款2所述的集成电路装置,其中所述多个从计算单元中的每个包括主计算子单元和多个从计算子单元,其中:

119.主计算子单元配置成:

120.从对应的所述主计算单元处接收所述第一子数据;

121.将所述第一子数据划分成多个第一原子数据后分别发送至对应的多个从计算子单元,其中所述第一原子数据的划分数目与该从计算单元所包含的从计算子单元的数目相关联;

122.从对应的多个从计算子单元处接收中间子结果;以及

123.根据多个所述中间子结果计算得到所述中间结果并将其发送至对应的主计算单元,其中所述对应的主计算单元为向所述主计算子单元发送所述第一子数据的主计算单元;

124.每个从计算子单元配置成:

125.根据所述第一原子数据和预先存储的第二原子数据进行计算以得到所述中间子

结果,其中所述第二原子数据为对该从计算单元中预先存储的第二子数据进行划分所形成的多个原子数据中之一,并且所述第二子数据划分形成的原子数据的数目与该从计算单元中所包含的从计算子单元的数目相关联;以及

126.将所述中间子结果发送至所述主计算子单元。

127.条款4、根据条款2所述的集成电路装置,还包括控制单元,其配置成控制每个所述计算单元中的所述主计算单元与所述多个从计算单元之间的信息交互以及所述主计算单元和/或所述多个从计算单元的数据计算。

128.条款5、根据条款4所述的集成电路装置,所述控制单元还配置成控制每个所述计算单元中的所述主计算单元从所述存储单元处接收所述第一数据以及将计算结果发送至所述存储单元。

129.条款6、根据条款1

‑

5中任一项所述的集成电路装置,其中所述多个计算单元中的每个分别位于不同的第一数据输出通道上,以使所述多个计算单元之间不复用所述第二数据。

130.条款7、根据条款1

‑

5中任一项所述的集成电路装置,其中所述第一数据为神经网络的神经元数据,所述第二数据为神经网络的权值,并且所述多个计算单元中的每个还配置成根据所述神经元数据和预先存储的权值进行卷积计算以得到所述计算结果。

131.条款8、一种电子设备,包括根据条款1

‑

7的任意一项所述的集成电路装置。

132.条款9、一种板卡,包括根据条款1

‑

7的任意一项所述的集成电路装置。

133.条款10、一种使用集成电路装置来执行计算的方法,其中所述集成电路装置包括数据接口、存储单元和多个计算单元,所述数据接口用于在所述集成电路装置和外部存储器之间传递数据,存储单元用于经由所述数据接口从所述外部存储器获取第一数据并发送至多个计算单元;所述方法包括在每个计算单元处执行以下操作:

134.从所述存储单元处接收来自于所述外部存储器的第一数据;

135.根据所述第一数据和预先存储的第二数据进行计算以得到计算结果;以及

136.将所述计算结果发送至所述存储单元,以使其进行存储。

137.应当理解,本公开的权利要求、说明书及附图中的术语“第一”、“第二”、“第三”和“第四”等是用于区别不同对象,而不是用于描述特定顺序。本公开的说明书和权利要求书中使用的术语“包括”和“包含”指示所描述特征、整体、步骤、操作、元素和/或组件的存在,但并不排除一个或多个其它特征、整体、步骤、操作、元素、组件和/或其集合的存在或添加。

138.还应当理解,在此本公开说明书中所使用的术语仅仅是出于描述特定实施例的目的,而并不意在限定本公开。如在本公开说明书和权利要求书中所使用的那样,除非上下文清楚地指明其它情况,否则单数形式的“一”、“一个”及“该”意在包括复数形式。还应当进一步理解,在本公开说明书和权利要求书中使用的术语“和/或”是指相关联列出的项中的一个或多个的任何组合以及所有可能组合,并且包括这些组合。

139.如在本说明书和权利要求书中所使用的那样,术语“如果”可以依据上下文被解释为“当...时”或“一旦”或“响应于确定”或“响应于检测到”。类似地,短语“如果确定”或“如果检测到[所描述条件或事件]”可以依据上下文被解释为意指“一旦确定”或“响应于确定”或“一旦检测到[所描述条件或事件]”或“响应于检测到[所描述条件或事件]”。

[0140]

虽然本文已经示出和描述了本公开的多个实施例,但对于本领域技术人员显而易

见的是,这样的实施例只是以示例的方式来提供。本领域技术人员可以在不偏离本公开思想和精神的情况下想到许多更改、改变和替代的方式。应当理解的是在实践本公开的过程中,可以采用对本文所描述的本公开实施例的各种替代方案。所附权利要求书旨在限定本公开的保护范围,并因此覆盖这些权利要求范围内的等同或替代方案。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。