1.本公开中所述实施例内容是有关于一种存储器技术,特别关于一种具有修复机制的存储器装置。

背景技术:

2.随着存储器技术的发展,存储器装置已应用至许多领域,以存储各式数据。基于不同的应用(例如:不同功耗),存储器装置需运作于不同的环境条件。当存储器装置中的位单元(bit cell)失效,将会影响到存储器装置的正常运作。

技术实现要素:

3.本公开的一些实施方式是关于一种存储器装置。存储器装置包含至少一个第一寄存器、一存储器电路、一分析电路以及一控制电路。存储器电路包含多个位单元。分析电路被配置为对这些位单元执行一分析程序,以产生一分析结果。若分析结果指示这些位单元中的一第一位单元失效,控制电路控制一数据写入至少一个第一寄存器,以及控制数据从至少一个第一寄存器读出,以完成一修复程序。

4.本公开的一些实施方式是关于一种存储器装置。存储器装置包含一存储器电路、一分析电路以及一控制电路。存储器电路包含多个位单元。分析电路被配置为分析这些位单元以产生一分析结果。若分析结果指示这些位单元中的一第一位单元失效,控制电路调整存储器装置的一操作电压以产生一调整操作电压,且存储器装置依据调整操作电压运作。

5.综上所述,本公开的存储器装置具有较佳的修复机制,可提升整体良率。

附图说明

6.为让本公开的上述和其他目的、特征、优点与实施例能够更明显易懂,附图的说明如下:

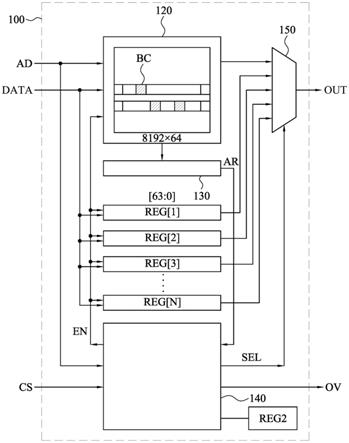

7.图1是依照本公开一些实施例所绘示的一存储器装置的示意图;

8.图2是依照本公开一些实施例所绘示的一存储器装置的示意图;

9.图3是依照本公开一些实施例所绘示的一存储器装置的示意图;

10.以及

11.图4是依照本公开一些实施例所绘示的一存储器装置的示意图。

具体实施方式

12.本文所使用的所有词汇具有其通常的意涵。上述词汇在普遍常用的字典中的定义,在本公开的内容中包含任一于此讨论的词汇的使用例子仅为示例,不应限制到本公开的范围与意涵。同样地,本公开亦不仅以于此说明书所示出的各种实施例为限。

13.本文所使用的用词“耦合”亦可指“电性耦合”,且用词“连接”亦可指“电性连接”。

“

耦合”及“连接”亦可指二个或多个组件相互配合或相互互动。

14.参考图1。图1是依照本公开一些实施例所绘示的存储器装置100的示意图。以图1标例而言,存储器装置100包含存储器电路120、分析电路130、控制电路140、选择电路150以及寄存器reg2。存储器装置100还包含寄存器reg[1]-reg[n],其中n为等于或大于1的正整数。

[0015]

存储器电路120耦合到分析电路130、控制电路140以及选择电路150。分析电路130耦合到控制电路140。控制电路140耦合到选择电路150、寄存器reg[1]-reg[n]以及寄存器reg2。寄存器reg[1]-reg[n]耦合到选择电路150。

[0016]

存储器电路120包含多个位单元(bit cell)bc。位单元亦可称为存储器单元。在这个例子中,存储器电路120包含8192

×

64个位单元bc。也就是说,这些位单元bc排列成8192行(row)以及64列(column)的数组型式。上述关于存储器电路120中位单元bc的数量仅用于示例,各种适用的数量皆在本公开所涵盖的范围内。

[0017]

分析电路130用以对存储器电路120中的这些位单元bc执行分析程序,以判断这些位单元bc中的哪些位单元bc是失效(fail)的,进而产生分析结果ar。若其中一位单元bc为失效,代表此位单元bc无法正常读写数据。分析结果ar将会携带此位单元bc的地址(失效地址)。

[0018]

控制电路140用以接收分析结果ar。如上所述,控制电路140会接收到携带有失效位单元bc的地址的分析结果ar。在一些实施例中,控制电路140会将分析结果ar存储于寄存器reg2中。也就是说,寄存器reg2可存储失效位单元bc的地址。

[0019]

当一外部处理器(未图示)欲对存储器装置100执行写入程序时,外部处理器会发送控制信号cs至控制电路140以控制控制电路140上电/启动。外部处理器亦会发送写入地址ad至存储器电路120以及控制电路140,且发送待写入的数据data至存储器电路120。控制电路140可依据分析结果ar判断写入地址ad是否为一失效地址。举例而言,控制电路140可将写入地址ad与携带于分析结果ar中的失效地址进行比对,以判断写入地址ad是否为失效地址。若写入地址ad为失效地址,控制电路140发送使能信号en以启动一对应的寄存器(例如:寄存器reg[1]),以将待写入的数据data写入寄存器reg[1]。借此,可避免将待写入的数据data存入存储器电路120中的失效地址,以使存储器装置100可正常运作。

[0020]

当外部处理器欲对存储器装置100执行读取程序时,外部处理器会发送读取地址ad至存储器电路120以及控制电路140。若控制电路140判断读取地址ad为失效地址,控制电路140会基于读取地址ad发送选择信号sel至选择电路150的选择端口。选择电路150依据选择信号sel选择一对应的寄存器(例如:寄存器reg[1]),且将寄存器reg[1]中的数据读出,以作为输出数据out。

[0021]

基于上述,当一位单元bc失效时,数据data是写入其中一寄存器(例如:寄存器reg[1])及从其中一寄存器(例如:寄存器reg[1])中读出。也就是说,本公开利用寄存器reg[1]-reg[n]以改变写入程序及读取程序的路径(使数据data未经过存储器电路120),进而完成修复程序。于此所称的“修复程序”是指当存储器电路120的一位单元发生失效时,通过特定机制使存储器装置100仍能正常运作。

[0022]

在一些实施例中,控制电路140是以处理器或微控制器实现,但本公开不以此为限。在一些实施例中,选择电路150是以多任务器来实现,但本公开不以此为限。

[0023]

在一些相关技术中,存储器装置中会额外设置一列(column)备用存储器电路。当存储器电路中的一位单元发生失效时,会利用此列备用存储器电路执行修复程序。也就是说,会将数据写入此列的存储空间或将数据从此列的存储空间读出,以完成修复程序。然而,由于备用存储器电路在电路布局上无法任意布设于其他零碎空间,因此将会限制整个电路的电路布局。

[0024]

相较于上述相关技术,本公开的存储器装置100可利用寄存器reg[1]-reg[n]完成修复程序。由于寄存器在电路布局上可布设于一些零碎空间,因此本公开可提高电路布局的弹性且无需更动其他组件的电路布局。

[0025]

在一些实施例中,若写入地址ad并未失效,控制电路140发送使能信号en启用存储器电路120,以将数据data写入存储器电路120中对应于写入地址ad的位单元bc。相似地,若读取地址ad并未失效,选择电路150可直接从存储器电路120将数据读出,以作为输出数据out。

[0026]

寄存器reg[1]-reg[n]的各者的容量可等于存储器电路120的一行(row)的容量。在这个例子中,存储器电路120的一行的容量为64位,但本公开不以此为限。实施上,若存储器电路120中的一位单元bc失效且此位单元bc位于第一行,当外部处理器要对第一行中的各位单元bc执行写入程序及读取程序时,可利用控制器140控制寄存器reg[1]以改变写入程序及读取程序的路径(使数据data未经过存储器电路120),以完成修复程序。若此失效位单元bc位于第二行,当外部处理器要对第二行中的各位单元bc执行写入程序及读取程序时,可利用控制器140控制寄存器reg[2]以改变写入程序及或读取程序的路径(使数据data未经过存储器电路120),以完成修复程序。以此类推。

[0027]

在一些其他的实施例中,寄存器reg[1]-reg[n]的各者的容量可等于存储器电路120的一列(column)的容量。

[0028]

在一些实施例中,存储器装置100可在测试阶段依据不同电压值的多个操作电压ov执行上述分析程序,以将对应于这些操作电压ov的所有失效地址存储于寄存器reg2中。如此,当外部处理器欲对存储器电路120执行写入程序及读取程序时,存储器电路120可运作在最佳操作电压ov(最少失效地址),且控制器140可控制寄存器reg[1]-reg[n]对寄存器reg2中所记录的所有失效地址执行修复程序。

[0029]

在一些实施例中,上述用以执行分析程序的操作电压ov包含三个电压值。举例而言,存储器装置100一般运作于最佳操作电压,而上述用以执行分析程序的操作电压ov可包含此最佳操作电压、高于最佳操作电压的一高电压以及低于最佳操作电压的一低电压。如此,当存储器装置120的操作电压ov有稍微偏移时,存储器装置120仍能正常运作。然而,本公开不以三个电压值为限。在一些其他的实施例中,用以执行分析程序的操作电压ov可包含超过三个电压值。

[0030]

参考图2。图2是依照本公开一些实施例所绘示的存储器装置200的示意图。图2的存储器装置200与图1的存储器装置100之间的主要差异在于,图2的存储器装置200可在测试阶段依据不同传输档位ck(也被称为“余裕档位”)执行上述分析程序。于此所述的“传输档位”是指写入程序及读取程序的频率上限。举例而言,当传输档位越高,代表存储器装置200执行写入程序及读取程序的频率上限越高,且存储器装置200的频率越快。当存储器装置200的频率越快,位单元bc较易失效。

[0031]

当存储器装置200在测试阶段依据不同传输档位ck执行上述分析程序后,可将对应于这些传输档位ck的所有失效地址存储于寄存器reg2中。如此,当外部处理器欲对存储器电路120执行写入程序及读取程序时,存储器电路120可运作在最佳传输档位ck,且控制器140可控制寄存器reg[1]-reg[n]对寄存器reg2中所记录的所有失效地址执行修复程序。

[0032]

由于图2的存储器装置200的部分操作类似于图1的存储器装置100,故于此不再赘述。

[0033]

参考图3。图3是依照本公开一些实施例所绘示的存储器装置300的示意图。图3的存储器装置300与图1的存储器装置100之间的主要差异在于,图3的存储器装置300包含非暂态存储电路non。

[0034]

在一些实施例中,可将在测试阶段不同测试条件(不同操作电压ov/不同传输档位ck)所测试到的失效地址存储于非暂态存储电路non中。当存储器装置300断电后,非暂态存储电路non中的数据不会遗失。据此,当外部处理器欲对存储器电路120执行写入程序及读取程序时,可基于非暂态存储电路non中所存储的失效地址直接利用寄存器reg[1]-reg[n]对失效地址执行修复程序。

[0035]

在一些实施例中,非暂态存储电路non是以电熔线实现,但本公开不以此为限。各种适用的非暂态存储电路皆在本公开所涵盖的范围内。

[0036]

由于图3的存储器装置300的部分操作类似于图1的存储器装置100,故于此不再赘述。

[0037]

参考图4。图4是依照本公开一些实施例所绘示的存储器装置400的示意图。以图4标例而言,存储器装置400包含存储器电路420、分析电路430、控制电路440以及寄存器reg3。

[0038]

存储器电路420耦合到分析电路430。分析电路430耦合到控制电路440。控制电路440耦合到存储器电路420以及寄存器reg3。

[0039]

分析电路430用以对存储器电路420中的这些位单元bc执行分析程序,以判断这些位单元bc中的哪些位单元bc是失效的,进而产生分析结果ar。当其中一位单元bc为失效,控制电路440调整存储器装置400的操作电压ov(例如:一般而言,调高操作电压ov可使存储器电路420中的位单元bc较不易失效),直至找出存储器电路420的位单元bc不会失效(或失效位置相对少)的操作电压ov。在一些实施例中,存储器装置400可被设置为依据调高后的操作电压ov(称为调整操作电压)运作。借此可提升存储器装置400的正常运作率。

[0040]

综上所述,本公开的存储器装置具有较佳的修复机制,可提升整体良率。

[0041]

各种功能性组件和方块已于此公开。对于具有本技术领域通常知识者而言,功能方块可由电路(不论是专用电路,或是在一个或多个处理器及编码指令控制下操作的通用电路)实现,其一般而言包含用以相应于此处描述的功能及操作对电气回路的操作进行控制的晶体管或其他电路组件。进一步地理解,一般而言电路组件的具体结构与互连,可由编译程序(compiler),例如寄存器传递语言(register transfer language,rtl)编译程序决定。寄存器传递语言编译程序对与汇编语言代码(assembly language code)相当相似的脚本(script)进行操作,将脚本编译为用于布局或制作最终电路的形式。

[0042]

虽然本公开已以实施方式公开如上,然其并非用以限定本公开,任何具有本领域通常知识者,在不脱离本公开的精神和范围内,当可以做出各种更动与润饰,因此本公开的

保护范围应以所附权利要求所界定者为准。

[0043]

【符号说明】

[0044]

100:存储器装置

[0045]

120:存储器电路

[0046]

130:分析电路

[0047]

140:控制电路

[0048]

150:选择电路

[0049]

200:存储器装置

[0050]

300:存储器装置

[0051]

400:存储器装置

[0052]

420:存储器电路

[0053]

430:分析电路

[0054]

440:控制电路

[0055]

reg[1]-reg[n]:寄存器

[0056]

reg2:寄存器

[0057]

reg3:寄存器

[0058]

bc:位单元

[0059]

ar:分析结果

[0060]

cs:控制信号

[0061]

ad:地址

[0062]

data:数据

[0063]

en:使能信号

[0064]

sel:选择信号

[0065]

out:输出数据

[0066]

ov:操作电压

[0067]

ck:传输档位

[0068]

non:非暂态存储电路

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。