技术特征:

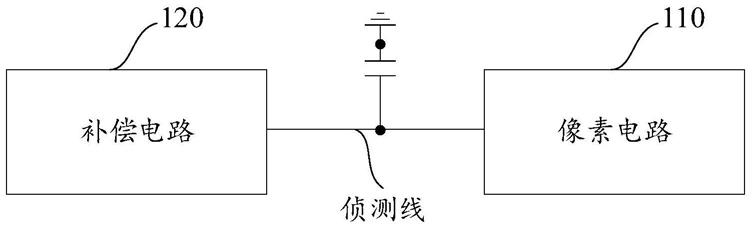

1.一种显示像素电路结构,其特征在于,所述显示像素电路结构包括补偿电路和像素电路,所述像素电路通过侦测线与所述补偿电路电连接,其中,所述补偿电路包括第一模块和第二模块;所述第一模块用于在侦测过程中经由所述侦测线向所述像素电路输入侦测信号;所述第二模块用于在所述侦测过程中经由所述侦测线侦测并存储所述像素电路的驱动晶体管的阈值电压;所述第一模块还用于在显示过程中接收来自数据信号端的原始数据信号并随之基于所存储的所述阈值电压将所述原始数据信号转换为经补偿的数据信号以补偿所述驱动晶体管的阈值电压的偏移,以及经由所述侦测线向所述像素电路输入所述经补偿的数据信号。2.根据权利要求1所述的显示像素电路结构,其特征在于,所述补偿电路还包括第一开关和第二开关;所述第一开关的控制端与第一控制信号端电连接,以接收第一控制信号序列,所述第一开关的第一端与所述第一模块电连接,以辅助所述第一模块向所述像素电路输出所述侦测信号以及所述经补偿的数据信号,所述第一开关的第二端与所述侦测线的第一端电连接;所述第二开关的控制端与第二控制信号端电连接,以接收第二控制信号序列,所述第二开关的第一端与所述第二模块电连接,以辅助所述第二模块侦测并存储所述像素电路的驱动晶体管的阈值电压,所述第二开关的第二端与所述侦测线的第一端电连接;其中,所述侦测线的第一端也与所述像素电路的第一节点电连接,并且所述第一开关和所述第二开关均为n型薄膜晶体管。3.根据权利要求2所述的显示像素电路结构,其特征在于,所述侦测线具有寄生电容,并且所述侦测线的第二端接地。4.根据权利要求3所述的显示像素电路结构,其特征在于,所述像素电路包括:驱动晶体管、第一晶体管、第二晶体管、储能元件和发光元件;所述驱动晶体管的控制端与第二节点电连接、第一端与第三节点电连接、第二端与第四节点电连接;所述第一晶体管的控制端与第一扫描信号端电连接,以接收第一扫描信号序列,所述第一晶体管的第一端与所述第二节点电连接、第二端与所述第一节点电连接;所述储能元件的第一端与所述第二节点电连接、第二端与所述第三节点电连接,其中,所述第三节点与第一电源信号端电连接,以接收第一电源电压;所述发光元件的第一端与所述第四节点电连接、第二端与第二电源信号电连接,以接收第二电源电压,其中,所述第二电源电压小于所述第一电源电压。5.根据权利要求4所述的显示像素电路结构,其特征在于,所述驱动晶体管、所述第一晶体管和所述第二晶体管均为n型薄膜晶体管;所述储能元件为电容;所述发光元件为发光二极管。6.根据权利要求5所述的显示像素电路结构,其特征在于,所述第二晶体管的控制端与第二扫描信号端电连接,以接收第二扫描信号序列,所述第二晶体管的第一端与所述第四

节点电连接、第二端与所述第一节点电连接。7.根据权利要求5所述的显示像素电路结构,其特征在于,所述第二晶体管的控制端与第二扫描信号端电连接,以接收第二扫描信号序列,所述第二晶体管的第一端与所述第四节点电连接、第二端与所述第二节点电连接。8.根据权利要求6所述的显示像素电路结构,其特征在于,所述侦测过程包括:侦测初始化阶段、阈值电压侦测阶段和采样阶段;在所述侦测初始化阶段,所述第一控制信号序列中的控制信号处于第一电位,以控制所述第一开关导通;所述第二控制信号序列中的控制信号处于第二电位,以控制所述第二开关截止;并且,所述侦测初始化阶段包括第一时间分段和第二时间分段;在所述第一时间分段,所述第一扫描信号序列中的扫描信号处于所述第一电位,以控制所述第一晶体管导通;所述第二扫描信号序列中的扫描信号处于所述第二电位,以控制所述第二晶体管截止;在所述第二时间分段,所述第一扫描信号序列中的扫描信号处于所述第二电位,以控制所述第一晶体管截止;所述第二扫描信号序列中的扫描信号处于所述第一电位,以控制所述第二晶体管导通;在所述阈值电压侦测阶段,所述第一控制信号序列中的控制信号处于所述第二电位,以控制所述第一开关截止;所述第二控制信号序列中的控制信号处于第二电位,以控制所述第二开关截止;所述第一扫描信号序列中的扫描信号处于所述第二电位,以控制所述第一晶体管截止;所述第二扫描信号序列中的扫描信号处于所述第一电位,以控制所述第二晶体管导通;在所述采样阶段,所述第一控制信号序列中的控制信号处于所述第二电位,以控制所述第一开关截止;所述第二控制信号序列中的控制信号处于所述第一电位,以控制所述第二开关导通;所述第一扫描信号序列中的扫描信号处于所述第二电位,以控制所述第一晶体管截止;所述第二扫描信号序列中的扫描信号处于所述第一电位,以控制所述第二晶体管导通。9.根据权利要求8所述的显示像素电路结构,其特征在于,在所述侦测初始化阶段的所述第一时间分段,所述第一模块通过所述第一开关和所述第一晶体管向所述像素电路的所述第二节点输入所述侦测信号;在所述侦测初始化阶段的所述第二时间分段,所述第一模块通过所述第一开关和所述第二晶体管向所述像素电路的所述第四节点输入复位信号;在所述采样阶段,所述第二模块通过所述第二开关和所述第二晶体管侦测所述第四节点的电位,以计算并存储所述驱动晶体管的阈值电压。10.根据权利要求7所述的显示像素电路结构,其特征在于,所述侦测过程包括:侦测初始化阶段、阈值电压侦测阶段和采样阶段;在所述侦测初始化阶段,所述第一控制信号序列中的控制信号处于第一电位,以控制所述第一开关导通;所述第二控制信号序列中的控制信号处于第二电位,以控制所述第二开关截止;所述第一扫描信号序列中的扫描信号处于所述第一电位,以控制所述第一晶体管导通;所述第二扫描信号序列中的扫描信号处于所述第二电位,以控制所述第二晶体管截止;在所述阈值电压侦测阶段,所述第一控制信号序列中的控制信号处于所述第二电位,

以控制所述第一开关截止;所述第二控制信号序列中的控制信号处于第二电位,以控制所述第二开关截止;所述第一扫描信号序列中的扫描信号处于所述第一电位,以控制所述第一晶体管导通;所述第二扫描信号序列中的扫描信号处于所述第一电位,以控制所述第二晶体管导通;在所述采样阶段,所述第一控制信号序列中的控制信号处于所述第二电位,以控制所述第一开关截止;所述第二控制信号序列中的控制信号处于所述第一电位,以控制所述第二开关导通;所述第一扫描信号序列中的扫描信号处于所述第一电位,以控制所述第一晶体管导通;所述第二扫描信号序列中的扫描信号处于所述第一电位,以控制所述第二晶体管导通。11.根据权利要求10所述的显示像素电路结构,其特征在于,在所述侦测过程中,所述第一电源信号端向所述第三节点提供第三电源电压,其中,所述第三电源电压小于所述第一电源电压;并且,在所述侦测初始化阶段,所述第一模块通过所述第一开关和所述第一晶体管向所述第二节点输入所述侦测信号;在所述采样阶段,所述第二模块通过所述第二开关和所述第二晶体管侦测所述第二节点的电位,以计算并存储所述驱动晶体管的阈值电压。12.根据权利要求8或10所述的显示像素电路结构,其特征在于,在所述显示过程中,所述第一控制信号序列中的控制信号处于所述第一电位,以控制所述第一开关导通;所述第二控制信号序列中的控制信号处于所述第二电位,以控制所述第二开关截止;所述第二扫描信号序列中的扫描信号处于所述第二电位,以控制所述第二晶体管截止;并且,所述显示过程包括:显示初始化阶段和发光阶段;在所述显示初始化阶段,所述第一扫描信号序列中的扫描信号处于所述第一电位,以控制所述第一晶体管导通;在所述发光阶段,所述第一扫描信号序列中的扫描信号处于所述第二电位,以控制所述第一晶体管截止。13.根据权利要求12所述的显示像素电路结构,其特征在于,在所述显示过程中,所述第一电源信号端向所述第三节点提供所述第一电源电压;并且,在所述显示初始化阶段,所述第一模块通过所述第一开关和所述第一晶体管向所述第二节点提供所述经补偿的数据信号。14.根据权利要求13所述的显示像素电路结构,其特征在于,所述第一电位为高电位,所述第二电位为低电位。15.一种显示面板,其特征在于,包含如权利要求1至14中任一项所述的显示像素电路结构。

技术总结

本公开提供一种显示像素电路结构及显示面板。其中,该显示像素电路结构包括像素电路和补偿电路,像素电路通过侦测线与补偿电路电连接,所述补偿电路包括第一模块和第二模块。在侦测过程中,所述第一模块用于经由所述侦测线向所述像素电路输入侦测信号,所述第二模块用于经由所述侦测线侦测并存储所述像素电路的驱动晶体管的阈值电压,在显示过程中,所述第一模块用于基于所存储的所述阈值电压经由所述侦测线向所述像素电路输入经补偿的数据信号,以补偿所述驱动晶体管的阈值电压的偏移。采用本公开提供的技术方案,可以实现更高像素密度的产品。像素密度的产品。像素密度的产品。

技术研发人员:卢奕宏

受保护的技术使用者:深圳市华星光电半导体显示技术有限公司

技术研发日:2021.08.18

技术公布日:2021/11/28

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。