一种支持低功耗无感唤醒的高速spi接口电路结构及其控制方法

技术领域

1.本发明属于高速数字接口技术领域,提出了一种支持低功耗无感唤醒的高速spi接口电路结构及其控制方法。

背景技术:

2.spi是由motorola提出的一种串行外设接口,它具有全双工和高效率的特点。spi的标准协议只占用四根线,不仅节约了芯片的管脚,同时也有利于pcb布局布线,且spi的通信原理很简单,与之相关的软件程序也很简单,正是由于这种简单易用的特性,现在越来越多的芯片集成了spi接口。motorola在提出spi协议时,没有定义其工作速率,通常芯片中的spi工作速率在1

‑

10m范围内。此外在通过spi接口唤醒芯片时,一般都需要在spi主设备端增加使用限制,如spi主设备端拉低片选后不能立即发起数据通信,需要等待spi从端芯片被唤醒后才能开始数据通信,否则spi从端将无法正确接收数据,或者是在软件协议中增加唤醒帧,通过唤醒帧来唤醒spi从端芯片,并确认芯片从低功耗状态正确退出,这两种做法均会对spi主端增加额外的使用约束,导致降低通信效率。

3.但是随着spi接口使用的普及,应用对spi的通信速率要求也越来越高,其通信速率需要达到40m甚至更高。在提高速率的基础上,应用也希望可以进一步提高spi的通信效率,尤其是为了兼容低功耗唤醒时的工作场景,上述常规手段虽然支持了低功耗唤醒的工作场景,但是降低了通信效率;为了提高通信效率,本发明的电路结构可以支持低功耗无感唤醒,即使芯片处于低功耗状态,对于spi主设备端也是一次正常的spi通信,在通信的过程中唤醒spi从端芯片,当芯片从低功耗状态退出时就可以直接处理接收到的数据,不需要限制spi主设备端拉低片选到发送第一个数据的时间,也不需要在软件协议中增加唤醒帧,从而进一步提高通信效率和降低软件复杂度。

技术实现要素:

4.针对上述问题,本发明提出了一种支持低功耗无感唤醒的高速spi接口电路结构及其控制方法,电路描述如下:

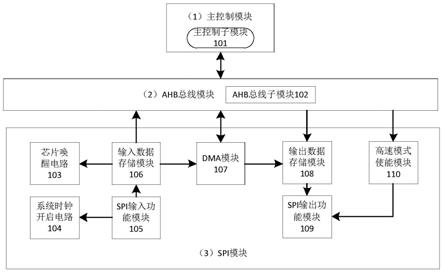

5.该电路主要由三个部分组成,分别是主控制模块(1)、ahb总线模块(2)和spi模块(3)。其中主控制模块有主控制子模块(101)构成,ahb总线模块由ahb总线子模块(102)构成,spi模块(3)由芯片唤醒电路(103)、系统时钟开启电路(104)、spi输入功能模块(105)、输入数据存储模块(106)、dma模块(107)、输出数据存储模块(108)、spi输出功能模块(109)和高速模式使能模块(110)构成。

6.主控制子模块(101)通过ahb总线子模块(102)分别与输入数据存储模块(106)、dma模块(107)、输出数据存储模块(108)和高速模式使能模块(110)相互连接,spi输入功能模块(105)分别与系统时钟开启电路(104)、输入数据存储模块(106)相互连接,输入数据存储模块(106)和芯片唤醒电路(103)相互连接,dma模块(107)通过ahb总线子模块(102)分别

与输入数据存储模块(106)和输出数据存储模块(108)相互连接,spi输出功能模块分别与输出数据存储模块(108)和高速模式使能模块(110)相互连接。

7.主控制子模块(101)根据应用需求配置整个电路系统中的寄存器参数,并启动电路功能。

8.ahb总线子模块(102)符合标准的amba总线协议,将电路中其它模块相互连接起来。

9.芯片唤醒电路(103)根据输入数据存储模块(106)接收到的数据量和电路的寄存器初始化配置条件判断是否唤醒芯片。

10.系统时钟开启电路(104)根据spi输入功能模块(105)判断当前spi模块是否处于通信状态,如果spi模块正在通信则开启系统时钟,从而给ahb总线子模块(102)和dma模块(107)提供工作时钟,避免接收数据溢出,导致通信失败。

11.spi输入功能模块(105)在芯片处于低功耗状态时依然可以保持与spi主设备端正常通信,且不会对spi主设备端增加任何使用限制,进而实现芯片低功耗状态下高速无感唤醒。

12.spi输入数据存储模块(106)的作用是用于缓存spi输入功能模块(105)接受的数据,防止接收数据溢出。

13.dma模块(107)主要用于输入数据存储模块(106)和输出数据存储模块(108)的数据搬移,当输入数据存储模块(106)缓存的数据大于一定阈值时,dma则会将数据搬走避免数据溢出,当输出数据存储模块(108)中的数据小于一定阈值时,dma则会往输出数据存储模块(108)中搬移数据,防止输出数据被读空。

14.输出数据存储模块(108)用于提前缓存准备发送给spi主设备端的数据,当主设备端发起通信时即可将缓存的数据发送出去。

15.spi输出功能模块(109)的功能是将输出数据存储模块(108)中缓存的数据发送给spi主设备端,且spi输出功能模块(109)与高速模式使能模块(110)配合工作可以实现spi模块高速通信模式。

16.高速模式使能模块(110)可以实现spi高速通信模式,当spi通信速率需要大于40m时,此时使能高速模式,spi输出功能模块(109)会提前半周期发送数据,使主设备端多出了半个周期的时序余量,从而实现spi高速通信。

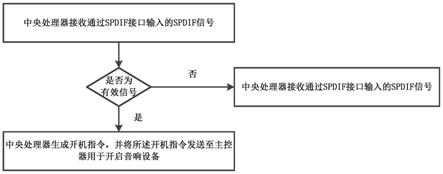

17.本发明提出了一种支持低功耗无感唤醒的高速spi接口电路结构及其控制方法,该控制方法描述如下:

18.(1)对spi模块(3)进行初始化配置,主控制子模块(101)根据应用需求配置整个电路系统中的寄存器参数,如果要进行spi高速通信,则需要再配置高速模式使能模块,然后执行启动功能,等待spi主设备发起通信。

19.(2)spi输入功能模块(105)处理spi主设备端发送过来的数据,并将数据存入输入数据存储模块(106),同时spi输入功能模块(105)生成系统时钟开启信号,并将该信号送给系统时钟开启电路(104)。

20.(3)系统时钟开启电路(104)判断芯片是否处于低功耗状态,如果芯片处于低功耗状态且接收到系统时钟开启信号,则电路会开启系统时钟,给dma模块(107)和芯片唤醒电路(103)提供工作时钟;反之,则电路会忽略该开启信号,并直接开始步骤(6)。

21.(4)输入数据存储模块(106)根据缓存的数据量生成芯片唤醒信号,并将该信号发送给芯片唤醒电路(103)。

22.(5)芯片唤醒电路(103)判断芯片是否处于低功耗状态,如果芯片处于低功耗状态且接收到唤醒信号,则电路会开始唤醒芯片;反之,则电路会忽略该唤醒信号。

23.(6)dma模块(107)将输入数据存储模块(106)中的数据搬移走,避免接收数据溢出。

24.(7)判断此次数据接收是否完成,如果完成则等待芯片处理接收数据,处理完成后主控制子模块(101)则会往输出数据存储模块(108)中缓存待发送数据,等待spi主设备发起通信。

25.(8)spi主设备发起通信,spi输出功能模块(109)将输出数据存储模块(108)中缓存的数据发送给spi主设备。

26.本发明成功将一种支持低功耗无感唤醒的高速spi接口电路实现,能够用于spi高速通信,通信速率支持大于40m,且支持低功耗状态下高速无感唤醒芯片。

附图说明

27.图1为本发明方法设计的一种支持低功耗无感唤醒的高速spi接口电路实现结构图。

28.图2为本发明方法设计的一种支持低功耗无感唤醒的高速spi接口电路结构的控制方法流程图。

具体实施方式:

29.结合图1,本发明的电路结构示意图,对本发明的电路结构进行详细说明。

30.该电路主要由三个部分组成,分别是主控制模块(1)、ahb总线模块(2)和spi模块(3)。其中主控制模块有主控制子模块(101)构成,ahb总线模块由ahb总线子模块(102)构成,spi模块(3)由芯片唤醒电路(103)、系统时钟开启电路(104)、spi输入功能模块(105)、输入数据存储模块(106)、dma模块(107)、输出数据存储模块(108)、spi输出功能模块(109)和高速模式使能模块(110)构成。

31.主控制子模块(101)通过ahb总线子模块(102)分别与输入数据存储模块(106)、dma模块(107)、输出数据存储模块(108)和高速模式使能模块(110)相互连接,spi输入功能模块(105)分别与系统时钟开启电路(104)、输入数据存储模块(106)相互连接,输入数据存储模块(106)和芯片唤醒电路(103)相互连接,dma模块(107)通过ahb总线子模块(102)分别与输入数据存储模块(106)和输出数据存储模块(108)相互连接,spi输出功能模块分别与输出数据存储模块(108)和高速模式使能模块(110)相互连接。

32.主控制子模块(101)根据应用需求配置整个电路系统中的寄存器参数,并启动电路功能。

33.ahb总线子模块(102)符合标准的amba总线协议,将电路中其它模块相互连接起来。

34.芯片唤醒电路(103)根据输入数据存储模块(106)接收到的数据量和电路的寄存器初始化配置条件判断是否唤醒芯片。

35.系统时钟开启电路(104)根据spi输入功能模块(105)判断当前spi模块是否处于通信状态,如果spi模块正在通信则开启系统时钟,从而给ahb总线子模块(102)和dma模块(107)提供工作时钟,避免接收数据溢出,导致通信失败。

36.spi输入功能模块(105)在芯片处于低功耗状态时依然可以保持与spi主设备端正常通信,且不会对spi主设备端增加任何使用限制,进而实现芯片低功耗状态下高速无感唤醒。

37.spi输入数据存储模块(106)的作用是用于缓存spi输入功能模块(105)接受的数据,防止接收数据溢出。

38.dma模块(107)主要用于输入数据存储模块(106)和输出数据存储模块(108)的数据搬移,当输入数据存储模块(106)缓存的数据大于一定阈值时,dma则会将数据搬走避免数据溢出,当输出数据存储模块(108)中的数据小于一定阈值时,dma则会往输出数据存储模块(108)中搬移数据,防止输出数据被读空。

39.输出数据存储模块(108)用于提前缓存准备发送给spi主设备端的数据,当主设备端发起通信时即可将缓存的数据发送出去。

40.spi输出功能模块(109)的功能是将输出数据存储模块(108)中缓存的数据发送给spi主设备端,且spi输出功能模块(109)与高速模式使能模块(110)配合工作可以实现spi模块高速通信模式。

41.高速模式使能模块(110)可以实现spi高速通信模式,当spi通信速率需要大于40m时,此时使能高速模式,spi输出功能模块(109)会提前半周期发送数据,使主设备端多出了半个周期的时序余量,从而实现spi高速通信。

42.结合图2,本发明的控制方法流程图,对本发明的具体实施方式进行说明。

43.(1)对spi模块(3)进行初始化配置,主控制子模块(101)根据应用需求配置整个电路系统中的寄存器参数,如果要进行spi高速通信,则需要再配置高速模式使能模块,然后执行启动功能,等待spi主设备发起通信。

44.(2)spi输入功能模块(105)处理spi主设备端发送过来的数据,并将数据存入输入数据存储模块(106),同时spi输入功能模块(105)生成系统时钟开启信号,并将该信号送给系统时钟开启电路(104)。

45.(3)系统时钟开启电路(104)判断芯片是否处于低功耗状态,如果芯片处于低功耗状态且接收到系统时钟开启信号,则电路会开启系统时钟,给dma模块(107)和芯片唤醒电路(103)提供工作时钟;反之,则电路会忽略该开启信号,并直接开始步骤(6)。

46.(4)输入数据存储模块(106)根据缓存的数据量生成芯片唤醒信号,并将该信号发送给芯片唤醒电路(103)。

47.(5)芯片唤醒电路(103)判断芯片是否处于低功耗状态,如果芯片处于低功耗状态且接收到唤醒信号,则电路会开始唤醒芯片;反之,则电路会忽略该唤醒信号。

48.(6)dma模块(107)将输入数据存储模块(106)中的数据搬移走,避免接收数据溢出。

49.(7)判断此次数据接收是否完成,如果完成则等待芯片处理接收数据,处理完成后主控制子模块(101)则会往输出数据存储模块(108)中缓存待发送数据,等待spi主设备发起通信。

50.(8)spi主设备发起通信,spi输出功能模块(109)将输出数据存储模块(108)中缓存的数据发送给spi主设备。以上实施例仅用以说明而非限制本发明的技术方案,尽管参照上述实施例对本发明进行了详细说明,本领域的普通技术人员应当理解:依然可以对本发明进行修改或等同替代,而不脱离本发明的精神和范围的任何修改或局部替代,其均应涵盖在本发明的权利要求范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。