1.本发明涉及一种基于单数字信号处理单元的双乘法计算装置和方法,属于数字信号处理技术领域。

背景技术:

2.目前的机器学习技术中,卷积神经网络是一种实用价值极高的神经网络。为了高效实现卷积神经网络的硬件部署,大量计算加速的研究应运而生。乘法是卷积神经网络的重要计算之一,但如何充分利用硬件资源进行乘法加速,却存在很多空白。

3.基于现场可编程逻辑门阵列(fpga),对卷积神经网络算法的硬件部署过程中,乘法器有基于查找表(lut)和数字信号处理单元(dsp)的两种实现方案。由于lut资源受限,因此乘法器的部署往往依赖dsp。但卷积神经网络中的乘法位宽往往远小于dsp的操作数位宽,因此造成了硬件资源的浪费。由于卷积核权重固定,在卷积过程中可作为多个激励的公共乘数,一些研究据此将多个激励拼接为长操作数与权值相乘,对结果进行截位后,就能通过一次乘法操作得到多个结果。但该方法仅限于无符号数之间的运算,不能通用有符号数的乘法。

4.卷积神经网络使用的非线性激活函数和数据增强方法,对提高网络的性能有重要作用,而这些操作通常会产生有符号数;因此,将一次dsp乘法实现多个卷积乘法的适用范围,拓展到有符号数的乘法就十分必要。

技术实现要素:

5.为了使卷积神经网络能够获得较快的运算速度和使用较少的电路资源,本发明针对复用相同乘数的有符号定点数乘法,提出了一种基于单数字信号处理单元的双乘法计算装置和方法。

6.本发明装置的技术方案如下:

7.一种基于单数字信号处理单元的双乘法计算装置,该装置包括:输入处理单元,用于拼接具有公共乘数w的两个被乘数x1和x2,拼接后得到的长乘数从高位到低位依次为:被乘数x1、保留位、被乘数x2绝对值的长乘数x;通用乘法器单元,用于计算长乘数x与公共乘数w的乘法运算;输出修正单元,用于根据公共乘数w的符号位和被乘数x2的数值,对通用乘法器单元的输出结果进行拆分和修正,得到待求乘积y1=x1*w和y2=x2*w的输出值。

8.进一步地,所述通用乘法器单元仅包括一个基于单数字信号处理单元的乘法器。

9.进一步地,所述输入处理单元包括取绝对值单元和输入拼接单元。

10.进一步地,所述输出修正单元包括乘积拆分单元和乘积修正单元。

11.本发明还提供一种基于单数字信号处理单元的双乘法计算方法,该方法基于单数字信号处理单元的一次乘法运算,计算共享同一乘数的两次定点数乘法的结果,具体步骤包括:(1)将具有公共乘数的两个被乘数拼接为一个长乘数;(2)将所述长乘数与公共乘数进行乘法操作,得到长乘数与公共乘数的积;(3)根据两个被乘数与公共乘数的位宽,将步

骤(2)计算得到的长乘数与公共乘数的积,拆分成两个待求乘积的中间结果;根据第二个被乘数的符号位,对第二个被乘数与公共乘数乘积的中间结果进行修正,得到第二个被乘数与公共乘数的乘积;根据第二个被乘数是否为零与公共乘数的符号位,对第一个被乘数与公共乘数乘积的中间结果进行修正,得到第一个被乘数与公共乘数的乘积。

12.进一步地,所述步骤(1)中,长乘数从高位到低位依次为第一个被乘数,保留位和第二个被乘数的绝对值;其中保留位为位宽与公共乘数相同的若干零。

13.进一步地,所述步骤(3)中,第一个被乘数与公共乘数乘积的中间结果,为长乘数与公共乘数的积的最高若干位,位宽等于第一个被乘数位宽与公共乘数位宽之和;第二个被乘数位宽与公共乘数乘积的中间结果,为长乘数与公共乘数的积的最低若干位,位宽等于第二个被乘数位宽与公共乘数位宽之和。

14.进一步地,如果公共乘数的符号位为1,且第二个被乘数不为零,则第一个被乘数与公共乘数的乘积最终结果为:第一个被乘数与公共乘数乘积的中间结果加1;否则,第一个被乘数与公共乘数的乘积最终结果为:第一个被乘数与公共乘数乘积的中间结果;如果第二个被乘数小于零,则第二个被乘数与公共乘数的乘积最终结果为:第二个被乘数与公共乘数乘积中间结果的相反数;否则,第二个被乘数与公共乘数的乘积最终结果为:第二个被乘数与公共乘数乘积的中间结果。

15.本发明具有以下有益效果:

16.(1)本发明提供的基于单数字信号处理单元的双乘法计算装置,可以计算任意有符号数或无符号数的乘法,具有一定的通用性。

17.(2)充分利用了数字信号处理单元的位宽,提高了计算资源的利用率,降低了计算资源的消耗,节省了lut开销,并且有效提高了卷积运算的数据吞吐率。

18.(3)能够将共享乘数的两次短操作数乘法,合并为一次长操作数乘法,同时输出两个乘法结果,提高了运算速度,增加了数据吞吐率。

19.(4)利用少量修正资源,实现单dsp一次运算实现两次乘法,整体计算资源消耗小于单独例化两个乘法器的消耗,有利于有限计算资源的灵活部署。

附图说明

20.图1是本发明计算装置的整体架构图。

21.图2是有符号定点数的示意图。

22.图3是输入处理单元输出数据格式的示意图。

23.图4是输入处理单元的内部结构示意图。

24.图5是输出修正单元的内部结构示意图。

25.图6是fpga平台下利用本发明部署卷积运算单元的示意图。

具体实施方式

26.以下结合附图对本发明方案进行详细说明。

27.图1是本发明的基于单数字信号处理单元的双乘法计算装置的结构示意图。计算装置包括输入处理单元,用于拼接共享同一乘数的两个被乘数x1和x2,拼接后得到的长乘数从高位到低位依次为:被乘数x1、保留位、被乘数x2绝对值的长乘数x;通用乘法器单元,用于

计算长乘数x与公共乘数w的乘法运算;输出修正单元,用于根据公共乘数w的符号位和被乘数x2的数值,对通用乘法器单元的输出结果进行拆分和修正,得到待求乘积y1=x1*w和y2=x2*w。

28.本实施例有符号定点数的表示形式如图2所示,分为符号位和数值位。对于一个n位的有符号定点数x,如果其二进制表示为a

n

‑1a

n

‑2…

a1a0,则其表示的十进制值为:

[0029][0030]

根据有符号定点数每一位的权值,可以得到以下推导:对一个位宽为(a b c)的有符号数,其最高a位可视为一有符号数乘以2

(b c)

后的值,最低c位可视为一无符号数。据此,一最高a位为有符号数a=a

a

‑1a

a

‑2…

a1a0,中间b位均为零,最低c位为无符号数c=c

c

‑1c

c

‑2…

c1c0的有符号数x的值可表示为:

[0031]

x=a*2

(b c)

c

ꢀꢀꢀ

(2)

[0032]

该有符号数与一位宽为b的有符号数b=b

b

‑1b

b

‑2…

b1b0的乘积p为:

[0033]

p=x*b=a*b*2

(b c)

c*b

ꢀꢀꢀ

(3)

[0034]

由二进制数的乘法规则可知,位宽为m和n的数相乘,其有效位宽不会超过(m n),因此乘积p的两部分p1=a*b*2

(b c)

与p2=c*b的有效位不会发生重叠,且其有效位分别对应乘积p的高(a b)位和低(b c)位。根据这一性质,若通过一次乘法计算两个位宽分别a和c的有符号数x1、x2与位宽为b的公共乘数w,可设置一位宽为(a b c)的有符号数x作为长乘数,将x1置于x的高a位,将x2的绝对值|x2|置于x的低c位。其中长乘数x的值如下所示,在实施例中通过位拼接操作实现,图3展示了长乘数x的形式:

[0035]

x=x1*2

(b c)

|x2|

ꢀꢀꢀ

(4)

[0036]

|x2|在实施例中的求解如(5)所示。其中sign(x2)为x2的符号位,即最高位;为x2按位取反的值:

[0037][0038]

注意128和

‑

128的8位二进制表示相同,因此不存在溢出的情况。

[0039]

由公式(3)得到的x与w的乘积y为:

[0040]

y=x*w=x1*w*2

(b c)

|x2|*w

ꢀꢀꢀ

(6)

[0041]

易知y为一位宽为(a 2b c)的有符号数。取y的高(a b)位作为x1*w的中间结果低(b c)位作为x2*w的中间结果中间结果的含义是,该结果并非最终的乘法运算结果,需要根据乘数的性质进行修正,结果修正的依据和方法如下:

[0042]

由公式(6)可知,当w<0且|x2|≠0时,低位的运算结果为一负数,由计算机执行有符号数乘法的原理可知,当w<0且|x2|≠0时,低位的位扩展会对高位结果产生干扰,影响高位结果的准确性,由x2和w的位宽可知:

[0043]

||x2|*w|≤|(2

c

‑

1)*(

‑

2)

b

|<2

(b c)

ꢀꢀꢀ

(7)

[0044]

由公式(1)可知,虽然截位后的可视为有符号数,但在y中被视为一正数因此由公式(7)得,y的真值满足:

[0045]

[0046]

公式(8)中第二个不等号在|x2|*w≥0时等号成立,此情况下,高位的中间结果恰好等于x1*w的真值y1;否则由公式(8)易得,由此得到实施例中y1的修正方法:

[0047][0048]

由公式(6)可知,将看作有符号数时,其取值满足以下条件:

[0049][0050]

由公式(10)得到实施例中y2的修正方法,其中sign(x2)是乘数x2的符号位,为为按位取反的值:

[0051][0052]

至此,整个计算过程完成。

[0053]

实施例

[0054]

(1)利用本发明计算装置来计算8比特无符号定点数乘法,被乘数x1、x2的取值分别为

‑

117(10001011)和34(00100010),公共乘数w为

‑

50(11001110),则长乘数x位宽为24,保留位为八个0,乘法器定义为24bit*8bit有符号数乘法器,计算将依次经过以下处理单元完成:

[0055]

输入处理单元:如图4所示,包括取绝对值单元和输入拼接单元,首先,取绝对值单元对被乘数x2取绝对值,本实施例中x2=34,则输出为|x2|=34(0010 0010);然后,将被乘数x1,保留位与|x2|按从高位到低位的顺序由输入拼接单元拼接为长乘数x,结果为100010110000000000100010。

[0056]

通用乘法器单元:执行长乘数x与公共乘数w的有符号乘法,输出中间结果y。此例中y的结果为00010110110110011111100101011100。

[0057]

输出修正单元:如图5所示,包括乘积拆分单元和两个乘积修正单元。首先,乘积拆分单元根据被乘数x1、x2和公共乘数w的位宽,得到中间结果y的拆分方式。在本实施例中,y的高16位为x1*w的中间结果(0001 0110 1101 1001),低16位为x2*w的中间结果(1111100101011100)。然后,根据公式(9)判断待求乘积y1=x1*w的取值:本实施例中,由于w的符号位为1,且x2≠0,因此结果为0001 0110 1101 1010,即5850;根据公式(11)判断的待求乘积y2=x2*w的取值:本实施例中,x2符号位为0,因此结果为1111100101011100,即

‑

1700。

[0058]

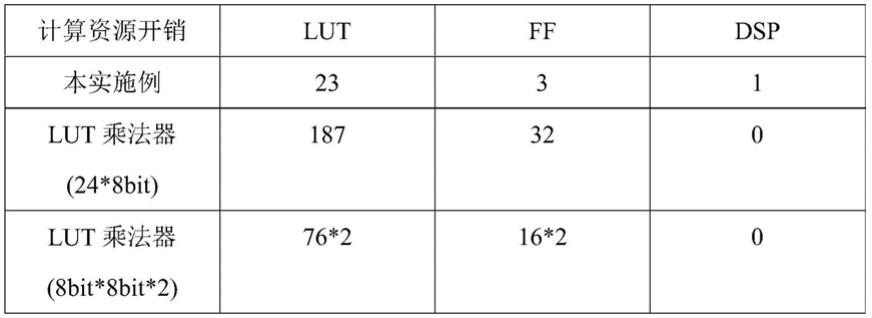

在xilinx的vivado 2018.2下,基于开发板zynqultrascale zcu102 evaluation board,综合本发明的硬件设计,本实施例与相同功能乘法器计算资源开销的对比如下表所示:

[0059]

表1计算开销对比

[0060][0061]

本实施例的lut消耗远小于完全基于lut搭建的乘法器,在充分利用dsp位宽的同时,有效缓解了特定算法在硬件部署过程中,lut资源开销过大的问题。本实施例所用ff(flip flop,触发器)的数量也大大减少。同时,本实施例基于单次dsp乘法计算,得到两次乘法的结果,利用相同硬件资源,使复用公共因子的有符号数乘法数据吞吐率翻倍。

[0062]

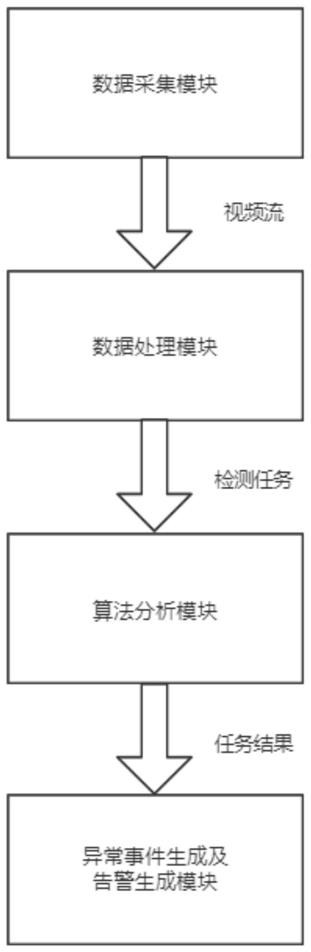

(2)本实施例以卷积神经网络的硬件部署为例,说明本发明提供的计算装置如何进行实际部署。图6所示的3*3卷积计算单元中,部署了三个本发明的计算装置(用“*”表示)。其中每个装置负责计算不同行的激励和权重,数字代表激励或权重在该行数据中的顺序。本发明的计算装置每个时钟周期可同时输入行方向上连续的两个激励值,与该行对应的权重进行乘法,每三个周期输出两个卷积结果,实现了卷积乘法的计算加速。

[0063]

(3)本实施例以最低位权值为2

i

(i为不为零的整数)的有符号定点数为例,说明本发明提供的计算方法的普适性。假设被乘数x1(a bit)、x2(b bit)和公共乘数w(c bit)最低位的权值依次为2

a

,2

b

,2

c

,不失一般性地,按照本发明提供的计算方法得到的待求乘积y1,y2,其二进制形式不依赖最低位权值的大小。在二进制转换为十进制时,将y1最低位权值视为2

a b

,y2最低位权值视为2

b c

进行转换,即可得到正确的结果。或者假设小数点左边一位权值为1,如果不存在小数点,则最低位权值为1。在该假设下判断a b(或b c)的值,若大于零,则在结果y1(或y2)的右边补|a b|(或|b c|)为零,则其结果由具体实施方法一节的公式(1)给出。若小于零,则在y1(或y2)从最低位起第|a b|(或|b c|)的左边打小数点,也可以得到各位权值含义明确的二进制有符号数。

[0064]

以上所述,仅为本公开的具体实施方式,但本公开的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本公开揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本公开的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。