1.本发明涉及可编程半导体器件技术领域,特别涉及一种用于可编程半导体器件的通用处理系统及通用处理方法。

背景技术:

2.集成电路的分类方法有很多,按照功能可分为存储器(memory)、微处理器(cpu)、定制电路(asics)和可编程半导体器件(programmable semiconductor devices)。可编程半导体器件中又可分为简单可编程逻辑器件(spld)、复杂可编程逻辑器件(cpld)和现场可编程门阵列(fpga)。

3.可编程半导体器件被广泛地应用于各个领域中,如工业控制、嵌入式系统、密码学、航空飞船、网络等。这主要源于可编程半导体器件可提供高性能、低一次性工程费用成本,非常适合大电路的实现以及快速的上市。同时,为了进一步增强可编程半导体器件的处理性能,各个厂商会在可编程半导体器件内集成一些具有特定功能的硬件电路,如mcu、adc/dac、serdes等,我们称之为hardcore,即硬核;相对应的,我们称可编程半导体器件内可由用户进行编程的硬件部分为softcore,即软核。

4.虽然硬核的加入可以改善可编程半导体器件的性能,但是由于其采用了固定的状态机控制,导致硬核应用的灵活性受到一定的限制,降低了可编程半导体器件应用的广泛度。因此,如何解决硬核应用的灵活性受限的问题,成了本领域技术人员亟待解决的一个难题。

技术实现要素:

5.本发明的目的在于提供一种通用处理系统及通用处理方法,以解决现有技术中硬核应用的灵活性受限的问题。

6.为解决上述技术问题,本发明提供一种通用处理系统,用于可编程半导体器件,所述可编程半导体器件包括硬核和软核,所述通用处理系统包括:任务代理器、指令存储单元、通用处理器和通用控制代理器;其中,

7.所述任务代理器用于获取主设备的控制信息;

8.所述指令存储单元用于存储控制指令;

9.所述通用处理器用于根据所述主设备的控制信息以及所述控制指令形成控制信号;

10.所述通用控制代理器用于根据所述控制信号实现对于作为从设备的硬核或者软核的状态控制。

11.可选的,在所述的通用处理系统中,所述通用处理系统具有任务配置接口,所述任务代理器通过所述任务配置接口获取所述主设备的控制信息。

12.可选的,在所述的通用处理系统中,所述通用处理系统具有控制接口,所述通用控制代理器通过所述控制接口实现对于作为从设备的硬核或者软核的状态控制。

13.可选的,在所述的通用处理系统中,所述通用处理器具有任务接口,所述任务代理器获取的所述主设备的控制信息通过所述任务接口提供给所述通用处理器。

14.可选的,在所述的通用处理系统中,所述通用处理器具有外设接口,所述通用控制代理器通过所述外设接口从所述通用处理器获取所述控制信号。

15.可选的,在所述的通用处理系统中,所述主设备的控制信息包括指令地址信息,所述通用处理系统还包括指令接口代理器,所述指令接口代理器用于根据所述指令地址信息自所述指令存储单元中存储的控制指令中寻址到相应的控制指令并提供给所述通用处理器。

16.可选的,在所述的通用处理系统中,所述通用处理系统具有软核总线接口,所述指令存储单元存储的控制指令经由所述软核总线接口获取。

17.可选的,在所述的通用处理系统中,所述通用处理系统具有软核扩展指令接口,所述指令接口代理器还用于通过所述软核扩展指令接口从外部读取控制指令以提供给所述通用处理器。

18.可选的,在所述的通用处理系统中,所述通用处理器具有指令接口,所述指令接口代理器获取的所述控制指令通过所述指令接口提供给所述通用处理器。

19.可选的,在所述的通用处理系统中,所述通用处理系统还包括调试与中断代理器,所述调试与中断代理器用于读取所述通用处理器的运行信息以及用于中断所述通用处理器的运行状态。

20.可选的,在所述的通用处理系统中,所述通用处理器具有调试接口和中断接口,所述调试与中断代理器通过所述调试接口读取所述通用处理器的所述运行信息以及通过所述中断接口中断所述通用处理器的运行状态。

21.可选的,在所述的通用处理系统中,所述通用处理系统还包括硬件调度代理器,所述硬件调度代理器用于根据所述控制信号实现对于作为从设备的硬核或者软核的硬件调度。

22.可选的,在所述的通用处理系统中,所述通用处理系统具有硬件调度接口,所述硬件调度代理器通过所述硬件调度接口实现对于作为从设备的硬核或者软核的硬件调度。

23.可选的,在所述的通用处理系统中,所述通用处理系统还包括定时器,所述定时器用于根据所述控制信号进行定时控制。

24.相应的,本发明还提供一种通用处理方法,用于可编程半导体器件,所述可编程半导体器件包括硬核和软核,所述通用处理方法包括:

25.任务代理器获取主设备的控制信息并提供给通用处理器;

26.指令存储单元获取并存储控制指令;

27.所述通用处理器根据所述主设备的控制信息读取所述控制指令并形成控制信号,并将所述控制信号提供给所述通用控制代理器;以及

28.所述通用控制代理器根据所述控制信号实现对于作为从设备的硬核或者软核的状态控制。

29.在本发明提供的通用处理系统及通用处理方法中,通过主设备的控制信息经由通用处理器和通用控制代理器实现对于作为从设备的硬核或者软核的状态控制,即基于任务驱动实现了对于硬核的控制,由此使得对于可编程半导体器件中硬核的应用更加灵活了。

附图说明

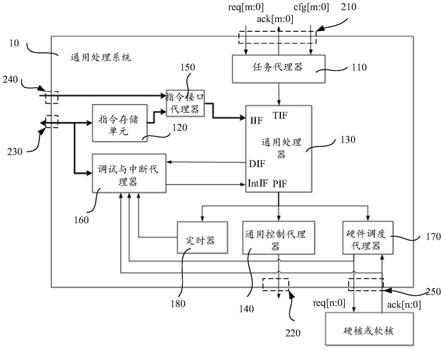

30.图1是本发明实施例的通用处理系统的一框结构示意图;

31.图2是本发明实施例的通用处理系统的另一框结构示意图;

32.图3是本发明实施例的通用处理方法的一流程示意图;

33.图4是本发明实施例的通用处理方法的另一流程示意图;

34.图5是本发明实施例的通用处理方法的另一流程示意图。

35.其中,附图标记说明如下:

36.10-通用处理系统;

37.110-任务代理器;120-指令存储单元;130-通用处理器;140-通用控制代理器;150-指令接口代理器;160-调试与中断代理器;170-硬件调度代理器;180-定时器;

38.210-任务配置接口;220-控制接口;230-软核总线接口;240-软核扩展指令接口;250-硬件调度接口;

39.tif-任务接口;pif-外设接口;iif-指令接口;dif-调试接口;intif-中断接口。

具体实施方式

40.以下结合附图和具体实施例对本发明提出的通用处理系统及通用处理方法作进一步详细说明。根据下面的说明,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。此外,附图所展示的结构往往是实际结构的一部分。特别的,各附图需要展示的侧重点不同,有时会采用不同的比例。

41.本技术实施例提供一种通用处理系统及通用处理方法,用于可编程半导体器件,在本技术实施例中,以用于可编程半导体器件中的现场可编程门阵列(fpga)为例。如图1所示,其为本发明实施例的通用处理系统的框结构示意图。如图1所示,在本技术实施例中,所述通用处理系统(general processor system)10包括:任务代理器(task agent)110、指令存储单元(instruction storage)120、通用处理器(general processor)130和通用控制代理器(general control agent)140。进一步的,如图2所示,所述通用处理系统10还包括指令接口代理器(iif agent)150、调试与中断代理器(debug and interrupt agent)160、硬件调度代理器(engines agent)170以及定时器(timer)180。

42.在本技术实施例中,所述通用处理器130具有任务接口tif、外设接口pif、指令接口iif、调试接口dif以及中断接口intif。具体的,所述通用处理器130通过所述任务接口tif与所述任务代理器110连接以进行信号传递,通过所述外设接口pif与所述通用控制代理器140、硬件调度代理器170以及定时器180信号连接,通过所述指令接口iif与所述指令接口代理器150信号连接,通过所述调试接口dif以及中断接口intif与所述调试与中断代理器160信号连接。

43.请继续参考图1和图2,所述通用处理系统10具有任务配置接口210、控制接口220、软核总线接口(bus if)230、软核扩展指令接口(optional extended interface)240以及硬件调度接口250。

44.具体的,所述任务配置接口210包括任务请求接口req[m:0]、任务应答接口ack[m:0]以及任务配置接口cfg[m:0]。在本技术实施例中,所述任务代理器110用于获取主设备的

控制信息,具体的,所述任务代理器110通过所述任务配置接口210获取所述主设备的控制信息。即所述主设备(图中未示出)通过所述任务配置接口210向所述任务代理器110发送控制信息。其中,所述主设备可以是上位机,其具体可以是一处理器或者一包括处理器的硬件设备等,本技术对此并不作限定。进一步的,所述主设备的数量可以为m个,其中,m为大于等于1的自然数,并且,优选的,所述m的取值与一相应的主设备对应。

[0045]

在本技术实施例中,当需要调用/调度可编程半导体器件(在此即fpga)中的软核或者硬核时,所述主设备即可通过所述任务请求接口req[m:0]以及所述任务配置接口cfg[m:0]向所述任务代理器110发送任务请求以及任务配置。在此,所述任务请求以及任务配置均作为所述主设备的控制信息。其中,所述任务配置可以包括指令地址信息以及主设备优先级等具体的控制信息,所述指令地址信息例如包括:指令指针的起始地址、指令长度、指令指针的结束地址等。

[0046]

在此,所述任务代理器110获取所述主设备的控制信息并记录相应的任务标志。在所述主设备为多个时,即多个所述主设备向所述任务代理器110发送任务请求以及任务配置时,所述任务代理器110可以根据所述主设备的优先级向所述通用处理器130发送控制信息(的全部或者部分),以启动所述通用处理器130形成控制信号。在此,所述任务代理器110通过所述任务接口tif向所述通用处理器130发送主设备的控制信息。

[0047]

在本技术实施例中,所述任务代理器110还用于完成所述主设备时钟域信号到所述通用处理器130所在的时钟域信号的同步处理过程,从而提高了所述通用处理系统10的可靠性。

[0048]

请继续参考图1和图2,在本技术实施例中,所述指令存储单元120用于存储控制指令。具体的,所述指令存储单元120通过所述软核总线接口230获取指令并进行存储。即在此,用户可以通过所述软核总线接口230配置所述通用处理器130执行所需的控制指令并存储于所述指令存储单元120中。在本技术实施例中,可以通过可编程半导体器件(在此即fpga)的软核配置所述指令存储单元120存储的控制指令,由此,可以灵活的配置所述通用处理器130形成的控制信号,相应的,可以灵活的配置、调用可编程半导体器件(在此即fpga)的硬核,并且可以兼顾可编程半导体器件(在此即fpga)的软核的配置与调用。

[0049]

进一步的,所述通用处理器130通过所述指令接口代理器150获取所述控制指令。具体的,所述指令接口代理器150根据所述指令地址信息自所述指令存储单元120中存储的所述控制指令中寻址到相应的控制指令并经由所述指令接口iif提供给所述通用处理器130。

[0050]

在本技术实施例中,所述指令接口代理器150还可以通过所述软核扩展指令接口240从外部读取控制指令以提供给所述通用处理器130。具体的,当所述指令存储单元120空间大小不满足存储所需的控制指令的数量时,可以通过所述软核扩展指令接口240直接从外部向所述指令接口代理器150提供控制指令,并经由所述指令接口代理器150提供给所述通用处理器130。由此,可以提供多种长度的控制指令,使得对于所述硬核和软核的应用更加灵活。

[0051]

其中,所述通用处理器130根据所述主设备的控制信息以及所述控制指令形成控制信号。所述控制信号具体可以包括:对硬核或者软核的状态控制的信号、对硬核或者软核的硬件调度的信号、定时控制的信号等。所述通用处理器130通过所述外设接口pif将所述

控制信号发送给所述通用控制代理器140、所述硬件调度代理器170或者所述定时器180。

[0052]

所述通用控制代理器140根据所述控制信号实现对于硬核或者软核的状态控制。具体的,通过所述控制信号,所述通用处理器130可以配置所述通用控制代理器140内的寄存器为0或者1,相应的,可以完成所述硬核或者软核的控制线状态的控制,即达到对于硬核或者软核的状态控制。其中,所述硬核或者软核的数量分别可以为多个,通过配置所述寄存器的数量以及所述控制信号的具体形式,可以实现对多个硬核以及多个软核的同时控制或者顺序控制。在本技术实施例中,所述通用控制代理器140通过所述控制接口220实现对于作为从设备的硬核或者软核的状态控制。在此,所述从设备与所述主设备相对应,所述主设备作为控制设备,所述从设备作为被控制设备,其中,所述主设备和所述从设备均可以为硬核或者软核。

[0053]

在所述通用控制代理器140根据所述控制信号完成了所述硬核或者软核的状态控制后,若完成了所述任务代理器110发送的主设备的控制信号,则相应的任务标志可以置为完成标志,其中,任务标志置为完成标志可以是特定的结束指令,也可以是将指令指针置为有效地址的最大值。

[0054]

在本技术实施例中,所述硬件调度代理器170根据所述控制信号实现对于作为从设备的硬核或者软核的硬件调度。具体的,所述硬件调度代理器170通过所述硬件调度接口250实现对于所述硬核调度的控制。其中,所述硬件调度接口250具体可以包括调度请求接口req[n:0]以及调度应答接口ack[n:0],n表示硬核数量,其取值为大于等于1的自然数,并且,优选的,所述n的取值与一相应的作为从设备的硬核对应。

[0055]

所述硬件调度代理器170通过所述外设接口pif接收到所述控制信号后,通过调度请求接口req[n:0]向相应的硬核发送调度请求,其中,当n取值为大于等于2时,可以实现多个硬核并行调度,提到了硬核调度的灵活性。相应的硬核根据所述调度请求的信号进行硬件调度,并且,相应的硬核在完成所述调度请求的信号后,通过所述调度应答接口ack[n:0]向所述硬件调度代理器170反馈调度完成的信号。由此,即可完成所述主设备的控制信号的一部分或者全部。若为完成了所述主设备控制信号的全部,则相应的任务标志可以置为完成标志。

[0056]

在本技术实施例中,所述定时器180根据所述控制信号进行定时控制。具体的,所述定时器180通过所述外设接口pif接收所述控制信号,并根据所述控制信号进行定时并等待定时结束。所述通过定时器180的定时控制,可以进一步实现对于硬核或者软核的配置,提高了所述硬核应用的灵活性。

[0057]

请继续参考图1和图2,所述通用处理系统10包括调试与中断代理器160,所述调试与中断代理器160可以读取所述通用处理器130的运行信息以及中断所述通用处理器130的运行状态。具体的,所述调试与中断代理器160通过所述调试接口dif读取所述通用处理器130的运行信息,或者说,所述通用处理器130通过所述调试接口dif将运行信息发送给所述调试与中断代理器160;所述调试与中断代理器160通过所述中断接口intif可以中断所述通用处理器130的运行状态。在本技术实施例中,所述调试与中断代理器160还用于实现可编程半导体器件(在此即fpga)软核时钟域信号到所述通用处理器130所在时钟域信号的同步处理过程,从而使得可编程半导体器件(在此即fpga)软核通过所述软核总线接口230对所述通用处理器130进行调试或者中断处理的可靠性提高。

[0058]

具体的,用户(或者说编程半导体器件(fpga)的软核)可以通过所述软核总线接口230经由所述调试与中断代理器160读取所述通用处理器130的运行信息。例如包括:所述通用处理器130所处理的指令的指针地址、所述通用处理器130当前处于运行或者等待的状态信息等。进一步的,通过所述调试与中断代理器160读取所述通用处理器130的运行信息还可以获取所述硬件调度代理器170中的调度请求状况,包括各硬核的调度处理及调度应答的情况。

[0059]

所述调试与中断代理器160通过所述中断接口intif可以中断所述通用处理器130的运行状态,由此,可以提高所述通用处理器130的运行效率与可靠性。其中,所述调试与中断代理器160的中断来源可以是可编程半导体器件(在此即fpga)的软核通过所述软核总线接口230发送的中断信息、可以是所述定时器180定时完成产生的中断信息、还可以是所述硬件调度代理器170完成硬核调度产生的中断信息。由此,可以在所述通用处理系统10的内部或者外部实现中断处理,使得对于硬核以及软核的调度、配置更加灵活。

[0060]

在本技术实施例中,通过所述任务代理器110以任务驱动的方式配置、调度所述硬核,使得对于可编程半导体器件(在此即fpga)的硬核的配置与调度更加灵活。进一步的,通过指令存储单元120以及指令接口代理器150经由所述软核总线接口230或者所述软核扩展指令接口240获取控制指令,使得控制指令更加的丰富,从而提高了对于可编程半导体器件(在此即fpga)的硬核以及软核的配置与调度的灵活性。更进一步的,通过所述调试与中断代理器160能够方便的获取所述通用处理器130的运行状态以及通过外设接口pif与所述通用处理器130信号连接的各部件的状态,从而能够据此更好的实现对于硬核以及软核的配置。此外,通过所述调试与中断代理器160对所述通用处理器130进行各种中断处理,可以控制所述通用处理器130的运行进程,从而使得整个系统的配置与使用更加可控、可测以及灵活。

[0061]

相应的,本发明实施例还提供一种所述通用处理系统的通用处理方法,请参考图3至图5,其为本发明实施例的通用处理方法的流程示意图。如图3所示,所述通用处理方法具体包括:

[0062]

步骤s310:任务代理器获取主设备的控制信息并提供给通用处理器;

[0063]

步骤s320:指令存储单元获取并存储控制指令;

[0064]

步骤s330:所述通用处理器根据所述主设备的控制信息读取所述控制指令并形成控制信号,并将所述控制信号提供给所述通用控制代理器;以及

[0065]

步骤s340:所述通用控制代理器根据所述控制信号实现对于作为从设备的硬核或者软核的状态控制。

[0066]

在本技术实施例中,所述步骤s310和所述步骤s320可以同时执行(如图4所示),也可以先执行所述步骤s310再执行所述步骤s320,或者先执行所述步骤s320再执行所述步骤s310。其中,所述步骤s310和所述步骤s320先于所述步骤s330执行,所述步骤s330先于所述步骤s340执行。

[0067]

进一步的,如图5所示,所述通用处理方法还可以包括:

[0068]

步骤s350:所述硬件调度代理器根据所述控制信号实现对于作为从设备的硬核或者软核的硬件调度;

[0069]

步骤s360:所述定时器根据所述控制信号进行定时控制;以及

[0070]

步骤s370:所述调试与中断代理器读取所述通用处理器的运行信息和/或中断所述通用处理器的运行状态。

[0071]

其中,所述通用处理方法可以包括所述步骤s350、所述步骤s360以及所述步骤s370中的一个步骤或者多个步骤。进一步的,本技术并不对所述步骤s350、所述步骤s360以及所述步骤s370之间的顺序进行限定,所述步骤s350、所述步骤s360以及所述步骤s370可以同时执行,也可以先执行所述步骤s370,再执行所述步骤s350以及所述步骤s360,也可以是按照所述步骤s350、所述步骤s360以及所述步骤s370的顺序依次执行,等等。进一步的,所述步骤s370还可以在所述步骤s330之前执行或者在所述步骤s330和步骤s340之间执行,本技术对此不作限定。

[0072]

所述任务代理器、所述通用处理器、所述指令存储单元、所述通用控制代理器、所述指令接口代理器、所述调试与中断代理器、所述硬件调度代理器以及所述定时器的具体工作方式可以参考前述对于通用处理系统的描述,本技术对此不再赘述。

[0073]

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。