mos管控制电路及装置

技术领域

1.本实用新型属于电子电路技术领域,尤其涉及一种mos管控制电路及装置。

背景技术:

2.mos管,是mosfet的缩写,mosfet是一种金属

‑

氧化物半导体场效应晶体管,简称金氧半场效晶体管(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,mosfet)。在电路中通常会使用mos管作为开关管以控制电路的通断,其原理是利用mos管栅极控制mos管源极和漏极通断的原理,从而构造开关电路。mos管包括n沟道mos管和p沟道mos管,其中,p沟道mos管的特性,vgs小于一定的值就会导通,适合用于源极接vcc时的情况,vgs指的是栅极g与源极s的电压,即栅极低于电源一定电压就导通。而n沟道mos管的特性,vgs大于一定的值就会导通,适合用于源极接地时的情况,只要栅极电压大于参数手册中给定的vgs就可以了,漏极d接电源,源极s接地。

3.在电池管理系统(bms)中,存在需要多种方式来控制充放电mos管的情况,但是现有mos管控制往往是mcu输出控制信号至mos管实现对mos管进行控制,方式比较单一,无法随时控制mos管的通断,例如当mcu出现故障失效后无法关断mos管,导致mos管控制不灵活不方便。

技术实现要素:

4.本实用新型提供一种mos管控制电路,旨在解决现有的mos管控制方式单一的问题。

5.本实用新型是这样实现的,一种mos管控制电路,包括:

6.电平转换模块,与至少两个控制信号端连接,用于分别接收至少两个控制信号端输入的控制信号并转换成预设电压值的电平信号;

7.门逻辑模块,与电平转换模块的输出端连接,用于接收电平转换模块输出的至少两个电平信号并进行逻辑与运算生成驱动控制信号;

8.驱动模块,与门逻辑模块的输出端连接,驱动模块的输出端与目标mos管的控制端连接。

9.更进一步地,电平转换模块包括采集端转换单元和控制芯片信号单元,至少两个控制信号端包括第一控制信号端和第二控制信号端,采集端转换单元的输入端与第一控制信号端连接,采集端转换单元的输出端与门逻辑模块的第一输入端连接;控制芯片信号单元的输入端与第二控制信号端连接,控制芯片信号单元的输出端与门逻辑模块的第二输入端连接。

10.更进一步地,采集端转换单元包括一端连接至第一控制信号端的第一电阻r1,第一电阻r1的另一端连接至第一稳压二极管z1的阴极,第一稳压二极管z1的阳极接地,第一稳压二极管z1与第二电阻r2并联,第一电阻r1的另一端还连接至第一场效应管q1的栅极,第一场效应管q1的源极接地,第一场效应管q1的漏极通过第三电阻r3连接至内部电压端

vdd,第一场效应管q1的漏极还连接至第二场效应管q2的栅极,第二场效应管q2的源极连接至内部电压端vdd,第二场效应管q2的漏极依次通过第四电阻r4和第五电阻r5接地,第四电阻r4与第五电阻r5连接的一端还连接至采集信号输出端a_dsg,采集信号输出端a_dsg与第一输入端连接;控制芯片信号单元包括mcu,mcu的信号输入端与第二控制信号端连接,mcu的mcu信号输出端m_dsg与第二输入端连接。

11.更进一步地,电平转换模块还包括控制器信号转换单元以及开关信号转换单元,至少两个控制信号端还包括第三控制信号端和第四控制信号端,控制器信号转换单元的输入端与第三控制信号端连接,控制器信号转换单元的输出端与门逻辑模块的第三输入端连接;开关信号转换单元的输入端与第四控制信号端连接,开关信号转换单元的输出端与门逻辑模块的第四输入端连接。

12.更进一步地,控制器信号转换单元包括一端连接至第三控制信号端的第六电阻r6,第六电阻r6的另一端连接至光耦合器的第一输入端,光耦合器的第二输入端接地,光耦合器的第一输出端连接至内部电压端vdd,光耦合器的第二输出端通过第七电阻r7接地,光耦合器的第二输出端连接至控制器信号输出端ctrl,控制器信号输出端ctrl与第三输入端连接。

13.更进一步地,开关信号转换单元包括一端与第四控制信号端连接的开关器s1,开关器s1的另一端通过第八电阻r8连接至第二稳压二极管z2的阴极,第二稳压二极管z2的阳极接地,第二稳压二极管z2与第九电阻r9并联,第二稳压二极管z2的阴极还连接至第三场效应管q3的栅极,第三场效应管q3的源极接地,第三场效应管q3的漏极通过第十电阻r10连接至内部电压端vdd,第三场效应管q3的漏极还连接至第四场效应管q4的栅极,第四场效应管q4的源极连接至内部电压端vdd,第四场效应管q4的漏极依次通过第十一电阻r11和第十二电阻r12接地,第十一电阻r11与第十二电阻r12连接的一端还连接至开关信号输出端sw,开关信号输出端sw与第四输入端连接。

14.更进一步地,门逻辑模块包括第一门逻辑芯片u1,第一门逻辑芯片u1的第一管脚作为第一输入端与采集信号输出端a_dsg连接,第一门逻辑芯片u1的第二管脚作为第二输入端与mcu信号输出端m_dsg连接,第一门逻辑芯片u1的第三管脚接地,第一门逻辑芯片u1的第四管脚与驱动模块的输入端连接,第一门逻辑芯片u1的第五管脚连接至内部电压端vdd,第一门逻辑芯片u1的第五管脚还通过第一电容c1接地。

15.更进一步地,门逻辑模块包括第二门逻辑芯片u2和第三门逻辑芯片u3,第二门逻辑芯片u2的第一管脚作为第三输入端与控制器信号输出端ctrl连接,第二门逻辑芯片u2的第二管脚作为第四输入端与开关信号输出端sw连接,第二门逻辑芯片u2的第三管脚接地,第二门逻辑芯片u2的第五管脚连接至内部电压端vdd,第二门逻辑芯片u2的第五管脚还通过第二电容c2接地;第三门逻辑芯片u3的第一管脚与第一门逻辑芯片u1的第四管脚连接,第三门逻辑芯片u3的第二管脚与第二门逻辑芯片u2的第四管脚连接,第三门逻辑芯片u3的第三管脚接地,第三门逻辑芯片u3的第四管脚与驱动模块的输入端连接,第三门逻辑芯片u3的第五管脚连接至内部电压端vdd,第三门逻辑芯片u3的第五管脚还通过第三电容c3接地。

16.更进一步地,驱动模块包括第十三电阻r13,第十三电阻r13的一端作为驱动模块的输入端与门逻辑模块的输出端连接,第十三电阻r13的另一端连接至第五场效应管q5的

栅极,第五场效应管q5的源极接地,第五场效应管q5的栅极和源极之间连接有第十四电阻r14,第五场效应管q5的漏极依次通过第十五电阻r15和第十六电阻r16连接至第一电压端vae,第一电压端vae还连接至三极管q6的发射极,三极管q6的基极连接至第十五电阻r15和第十六电阻r16之间的线路上,三极管q6的集电极连接至二极管d1的阳极,二极管d1的阴极通过第十七电阻r17连接至驱动信号输出端dsg_mos,驱动信号输出端dsg_mos用于与目标mos管的控制端连接。

17.更进一步地,驱动模块还包括第十八电阻r18,第十八电阻r18的一端作为驱动模块的输入端与门逻辑模块的输出端连接,第十八电阻r18的另一端连接至第六场效应管q7的栅极,第六场效应管q7的源极接地,第六场效应管q7的栅极和源极之间连接有第十九电阻r19,第六场效应管q7的漏极连接至第七场效应管q8的栅极,第七场效应管q8的栅极还通过第二十电阻r20连接至第一电压端vae,第七场效应管q8的源极接地,第七场效应管q8的栅极和源极之间连接有第二十一电阻r21,第七场效应管q8的漏极通过第二十二电阻r22连接至驱动信号输出端dsg_mos,驱动信号输出端dsg_mos还分别通过第二十三电阻r23和第四电容c4接地,驱动信号输出端dsg_mos还连接至第三稳压二极管z3的阴极,第三稳压二极管z3的阳极接地。

18.更进一步地,驱动模块还包括第五电容c5,第一电压端vae通过第五电容c5接地。

19.第二方面,本技术还提供一种mos管控制装置,包括目标mos管以及如上述的mos管控制电路,目标mos管的控制端与mos管控制电路的驱动模块的输出端连接。

20.本实用新型实施例通过设置电平转换模块,电平转换模块用于将至少两路控制信号端输入的控制信号转换为预设电压值的电平信号,并将该电平信号输出至门逻辑模块,门逻辑模块用于根据接收到的多个电平信号进行逻辑与运算生成驱动控制信号并输出至驱动模块,驱动模块用于通过驱动控制信号控制目标mos管的通断,由于至少两个电平信号经过逻辑与运算后控制目标mos管,所以当其中一种控制方式失效时,可以通过其他控制方式控制mos管的通断,提高mos管控制的灵活性。

附图说明

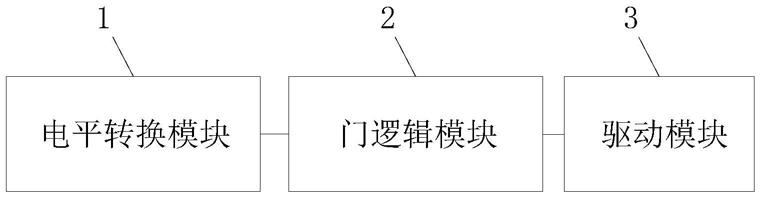

21.图1是本实用新型提供的mos控制电路的模块示意图;

22.图2是本实用新型提供的电平转换模块一个实施例的单元结构示意图;

23.图3是本实用新型提供的一个实施例的mos控制电路的电路结构示意图;

24.图4是本实用新型提供的电平转换模块另一个实施例的单元结构示意图;

25.图5是本实用新型提供的另一个实施例的mos控制电路的电路结构示意图。

具体实施方式

26.为了使本实用新型的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本实用新型进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本实用新型,并不用于限定本实用新型。

27.现有的mos管控制方式通常由mcu控制实现,当mcu出现故障时,无法及时控制mos管关断,控制方式单一不灵活。本技术通过多种控制方式组合控制mos管的通断,当其中一种控制方式出现故障失效时,可以通过其他控制方式实现mos管的控制,提高mos管控制的

灵活性。

28.实施例一

29.在一些可选实施例中,请参阅图1,图1是本技术一个实施例控制电路的模块示意图。

30.如图1所示,本技术提供一种mos管控制电路,包括电平转换模块1、门逻辑模块2和驱动模块3。

31.电平转换模块1与至少两个控制信号端连接,用于分别接收至少两个控制信号端输入的控制信号并转换成预设电压值的电平信号;门逻辑模块2与电平转换模块1的输出端连接,用于接收电平转换模块输出的至少两个电平信号并进行逻辑与运算生成驱动控制信号;驱动模块3与门逻辑模块2的输出端连接,驱动模块3的输出端与目标mos管的控制端连接。

32.在实施时,电平转换模块1与至少两个控制信号端连接,其中,控制信号端用于输出控制信号,不同的控制信号端输出的控制信号的电平值不同,通过电平转换模块1将各个控制信号转换为统一电压值的电平信号,例如将控制信号统一转换成ttl电平信号,ttl电平信号是ttl器件的电平,其包含了高电平和低电平的范围,在具体实施时,ttl电平信号规定, 5v等价于逻辑“1”,0v等价于逻辑“0”(采用二进制来表示数据时)。这样的数据通信及电平规定方式,被称做ttl(晶体管

‑

晶体管逻辑电平)信号。

33.门逻辑模块2接收电平转换模块1输出的多个电平信号进行逻辑与运算生成驱动控制信号,在一些实施例中,以门逻辑模块2接收两路电平信号为例,分别为对应一个控制信号端的第一电平信号和对应另一个控制信号端的第二电平信号,门逻辑模块2将第一电平信号和第二电平信号进行与运算生成驱动控制信号,并将驱动控制信号输出至驱动模块3,驱动模块3的输出端与目标mos管的控制端连接,mos管是一种金属氧化物半导体场效应晶体管,mos管共有g、d、s三个脚,其中,g、d、s三个脚分别表示mos管的栅极、漏极和源极,目标mos管的控制端是mos管的栅极,通过驱动模块3根据驱动控制信号控制目标mos管的控制端的电平。例如控制信号端为mcu输出的5v高电平信号,另一个控制信号端为电源端输出的3.3v电源电压信号,电平转换模块1可以将mcu输出的5v高电平信号和3.3v电源电压信号统一转换成3v的电平信号,在门逻辑模块2中,3v等价于逻辑“1”,而0v等价于逻辑“0”,则门逻辑模块2接收到的两个等价于逻辑“1”的电平信号,然后根据该电平信号进行与运算生成驱动控制信号后输出至驱动模块3,驱动模块3控制mos管持续导通,以mos管为pmos(p沟道mos管)管为例,驱动模块3的输出端连接pmos管的栅极,当驱动模块3输出高电平至pmos管使pmos管的vgs小于导通阈值时,pmos管持续导通;当mcu故障时,mcu持续输出5v高电平信号导致mcu无法自主关断mos管,此时,若想要关闭mos管,可以通过断开3.3v电源电压信号,使另一个控制信号端为0v,此时电平转换模块1接收到5v和0v这两路控制信号,然后输出两路电平信号分别为3v和0v,即门逻辑模块2接收到其中一个电平信号等价于逻辑“1”,而另一个电平信号等价于逻辑“0”,门逻辑模块2根据这两个电平信号进行逻辑与运算生成驱动控制信号输出至驱动模块3,驱动模块3根据该驱动控制信号控制mos管不导通,还是以上述的pmos为例,驱动模块3输出低电平至pmos管截止,实现对目标mos管的灵活控制。

34.本技术实施例通过设置电平转换模块1,电平转换模块1用于将至少两路控制信号端输入的控制信号转换为预设电压值的电平信号,并将电平信号输出至门逻辑模块2,门逻

辑模块2用于根据多个电平信号进行逻辑与运算生成驱动控制信号并输出至驱动模块3,驱动模块3用于通过驱动控制信号控制目标mos管的通断,由于至少两个控制信号经过门逻辑与运算后控制目标mos管,当其中一种控制方式失效时,可以通过其他控制方式控制mos管的通断,提高mos管控制的灵活性。

35.实施例二

36.在一些可选实施例中,请参阅图2,图2是本技术一个实施例电平转换模块的单元结构示意图。

37.如图2所示,电平转换模块1包括采集端转换单元11和控制芯片信号单元12,至少两个控制信号端包括第一控制信号端和第二控制信号端,采集端转换单元11的输入端与第一控制信号端连接,采集端转换单元11的输出端与门逻辑模块2的第一输入端连接;控制芯片信号单元12的输入端与第二控制信号端连接,控制芯片信号单元12的输出端与门逻辑模块2的第二输入端连接。

38.在实施时,请参阅图3,图3是本技术一个实施例的电路结构示意图。

39.如图3所示,采集端转换单元11包括一端连接至采集信号端dsg_d的第一电阻r1,采集信号端dsg_d即第一控制信号端,第一电阻r1的另一端连接至第一稳压二极管z1的阴极,第一稳压二极管z1的阳极接地,第一稳压二极管z1与第二电阻r2并联,第一电阻r1的另一端还连接至第一场效应管q1的栅极,第一场效应管q1的源极接地,第一场效应管q1的漏极通过第三电阻r3连接至内部电压端vdd,第一场效应管q1的漏极还连接至第二场效应管q2的栅极,第二场效应管q2的源极连接至内部电压端vdd,第二场效应管q2的漏极依次通过第四电阻r4和第五电阻r5接地,第四电阻r4与第五电阻r5连接的一端还连接至采集信号输出端a_dsg,采集信号输出端a_dsg与门逻辑模块2的第一输入端连接;控制芯片信号单元12包括mcu,mcu的信号输入端与第二控制信号端连接,mcu的mcu信号输出端m_dsg与第二输入端连接。

40.在实施时,采集信号端dsg_d输入采集信号,例如采集信号端dsg_d连接温度传感器或者湿度传感器,从而接收温度传感器或者湿度传感器采集到的温度或湿度采集信号,当采集信号端dsg_d为高电平时,第一场效应管q1导通进而第二场效应管q2导通,采集信号输出端a_dsg输出内部电压端vdd的电压至门逻辑模块2的第一输入端,内部电压端vdd是电路的工作电压,由于温度传感器或者湿度传感器的输出电信号电平不一致,通过采集端转换单元即可输出统一电平信号的控制信号,mcu根据第二控制信号端的控制信号通过mcu信号输出端输出控制信号至门逻辑模块2的第二输入端,在一些实施例中,mcu可以不连接第二控制信号端而直接定时或者自主触发输出控制信号至门逻辑模块2的第二输入端,mcu输出的控制信号与内部电压端vdd的电平一致,从而便于门逻辑模块2进行逻辑与运算生成驱动控制信号。

41.实施例三

42.在一些实施例中,本技术提供的mos管控制电路的门逻辑模块2包括第一门逻辑芯片u1,第一门逻辑芯片u1的第一管脚作为第一输入端与采集信号输出端a_dsg连接,第一门逻辑芯片u1的第二管脚作为第二输入端与mcu信号输出端m_dsg连接,第一门逻辑芯片u1的第三管脚接地,第一门逻辑芯片u1的第四管脚与驱动模块3的输入端连接,第一门逻辑芯片u1的第五管脚连接至内部电压端vdd,第一门逻辑芯片u1的第五管脚还通过第一电容c1接

地。

43.第一门逻辑芯片u1的第一输入端和第二输入端分别接采集信号输出端a_dsg和mcu信号输出端m_dsg,第一门逻辑芯片u1采用能实现基本逻辑与运算的硬件电路芯片,以第一门逻辑芯片u1为与门逻辑为例,例如第一门逻辑芯片u1的型号为sn74ahc1g08,sn74ahc1g08是一种两路输入信号与门运算的逻辑芯片,sn74ahc1g08的输入电压范围为

‑

0.5v

‑

7v,则可以将预设电压值设置为

‑

0.5v

‑

7v之间,例如将至少两路控制信号统一转换成电压值为2v的电平信号后输出至sn74ahc1g08芯片,以满足sn74ahc1g08芯片的运算要求。以电平转换模块1输出两路电平信号为例,sn74ahc1g08芯片的第一输入端与电平转换模块1的一个输出端连接,用于接收一路电平信号,sn74ahc1g08芯片的第二输入端与电平转换模块1的另一个输出端连接,用于接收另一路电平信号,sn74ahc1g08芯片的第四管脚输出驱动控制信号dsg至驱动模块3的输入端,进而通过驱动模块3控制目标mos管的通断。

44.实施例四

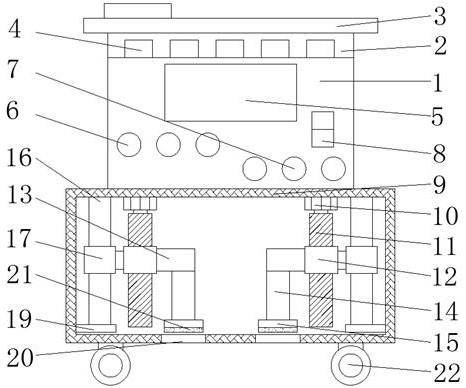

45.在一些可选实施例中,请参阅图4,图4是本技术又一个实施例电平转换模块的单元结构示意图。

46.如图4所示,电平转换模块1还包括控制器信号转换单元13以及开关信号转换单元14,至少两个控制信号端还包括第三控制信号端和第四控制信号端,控制器信号转换单元13的输入端与第三控制信号端连接,控制器信号转换单元13的输出端与门逻辑模块2的第三输入端连接;开关信号转换单元14的输入端与第四控制信号端连接,开关信号转换单元14的输出端与门逻辑模块2的第四输入端连接。

47.在实施时,请参阅图5,图5是本技术一个实施例的电路结构示意图。

48.如图5所示,控制器信号转换单元13包括一端连接至控制器信号端control的第六电阻r6,控制器信号端control即第三控制信号端,第六电阻r6的另一端连接至光耦合器的第一输入端,光耦合器的第二输入端接地,光耦合器的第一输出端连接至内部电压端vdd,光耦合器的第二输出端通过第七电阻r7接地,光耦合器的第二输出端连接至控制器信号输出端ctrl,控制器信号输出端ctrl与门逻辑模块2的第三输入端连接。

49.在一些可选实施例中,本技术提供的mos管控制电路的开关信号转换单元14包括一端与外部电压端vcc连接的开关器s1,外部电压端vcc即第四控制信号端,开关器s1的另一端通过第八电阻r8连接至第二稳压二极管z2的阴极,第二稳压二极管z2的阳极接地,第二稳压二极管z2与第九电阻r9并联,第二稳压二极管z2的阴极还连接至第三场效应管q3的栅极,第三场效应管q3的源极接地,第三场效应管q3的漏极通过第十电阻r10连接至内部电压端vdd,第三场效应管q3的漏极还连接至第四场效应管q4的栅极,第四场效应管q4的源极连接至内部电压端vdd,第四场效应管q4的漏极依次通过第十一电阻r11和第十二电阻r12接地,第十一电阻r11与第十二电阻r12连接的一端还连接至开关信号输出端sw,开关信号输出端sw与门逻辑模块2的第四输入端连接。

50.在一些可选实施例中,本技术提供的mos管控制电路的门逻辑模块2包括第二门逻辑芯片u2和第三门逻辑芯片u3,第二门逻辑芯片u2的第一管脚作为第三输入端与控制器信号输出端ctrl连接,第二门逻辑芯片u2的第二管脚作为第四输入端与开关信号输出端sw连接,第二门逻辑芯片u2的第三管脚接地,第二门逻辑芯片u2的第五管脚连接至内部电压端vdd,第二门逻辑芯片u2的第五管脚还通过第二电容c2接地,第三门逻辑芯片u3的第一管脚

与第一门逻辑芯片u1的第四管脚连接,第三门逻辑芯片u3的第二管脚与第二门逻辑芯片u2的第四管脚连接,第三门逻辑芯片u3的第三管脚接地,第三门逻辑芯片u3的第四管脚与驱动模块3的输入端连接,第三门逻辑芯片u3的第五管脚连接至内部电压端vdd,第三门逻辑芯片u3的第五管脚还通过第三电容c3接地。

51.第一门逻辑芯片u1用于对采集信号输出端a_dsg输出的控制信号和mcu信号输出端m_dsg输出的控制信号进行逻辑与运算后输出第一驱动控制信号dsg1至第三门逻辑芯片u3的第一管脚,第二门逻辑芯片u2用于对控制器信号输出端ctrl输出的控制信号和开关信号输出端sw输出的控制信号进行逻辑与运算后输出第二驱动控制信号dsg2至第三门逻辑芯片u3的第二管脚,由第三门逻辑芯片u3对第一驱动控制信号dsg1和第二驱动控制信号dsg2进行逻辑与运算生成驱动控制信号dsg并输出至驱动模块3的输入端。

52.实施例五

53.在一些可选实施例中,本技术提供的mos管控制电路的驱动模块3包括第十三电阻r13,第十三电阻r13的一端作为驱动模块3的输入端与门逻辑模块2的输出端连接,第十三电阻r13的另一端连接至第五场效应管q5的栅极,第五场效应管q5的源极接地,第五场效应管q5的栅极和源极之间连接有第十四电阻r14,第五场效应管q5的漏极依次通过第十五电阻r15和第十六电阻r16连接至第一电压端vae,第一电压端vae还连接至三极管q6的发射极,三极管q6的基极连接至第十五电阻r15和第十六电阻r16之间的线路上,三极管q6的集电极连接至二极管d1的阳极,二极管d1的阴极通过第十七电阻r17连接至驱动信号输出端dsg_mos,驱动信号输出端dsg_mos用于与目标mos管的控制端连接。

54.在实施时,当门逻辑模块2输出的驱动控制信号为高电平时,第五场效应管q5导通使得三极管q6导通,第一电压端vae依次经过三极管q6、二极管d1和第十七电阻r17输出电压至驱动信号输出端dsg_mos,从而实现控制mos管的功能。

55.实施例六

56.在一些可选实施例中,本技术提供的mos管控制电路的驱动模块3还包括第十八电阻r18,第十八电阻r18的一端作为驱动模块3的输入端与门逻辑模块2的输出端连接,第十八电阻r18的另一端连接至第六场效应管q7的栅极,第六场效应管q7的源极接地,第六场效应管q7的栅极和源极之间连接有第十九电阻r19,第六场效应管q7的漏极连接至第七场效应管q8的栅极,第七场效应管q8的栅极还通过第二十电阻r20连接至第一电压端vae,第七场效应管q8的源极接地,第七场效应管q8的栅极和源极之间连接有第二十一电阻r21,第七场效应管q8的漏极通过第二十二电阻r22连接至驱动信号输出端dsg_mos,当门逻辑模块2输出的驱动控制信号dsg为高电平时,第五场效应管q5导通,使得三极管q6导通,而第六场效应管q7导通使得第七场效应管q8不导通,驱动信号输出端dsg_mos输出高电平信号至目标mos管的栅极,控制mos管持续导通;当门逻辑模块2输出的驱动控制信号dsg为低电平时,第五场效应管q5不导通,使得三极管q6不导通,而第六场效应管q7不导通使得第七场效应管q8导通,将驱动信号输出端dsg_mos拉至低电平,目标mos管不导通,对电路进行泄放作用,避免电路因电源脱开而造成电路中元器件损坏。另外,驱动信号输出端dsg_mos还分别通过第二十三电阻r23和第四电容c4接地,驱动信号输出端dsg_mos还连接至第三稳压二极管z3的阴极,第三稳压二极管z3的阳极接地,第三稳压二极管z3能保持驱动信号输出端dsg_mos的电压的稳定,当驱动信号输出端dsg_mos输出高电平时,对第四电容c4进行充电,

而当驱动信号输出端dsg_mos输出低电平时,第四电容c4通过第二十三电阻23进行放电,能有效过滤电压接入时产生的波峰,降低电压波动,提供电路稳定性。

57.在实施时,驱动模块3还包括第五电容c5,第一电压端vae通过第五电容c5接地。第五电容c5对电源进行滤波作用,减少对电路的干扰。

58.实施例七

59.在一些可选实施例中,本技术还提供一种mos管控制装置,包括目标mos管以及如上述的mos管控制电路,目标mos管的控制端与mos管控制电路的驱动模块3的输出端连接。mos管控制电路包括电平转换模块1、门逻辑模块2和驱动模块3,电平转换模块1用于将至少两路控制信号端输入的控制信号转换为预设电压值的电平信号,并将电平信号输出至门逻辑模块2,门逻辑模块2用于根据多个电平信号进行逻辑与运算生成驱动控制信号并输出至驱动模块3,驱动模块3用于通过驱动控制信号控制目标mos管的通断,由于至少两个控制信号经过门逻辑与运算后控制目标mos管,所以对mos管的控制方式多种多样,实现多种方式组合控制mos管的通断,灵活对mos管进行控制。

60.以上所述仅为本实用新型的较佳实施例而已,并不用以限制本实用新型,凡在本实用新型的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本实用新型的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。