1.本技术涉及光学逻辑元件技术领域,特别涉及一种光电数字逻辑运算的光学逻辑元件及其逻辑运算方法。

背景技术:

2.在以数据驱动的新工业革命时代,算力是第一生产力,目前随着人工智能技术的发展,相应的人工智能算法变得越来越复杂。目前传统微纳电子芯片上的器件密度和尺寸已趋近物理极限,功耗和算力也面临瓶颈。光电计算充分利用光在算力和能耗上的双重优势,有潜力解决目前大规模计算所面临的算力和功耗瓶颈。光电智能芯片能够在智慧城市、智能交通、智能安防、云计算和数据中心以及国防等多个领域带来算力和规模性能三个数量级以上的提升。

3.光电数字逻辑运算芯片是实现光电智能计算的重要组件,目前有多种实现路径:光学数字逻辑门可以通过半导体光放大器、周期极化铌酸锂波导、电吸收调制器等非线性器件实现,但其单位计算能耗、噪声等性能尚不理想,且集成潜力有限;在集成光学计算方面,国际上的代表性工作主要包括基于硅光的光学干涉网络阵列实现矩阵数值计算、光学相变材料阵列实现存算一体构架等,类似工作实现了部分简单的光学计算,但目前的硅光方案存在参数规模低,模型构架较为简单等问题;基于空间光学的光电傅里叶域卷积神经网络实现了高通量的光学计算,但系统调制速率受限,误差难以校正。相关技术中缺少一种可以进行大规模运算、且调制速率高的逻辑运算器件,亟待解决。

技术实现要素:

4.本技术提供一种光电数字逻辑运算的光学逻辑元件及其逻辑运算方法,通过人工智能方法实现高速的光电逻辑计算芯片,提供了一种运算规模大,调制速率高,且可以进行不同运算逻辑的逻辑元件。

5.本技术第一方面实施例提供一种光电数字逻辑运算的光学逻辑元件,包括以下:驱动件,用于为光电集成件提供驱动,产生所述光电集成件能够识别的数字调制信息以及读取所述光电集成件输出的电信号;所述光电集成件,用于利用相干光信号搭载所述驱动件输入的所述数字调制信息,并在预设光学衍射神经网络中对所述相干光信号进行数字逻辑运算,得到运算结果,并将所述运算结果基于数字逻辑映射关系生成电信号,并利用所述驱动件读取所述电信号后输出所述运算结果。

6.根据本技术的实施例,所述光电集成件包括:激光器,用于基于所述驱动件发送的第一驱动信号生成所述相干光信号;分光器件,用于将所述相干光信号分束成至少一束相干光信号;调制器组,用于将所述数字调制信息加载到所述至少一束相干光信号上,得到加载所述数字调制信息的相干光信号;微纳光学衍射线阵列,用于由阵列产生的所述预设光学衍射神经网络对所述相干光信号进行数字逻辑运算,输出所述运算结果;探测器阵列,用于根据所述运算结果生成所述电信号。

7.根据本技术的实施例,所述分光器件包括:波导,用于引导所述相干光信号;分束器,用于将引导的相干光信号进行分束。

8.根据本技术的实施例,所述微纳光学衍射线阵列的阵列结构由所述预设光学衍射神经网络对应的数字逻辑运算功能确定。

9.根据本技术的实施例,所述阵列结构通过衍射线数量、衍射线间的间距、每条衍射线的厚度、每条衍射线的宽度、每条衍射线的长度和由每条衍射线的厚度、宽度、长度的均方根粗糙度中的一项或多项进行调整。

10.根据本技术的实施例,所述驱动件包括:第一驱动子件,用于生成驱动所述激光器产生所述相干光信号的第一驱动信号;第二驱动子件,用于生成驱动所述调制器组加载所述数字调制信息的第二驱动信号;第三驱动子件,用于生成驱动所述探测器阵列产生所述电信号的第三驱动信号;读取子件,用于从所述探测器阵列中读取所述电信号,并基于所述电信号输出所述运算结果。

11.根据本技术的实施例,所述调制器组中调制器的数量为至少一个。

12.根据本技术的实施例,所述驱动件与所述光电集成件集成设置。

13.根据本技术的实施例,所述光电集成件加载所述数字调制信息的加载时序包括同步与异步。

14.本技术第二方面实施例提供一种光电数字逻辑运算方法,采用上述实施例中的光电数字逻辑运算的光学逻辑元件,包括以下步骤:确定所述数字调制信息;驱动所述数字调制信息加载至所述相干光信号,得到加载所述数字调制信息的相干光信号;在所述预设光学衍射神经网络中对所述相干光信号进行数字逻辑运算,得到所述运算结果,并将所述运算结果基于所述数字逻辑映射关系生成所述电信号,并根据所述电信号输出所述运算结果。

15.本技术实施例的光电数字逻辑运算的光学逻辑元件及其逻辑运算方法,通过驱动件确定数字调制信息,并驱动数字调制信息加载至光电集成件生成的相干光信号上,光电集成件利用预设光学衍射神经网络中对调制后的相干光信号进行数字逻辑运算,得到运算结果,并将运算结果基于数字逻辑映射关系生成电信号,并利用驱动件读取电信号后输出运算结果,从而实现混合集成的光电逻辑计算,具有更高的单位能耗计算性能(flops/j),可以重构、批量地设计不同的专用逻辑运算,运算规模大,调制速率高。

16.本技术附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本技术的实践了解到。

附图说明

17.本技术上述的和/或附加的方面和优点从下面结合附图对实施例的描述中将变得明显和容易理解,其中:图1为根据本技术实施例提供的一种光电数字逻辑运算的光学逻辑元件结构示意图;图2为根据本技术实施例提供的一种具体地光电数字逻辑运算的光学逻辑元件结构示意图;图3为根据本技术实施例提供的一种光电集成件的俯视结构示意图;

图4为根据本技术实施例提供的一种光电集成件的三维侧视结构示意图;图5为根据本技术实施例提供的另一种具体地光电数字逻辑运算的光学逻辑元件结构示意图;图6为根据本技术实施例提供的一种光电数字逻辑运算方法流程图。

18.附图标记:100

‑

驱动件,101

‑

第一驱动子件,102

‑

第二驱动子件,103

‑

第三驱动子件,104

‑

读取子件,200

‑

光电集成件,201

‑

激光器,202

‑

分光器件,203

‑

调制器组,204

‑

微纳光学衍射线阵列,205

‑

探测器阵列。

具体实施方式

19.下面详细描述本技术的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本技术,而不能理解为对本技术的限制。

20.下面参考附图描述本技术实施例的光电数字逻辑运算的光学逻辑元件及其逻辑运算方法。针对上述背景技术中心提到的缺少一种可以进行大规模运算、且调制速率高的逻辑运算器件的问题,本技术提供了一种光电数字逻辑运算的光学逻辑元件及其逻辑运算方法,通过驱动件确定数字调制信息,并驱动数字调制信息加载至光电集成件生成的相干光信号上,光电集成件利用预设光学衍射神经网络中对调制后的相干光信号进行数字逻辑运算,得到运算结果,并将运算结果基于数字逻辑映射关系生成电信号,并利用驱动件读取电信号后输出运算结果,从而实现混合集成的光电逻辑计算,具有更高的单位能耗计算性能(flops/j),可以重构、批量地设计不同的专用逻辑运算,运算规模大,调制速率高。

21.具体而言,图1为根据本技术实施例提供的一种光电数字逻辑运算的光学逻辑元件结构示意图。

22.如图1所示,该光电数字逻辑运算的光学逻辑元件包括:驱动件100和光电集成件200。

23.其中,驱动件100,用于为光电集成件200提供驱动,产生光电集成件200能够识别的数字调制信息以及读取光电集成件200输出的电信号。光电集成件200,用于利用相干光信号搭载驱动件100输入的数字调制信息,并在预设光学衍射神经网络中对相干光信号进行数字逻辑运算,得到运算结果,并将运算结果基于数字逻辑映射关系生成电信号,并利用驱动件100读取电信号后输出运算结果。

24.可以理解的是,本技术的光电数字逻辑运算的光学逻辑元件是通过驱动件100和光电集成件200混合集成的,集成方法包括但不限于wafer bonding,die bonding,wire bonding,flip chip bonding等。

25.根据本技术的实施例,光电集成件200包括:激光器201,用于基于驱动件100发送的第一驱动信号生成相干光信号。分光器件202,用于将相干光信号分束成至少一束相干光信号。调制器组203,用于将数字调制信息加载到至少一束相干光信号上,得到加载数字调制信息的相干光信号。微纳光学衍射线阵列204,用于由阵列产生的预设光学衍射神经网络对相干光信号进行数字逻辑运算,输出运算结果。探测器阵列205,用于根据运算结果生成电信号。

26.如图2所示,展示了一种具体的光电数字逻辑运算的光学逻辑元件结构,根据信号

的传输方向,光电集成件200依次包括激光器201、分光器件202、调制器组203、微纳光学衍射线阵列204和探测器阵列205。

27.具体地,激光器201根据驱动件100的第一驱动信号发出相干光信号。在一个具体实施例中,激光器201包括但不限于分布式反馈激光器(distributed feedback laser,dfb),微环激光器(micro

‑

ring),垂直腔面发射激光器(vertical

‑

cavity surface

‑

emitting laser,vcsel),lp激光器。其中,中心波长包括但并不限于紫外光、可见光、红外光的波长;激光器材料包括但并不限于ingaas,alasp,gaas,gan,ingan,algan等;激光器结构包括但并不限于多量子阱和量子点等。

28.根据本技术的实施例,分光器件202包括:波导,用于引导相干光信号。分束器,用于将引导的相干光信号进行分束。

29.具体地,通过激光器201发出相干光信号后,利用分光器件202对相干光信号进行引导和分束。在本技术的一个具体实施例中,分光器件202可以包括波导和分束器,其他可以用来将相干光信号进行分束的器件也可应用在本技术的实施例中,不作具体限制。

30.在一些实施例中,波导和分束器的波导中心波长包括但不限于紫外光、可见光、红外光的波长;模式包括但不限于单模和多模;分束器将相干光信号至少分为一束相干光信号分束器,分束形式包括并不限于y

‑

splitter,mmi(multi

‑

mode inferometer,多模干涉器)等。

31.根据本技术的实施例,调制器组203中调制器的数量为至少一个。

32.可以理解的是,通过调制器组203将数字调制信息加载到至少一束相干光信号上,为了对至少一束相干光信号进行调制,调制器组中至少包括一个调制器。

33.在一些实施例中,调制器包括但不限于franz

‑

keldysh效应(弗兰之

‑

克尔德什效应)和stark效应(斯塔克效应)调制器,mach

‑

zehnder调制器(马赫

‑

曾德尔调制器),电吸收调制器等。其中,调制器调制带宽为h(h>0hz)。

34.根据本技术的实施例,光电集成件200加载数字调制信息的加载时序包括同步与异步。

35.根据本技术的实施例,微纳光学衍射线阵列204的阵列结构由预设光学衍射神经网络对应的数字逻辑运算功能确定。

36.本技术实施例的光学逻辑元件可以实现多种不同的光电数字逻辑运算,其中,光电数字逻辑运算的计算部分由一系列具有相同长度、间隔、平均厚度的微纳衍射线阵列204构成,每根衍射线上刻有不同的预先设计的衍射图样。作为一种具体的实施方式,本技术实施例通过改变微纳光学衍射线阵列204的阵列结构实现预设光学衍射神经网络对应的数字逻辑运算功能,其中,数字逻辑运算功能包括但不限于全加器、移位器、与或非等基本逻辑门、以及其他组合逻辑计算等。

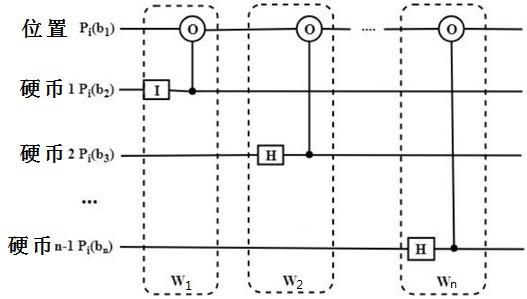

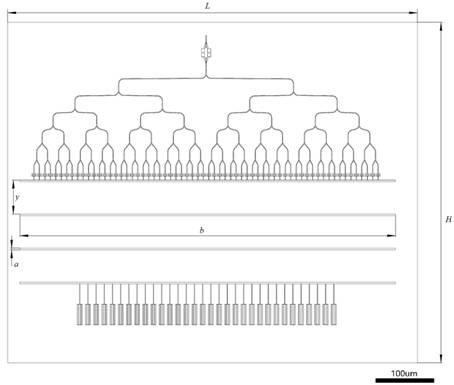

37.以全加器的数字逻辑运算功能为例,实现全加逻辑计算。图3和图4展示了全加器中光电集成件200的俯视结构和三维侧视结构,单个光电集成件200的长、宽分别为l、h,基底厚度为d,图中由上往下是信息的传递方向,分别由激光器、波导和分束器阵列、调制器组、微纳光学衍射线阵列、探测器阵列构成。微纳光学衍射线阵列的每一条衍射线平均厚度为a,长度为b,宽度为c,每条衍射线之间的间隔为y,衍射线数量为x(图中未标示),衍射计算靠衍射线的表面起伏完成。

38.根据本技术的实施例,阵列结构通过衍射线数量、衍射线间的间距、每条衍射线的厚度、每条衍射线的宽度、每条衍射线的长度和由每条衍射线的厚度、宽度、长度的均方根粗糙度中的一项或多项进行调整。

39.具体地,微纳光学衍射线阵列的阵列结构包括下面八组变量中的一个或多个,微纳光学衍射线数量x(x>0),每两条微纳光学衍射线间距y(1,000,000 nm>y>1 nm),每条衍射线厚度z(1,000,000 nm>z>1 nm),每条衍射线宽度a(1,000,000 nm>a>1 nm),每条衍射线长度b(1,000,000 nm>b>1 nm),z、a、b的均方根粗糙度c

z

,c

a

,c

b

(1,000,000 nm>c

z

,c

a

,c

b

>1 nm)。通过更改上述变量的参数,对微纳光学衍射线阵列的阵列结构进行改变,实现不同的光电逻辑运算,阵列结构中衍射线的设计方法包括但不限于神经网络反向传播法和物理光学计算法等。

40.在一些实施例中,微纳光学衍射线阵列制备材料包括但不限于sio2,sin

x

,si,gan和aln等。

41.根据本技术的实施例,驱动件100包括:第一驱动子件101,用于生成驱动激光器产生相干光信号的第一驱动信号。第二驱动子件102,用于生成驱动调制器组加载数字调制信息的第二驱动信号。第三驱动子件103,用于生成驱动探测器阵列产生电信号的第三驱动信号。读取子件104,用于从探测器阵列中读取电信号,并基于电信号输出运算结果。

42.具体地,驱动件100可以为光电集成件200提供能量驱动、数字信号加载及信号读取。如图5所示,第一驱动子件101与激光器201连接,利用第一驱动信号驱动激光器201产生相干光信号。第二驱动子件102与调制器组203连接,第二驱动子件102利用第二驱动信号驱动数字调制信息加载至相干光信号上。第三驱动子件103和读取子件104与探测器阵列205连接,利用第三驱动信号驱动探测器阵列205进行光电转换,将微纳光学衍射线阵列204的运算结果转换为电信号,并通过读取子件104读取该电信号,得到最终得到运算结果。

43.在一些实施例中,驱动件100包括但不限于高速模数转换器、高速数模转换器,功率放大器,跨导放大器等。

44.可以理解的是,上述实施例中的光学逻辑元件可以通过硅基光电子工艺进行加工,例如可以在对应的材料上进行刻蚀得到微纳光学衍射线阵列,刻蚀方法包括但不限于湿法刻蚀和干法刻蚀等。

45.在本技术的一个具体实施例中,两路n比特逻辑输入信号由驱动件100并行地输入至相应的2 * n个调制器组上,在激光器和波导分光器产生的直流激光上加载激光信号,经过微纳光学衍射线阵列进行光学衍射传播计算,其中,衍射线上刻有特定的衍射图样,能够将输入计算成相应的n比特光信号结果,经过n个探测器组成的探测器阵列进行光电激活和探测后从驱动件100进行数字信号的读取。

46.根据本技术实施例提出光电数字逻辑运算的光学逻辑元件及其逻辑运算方法,通过驱动件确定数字调制信息,并驱动数字调制信息加载至光电集成件生成的相干光信号上,光电集成件利用预设光学衍射神经网络中对调制后的相干光信号进行数字逻辑运算,得到运算结果,并将运算结果基于数字逻辑映射关系生成电信号,并利用驱动件读取电信号后输出运算结果,从而实现混合集成的光电逻辑计算,具有更高的单位能耗计算性能,可以重构、批量地设计不同的专用逻辑运算,运算规模大,调制速率高。

47.其次参照附图描述根据本技术实施例提出的光电数字逻辑运算方法。

48.图6为根据本技术实施例提供的一种光电数字逻辑运算方法流程图。

49.如图6所示,该光电数字逻辑运算方法采用上述实施例中的光电数字逻辑运算的光学逻辑元件,其具体包括以下步骤:步骤s1:确定数字调制信息。

50.步骤s2:驱动数字调制信息加载至相干光信号,得到加载数字调制信息的相干光信号。

51.步骤s3:在预设光学衍射神经网络中对相干光信号进行数字逻辑运算,得到运算结果,并将运算结果基于数字逻辑映射关系生成电信号,并根据电信号输出运算结果。

52.需要说明的是,前述对光电数字逻辑运算的光学逻辑元件实施例的解释说明也适用于该实施例的光电数字逻辑运算方法,此处不再赘述。

53.本技术实施例的光电数字逻辑运算方法,通过确定数字调制信息,驱动数字调制信息加载至相干光信号,得到加载数字调制信息的相干光信号,在预设光学衍射神经网络中对相干光信号进行数字逻辑运算,得到运算结果,并将运算结果基于数字逻辑映射关系生成电信号,并根据电信号输出运算结果。从而实现混合集成的光电逻辑计算,具有更高的单位能耗计算性能(flops/j),可以重构、批量地设计不同的专用逻辑运算,运算规模大,调制速率高。

54.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本技术的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或n个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

55.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。在本技术的描述中,“n个”的含义是至少两个,例如两个,三个等,除非另有明确具体的限定。

56.流程图中或在此以其他方式描述的任何过程或方法描述可以被理解为,表示包括一个或更n个用于实现定制逻辑功能或过程的步骤的可执行指令的代码的模块、片段或部分,并且本技术的优选实施方式的范围包括另外的实现,其中可以不按所示出或讨论的顺序,包括根据所涉及的功能按基本同时的方式或按相反的顺序,来执行功能,这应被本技术的实施例所属技术领域的技术人员所理解。

57.在流程图中表示或在此以其他方式描述的逻辑和/或步骤,例如,可以被认为是用于实现逻辑功能的可执行指令的定序列表,可以具体实现在任何计算机可读介质中,以供指令执行系统、装置或设备(如基于计算机的系统、包括处理器的系统或其他可以从指令执行系统、装置或设备取指令并执行指令的系统)使用,或结合这些指令执行系统、装置或设备而使用。就本说明书而言,"计算机可读介质"可以是任何可以包含、存储、通信、传播或传输程序以供指令执行系统、装置或设备或结合这些指令执行系统、装置或设备而使用的装置。计算机可读介质的更具体的示例(非穷尽性列表)包括以下:具有一个或n个布线的电连

接部(电子装置),便携式计算机盘盒(磁装置),随机存取存储器(ram),只读存储器(rom),可擦除可编辑只读存储器(eprom或闪速存储器),光纤装置,以及便携式光盘只读存储器(cdrom)。另外,计算机可读介质甚至可以是可在其上打印所述程序的纸或其他合适的介质,因为可以例如通过对纸或其他介质进行光学扫描,接着进行编辑、解译或必要时以其他合适方式进行处理来以电子方式获得所述程序,然后将其存储在计算机存储器中。

58.应当理解,本技术的各部分可以用硬件、软件、固件或它们的组合来实现。在上述实施方式中,n个步骤或方法可以用存储在存储器中且由合适的指令执行系统执行的软件或固件来实现。如,如果用硬件来实现和在另一实施方式中一样,可用本领域公知的下列技术中的任一项或他们的组合来实现:具有用于对数据信号实现逻辑功能的逻辑门电路的离散逻辑电路,具有合适的组合逻辑门电路的专用集成电路,可编程门阵列(pga),现场可编程门阵列(fpga)等。

59.本技术领域的普通技术人员可以理解实现上述实施例方法携带的全部或部分步骤是可以通过程序来指令相关的硬件完成,所述的程序可以存储于一种计算机可读存储介质中,该程序在执行时,包括方法实施例的步骤之一或其组合。

60.此外,在本技术各个实施例中的各功能单元可以集成在一个处理模块中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个模块中。上述集成的模块既可以采用硬件的形式实现,也可以采用软件功能模块的形式实现。所述集成的模块如果以软件功能模块的形式实现并作为独立的产品销售或使用时,也可以存储在一个计算机可读取存储介质中。

61.上述提到的存储介质可以是只读存储器,磁盘或光盘等。尽管上面已经示出和描述了本技术的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本技术的限制,本领域的普通技术人员在本技术的范围内可以对上述实施例进行变化、修改、替换和变型。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。