1.本发明属于模数混合电路领域,具体涉及一种单通道通信编码方法、解码方法、编码电路及解码电路。

背景技术:

2.数字隔离器用于通信,其包括源边和副边,副边接收源边发送的信号。

3.图1是一种常见的数据与时钟隔离传输的方式,源边的数据与时钟分别使用一个隔离通道将信号传输到隔离的副边,该方式需要占用两个隔离通道,工作时功耗较大,晶圆成本较高,且芯片封装时需要更多打线,封装成本较高。

4.图2为基于时钟数据恢复技术的单通道隔离通信,源边同步于时钟的数据信号通过发送器以串行方式发送到隔离的副边,副边通过时钟数据恢复电路将时钟从接收的数据信号里提取出来,然后用提取的时钟对数据进行重新采样,最终得到了恢复的时钟和数据信号。

5.图3是一种常见的基于锁相环电路的时钟数据恢复电路和时序。

6.图2和图3所示的电路都有以下技术缺点:(1)无法通信一长串的“0”或“1”信号;(2)传输信号的数据码率、相位与接收端时钟数据恢复电路中压控振荡器的频率、相位有偏差,需要较长的时间完成频率和相位的锁定,因此,需要较长时间建立通信;(3)时钟数据恢复电路需要先锁定频率再锁定相位,控制环路较多,设计复杂度较高,实现成本较高。

技术实现要素:

7.本发明目的是设计一种高效通信的方法,能同时编码时钟信号和数据信号,降低电路复杂度,减少芯片封装打线。

8.为实现上述发明目的之一,本发明一实施方式提供一种单通道通信编码方法,包括:将时钟信号和数据信号合成一路长短码信号;所述长短码信号包括长码信号和短码信号,所述长码信号的脉宽与时钟信号一致,所述短码信号的脉宽与时钟信号一致;所述长码信号与所述短码信号的占空比不同。

9.作为本发明一实施方式的进一步改进,所述长短码信号的占空比满足关系式:tclk=ts tl,其中,tclk为时钟周期,ts为短码信号的高电平时间,tl为长码信号的高电平时间,且ts不等于tl。

10.作为本发明一实施方式的进一步改进,将时钟信号和数据信号合成一路长短码信号包括:根据时钟信号产生第一延迟时钟信号;

根据所述第一延迟时钟信号产生脉冲信号;根据所述脉冲信号生成长码信号的高电平和短码信号的高电平;根据所述第一延迟时钟信号产生第二延迟时钟信号;根据所述第二延迟时钟信号生成短码信号的低电平;根据时钟信号生成长码信号的低电平;根据所述第一延迟时钟信号和数据信号产生数据延迟信号;根据数据信号选择所述长码信号或所述短码信号并生成长短码信号。

11.作为本发明一实施方式的进一步改进,所述第一延迟时钟信号相对于时钟信号延迟时间为ts;所述第二延迟时钟信号相对于第一延迟时钟信号延迟时间为ts;所述数据延迟信号相对于数据信号延迟时间为ts。

12.作为本发明一实施方式的进一步改进,将时钟信号和数据信号合成一路长短码信号进一步包括:根据时钟信号产生第一脉冲信号;根据时钟信号产生第一延迟时钟信号;根据所述第一延迟时钟信号产生第二延迟时钟信号;根据所述第二延迟时钟信号产生第二脉冲信号;根据所述第一延迟时钟信号产生第三脉冲信号;根据所述第三脉冲信号生成长码信号的高电平或短码信号的高电平;根据所述数据信号和所述第一延迟时钟信号产生数据延迟信号;根据所述数据延迟信号选择第一脉冲信号或第二脉冲信号;根据被选择的第二脉冲信号生成短码信号的低电平;根据被选择的第一脉冲信号生成长码信号的低电平。

13.为实现上述发明目的之一,本发明一实施方式提供一种单通道通信编码电路,包括:第一延迟电路,用于根据时钟信号产生第一延迟时钟信号;脉冲发生器,用于根据所述第一延迟时钟信号产生脉冲信号;长码触发器,其重置端接收所述脉冲信号,并输出长码信号的高电平,其时钟端接收时钟信号,时钟信号触发输出长码信号的低电平;短码触发器,其重置端接收所述脉冲信号,输出短码信号的高电平;第二延迟电路,用于根据所述第一延迟时钟信号产生第二延迟时钟信号;所述短码触发器的时钟端接收所述第二延迟时钟信号,并输出短码信号的低电平;选择触发器,其时钟端接收第一延迟时钟信号,数据端连接数据信号,输出端输出数据延迟信号;数据选择器,其第一输入端连接所述长码触发器的输出端,第二输入端连接短码触发器的输出端;选择端连接所述选择触发器的输出端,所述数据选择器根据所述数据延迟信号选择输出所述长码信号或短码信号并形成长短码信号。

14.为实现上述发明目的之一,本发明一实施方式提供一种单通道通信编码电路,包括:

第一延迟电路,用于根据时钟信号产生第一延迟时钟信号;第二延迟电路,用于根据第一延迟信号产生第二延迟时钟信号;第一脉冲发生器,用于根据第一延迟时钟信号产生第一脉冲信号;第二脉冲发生器,用于根据所述第二延迟时钟信号产生第二脉冲信号;第三脉冲发生器,用于所述第一延迟时钟信号产生第三脉冲信号;选择触发器,其时钟端接收第一延迟时钟信号,数据端连接数据信号,输出端输出数据延迟信号;数据选择器,其第一输入端连接所述第一脉冲发生器,第二输入端连接所述第二脉冲发生器;所述数据选择器的选择端连接数据延迟信号,并根据所述数据延迟信号选择第一脉冲信号或第二脉冲信号;输出触发器,其重置端与所述第三脉冲发生器连接,时钟端与所述数据选择器的输出端连接;所述输出触发器根据所述第三脉冲信号产生长码信号的高电平或短码信号的高电平,所述时钟端收到所述第一脉冲信号并产生长码信号的低电平;所述时钟端收到所述第二脉冲信号并产生短码信号的低电平。

15.为实现上述发明目的之一,本发明一实施方式提供一种单通道通信解码方法,包括:根据长短码信号的高电平产生时钟信号的低电平;根据长短码信号产生延迟脉冲信号,所述延迟脉冲信号的延迟时间为半个时钟周期;根据所述延迟脉冲信号产生时钟信号的高电平;根据所述时钟信号和长短码信号产生数字信号。

16.作为本发明一实施方式的进一步改进,所述根据长短码信号产生延迟脉冲信号进一步包括:根据所述长短码信号产生长短码延迟信号,根据所述长短码延迟信号和长短码信号的相位差控制所述长短码信号的延迟时间。

17.作为本发明一实施方式的进一步改进,根据长短码延迟信号和长短码信号的相位差控制所述长短码信号的延迟时间进一步包括:将所述相位差的信号转换为电压信号,根据所述电压信号控制长短码延迟信号的延迟时间。

18.为实现上述发明目的之一,本发明一实施方式提供一种单通道通信解码电路,包括:延迟脉冲电路,用于将长短码信号延迟半个时钟周期并产生长短码延迟信号;脉冲发生器,用于根据所述长短码延迟信号产生延迟脉冲信号;时钟触发器,其时钟端与长短码信号连接并根据长短码信号产生时钟信号的低电平,重置端与所述脉冲发生器的输出端连接,所述时钟触发器根据所述延迟脉冲信号产生时钟信号的高电平;数字信号触发器,其时钟端与所述时钟触发器的输出端连接,数据端与所述长短码信号连接,所述数字信号触发器根据时钟信号生成数字高电平或数字低电平。

19.作为本发明一实施方式的进一步改进,所述延迟脉冲电路包括延迟电路和脉冲电路,所述延迟电路包括:延迟电路中间级,用于将所述长短码信号转换为长短码延迟信号;鉴频鉴相器,用于检测长短码延迟信号和长短码信号之间的相位差;

电荷泵,用于将所述相位差转换为电流信号;低通滤波器,用于将所述电流信号转换为电压信号;其中,所述延迟电路中间级与所述低通滤波器连接,且所述延迟电路中间级用于接收所述电压信号并控制长短码延迟信号的延迟时间。

20.作为本发明一实施方式的进一步改进,所述解码电路进一步包括翻转检测器、振荡器和数据选择器;当不通信时,所述翻转检测器输出低电平,所述数据选择器将所述振荡器的输出接入延迟锁定环,并建立电压信号;当通信时,所述翻转检测器输出高电平,所述数据选择器将所述长短码信号接入所述延迟脉冲电路。

21.本发明相对现有技术至少有以下几方面的有益技术效果:(1)使用长短码编码方案将数据信号和时钟信号融合通信,效率更高,且功耗更低;(2)支持单通道通信可减少芯片封装和打线,降低芯片制造成本;(3)编码电路和解码电路结构简单,降低了电路设计复杂度;(4)通信建立时间短。

附图说明

22.图1是现有技术的通信电路示意图;图2是另一现有技术的通信电路示意图;图3是又一现有技术的通信电路示意图;图4是本发明通信电路结构示意图;图5是本发明编码时序示意图;图6是本发明编码方法流程示意图;图7是本发明编码电路结构示意图;图8是本发明编码电路时序示意图;图9是本发明另一种编码方法流程示意图;图10是本发明另一种电路结构示意图;图11是本发明另一种电路时序示意图;图12是本发明解码方法流程示意图;图13是本发明解码电路结构示意图;图14是本发明解码电路时序示意图;图15是本发明解码电路其中包含延迟电路的结构示意图;图16是本发明解码电路其中包含用于预建立控制电压的电路的结构示意图。

具体实施方式

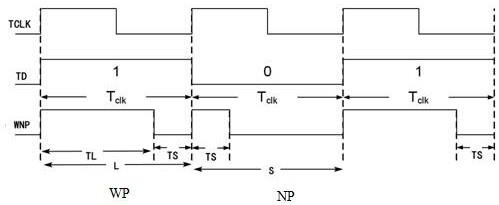

23.以下参照附图对本发明技术方案作进一步详尽的说明,以帮助本领域技术人员理解本发明的技术方案。以下按照编码解码的顺序叙述本发明技术方案。

24.编码方法

参图4,为数字隔离芯片或隔离放大芯片等通信电路结构示意图。

25.通信电路包括源边401和副边403,源边401发送通信数据,副边403接收通信数据。

26.源边401包括编码器402和发送器404,副边403包括接收器406和解码器408。

27.发送器404和接收器406之间通过隔离电容410连接。

28.编码器402的输入端用于接收数据信号td和时钟信号tclk,解码器408的输出端输出数字信号rd和时钟信号rclk。

29.图5为本发明数据信号td、时钟信号tclk和长短码信号wnp的编码时序示意图,通过编码方法将时钟信号tclk和数据信号td合成一路长短码信号wnp。

30.长短码信号wnp包括长码信号wp和短码信号np,长码信号wp的脉宽与时钟信号tclk一致,短码信号np的脉宽与时钟信号tclk一致;长码信号wp与短码信号np的占空比不同。

31.长码信号wp的高低电平的占空比大于短码信号np的高低电平的占空比。长码信号wp用于表示数据信号td为“1”,短码信号np用于表示数据信号td为“0”。

32.长码信号wp或短码信号np的脉宽为一个时钟周期tclk,并且,长短码信号wnp的占空比满足关系式:tclk=ts tl,其中,tclk为时钟周期,ts为短码信号np的高电平时间,tl为长码信号wp的高电平时间,并且ts不等于tl。如图中所示,长码信号wp的低电平与短码信号np的高电平的脉宽相等。

33.通过上述长短码编码方案将数据信号td和时钟信号tclk融合通信,效率更高功耗更低。同时,支持单通道通信可减少芯片封装和打线,降低芯片制造成本。并且,编码电路和解码电路结构简单,降低了电路设计复杂度。

34.需要指出的是,本发明和传统的ook法有本质区别,ook法是用振荡信号(on)表示1,没有振荡信号(off)表示0。而本发明中不同占空比的长短码信号wnp是用ook法传输的,即用on传输长短码信号wnp中的高电平,用off传输长短码信号wnp中的低电平,亦即,用on或off表示高低电平,但数据信号td的内容则使用长短码信号wnp的不同占空比表示。

35.编码方法一参照图6,是长短码编码方法流程示意图,其在获得“时钟信号”后包括步骤:602:根据时钟信号产生第一延迟时钟信号;604:根据第一延迟时钟信号产生脉冲信号;606:根据脉冲信号生成长码信号的高电平和短码信号的高电平;608:根据第一延迟时钟信号产生第二延迟时钟信号;610:根据第二延迟时钟信号生成短码信号的低电平;612:根据时钟信号生成长码信号的低电平;614:根据第一延迟时钟信号和数据信号产生数据延迟信号;616:根据数据信号选择长码信号或短码信号并生成长短码信号。

36.以下,结合图7所示的电路结构和图8所示的时序对步骤602至616做进一步详尽的解释。

37.图7及其他附图中所包含的延迟电路、脉冲发生器、触发器、数据选择器等电路均为标准器件,本发明不再对这些标准器件展开讨论,本领域技术人员能够根据其掌握的知识实现。

38.时钟信号tclk连接第一延迟电路(delay)702,第一延迟电路702的输出端连接脉冲发生器(one

‑

shot)706,脉冲发生器706按照图7右下方示出的时序进行动作,且其输出端连接长码触发器708和短码触发器710的重置端s;长码触发器708和短码触发器710的数据端d接地,长码触发器708和短码触发器710的输出端q分别连接数据选择器712的第一输入端(mux的1号端,其中mux全称为multiplexer,中文译名为数据选择器)和第二输入端(mux的0号端);第二延迟电路(delay)704的输入端与第一延迟电路702的输出端连接,第二延迟电路704的输出端连接短码触发器710的时钟端;第一延迟电路702的输出端与选择触发器716的时钟端连接,数据信号td与选择触发器716的数据端d连接,选择触发器716的输出端q与数据选择器712的选择端sel连接。数据选择器712还包括用于输出长短码信息wnp的输出端。

39.参照图6至图8,在步骤602中,根据时钟信号tclk产生第一延迟时钟信号td1。

40.第一延迟电路702根据时钟信号tclk产生第一延迟时钟信号td1,第一延迟时钟信号td1相对时钟信号tclk的延迟时间为ts。

41.在步骤604中,根据第一延迟时钟信号td1产生脉冲信号。

42.第一延迟时钟信号td1的上升沿触发脉冲发生器706,脉冲发生器706根据第一延迟时钟信号td1产生脉冲信号,该脉冲信号送入长码触发器708和短码触发器710的重置端s。

43.在步骤606中,长码触发器708和短码触发器710根据脉冲信号生成长码信号wp的高电平8022和短码信号np的高电平8024;并且在脉冲信号消失后,长码信号wp和短码信号np能够保持高电平状态。

44.在步骤608和步骤610中,根据第一延迟时钟信号td1产生第二延迟时钟信号td2。

45.第二延迟电路704根据第一延迟时钟信号td1产生第二延迟时钟信号td2,第二延迟时钟信号td2相对于第一延迟时钟信号td1的延迟时间为ts。

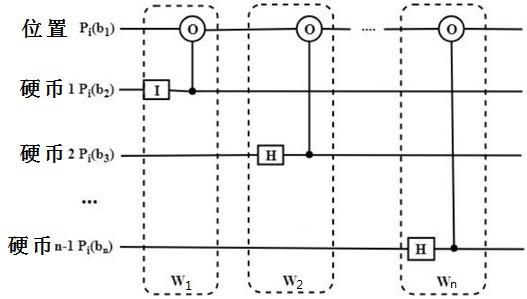

46.第二延迟时钟信号td2上升沿出现时,短码触发器710的时钟端为高电平,短码触发器710输出数据端d接地的低电平,由此,生成短码信号np的低电平804。

47.在步骤612中,根据时钟信号生成长码信号wp的低电平808。

48.在下一个时钟周期上升沿806到来时,长码触发器708的时钟端接收时钟信号,以触发输出数据端d的电平,数据端d接地,此时,输出信号形成长码信号wp的低电平808。

49.在步骤614中,根据第一延迟时钟信号td1和数据信号td产生数据延迟信号tdd1。

50.第一延迟时钟信号td1比时钟信号tclk或数据信号td延迟ts,数据信号td和时钟信号tclk同步,因此,以第一延迟时钟信号td1作为时钟源,数据信号td连接选择触发器716数据端后,会同步产生数据延迟信号tdd1。也即数据延迟信号tdd1相对于数据信号td延迟时间为ts。

51.在步骤616中,根据数据信号td选择长码信号wp或短码信号np并生成长短码信号wnp。

52.数据延迟信号tdd1与数据选择器712的选择端sel连接,数据延迟信号tdd1为高电平时,选择长码信号wp输出,对应图中第一输入端的输入信号;数据延迟信号tdd1为低电平时,选择短码信号np输出,对应图中第二输入端的输入信号,数据延迟信号tdd1与长短码信号wnp同步,根据数据延迟信号tdd1选择输出长码信号wp或短码信号np,从而形成长短码信

号wnp编码。

53.编码方法二参照图9,本发明提供另一种单通道通信编码方法。其包括下述在得到“时钟信号”后的步骤:902:根据时钟信号产生第一脉冲信号;904:根据时钟信号产生第一延迟时钟信号;906:根据第一延迟时钟信号产生第二延迟时钟信号;908:根据第二延迟时钟信号产生第二脉冲信号;910:根据第一延迟时钟信号产生第三脉冲信号;912:根据第三脉冲信号生成长码信号的高电平或短码信号的高电平;914:根据数据信号和第一延迟时钟信号产生数据延迟信号;916:根据数据延迟信号选择第一脉冲信号或第二脉冲信号;918:根据被选择的第二脉冲信号生成短码信号的低电平;920:根据被选择的第一脉冲信号生成长码信号的低电平。

54.以下结合图10所示的电路结构和图11所示的时序图对步骤902至920做进一步详尽的解释。

55.参照图10,编码电路包括第一延迟电路(delay)1002、第二延迟电路(delay)1004、第一脉冲发生器(one

‑

shot1)1006、第二脉冲发生器(one

‑

shot2)1008、第三脉冲发生器(one

‑

shot3)1014、数据选择器(mux)1010、选择触发器1012、输出触发器1016。

56.时钟信号tclk连接第一延迟电路1002、第一脉冲发生器1006。

57.第一延迟电路1002的输出端连接第二延迟电路1004的输入端,第二延迟电路1004的输出端连接第二脉冲发生器1008的输入端,第二脉冲发生器1008的输出端连接数据选择器1010的第二输入端(mux的0号端)。

58.第一脉冲发生器1006的输出端连接数据选择器1010的第一输入端(mux的1号端),数据信号td连接选择触发器1012的数据输入端d,选择触发器1012的输出端q连接数据选择器1010的选择端sel(也即数据选择器1010的选择端sel连接数据延迟信号tdd1),第三脉冲发生器1014的输出端连接输出触发器1016的重置端s,输出触发器1016的时钟端连接数据选择器1010的输出端形成结点a(node a)。输出触发器1016还包括接地的数据端d和用于输出长短码信号wnp的输出端q。

59.参照图9至图11,在步骤902中,根据时钟信号tclk结点a(node a)处产生第一脉冲信号p1,时钟信号的上升沿1102触发第一脉冲发生器1006,第一脉冲发生器1006根据第一延迟时钟信号(即上升沿1102)产生第一脉冲信号p1,该第一脉冲信号p1输入数据选择器1010的第一输入端。

60.在步骤904中,根据时钟信号tclk产生第一延迟时钟信号td1。

61.第一延迟电路1002根据时钟信号tclk产生第一延迟时钟信号td1,第一延迟时钟信号td1作为第二延迟时钟信号td2的基础,第一延迟时钟信号td1相对时钟信号的延迟时间为ts。

62.在步骤906中,根据第一延迟时钟信号td1产生第二延迟时钟信号td2。

63.第二延迟电路1004根据第一延迟信号td1产生第二延迟时钟信号td2,第二延迟时

钟信号td2相对第一延迟时钟信号td1的延迟时间为ts。

64.在步骤908中,根据第二延迟时钟信号td2产生第二脉冲信号p2。第二脉冲发生器1008根据第二延迟时钟信号td2产生第二脉冲信号p2,该第二脉冲信号p2用于使得输出触发器1016输出低电平。

65.在步骤910中,根据第一延迟时钟信号td1产生第三脉冲信号(时序图中未示出)。

66.第三脉冲发生器1014根据第一延迟时钟信号td1产生第三脉冲信号。

67.在步骤912中,该第三脉冲信号重置输出触发器1016而产生长码信号wp的高电平1104或短码信号np的高电平1106(长码信号wp和短码信号np记载于长短码信号wnp中)。

68.在步骤914中,根据数据信号td和第一延迟时钟信号td1产生数据延迟信号tdd1。

69.选择触发器1012的时钟端接收第一延迟时钟信号td1,数据端d连接数据信号td,输出端q输出数据延迟信号tdd1,该数据延迟信号tdd1与第一延迟时钟信号td1同步。

70.在步骤916中,根据数据延迟信号tdd1选择第一脉冲信号p1或第二脉冲信号p2。

71.数据选择器1012根据数据延迟信号tdd1选择第一脉冲信号p1或第二脉冲信号p2。数据延迟信号tdd1为高电平时,数据选择器1012输出第一脉冲信号p1;数据延迟信号tdd1为低电平时,数据选择器1012输出第二脉冲信号p2。

72.在步骤920中,根据被选择的第一脉冲信号p1生成长码信号wp的低电平1108。

73.第一脉冲信号p1的上升沿与时钟信号tclk的上升沿对齐,因此,第一脉冲信号p1使得输出触发器1016产生长码信号wp的低电平1108,随后,第三脉冲发生器1014产生脉冲信号,重新将输出触发器1016的输出电平拉高形成长码信号wp的高电平1104,从而完成一次长码编码。

74.在步骤918中,根据被选择的第二脉冲信号p2生成短码信号np的低电平1110。

75.第二脉冲信号p2的上升沿相对第一延迟时钟信号td1的延迟时间为ts,在输出触发器1016高电平持续延迟时间ts后,输出触发器1016的输出电平被第二脉冲信号p2拉低形成短码信号np的低电平1110,在随后的第一延迟时钟信号td1的上升沿出现后,第三脉冲发生器1014产生脉冲信号,重新将输出触发器1016的输出电平拉高形成短码信号np的高电平1106,从而完成一次短码编码。

76.解码方法参照图12,单通道通信的解码方法包括下述在得到“长短码信号”后的步骤:1202:根据长短码信号的高电平产生时钟信号的低电平;1204:根据长短码信号产生延迟脉冲信号,延迟脉冲信号的延迟时间为半个时钟周期;1206:根据延迟脉冲信号产生时钟信号的高电平;1208:根据时钟信号和长短码信号产生数字信号。

77.以下,结合图13所示的电路结构和图14所示的时序图对步骤1202至1208做进一步详尽的解释。

78.参照图13,电路结构包括延迟脉冲电路(delay 0.5tclk)1302、脉冲发生器(one

‑

shot)1304、时钟触发器1306、数字信号触发器1308。

79.延迟脉冲电路1302与长短码信号wnp连接,延迟脉冲电路1302的输出端与脉冲发生器1304连接,数字信号触发器1308的数据端d与长短码信号wnp连接,时钟触发器1306的

时钟端与长短码信号wnp连接,时钟触发器1306的重置端s与脉冲发生器1304的输出端连接,以接收延迟脉冲信号set,时钟触发器1306的输出端q与数字信号触发器1308的时钟端连接,以输出时钟信号rclk。时钟触发器1306还包括接地的数据端d,数字信号触发器1308还包括用于输出数字信号rd的输出端q。

80.参照图12至图14,在步骤1202中,根据长短码信号wnp的高电平产生时钟信号rclk的低电平1402。

81.长短码信号wnp上升沿1404输入时钟触发器1306后,时钟触发器1306输出端q输出数据端d的低电平1402(包含于时钟信号rclk中),也即时钟触发器1306根据长短码信号wnp产生时钟信号rclk的低电平。

82.在步骤1204中,根据长短码信号wnp产生延迟脉冲信号set,延迟脉冲信号set延迟时间为半个时钟周期(0.5tclk)。

83.延迟脉冲电路1302将长短码信号wnp延迟半个时钟周期并产生长短码延迟信号,脉冲发生器1304根据该长短码延迟信号产生延迟脉冲信号set,换言之,延迟脉冲信号set的上升沿1408距离长短码信号wnp的上升沿1404的长度为半个时钟周期。

84.在步骤1206中,该延迟脉冲信号set重置时钟触发器1306输出端q而使之输出高电平,构成了时钟信号rclk的高电平。

85.重复步骤1202至1206即可产生多个时钟信号rclk。

86.在步骤1208中,根据时钟信号rclk和长短码信号wnp产生数字信号rd。

87.数字信号触发器1308根据时钟信号rclk生成包含于数字信号rd内的数字高电平或数字低电平1406。

88.由于时钟信号rclk的上升沿1410恰好在数据信号的中间位置(半个周期处),数字信号触发器1308的输出信号为长码信号wp的高电平或短码信号np的低电平,使得输出的解码高低电平信号恰好与长短码信号wnp编码对应。

89.进一步地对上述方法改进,根据长短码信号wnp产生延迟脉冲信号set进一步包括:根据长短码信号wnp产生长短码延迟信号,根据长短码延迟信号和长短码信号wnp的相位差控制长短码信号wnp的延迟时间。

90.进一步地对上述方法改进,根据长短码延迟信号和长短码信号wnp的相位差控制长短码信号wnp的延迟时间进一步包括:将相位差对应的相位差信号转换为电压信号,根据电压信号控制长短码延迟信号的延迟时间。

91.参照图15所示的单通道通信的解码电路,其包括图13中延迟脉冲电路1302的延迟电路的内部结构,延迟脉冲电路1302还可以包括脉冲电路。

92.具体的,包括延迟电路中间级1502,用于将长短码信号wnp转换为长短码延迟信号wnpd;鉴频鉴相器1504,用于检测长短码延迟信号wnpd和长短码信号wnp之间的相位差;电荷泵1506,用于将相位差转换为电流信号;低通滤波器1508,用于将电流信号转换为电压信号vctrl;延迟电路中间级1502与低通滤波器1508输出端连接,且延迟电路中间级1502用于接收电压信号vctrl并控制长短码延迟信号wnpd的延迟时间。

93.上述由鉴频鉴相器1504至低通滤波器1508形成的、由相位信号到电压信号的反馈回路,能够精确控制延迟电路的时间,使得其延迟时间控制更加精准,结合解码电路的其他部分,从而还原出精确的时钟信号rclk。

94.所述其他部分,与图13中电路相似地,包括脉冲发生器one

‑

shot、时钟触发器和数字信号触发器。其中,脉冲发生器one

‑

shot的输入端连接长短码延迟信号wnpd,输出端连接时钟触发器的重置端s并输出延迟脉冲信号set。时钟触发器的数据端d接地,时钟端连接长短码信号wnp,且通过输出端q输出时钟信号rclk。数字信号触发器的时钟端与时钟触发器的输出端q连接,数据端d与长短码信号wnp连接,输出端q输出数字信号rd。

95.参照图16,其在图15的基础上进一步增加了用于预建立控制电压的电路,包括翻转检测器602、振荡器604(周期为tosc)和数据选择器(mux)608。振荡器604连接数据选择器608的第二输入端(mux的0号端),长短码信号wnp接入数据选择器608的第一输入端(mux的1号端)和翻转检测器602的输入端,翻转检测器602的输出端连接数据选择器608的选择端sel,并以数据选择器608的输出端替换图15中电路的wnp输入。

96.当不通信时,翻转检测器602输出低电平,数据选择器608将振荡器604的输出接入延迟锁定环(包括后侧延迟电路中间级1502、鉴频鉴相器、电荷泵、低通滤波器所形成的电路),并建立电压信号vctrl。

97.当通信时,翻转检测器602输出高电平,数据选择器608将长短码信号wnp接入延迟脉冲电路。

98.电路其他部分与图15中电路相似地,包括脉冲发生器one

‑

shot、时钟触发器和数字信号触发器。其中,脉冲发生器one

‑

shot的输入端连接长短码延迟信号wnpd,输出端连接时钟触发器的重置端s并输出延迟脉冲信号set;时钟触发器的数据端d接地,时钟端连接长短码信号wnp,且通过输出端q输出时钟信号rclk;数字信号触发器的时钟端与时钟触发器的输出端q连接,数据端d与长短码信号wnp连接,输出端q输出数字信号rd。

99.同时,鉴频鉴相器通过两个输出端与电荷泵连接,以输出控制信号up和down。

100.由于在不通信时,延迟锁定环已建立了压控延迟线(包括延迟电路中间级1502)的电压信号vctrl,且该电压信号vctrl与通信时最终的电压信号相近,因此,在长短码信号wnp到来时即可立即实现准确的通信,无需一般时钟数据恢复电路所需的建立时间,实现了快速建立通信。

101.本发明的技术内容及技术特征已揭示如上,然后熟悉本领域的技术人员仍可基于本发明的教导及揭示而作种种不背离本发明精神的替换及修饰,因此,本发明保护范围不限于实施例所揭示的内容,而应包括各种不背离本发明的替换及修饰,并为本专利申请的权利要求所涵盖。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。