1.本发明属于时间同步技术领域,具体地说,涉及一种基于脉宽调制的高精度双向时频比对系统的比对方法。

背景技术:

2.随着科学技术的不断发展、时间同步技术的运用也越发广泛,对时间同步精度的要求也越来越高。尤其在科学研究、现代高精度装备和系统中,时间的精确性和稳定度至关重要。目前国内外常用的授时方式有短波授时、长波授时、卫星授时、网络授时及光纤授时等。

3.由于受大气环境影响,基于卫星的时频传递方式已经逐渐不能满足当前的运用需求;且与传统卫星、长波和网络授时相比,采用光纤信道具有损耗低、传输稳定、带宽大及受外界环境影响较小等优点。因此采用光纤信道作为传输介质的时间同步方式,目前已得到了迅速的发展,成为了实现高精度时间同步的重要方式。其中基于双向比对的光纤时间同步方法是光纤授时中运用最广泛的技术。

技术实现要素:

4.本发明为了提高光纤双向比对的授时精度,提出了一种基于脉宽调制的高精度双向时频比对系统的比对方法,采用pwm调制方式,将时间信号调制到频率信号在同一个信道中传输。通过频率信号的自外差环回比对得到光纤链路噪声,并使用延迟线补偿链路噪声的方式,将稳定的时间信号传递到从端台,并且在本地端补偿链路的传输时延,实现两地之间的时间同步以及频率同源。

5.本发明具体实现内容如下:本发明提出了一种基于脉宽调制的高精度双向时频比对系统的比对方法,基于与参考时间频率源连接的光纤双向比对系统,用于光纤时间同步比对;所述光纤双向比对方法包括以下步骤:步骤1:构建光纤双向比对系统,具体构建方法为:设置主端台、光模块、从端台;在所述主端台中设置第一dpll模块、第一pwm整数分频模块、第一电光/光电转换模块;将所述第一dpll分别连接参考时间频率源、第一pwm整数分频模块、第一电光/光电转换模块;还将所述第一pwm整数分频模块与第一电光/光电转换模块连接;还将所述第一电光/光电转换模块与所述光模块连接;在所述从端台中分别设置第二dpll模块、第二pwm整数分频模块、第二电光/光电转换模块;将所述第二dpll分别连接参考时间频率源、第二pwm整数分频模块、第二电光/光电转换模块;还将所述第二pwm整数分频模块与第二电光/光电转换模块连接;还将所述第二电光/光电转换模块与所述光模块连接;步骤2:使用第一dpll模块接收参考时间频率源发送来的1pps时间信号和频率信号发送到第一dpll模块进行dpll模块锁相;

步骤3:将经过第一dpll模块进行dpll模块锁相后的1pps时间信号和频率信号发送到第一pwm整数分频模块进行pwm调制,将1pps时间信号调制到频率信号中,得到带有时间信息的频率信号;步骤4:使用第一电光/光电转换模块将带有时间信息的频率信号转换为光信号通过光模块发送到从端台的第二电光/光电转换模块上;步骤5:通过第二电光/光电转换模块将接收到的光信号转换为带有时间信息的频率信号,并解调出主端台对应的频率信号和1pps时间信号并发送到第二dpll模块上与第二dpll模块上的本地时钟源输出1pps时间信号和频率信号进行比对,测量得出1pps时间信号在链路往返的时间,并根据测量值计算出时延值,然后对第一dpll模块和/或第二dpll模块进行时延调整实现时间信号的同步。

6.为了更好地实现本发明,进一步地,使用从端台反向调制时间信息和频率信息依次通过第二电光/光电转换模块、光模块、第一电光/光电转换模块发送到主端台,并在主端台进行pwm解调得到从端台的对应的频率信号和1pps时间信号并与主端台本地的频率信号和1pps时间信号进行比对,测量得出1pps时间信号在链路往返的时间,并根据测量值计算出时延值,然后对第一dpll模块和/或第二dpll模块进行时延调整实现时间信号的同步。

7.为了更好地实现本发明,进一步地,在所述步骤1中还进行了ocxo晶振模块的设置,所述ocxo晶振模块设置在所述主端台内并与所述第一dpll模块连接;使用ocxo晶振模块保证第一dpll模块的本地时钟的稳定性。

8.为了更好地实现本发明,进一步地,所述步骤1中还设置了外置tdc测量芯片,所述外置tdc测量芯片设置在主端台中且与所述第一dpll模块、第一电光/光电转换模块连接;采用外置tdc测量芯片用于更高精度测量1pps时延情况以及频率信号的更高精度的时差测试。

9.为了更好地实现本发明,进一步地,所述外置tdc测量芯片采用ad9545芯片。

10.为了更好地实现本发明,进一步地,在所述步骤1中,在第一dpll模块和第二dpll模块中都设置输入时钟选择单元、第一dpll通道模块、第二dpll通道模块、系统dpll通道模块、pps编码器、pps分离器、系统apll模块和cpu控制单元;在所述第一dpll通道模块中设置鉴相器、低通滤波器、第一数字环路滤波器、分配器;将所述鉴相器的输入端连接输入时钟选择单元和分配器,将鉴相器的输出端连接低通滤波器后与cpu控制单元一起与所述第一数字环路滤波器连接;将所述第一数字环路滤波器的输出端与系统dpll通道模块的输出端一起与pps编码器连接;还将所述pps编码器与系统apll和分配器连接;将所述第二数字环路滤波器的输入端连接cpu控制单元,将第二数字环路滤波器的输出端与第一数字环路滤波器的输出端、系统dpll通道模块的输出端一起与所述pps分离器连接。

11.为了更好地实现本发明,进一步地,在所述pps编码器中设置第一可控输出分频器、第一整数分频器;将所述第一可控输出分频器分别与第一环路滤波器、系统dpll通道模块、系统apll模块、第一整数分频器连接;所述第一整数分频器与所述分配器连接。

12.为了更好地实现本发明,进一步地,在所述pps分离器设置有第二可控输出分频

器、第二整数分频器;将所述第一可控输出分频器分别与所述第二数字环路滤波器、第一数字环路滤波器、系统dpll通道模块、系统apll模块连接。

13.为了更好地实现本发明,进一步地,在所述第一pwm整数分频模块和第二pwm整数分频模块都设置有pwm调制解调器、整数分频器;将所述pwm调制解调器与整数分频器连接。

14.本发明与现有技术相比具有以下优点及有益效果:1、本发明实现了发射端和接收端时间信号的校准和同步、频率信号的同源和锁定,提高了光纤双向比对的授时精度;2、本发明采用pwm调制的光纤双向比对技术,能够直接传递频率和数据,在保证频率信号前沿周期性的前提下实现数据传输。也就是频率信号高保证的前提下实现数据传输。

附图说明

15.图1为本发明发射端的逻辑框架图;图2为基于图1的框架增加外置tdc测量芯片和ocxo晶振模块的逻辑框架图;图3为图1和图2的发射端对应的接收端的逻辑框架图;图4为本发明进行pwm调制的示意图;图5为本发明第一dpll模块和第二dpll模块进行dpll锁相的逻辑示意图;图6为本发明pwm编码的示意图;图7为本发明pwm编码的时间信息及通信管理信息时序关系0

‑

0.5s范围的示意图;图8为本发明pwm编码的时间信息及通信管理信息时序关系0.5

‑

1s范围的示意图。

具体实施方式

16.为了更清楚地说明本发明实施例的技术方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,应当理解,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例,因此不应被看作是对保护范围的限定。基于本发明中的实施例,本领域普通技术工作人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

17.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“设置”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;也可以是直接相连,也可以是通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

18.实施例1:本实施例提出了一种基于脉宽调制的高精度双向时频比对系统的比对方法,与参考时间频率源连接,用于光纤时间同步比对;如图1、图3所示,所述光纤双向比对系统包括主端台、光模块、从端台;所述主端台包括第一dpll模块、第一pwm整数分频模块、第一电光/光电转换模块;所述第一dpll分别连接参考时间频率源、第一pwm整数分频模块、第一电光/光电转换模块;

所述第一pwm整数分频模块还与第一电光/光电转换模块连接;所述第一电光/光电转换模块还与所述光模块连接;所述从端台包括第二dpll模块、第二pwm整数分频模块、第二电光/光电转换模块;所述第二dpll分别连接参考时间频率源、第二pwm整数分频模块、第二电光/光电转换模块;所述第二pwm整数分频模块还与第二电光/光电转换模块连接;所述第二电光/光电转换模块还与所述光模块连接。

19.工作原理:光纤双向比对系统的发射端设备将参考时间频率源的高稳定度、高准确度的1pps时间信号和频率信号通过光纤链路传递至接收端设备,接收端设备对本地1pps时间信号和频率信号进行比对、调整。

20.所述发射端中设置有dpll模块、电光/光电转换模块、光发射机;所述接收端中设置有dpll模块、电光/光电转换模块、光发射机。

21.本方案时延校准及时间信号同步原理如下:时间信号以1pps为例,参考时间频率源产生的1pps信号、10mhz频率信号经过dpll模块锁相、pwm调制;1pps信号将会调制到正弦频率信号中,再通过本地电光转换模块以及光发射机将带有时间信息的频率信号转换为光信号。通过光纤链路传递给远地端。在远地端光电转换模块会将光信号转换为带有时间信息的频率信号、通过dpll芯片经事先约定的编码规则,解码恢复出1pps信号以及频率信号。同时1pps通过远地端的光发射机把电信号再次转换为光信号沿着相同的光纤链路回传。在本地端使用光接收机及光电转换模块将回传的光信号转换为1pps输出。输出的1pps信号与本地端钟源的输出的1pps信号进行比对,用来测量1pps在链路往返的时间。并根据测量值计算出能使时间信号同步的时延值。通过dpll芯片调整时延、达到两地之间时间信号同步的效果。

22.实施例2:本实施例在上述实施例1的基础上,如图2、图3所示,为了更好地实现本发明,进一步地,还包括ocxo晶振模块,所述ocxo晶振模块设置在所述主端台内并与所述第一dpll模块连接。

23.为了更好地实现本发明,进一步地,还包括外置tdc测量芯片,所述外置tdc测量芯片设置在主端台中且与所述第一dpll模块、第一电光/光电转换模块连接。

24.工作原理:采用pwm调制的光纤双向比对系统可添加外置tdc测量芯片(ad9545),用于高精度测量1pps时延情况以及频率信号的高精度时差测试。添加高稳ocxo晶振,保证本地时钟稳定性。

25.本实施例的其他部分与上述实施例1相同,故不再赘述。

26.实施例3:本实施例在上述实施例1

‑

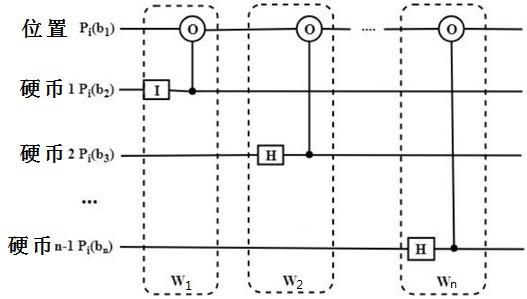

2任一项的基础上,如图5所示,为了更好地实现本发明,进一步地,所述第一dpll模块和第二dpll模块结构一样,都包括输入时钟选择单元、第一dpll通道模块、第二dpll通道模块、系统dpll通道模块、pps编码器、pps分离器、系统apll模块和cpu控制单元;所述第一dpll通道模块包括鉴相器、低通滤波器、第一数字环路滤波器、分配器;所述鉴相器的输入端连接输入时钟选择单元和分配器,鉴相器的输出端连接低通滤波器后与cpu控制单元一起与所述第一数字环路滤波器连接;所述第一数字环路滤波器的输出端

与系统dpll通道模块的输出端一起与pps编码器连接;所述pps编码器还与系统apll和分配器连接;所述第二数字环路滤波器的输入端连接cpu控制单元,第二数字环路滤波器的输出端与第一数字环路滤波器的输出端、系统dpll通道模块的输出端一起与所述pps分离器连接。

27.为了更好地实现本发明,进一步地,所述pps编码器包括第一可控输出分频器、第一整数分频器;所述第一可控输出分频器分别与第一环路滤波器、系统dpll通道模块、系统apll模块、第一整数分频器连接;所述第一整数分频器与所述分配器连接。

28.为了更好地实现本发明,进一步地,所述pps分离器包括第二可控输出分频器、第二整数分频器;所述第一可控输出分频器分别与所述第二数字环路滤波器、第一数字环路滤波器、系统dpll通道模块、系统apll模块连接。

29.工作原理:数字锁相环一般由数字鉴相器(dpd, digital phase detector)、数字环路滤波器(dlf,digital loop filter)、数字压控振荡器(dco,digital control oscillator)三部分组成。数字鉴相器用来比较输入信号与压控振荡器输出信号的相位,它的输出电压是 对应于这两个信号相位差的函数。数字环路滤波器在环路中对输入噪声起抑止作用,并且对环路的校正速度起调节作用。数控振荡器,又称为数字钟。它在数字环路中所处的地位相当于模拟锁相环中的压控振荡器(vco)。但是,它的输出是一个脉冲序列,而该输出脉冲序列的周期受数字环路滤波器送来的校正信号的控制。其控制特点是:前一采样时刻得到的校正信号将改变下一个采样时刻的脉冲时间位置。

30.数字锁相环的基本工作过程如下:1)输入信号 ui(t) 和本振信号(数字压控振荡器输出信号)uo(t) 分别是正弦和余弦信号,他们在数字鉴相器内进行比较,数字鉴相器的输出是一个与两者间的相位差成比例的电压ud(t)。

31.2) 数字环路滤波器除数字鉴相器输出中的高频分量,然后把输出电压uc(t) 加到数字压控振荡器的输出端,数字压控振荡器的本振信号频率随着输入电压的变化而变化。如果两者频率不一致,则数字鉴相器的输出将产生低频变化分量,并通过低通滤波器使dco的频率发生变化。只要环路设计恰当,则这种变化将使本振信号uo(t) 的频率与数字鉴相器输入信号ui(t) 的频率一致。

32.3)最后,如果本振信号的频率和输入信号的频率完全一致,两者的相位差将保持某一个恒定值,则数字鉴相器的输出将是一个恒定直流电压 (忽略高频分量),数字环路滤波器的输出也是一个直流电压,dco的频率也将停止变化,这时,环路处于“锁定状态”。

33.如图5的dpll锁相方案所示:该方案最多将会使用3个dpll通道。系统dpll通道作为源提供给其余两个dpll。在该方案中,一个dpll将会锁定一个参考输入时钟、例如同步以太网时钟或是经光电转换来的带有时间信息的频率时钟;并且该dpll可以产生不同频率的输出时钟跟踪输入的参考时钟。第二个通道用作dco,它由外部处理器控制、或者直接跟踪第一个通道,这样每一个通道都将不会导致任何丢失脉冲或者输出时钟,因为所以的频率变化至少都被一个环路滤波器所限制。dco本振是由本地高稳晶振提供的时钟,同时本地外

置测量芯片通过测量光接收机恢复的时钟与晶振的时钟情况,实现对恒温晶振的锁定。

34.在本方案中,主站根据参考时间源产生的pps,同步dpll产生的1pps,pwm编码pps、时间信息、设备间通信管理信息到时钟信号中发送给从站;从站根据解码产生的解调1pps、时钟信号,同步锁相环产生的1pps、频率信号后,pwm编码发送给主站。这样主从站之间进行时间和频率的双向测量和比对,实现高精度比对。

35.本实施例的其他部分与上述实施例1

‑

2任一项相同,故不再赘述。

36.实施例4:本实施例在上述实施例1

‑

3任一项的基础上,如图4、图6、图7、图8所示,为了更好地实现本发明,进一步地,所述第一pwm整数分频模块和第二pwm整数分频模块都包括pwm调制解调器、整数分频器。

37.工作原理:在本方案中,主站根据参考时间源产生的pps,同步dpll产生的1pps,pwm编码pps、时间信息、设备间通信管理信息到时钟信号中发送给从站;从站根据接收到的频率信号、解码产生1pps信号、时间信息和时钟信号;计算本地的时间、频率差调整本地的时间和频率,然后将本地的时间和频率信号通过上述的pwm调制方式发送给主站。主站解码产生从站环回的1pps,通过测量换回的1pps同本秒的时间差,这个时间差除以2,从而得到从站调整量,主站通过光纤网络传给从站该调整量,从站调整本地秒信号,实现主从对齐。同时也实现了主从站间的频率信号的测量及比对。

38.pwm调制的示意图如图4所示,dpll产生一个标准的频率信号、每个时钟的上升沿都是等周期的,通过改变每个时钟下降沿的位置,实现不同占空比的时钟,不同的占空比表示不同的数值。例如图6所示:逻辑0代表25%占空比,逻辑1代表75%占空比,50%占空比代表未调制。

39.1pps信号所对应的在经调制后的25m频率信号中的的时钟帧头如图4所示。编码时,除了编码产生1pps的帧头,还有接着编码产生时间信息(包括年月日时分秒)以及设备之间的通信管理信息。时间信息及通信管理信息时序关系如图7和图8所示。图7为0

‑

0.5s范围的时间信息及通信管理信息时序关系示意图,图7为0.5s

‑

1s范围内的时间信息及通信管理信息时序关系示意图,图7和图8拼接得到0

‑

1s的一个完整时间周期范围内的时间信息及通信管理信息时序关系示意图。如此,接收端在接收标准频率信号的同时,也可以根据约定的编码规则解码产生数据信息。

40.本实施例的其他部分与上述实施例1

‑

3任一项相同,故不再赘述。

41.实施例5:本实施例还提出了一种基于脉宽调制的高精度双向时频比对系统的比对方法,基于与参考时间频率源连接的光纤双向比对系统,用于光纤时间同步比对;如图1、图2、图3所示,所述光纤双向比对方法包括以下步骤:步骤1:构建光纤双向比对系统,具体构建方法为:设置主端台、光模块、从端台;在所述主端台中设置第一dpll模块、第一pwm整数分频模块、第一电光/光电转换模块;将所述第一dpll分别连接参考时间频率源、第一pwm整数分频模块、第一电光/光电转换模块;还将所述第一pwm整数分频模块与第一电光/光电转换模块连接;还将所述第一电光/光电转换模块与所述光模块连接;在所述从端台中分别设置第二dpll模块、第二pwm整数分频模块、第二电光/光电

转换模块;将所述第二dpll分别连接参考时间频率源、第二pwm整数分频模块、第二电光/光电转换模块;还将所述第二pwm整数分频模块与第二电光/光电转换模块连接;还将所述第二电光/光电转换模块与所述光模块连接;步骤2:使用第一dpll模块接收参考时间频率源发送来的1pps时间信号和频率信号发送到第一dpll模块进行dpll模块锁相;步骤3:将经过第一dpll模块进行dpll模块锁相后的1pps时间信号和频率信号发送到第一pwm整数分频模块进行pwm调制,将1pps时间信号调制到频率信号中,得到带有时间信息的频率信号;步骤4:使用第一电光/光电转换模块将带有时间信息的频率信号转换为光信号通过光模块发送到从端台的第二电光/光电转换模块上;步骤5:通过第二电光/光电转换模块将接收到的光信号转换为带有时间信息的频率信号,并解调出主端台对应的频率信号和1pps时间信号并发送到第二dpll模块上与第二dpll模块上的本地时钟源输出1pps时间信号和频率信号进行比对,测量得出1pps时间信号在链路往返的时间,并根据测量值计算出时延值,然后对第一dpll模块和/或第二dpll模块进行时延调整实现时间信号的同步。

42.实施例6:本实施例在上述实施例5的基础上,为了更好地实现本发明,进一步地,如图1、图2、图3所示,为了更好地实现本发明,进一步地,使用从端台反向调制时间信息和频率信息依次通过第二电光/光电转换模块、光模块、第一电光/光电转换模块发送到主端台,并在主端台进行pwm解调得到从端台的对应的频率信号和1pps时间信号并与主端台本地的频率信号和1pps时间信号进行比对,测量得出1pps时间信号在链路往返的时间,并根据测量值计算出时延值,然后对第一dpll模块和/或第二dpll模块进行时延调整实现时间信号的同步。

43.本实施例其他部分与上述实施例5相同,故不再赘述。

44.以上所述,仅是本发明的较佳实施例,并非对本发明做任何形式上的限制,凡是依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化,均落入本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。