1.本发明涉及用于量子信息处理和存储的设备、架构和系统。

背景技术:

2.本文描述的本发明至少部分地基于量子力学、量子信息和量子计算。对于感兴趣的读者,michael a nielsen和isaac l chuang在“量子计算与量子信息(quantum computation and quantum information)”中详细介绍了基础知识。具体而言,该文献包含量子位的特性和互补碱基中量子测量的基础知识,并介绍了量子纠错和容错量子计算。该文献还可使读者熟悉量子物理学领域中常用的符号。

3.量子计算机是一种用于处理量子信息的设备,其中,量子信息是经典计算机处理的经典信息(例如,离散经典比特,即0和1)的概括。至少对于某些过程,量子计算机有可能比经典计算机强大得多,因为其可以更有效地执行许多操作。

4.在用于处理量子比特(也称为“量子位(qubit)”)的计算机中,每个量子位都可以处于两种状态之一。但是,由于量子位的性质,它们也可以处于这两种状态的叠加中。如果将计算机的每个量子位都置于合适的状态叠加中,则计算机中的整体状态叠加会缩放为2

n

,其中n为量子位的数量。通过将计算机置于这种状态叠加,可以使用诸如grover算法等量子算法更快地解决各种问题。这可以看作是由于这样一个事实,即量子位不是按顺序运行通过每个可能的状态,而是同时处于所有可能的状态组合中。虽然量子位可被认为是经典的0、经典的1或这两种状态的叠加,但量子位可被认为是0、1、...、n

‑

1或这n个状态的任意状态的叠加。

5.通用量子计算机有望加快多项操作的处理时间,例如,因数分解、搜索算法和量子模拟,但此类量子计算机的发展进程受到对量子态控制的高精度要求的阻碍。

6.就量子位而言,原则上任何满足量子位算符和(其中,和为泡利(pauli)算符)的二能级系统都可用于定义量子位。算符的本征态可以是例如基态|g>和激发态|e>。基态是算符的 1本征态,其中,激发态是算符的

‑

1本征态,其中,然而,量子位可以以其本征态的叠加形式存在,|ψ>=α|g> β|e>。量子位在z基下的测量通常将量子位投影到基态或激发态,其概率取决于参数α和β。状态投影可由测量有意地引起,也可是由于量子位与环境的相互作用而无意引起的。这种无意的状态投影会导致量子错误(quantum errors)。因此,可以通过引入随机相位翻转操作(randomphase flip operations)或位翻转操作(bit flip operations)来模拟量子位错误。

7.量子计算机发展的一个主要障碍是退相干(decoherence)——量子态与外部世界的意外相互作用导致量子信息的丢失。量子纠错可用于保护量子信息免受由于退相干和其他噪声源所引起的错误。实际上,可以从多个物理量子位构建逻辑量子位,使得可以比任何

单个物理量子位更精确地处理逻辑量子位。

8.建造量子计算机的一种方法是基于表面码(surface code),其作为稳定子码(stabilizer code)运行。理论上,表面码具有非常显著的优势,因为它们对局部错误的容错性相对较高。在典型的表面码中,物理量子位使用一系列物理量子位受控非(control

‑

not(cnot))操作纠缠在一起,随后对纠缠态的测量提供了纠错和错误检测的手段。一组以这种方式纠缠在一起的物理量子位被用来定义一逻辑量子位,由于纠缠和测量,逻辑量子位的性能远远优于底层物理量子位。

9.有关表面码量子计算的介绍,包括“元格(plaquettes)”的定义,读者可以阅读fowler等人发表的“surface codes:towards practical large

‑

scale quantumcomputation”,(physical reviewa,第86卷,第3期,032324,2012年9月18日)。

10.在典型的二维表面码架构中,多个“数据量子位(data qubits)”中散布着多个“辅助量子位(ancillary qubits)”(也被称为“测量量子位(measurement qubits)”)。图1中示出了一种典型的表面码架构100。在纠缠物理量子位的二维阵列中,多个数据量子位110(图中示为黑色圆圈)中散布着多个辅助量子位120(图中示为白色圆圈)。数据量子位110与辅助量子位120之间的直接交互(可以是直接交换交互(direct exchange interaction))用于操纵架构100的量子信息。远离边界处,每个数据量子位110耦合至四个辅助量子位120,并且,每个辅助量子位120与四个数据量子位110耦合。辅助量子位120用于稳定和操纵数据量子位110的量子态。可以通过在最近邻量子位(涉及数据量子位110和辅助量子位120两者)之间执行两个量子位测量的组合来实现量子逻辑门,例如,受控非门(controlled

‑

not gate,cnot)、数据量子位上的单量子位操作以及辅助量子位上的测量。

11.虽然图1所示的表面码架构在理论上是容错的,但根据表面码架构所依赖的物理系统的性质,仍然可能有例如大量电荷泄露到计算子空间之外的物理状态。泄漏可能是由于,例如,阵列的一个位置处的电子隧穿到相邻位置。这种泄漏会导致计算错误,无法通过标准表面码协议进行纠正。

12.本发明提供了能够减轻上述问题中的一些问题的设备、架构和装置。

技术实现要素:

13.根据本发明的一方面,提供了一种设备,该设备适用于量子信息处理。该设备包括用于限制用作数据量子迪特(qudits)的自旋电荷载流子的第一多个限制区或称为“第一组限制区”。该设备还包括用于限制用作辅助量子迪特(qudits)的自旋电荷载流子的第二多个限制区或称为“第二组限制区”,所述第二组限制区中的每个限制区都可耦合至用于测量辅助量子迪特(qudit)的测量装置。该设备还包括用于限制自旋电荷载流子的第三多个限制区或称为“第三组限制区”。所述第三组限制区中的每个限制区位于所述第一组限制区中的第一限制区与所述第二组限制区中的第二限制区之间,适于介导所述第一限制区的数据量子迪特(qudits)与所述第二限制区的辅助量子迪特(qudits)之间的相互作用。该设备进一步包括一个或多个电荷库。所述第三组限制区中的每个限制区可耦合至所述一个或多个电荷库中的电荷库。

14.本发明的设备可用于表面码量子信息处理。在以下整个描述中,参考表面码量子信息处理和存储描述了本文公开的设备以及用于控制和使用这些设备的方法。然而,本领

域技术人员将理解,本文公开的设备可以与其他量子信息处理方法一起使用,例如,二维颜色码方案(2

‑

d colour code scheme)。

15.有利地,如本领域技术人员将理解的,本文公开的设备为量子信息处理提供了许多优点。特别是,这些设备能够减少泄漏错误(leakage errors)。

16.术语“泄漏错误”是指量子系统逃出计算子空间的状态。典型的量子纠错协议并非旨在处理泄漏错误。如果没有任何纠错协议,即使这种泄漏错误发生的几率非常小,它们也会随着计算的进行而持续存在和累积,并最终破坏存储在架构中的逻辑量子位。人们已经提出了处理泄漏错误的一般方案,其中对泄漏错误的特性进行了各种假设。为了纠正泄漏错误,可以检测泄漏错误并替换泄漏的量子位。或者,可以将泄漏减少协议(leakage

‑

reduction protocols)应用于所有量子位,理想情况下,这将在不影响正常量子位的情况下恢复泄漏的量子位。使用这些方法,可以将泄漏错误转化为可以由量子纠错码处理的计算错误。实际上,泄漏错误的来源、影响和解决方案非常依赖于硬件。

17.本文所述的设备对于泄漏错误具有固有的鲁棒性。本文所述的设备包括用于限制自旋电荷载流子的第三组限制区,并且,还包括一个或多个电荷库。所述第三组限制区中的每个限制区位于所述第一组限制区中的第一限制区与第二组限制区中的第二限制区之间,并适用于介导所述第一限制区的数据量子迪特(qudits)与所述第二限制区的辅助量子迪特(qudits)之间的相互作用。所述第三组限制区中的每个限制区可耦合至所述一个或多个电荷库中的电荷库。如果有电荷载流子从相邻的限制区泄漏到所述第三组限制区中的一限制区,则电荷库可以耦合至该限制结构以重置系统的电荷。通过这种方式,该设备能够减少泄漏错误。

18.在整个本发明中,使用了术语“限制区”。本领域技术人员将理解的是,这样的术语应该被广义地解释为可以限制或包含作为量子客体处理的电荷载流子的区域,但是这种限制区的能量边界可是可调整的,例如,使用电场。限制结构可允许量子隧穿(quantum tunnelling)。术语“区”或“区域”应理解为具有任何合适的维度。例如,一限制区或限制区域可包括量子点(其通常被认为是“零维”结构,但更恰当地是在所有三个维度上都小但有限范围的势阱(potential well))或量子阱(quantum well)。因此,限制区域/限制结构可以被认为是可限制电荷载流子的低维特征。

19.在整个本发明中,使用了术语“数据量子迪特(data qudit)”。数据量子迪特可被认为是一个量子信息单元,但在本发明中并不使用经典的读出/测量装置直接读取。相比之下,“辅助量子迪特(ancillary qudit)”可被视为用于测量的量子迪特。可以使用辅助量子迪特(ancillary qudits)的仔细操作来读取或处理存储在数据量子迪特(data qudits)中的信息。术语“数据量子迪特”和“辅助量子迪特”分别是唯一可用逻辑状态是0、1或0和1的叠加的数据量子迪特和辅助量子迪特。

20.在整个本发明中,第三组限制介体的限制区有时被称为介体区,或者在本文描述的一个示例中,被称为介体点。这种介体区适用于介导相邻限制区中的数据量子迪特与辅助量子迪特之间的相互作用。

21.介导的相互作用可被理解为是指相邻限制区之间的介导交换耦合使得自旋电荷载流子可(当设备使用时)在位点(sites)之间隧穿。

22.本文使用的术语“介导的相互作用”可被本领域技术人员理解为包括基本上同时

影响数据量子迪特(data qudit)和辅助量子迪特(ancillary qudit)的交互或相互作用。例如,所述介体区被配置成当调到正确的能级时基本上同时与相邻数据区和相邻辅助区相互作用,以使得实现数据区与介体区之间、及介体区与辅助区之间的耦合相互作用,并由此通过扩展在数据区与辅助区之间形成耦合。

23.在本文所述的设备中,所述第三组限制区中的每个限制区可耦合至所述一个或多个电荷库中的一电荷库。在这个意义上的可耦合可被认为是指可充电耦合(chargeably coupleable)。例如,一电荷库可耦合至第三组限制区中的限制区,使得电荷载流子可在所述限制区与所述电荷库之间移动。所述耦合可例如通过调节限制区与电荷载流子之间的相互作用强度来实现。

24.每个量子迪特(qudit)可包括一量子比特(qubit,量子位)。

25.第一组限制区中的每个限制区可包括量子点(在本文中通常称为“数据点”)。所述第一组限制区的每个量子点的直径可在5nm

‑

100nm之间,例如,在28nm至60nm之间,以提供与标准cmos处理兼容的便利尺寸。

26.第二组限制区中的每个限制区可包括量子点(在本文中通常称为“辅助点”)。

27.人们已为领先的量子信息处理平台提出了表面码架构,包括超导量子位(superconducting qubits)和陷俘离子(trapped ions)。据估计,使用表面码执行non

‑

trivial shor分解算法可能需要超过2x108个具有门错误率(gate error rate)约为10

‑3的量子比特。如果要尝试使用超导量子位构建用于表面码处理的设备,则最终的设备尺寸将非常大(面积约为平方米量级)。对于非固态量子位,例如,陷俘离子,所需的架构可能比超导量子位的架构大几个数量级。制造这种尺寸的量子处理器和/或创建所需的低温环境远远超出了当今的技术。然而,基于量子点(例如,硅量子点)并针对类似数量的量子位进行缩放的量子信息处理设备可以比超导量子位的小得多(面积约为平方毫米量级)。如此高的量子位密度和利用现有半导体集成电路行业可用技术的可能性使硅量子点自旋(ss)量子位成为可扩展量子信息处理设备的有希望的候选者。

28.第二组限制区中的每个限制区可包括一对量子点。提供一对量子点可产生若干优点,如下文具体实施方式部分中进一步详述的。

29.第三组限制区中的每个限制区可包括量子点(其可被称为“介体量子点”或“介体点”)。介体量子点可适用于限制一个或多个自旋电荷载流子,例如,两个自旋电荷载流子。在一些示例中,所述第三组限制区中的每个限制区适于限制四个自旋电荷载流子。限于介体点的电荷载流子不用于携带量子信息。

30.用ss量子位放大设备带来了许多挑战。ss量子位的高量子位密度给经典控制线的封装、避免串扰和散热带来了挑战。例如,如果考虑图1的传统架构包含硅量子点,则可能会由于点之间的泄漏而引入噪声和其他错误,并且使用经典控制线与各量子点交互而不干扰其他量子点的难度令人望而却步。虽然在本领域中已经就如何实现这种基于ss量子位的表面码架构提出了一些建议,但这些建议中的每一个都有其自身的缺点。更重要的是,这些架构都没有解决如何减轻泄漏错误的问题(其中,泄露错误是指量子系统逃出计算子空间)。ss量子位的控制涉及调节隧穿势垒(tunnelling barrier)、改变在位能(on

‑

site energy)和/或使电子从一个位置穿梭到另一个位置,所有这些操作都容易导致电子落在错误的量子点上,这相当于电荷泄漏错误(charge leakage error)。在已知的表面码架构中,纠错循

环的成功实现在很大程度上依赖于系统处于正确电荷配置的假设。如果发生一次电荷泄漏事件,则错误可能会以无法控制的方式传播。由于此类泄漏错误无法通过通常的量子纠错协议进行纠正(甚至可能会加剧),因此,即使这些泄漏错误发生的概率非常小,它们也会累积并最终破坏表面码。

31.有利地,在本发明的示例中,本文中的设备包括多个介体点,所述多个介体点中的每个介体点都被定位用于介导相邻数据点与相邻辅助点之间的交互。因此,所述介体点有助于将数据点与辅助点隔开,同时仍然能够实现数据点和辅助点之间的交互。数据点与辅助点之间的这种间隔有助于充分隔离数据点和辅助点,使得可以使用经典控制线来寻址各个量子位。此外,在本发明的示例中,每个介体点可耦合至电荷库以重置设备,从而消除泄漏错误。

32.在本发明的示例中,至少一些介体点是细长的量子点。因此,每个介体点可基本上在相邻数据点和辅助数据点所在的线的方向上被拉长。即,每个介体点可在相邻数据点和相邻辅助点的方向上被拉长。细长的介体点有助于进一步隔开数据点和辅助点,从而允许在其间定位经典控制线。

33.每个介体点/介体量子点可具有在5

‑

100nm之间且不小于数据点的直径的第一维度、及在50nm

‑

1000nm之间的第二维度。需要说明的是,第二维度的下限一般也受第一维度的选择值的限制,如果小于50nm。

34.根据本文所述的设备的示例,第三组限制区中的每个限制区位于第一组限制区中的第一限制区与第二组限制区中的第二限制区之间;并且,所述第一限制区与所述第二限制区之间的距离可介于50nm至1000nm之间。

35.根据本文所述的设备的示例,第三组限制区中的每个限制区位于第一组限制区中的第一限制区与第二组限制区中的第二限制区之间;并且,第三组限制区中的所述限制区与所述第一限制区之间的距离介于0.5nm与20nm之间;第三组限制区中的所述限制区与所述第二限制区之间的距离介于0.5nm与20nm之间。

36.自旋电荷载流子可以是电子。自旋电荷载流子可以是空穴(holes)。自旋电荷载流子可以是在数据量子位位置注入的施体离子或受体离子。

37.本发明的设备还可包括测量设备/测量装置。所述测量装置可被配置成测量一个或多个辅助量子迪特的状态。

38.本发明的设备可用于表面码量子信息处理。

39.本发明的设备可被配置成保持跨所述第一组限制区和所述第二组限制区的电荷稳定性。

40.本发明的设备还可包括控制器,其被配置成使磁场被施加至所述第一组和第二组限制区,以分离第一组和第二组限制区中的电荷载流子的自旋态的能级。

41.本发明的设备还可包括控制器,其被配置成使振荡磁场被施加至所述第一组和第二组限制区。该振荡磁场可具有与所述第一组限制区中的电荷载流子的塞曼分裂基本匹配的频率。这种振荡磁场可用于执行单量子位逻辑门操作。

42.本发明的设备还可包括控制器,其被配置成使所述第三组限制区中的至少一个限制区耦合至一电荷库,以使得能够在所述电荷库与所述第三组限制区中的所述至少一个限制区之间转移电荷载流子。

43.本发明的设备还可包括多个微磁体,每个微磁体布置成靠近所述第一组限制区中的限制区。本领域技术人员将理解,术语“微磁体”应被解释为任何合适尺寸的磁体,例如,纳米级尺寸的磁体,而不应被解释为仅限于微米级尺寸的磁体。有利地,可以使用微磁体向第一组限制区中的限制区提供高度局部化的磁场梯度。这种磁场梯度对于加快实现量子逻辑门操作所需的时间很有用。

44.根据本发明的一方面,提供了一种操作如本文所述的设备的方法。该方法包括使所述第三组限制区中的限制区耦合至所述一个或多个电荷库中的电荷库,以使得能够在所述电荷库与所述第三组限制区中的所述至少一个限制区之间转移电荷载流子。通过将限制区耦合至电荷库,可以去除所述限制区中的过量电荷载流子,或者可以向所述限制区提供额外的电荷载流子,从而能够纠正设备中的泄漏错误并确保保持电荷稳定性。

45.使第三组限制区中的限制区与所述一个或多个电荷库中的电荷库耦合可包括:将所述第三组限制区中的所述限制区耦合至所述电荷库。

46.使第三组限制区中的限制区与所述一个或多个电荷库中的电荷库耦合可包括使所述耦合作为稳定子操作(stabiliser operation)的一部分。有利地,这有助于减少执行稳定子操作中的错误,因为电荷迁移错误被定期纠正。

47.根据本发明的一方面,提供了一种计算机可读介质,该计算机可读介质上存储有指令,当由处理器执行时,该些指令使所述处理器执行如本文所述的方法。所述计算机可读介质可包括非暂时性计算机可读介质。

48.可在计算机可读介质或计算机程序产品上向一装置(例如,计算机)提供用于执行如本文所述的方法的计算机程序和/或代码/指令。所述计算机可读介质可以是,例如,电子、磁、光、电磁、红外或半导体系统,或用于数据传输的传播介质,例如,用于通过因特网下载代码。或者,所述计算机可读介质可以采用物理计算机可读介质的形式,例如,半导体或固态存储器、磁带、可移动计算机软盘、随机存取存储器(ram)、只读存储器(rom)、硬磁盘和光盘,如,cd

‑

rom、cd

‑

r/w或dvd。

49.根据本文提出的教导,本发明所属领域的技术人员将想到本文阐述的本发明的许多修改和其他实施例。因此,应当理解,本发明不限于本文公开的具体实施例。此外,尽管本文提供的描述在元件、步骤和/或功能的某些组合的情况下提供了示例性实施例,但是在不背离本发明的范围的情况下可以由替代实施例提供。

50.附图简要说明

51.下面将参照附图仅以示例的方式对本发明的实施例进行说明。附图中:

52.图1示出了典型、已知的表面码架构,包括数据量子迪特(data qudits)和辅助量子位(ancillary qudits);

53.图2示出了根据本发明的一实施例的表面码架构;

54.图3示出了图2架构中的量子点之间的能级和跃迁;

55.图4示出了实现control

‑

z门的量子电路图;

56.图5示出了实现control

‑

z门的量子电路图;

57.图6a示出了表面码架构的“单位单元(unit cell)”,示出了图2所示组件的进一步组件;

58.图6b是由如图6a所示的多个单位单元形成的表面码架构;

59.图7a示出了用于量子信息处理的设备的第一层的一部分;

60.图7b示出了图7a所示的用于量子信息处理的设备的第二层的一部分;

61.图7c示出了图7a所示的用于量子信息处理的设备的第三层的一部分;

62.图7d示出了图7a所示的用于量子信息处理的设备的第四层的一部分;

63.图7e示出了图7a所示的用于量子信息处理的设备的第五层的一部分;

64.图7f示出了图7e所示设备上量子点的位置。

65.图8a示出了图7e所示设备架构的第一视点图示;

66.图8b示出了图7e所示设备架构的第二视点图示;

67.图8c示出了图7e所示设备架构的第三视点图示;

68.图9示出了用于实现稳定子检查的量子电路图;

69.图10示出了另一用于量子信息处理的设备的一部分,特别是一单位单元;

70.图11示出了另一用于量子信息处理的设备的一部分,特别是一单位单元;

71.图12是控制器的方框图;及

72.图13示出了用于量子信息处理的另一设备的一部分,特别是一单位单元,特别是如图7e所示的包括磁体的单位单元。

73.在整个说明书和附图中,相同的附图标记表示相同的部件。

具体实施方式

74.本发明涉及一种改进的用于量子信息处理的设备。虽然下文中描述了各种实施例,但本发明并不限于这些实施例,本领域技术人员将理解在不脱离本发明的范围的情况下可以对这些实施例进行变型。

75.出于讨论的目的,下文描述了用于处理基于量子位的量子信息的设备,特别是硅量子点自旋量子位(silicon quantum dot spin qubits,其中,电子自旋态包含信息)。因此,描述的设备包括:用于限制用作数据量子位的电子的第一多个量子点(数据点),其在本文中也被称为第一组量子点(数据点);用于限制用作辅助量子位的电子的第二多个量子点(或量子点对)(其在本文中也被称为第二组量子点(数据点)),也被称为辅助点;用于限制电子的第三多个介体量子点(mediator quantum dots,在本文中也被称为第三组介体量子点),每个介体量子点位于数据点与辅助点之间,用于介导数据点与辅助点之间的相互作用;以及一个或多个电荷库,其中,每个介体量子点可耦合至电荷库。

76.图2示出了根据一示例的二维阵列200。阵列200可形成在用于量子信息处理的设备内/上。该示例的表面码架构200包括用于限制用作数据量子位的自旋电荷载流子的第一组限制区。特别地,第一组限制区包括多个限制结构,在该示例中,这些限制结构是量子点,在下文中关于该示例被称为数据点210。

77.每个数据点210被电子(未示出)占据,所述电子的自旋态代表一物理数据量子位。恒定磁场可穿过阵列200,基本上垂直于该阵列的平面(在将被视为z方向的方向上),以便去除数据点中电子的自旋态的简并(degeneracy)。在该示例中,阵列200被认为在x和y方向上延伸。

78.单量子位逻辑门操作可通过电子自旋共振(esr)执行,其中,施加垂直于z方向(例如,沿x方向)且频率与电子自旋的塞曼分裂(zeeman splitting)相匹配的振荡磁场来驱动

其旋转。单量子位可寻址性可通过斯塔克偏移(stark shift)改变单个自旋的共振频率来实现。单量子位esr门的保真度已被证实可高达99.9%,但可能相对较慢,具体取决于所施加的振荡磁场的强度。

79.出于该示例的目的,数据点210被认为是近似圆形的。数据点210的直径约为50nm。如此小的尺寸将导致大的库仑排斥(coulomb repulsions)u~10thz,防止数据点的双自旋占据。

80.阵列200还包括用于限制用作辅助量子位的自旋电荷载流子的第二组限制区。特别地,第二组限制区中的每个限制区均包括两个限制结构,在该示例中,所述两个限制结构包括量子点。即,在图2所示的示例中,第二组限制区中的每个限制区包括一对量子点220,其在下文中被称为辅助点220。每个辅助点可耦合至测量装置(表示为240),测量装置用于测量存储在辅助点中的电子的量子态。本示例的每个辅助点220与数据点210的尺寸基本相同。也就是说,每个辅助点220具有大约50nm的直径。

81.辅助量子位由成对辅助点220中电子对的自旋态表示。通过在单重态初始化设备,如果错误导致稳定子检查失败,则将辅助点中电子对的自旋态转换为三重态。由此,可以使用从一个点到另一个点的泡利自旋阻塞自旋(pauli spinblockade spin)相关隧穿来确定稳定子检查的结果。

82.可耦合至辅助点220的测量设备240用于隧穿结果(tunnelling outcome)的色散读出(dispersive readout)。辅助量子位通过将辅助(ancilla)配置成使得两个可用量子点220之一被两个电子双重占据来进行初始化。在这里,基态是单重态,可以通过(1,1)

‑

(0,2)电荷跃迁附近的“热点”弛豫快速制备。

83.这种双点辅助量子位与单点辅助量子位相比有若干优点。

84.首先,当使用单个辅助点220代替一对辅助点220时,单点辅助的测量读出通常通过与自旋相关的至相邻读出点的隧穿来实现。在表面码中,这意味着辅助点旁边需要有读出点以及四个数据点。另一方面,对于诸如阵列200中的双点辅助,每个辅助点220将仅连接至两个数据点210和另一个辅助点220。因此,当使用双点辅助时,二维阵列要比使用单点辅助时不混乱得多。

85.第二,当在z(x)基上准备和测量时,单点辅助可用于检测x(或z)错误,而在单重态准备时双点辅助可用于检测x错误和z错误,因为x和z错误都会将单重态变成三重态之一。这意味着可以将所有辅助全体初始化为相同的状态并以相同的方式对其进行测量,而不管它们对应于哪个稳定子检查。在不需要改变测量基的情况下,还减轻了将哈达玛门(hadamard gate)应用于辅助的需要。与单点辅助情况不同,z(x)基上的初始化和测量不受z(x)误差的影响。

86.第三,在两个自旋的交换下对称的操作不能将量子态带出单重态(交换

‑

反对称(exchange

‑

antisymmetric))或三重态(交换

‑

对称(exchange

‑

symmetric))子空间。因此,全局esr(global esr)(单量子位门)可应用于所有数据量子位而不影响双点辅助,这对于表面码的x和z稳定子检查之间的切换很有用。由于两个辅助点自旋之间的残余交换相互作用(residue exchange interaction),双点辅助的初始化和测量也不太容易受到噪声的影响。

87.第四,辅助双点与两个数据量子位之间的相互作用可以基本上并行发生,将执行

稳定子检查所需的时间减半。

88.阵列200还包括用于限制自旋电荷载流子的第三组限制区。在图2所示的示例中,第三组限制区包括多个细长的双电子量子点,其用于介导数据量子位和辅助量子位之间的相互作用。即,第三组限制区中的每个限制区包括位于数据点与辅助点之间的细长型量子点,下文中将其称为介体点(mediator dot)230,并且,该介体点限制两个电子。

89.出于使用图2所示的架构200的目的,限制在介体点230中的电子不携带任何量子信息——图2所示的架构200的计算子空间包括数据点210和辅助点220中的电子的自旋态。

90.为了处理量子信息,需要两个量子位门,使得辅助量子位与数据量子位相互作用。这两个量子位门通过数据点210与辅助点220之间经由介体点230的介导交换耦合实现,这在图3中进行了说明。

91.图3示出了三点系统。图3示出了三个量子点的能级,左侧为点l,中间为介体点230,右侧为点r。左侧的点l可代表数据点210,右侧的点r可代表辅助点220(即一对辅助点220的一半)。或者,左侧的点l可代表辅助点220,右侧的点r可代表数据点210。在这个三点模型系统中有四个电子。每侧的点(l和r)都填充了轨道l/r中的一个电子。中间的介体点230将两个电子限制在轨道1中,而轨道2中没有电子处于其基态。出于本讨论的目的,假设两侧的点处的电子

‑

电子排斥能非常大(由于它们的尺寸小),以至于在两侧的点中不可能有电子的双重占据。图3中的箭头代表可能发生的电子跳跃,标注表示从基态跃迁的能量消耗。

92.两侧的点中的电子以如下交换耦合强度交互:

[0093][0094]

其中,t

ab

为从轨道a到轨道b的隧穿能量(tunnelling energy),而δ

r

、δ

m

和δ

l

是图3中所示的各电子跃迁所需的能量。

[0095]

在该示例中,介体点230具有大约50nm

×

300nm的尺寸,这意味着δ

m

~10ghz的介体量子跃迁能量。介体点230与数据/辅助点之间的间距大约为10nm,导致t~1ghz的隧穿能量。通过调节介体点230的在位能(on

‑

site energy),可以同时改变δ

r/l

的值,从而控制交换相互作用的强度。δ

r/l

的下限是隧穿能量,上限是数据点的库仑排斥能。相应地,出于本示例的目的,可以选择δ

r/l

=δ

on

=10ghz来开启交换相互作用,而选择δ

r/l

=δ

off

=3thz来关闭交换相互作用。

[0096]

使用等式1,开启时,交换相互作用的强度为:

[0097][0098]

关闭时,交换相互作用的残余强度为:

[0099][0100]

如此小的残余交换相互作用会导致错误的概率为如下量级,远低于表面码的阈值,因此在接下来的讨论中可以安全地忽略。

[0101][0102]

为了控制介导交换,只需要调节介体点的在位能,而无需调节点之间的隧穿能量。有利地,这意味着不需要在点之间实施隧穿门(由于隧穿门具有小特征尺寸,因此,在点之间实施隧穿门是比较困难的,并且会增加经典控制线的混乱度)。

[0103]

如果所施加的(z向)磁场包含梯度(或者,如果g因子中存在梯度),则两侧的点l和r将具有不同的zeeman分裂,出于本讨论的目的,将其表示为ω。当ω被调节为满足ω<<j时,交换相互作用使得可以实现门。这将在此处作简要说明。

[0104]

两个自旋态的相互作用的哈密顿量(hamiltonian)可以建模为:

[0105][0106]

等式5的第一项可被称为h0,表示zeeman分裂。第二项可被称为h

ex

,表示交换相互作用。zeeman分裂h0可被进一步拆分成:

[0107][0108]

其中,(等式7)。

[0109]

等式6右侧的第一项可被称为h

z

,即平均zeeman分裂。等式6右侧的第二项可被称为h

δ

,即“zeeman分裂梯度”。

[0110]

在ω<<j的状态下,哈密顿算子h

z

可与哈密顿算子h

ex

交换,因此,在交互图(旋转坐标系)中,交换哈密顿量可以写为:

[0111][0112]

因此,在旋转坐标系中进行交换相互作用与在实验室坐标系(lab frame)中进行交换相互作用是一样的。由于h

ex

的演化算符由下式给出:

[0113][0114]

swap门对应于而门对应于

[0115]

发明人分析了由于不精确的脉冲定时或电荷涨落而导致的在应用交换相互作用中的误差,并且发现该误差可以忽略不计。

[0116]

单量子位z旋转与门的组合可用于实现control

‑

z门。图4示出了使用单量子位z旋转和门实现control

‑

z门的量子电路。

[0117]

如果在各向同性提纯硅衬底上构建图2的架构200,则,由于其无核自旋环境,可以进一步提高量子点210与220之间的这种介导交换相互作用的保真度。

[0118]

为了解决单个量子位的问题,需要该量子位的谐振频率与其他量子位的谐振频率之差大于2khz左右的esr峰宽。为了使用电门控斯塔克偏移(stark shift)实现这一点,需要改变约0.1mv的顶栅电压,其大致对应于在位能改变约5ghz。这远小于δ

off

~3thz,因此在尝试实现一个量子位逻辑门时不会导致任何不需要的交换相互作用。

[0119]

阵列200还包括若干个局部电荷库250。如图2所示,每个电荷库250可耦合至四个介体点230。电荷库250充当电子的源极和漏极。当量子点和电荷库的能级被调至正确的水平时,可以等待系统松弛至其基态以初始化系统。

[0120]

电荷库250还可用于恢复系统的电荷配置,其将在下文中作进一步说明。

[0121]

虽然上面讨论了与实现单量子位逻辑门相关的电子自旋共振的使用,但实现单量子位门的另一种方法是通过电偶极自旋共振(edsr)。尽管图2中未示出,但可以将微磁体(1300,图13)放置在量子点附近以产生磁场梯度。微磁体可以是纳米级尺寸,或任何其他合适尺寸的磁体。当使用振荡电场移动量子点中的电子时,电子本身将会经历有效的振荡磁场,而振荡磁场又会驱动自旋旋转。edsr可以比esr快一个数量级以上(>10mhz)。可以实现保真度约为99.9%的单量子位edsr门。

[0122]

为了使用这种表面码架构执行量子信息处理,不需要将任何单量子位门应用至辅助点220。因此,也不需要在辅助点220处放置任何微磁体。仅通过在数据点210处放置微磁体,就可以在数据点210和辅助点220之间产生较大的zeeman分裂梯度。当ω>>j时,这两种点之间存在由交换相互作用介导的类偶极

‑

偶极相互作用(dipole

‑

dipole like interaction),可用于实现下面将简要说明如何实现s。

[0123]

使用等式5,描述算子h0(没有交换相互作用)的矩阵由下式给出:

[0124][0125]

因此,e

z

确定了平行自旋子空间中的本征能,而ω确定了反平行自旋子空间中的本征能。交换哈密顿量可以用以下矩阵表示:

[0126][0127]

在平行自旋子空间中,两种状态的能量都会上移j/2。在反平行自旋子空间中,如果ω>>j,则h

ex

可被视为h0的微扰。使用一阶微扰理论,反平行自旋态的本征能量偏移量为0。

[0128]

因此,对于一阶近似(first order approximation,其中,本征态不改变,并且,只考虑本征能的一阶偏移(first order shift)),交换哈密顿量(其对于一阶近似为本征能的偏移)变为:

[0129][0130]

其为偶极

‑

偶极相互作用。要注意的是其也可与h0交换,因此,其旋转坐标系形式与其实验室形式相同。

[0131]

允许此哈密顿量在π/j时间段内演化导致可表示为如下等式的矩阵形式的算子s:

[0132][0133]

因此,当微磁体位于数据点附近时,可以使用s操作实现control

‑

z门。图5示出了使用s操作和单量子位z旋转来实现control

‑

z门的量子电路。

[0134]

由于在本文所述的架构中,例如,架构200中,微磁体被介体点和辅助点隔开,与没有介体点的密集结构相比,杂散磁场影响其他数据点的问题大大减少。

[0135]

微磁体可能会损坏任何涉及电子穿梭的架构,因为在杂散场内移动电子会旋转穿梭电子的自旋。在本文描述的架构中,电子的有意穿梭仅在读出期间发生在辅助双点220处,其中,与任何微磁体有合理的距离并且穿梭距离非常短。因此,在辅助点220处的穿梭过程中由微磁体引起的噪声可以忽略不计。

[0136]

在一些示例中,可以虚拟地执行单量子位z旋转中的一个或多个。也就是说,可以通过将旋转参考系移动给定相位以虚拟方式实现某些z旋转。这种z旋转基本上没有错误并且需要零时间。这将对应于向任何后续的x、y门脉冲添加相位偏移,并在虚拟z旋转后将所有后续的双量子位门切换至新的旋转坐标系中。

[0137]

到目前为止,总而言之,已描述了包括用于实现表面码的架构200的设备,以及在该架构上实现control

‑

z门的两种方式。

[0138]

下面将简要讨论与图2的架构200相关的泄漏错误。

[0139]

在图2的架构中,计算子空间是基电荷组态(ground charge configuration)中数据点210和辅助点220中的电子的整个自旋空间。这种架构中的任何泄漏错误都是由电荷迁移引起的,电荷迁移将架构从电荷基态带到更高能量的电荷态。电荷基态仅在交换相互作用期间(即,在执行两个量子位门相互作用时)与更高能量的电荷态耦合,因此,本讨论仅考虑在交换相互作用期间发生的泄漏。

[0140]

更具体地说,如果考虑上述与图3相关的三点系统,使用(n

l

;n

m

;n

r

)分别表示点l、介体点和点r上的电荷数,则泄漏错误对应于从基电荷组态(1;2;1)到更高能量的电荷组态(1;3;0)或(0;3;1)。回顾一下,量子位点中的电子

‑

电子排斥能远高于架构200中的任何其他能量,因此,数据点210或辅助点220中的双重占据受到严重抑制,使得当以基态开始时无需考虑电荷自介体点迁移至数据点210或辅助点220。

[0141]

任何泄漏的状态都会通过各种弛豫机制自然地衰减回较低的能量状态,其时间尺度由半导体量子点中电荷量子比特的t1时间表示。si/sige双量子点中的电荷弛豫时间已在别处进行了测量,其显示出对轨道之间的隧穿能量的强烈依赖和对轨道之间的失谐的弱依赖。对于图2的架构200的当前讨论中感兴趣的隧穿能量机制(t~1ghz),弛豫时间约为10ns,这远短于设备中的其他时间尺度(所有的门都以微秒的时间尺度运行)。因此,可以假设一旦在交换相互作用期间发生泄漏错误(电荷从数据点210或辅助点220逸出),就会迅速发生弛豫过程,在该过程中,相邻介体点之一(不一定是电子逃逸到的介体点)中的电子向下跳跃以填充“空”数据点210或辅助点220。这样的弛豫过程因此将数据点210和辅助点220恢复到单独占据状态,从而恢复到计算子空间。

[0142]

因此,随着弛豫过程将电荷载流子返回到计算子空间中,任何泄漏错误都可以被

视为由表面码处理的计算错误,而无需额外开销,例如,泄漏错误检测和主动纠正,或无需任何泄漏减少协议的应用。因此,图2的架构200对于泄漏错误具有固有的鲁棒性。

[0143]

在弛豫过程将电荷恢复到数据点210或辅助点220之后,介体点230中可能会有缺失或额外的电子,这将导致有缺陷的交换门。然而,每个介体点230可耦合至一电荷库(其可以是与最初用于填充量子点阵列的电荷库相同的电荷库)以将丢失的电子恢复到介体点230或从介体点230移除额外的电子。由于介体点230中的电子在计算子空间之外(即不被视为携带任何相关量子信息),因此,与电荷库的这种耦合极不可能引入任何进一步的误差。

[0144]

与图2的架构200不同,在诸如图1的架构100之类的依赖于数据点110与辅助点120之间的直接交换相互作用(即,没有任何介导交互)的架构中,任何从例如数据点110泄漏的电子总是会迁移到辅助点120。即使试图通过将数据点110或辅助点120连接到电荷库来恢复泄漏错误,存储在量子位中的量子信息也会被破坏。

[0145]

图6a示出了类似于图2的表面码架构的表面码架构的单位单元。图6b示出了使用图6a的单位单元的表面码网格。从图6a和图6b中可以看出,每个数据点210都位于介体点230旁边,介体点230的另一端位于辅助点对的一辅助点220旁边。门控单元270和导电引线260被布置成控制每个数据点210、辅助点220、介体点230和电荷库250。每个辅助点220还通过引线260耦合至一测量单元240(及门孔单元270)。

[0146]

参照图7a

‑

图7g,下面将描述用于处理量子信息的设备的多个层。本领域技术人员在阅读本发明后将会理解,可以使用“多层栅堆叠(multi

‑

layered gate stack)”方法来制造这样的设备。该设备是分层构建的。金属电极可以光刻限定并沉积在一层上。每个电极层随后可通过氧化物层的沉积或生长与下一层隔离。本领域技术人员将理解的是可以使用用于制造该设备的其他方法。

[0147]

图7a

‑

图7f示出了cmos结构的许多层,因为该设备是按层构建的。图中未示出每一层(例如,未示出沉积或生长的氧化物)。然而,这些层是从最低(图7a)到最高(图7e)的顺序。诸如“更低”、“最低”、“更高”、“最高”、“上方”和“下方”等术语纯粹是表示图中特征的相对位置。也就是说,诸如本文使用的那些方向性术语不是指相对于用户的视角的方向,而是在所有方面都应被视为相对术语。

[0148]

这些图特别关注一单位单元。在图7b

‑

图7f中,不构成中央单位单元的一部分并在前一阶段中提供的特征用虚线示出。

[0149]

图7a示出了硅衬底710的一部分。还示出了欧姆注入区720(图7a中未示出其他欧姆区)的位置,其在使用中可将载流子馈送给电荷库250。硅氧化层也以基本均匀的覆盖被沉积(未示出)。

[0150]

图7b示出了比图7a中的层更高的层。沉积第一导电层以限定电荷库250并限定限制区。第一导电层包括多晶硅电极740。第一导电层还包括金属电极750。图7b还示出了自前一阶段沉积的触点730(其不构成单位单元的一部分)。然后使用原子层沉积在第一导电层上方生长基本均匀的隔离氧化物层。

[0151]

一旦设备设置好了多晶硅电极740和金属电极750以及随后的隔离氧化物层,就设置第二导电层。具体地,向该设备提供金属电极760(参见图7c,其示出了位于图7b所示层的上方的层)。该第二导电层有助于限定介体点230。随后使用原子层沉积生长基本上均匀的隔离氧化物层。在图7c中以虚线示出了不构成单位单元的一部分并应用在下层中的多晶硅

电极740和金属电极750。

[0152]

还提供包括另外的金属电极770的第三导电层(参见图7d,其示出了位于图7c所示层的上方的层)以限定至电荷库250的屏障,并提供用于控制数据点210和辅助点220的电极。随后使用原子层沉积来生长基本均匀的隔离氧化物层。不构成单位单元的一部分并应用在下层中的电极740、750和760在图7d中以虚线示出。

[0153]

提供第四导电层用于限定介体点230。该第四导电层还包括另外的金属电极780(参见图7e,其示出了位于图7d所示层的上方的层)。随后使用原子层沉积来生长基本均匀的隔离氧化物层。不构成单位单元的一部分并应用在下层中的电极740、750、760和770在图7e中以虚线示出。

[0154]

图7f示出了图7e所示结构中数据点210和辅助点220的位置。

[0155]

图8a示出了沿图7e中指示的方向a所看到的图7e的结构的侧面轮廓。附图标记810表示氧化硅层(栅层(gate layer))。附图标记820表示ald氧化物。附图标记830代表另一氧化硅层。

[0156]

图8b示出了沿图7e中指示的方向b所看到的图7e的结构的侧面轮廓。

[0157]

图8c示出了沿图7e中指示的方向c所看到的图7e的结构的侧面轮廓。附图标记750表示金属通孔或插塞。

[0158]

表面码可以通过检查阵列200的元格(plaquette)的数据量子位的x奇偶校验和/或z奇偶校验来实现。本领域技术人员将理解,术语“元格”是本领域的术语,并且可在本示例中理解成表示形成在阵列200的四个物理数据点210之间的面。这些奇偶校验是表面码的稳定子生成器(stabiliser generator),并使用诸如图9所示的稳定子检查量子电路来进行测量。图9所示的control

‑

z门可被进一步分解为图4或图5的量子电路,具体取决于微磁体是否位于数据点210附近。x稳定子检查包括图9的操作(虚线框内),但z稳定子检查不将其包括在内。辅助双点220在单重态(表示为|s>)初始化,并使用单重态

‑

三重态自旋相关隧穿读出(singlet

‑

triplet spin

‑

dependenttunnelling readout)进行测量。

[0159]

图10示出了图7e中所示的设备单位单元的变化。在图10所示的示例中,若干个电极组合成单个电极。

[0160]

图11示出了图7e中所示的设备单位单元的变化,其中,每个量子点的静电势是高度可调的。在图11的设备中,任两个介体之间不共享电极。

[0161]

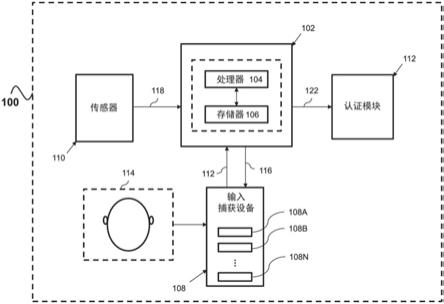

图12是控制器/计算装置1200的框图。例如,计算装置1200可包括计算设备。计算装置1200可跨多个连接的设备分布。本领域技术人员可以理解,可以使用与图12所示的架构不同的其他架构。

[0162]

参照该图,控制器/计算装置1200包括一个或多个处理器1210、一个或多个存储器1220、多个可选的用户界面(例如,视觉显示器1230和虚拟或物理键盘1240)、通信模块1250和可选的端口1260及可选的电源1270。组件1210、1220、1230、1240、1250、1260和1270中的每一个使用各种总线互连。处理器1210可以处理用于在计算装置1200内执行的指令,包括存储在存储器1220中、经由通信模块1250或经由端口1260接收的指令。

[0163]

存储器1220用于在计算装置1200内存储数据。一个或多个存储器1220可包括一个或多个易失性存储器单元。一个或多个存储器可包括一个或多个非易失性存储器单元。一个或多个存储器1220也可以是另一种形式的计算机可读介质,例如,磁盘或光盘。一个或多

个存储器1220可为计算装置1200提供大容量存储。用于执行本文所述的方法的指令可存储在所述一个或多个存储器1220内。

[0164]

装置1200包括多个用户界面,其包括诸如可视显示器1230之类的可视化装置和诸如键盘1240之类的虚拟或专用用户输入设备。

[0165]

通信模块1250适用于在处理器1210和远程系统之间发送和接收通信。例如,通信模块1250可用于经由诸如因特网等通信网络发送和接收通信。

[0166]

端口1260适于接收例如包含要由处理器1210处理的指令的非暂时性计算机可读介质。

[0167]

处理器1210被配置成接收数据、访问存储器1220、及根据从所述存储器1220或连接至端口1260的计算机可读存储介质、从通信模块1250或从用户输入设备1240接收的指令而动作。

[0168]

处理器1210可被配置成使磁场被施加至阵列200,以便分离第一组和第二组限制区中的电荷载流子的自旋态的能级。也就是说,处理器1210可被配置成使磁场被施加至数据点210和辅助点220,以去除存储在那些量子点中的任何电子的自旋态的简并性。控制器1200还可包括用于向阵列200施加磁场的磁场发生器。

[0169]

处理器1210可被配置成使振荡磁场被施加至第一组和第二组限制区,该振荡磁场的频率基本上匹配电荷载流子的塞曼分裂。控制器1210还可包括用于产生所述振荡磁场的磁场发生器。

[0170]

处理器1210可被配置成使第三组限制区中的至少一个限制区与电荷库耦合,以使得能够在所述电荷库与所述第三组限制区中的所述至少一个限制区之间转移电荷载流子。例如,该处理器可被配置成使阵列200的介体点230与电荷库250耦合,以便在该介体点和电荷库之间发生电子转移。这种操作可用于初始化用于量子信息处理的设备,并消除由于载流子位于错误位置而引起的误差。

[0171]

图13示出了图7e中所示的设备单位单元的变化。具体地,在图13所示的架构中,适当大小的磁体1300(例如,纳米磁体)已被放置在图7e的单位单元的上方,使得磁体1300的北极(n)和南极(s)位于数据点210附近。第一磁体1300的北极与第二磁体1300的南极之间的间隔位于数据点210之上,从而将第一磁体1300的北极与第二磁体的南极之间的磁场集中于数据点210上方。

[0172]

如上文中参照图2、图3和图5所描述的,包含磁体1300使得能够通过电偶极自旋共振(edsr)实现单量子位门。此外,通过图13所示的架构,可以使用图5的电路图实现control

‑

z门。

[0173]

本领域技术人员可设想上文所述的实施例的变化,例如,所有公开的实施例的特征可以以任何方式和/或组合进行组合,除非这些特征不兼容。

[0174]

本领域技术人员将理解,图中所示的布局可以变化,并且,可以不是二维网格。

[0175]

电荷库可定位在例如与限制区不同的深度处。

[0176]

本说明书(包括任何随附的权利要求、摘要和附图)中公开的所有特征和/或如此公开的任何方法或过程的所有步骤,可以以任何组合方式组合,除了至少一些特征和/或步骤是相互排斥的组合。

[0177]

除非另有明确说明,否则本说明书(包括任何随附的权利要求、摘要和附图)中公

开的每个特征都可以被用于相同、等效或相似目的的替代特征替换。因此,除非另有明确说明,否则所公开的每个特征仅是一系列等效或相似特征的一个示例。

[0178]

本发明不限于任何前述实施例的细节。本发明可扩展到本说明书(包括任何随附的权利要求、摘要和附图)中公开的特征的任何新的一个或任何新的组合,或所公开的任何方法或过程的步骤的任何新的一个或任何新的组合。不应将权利要求解释为仅涵盖前述实施例,而是包括落入权利要求范围内的任何实施例。

[0179]

如本领域技术人员将从至少第0106段和图6a和图6b所理解的,每个介体点230通过导电引线260(即不通过中间点,例如,数据点210或辅助点220)直接耦合至电荷库250。在图6a和图6b所示的具体实施例中,每个电荷库250直接耦合至四个介体点230。

[0180]

更具体地,每个介体点230可以选择性地直接耦合至电荷库250。这可以经由导电引线260或任何其他形式的直接耦合。介体点230和/或电荷库250也可以可选地耦合至门控单元270,这可以经由导电引线260或任何其他耦合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。