1.本发明属于电子设计自动化领域,尤其涉及一种寄存器时序约束灵活建模方法。

背景技术:

2.在静态时序分析(sta)中,建立和保持同步时序检查是验证基于寄存器的时序电路的时序是否正确所必须的。寄存器建立时间(setup time)为在时钟翻转(对于正沿触发寄存器为0

→

1的翻转)之前数据输入(d)必须有效的时间,寄存器维持时间(hold time)是在时钟边沿之后数据输入必须仍然有效的时间。只有建立和保持时间都满足要求时,输入端(d)处的数据才会被复制到输出端(q)。如果违反了这两个约束中的任意一个,则认为寄存器工作不正常,报告时序违规。

3.在传统的静态时序分析(sta)中,寄存器被假定工作在有恒定寄存器延时即时钟端到输出端延时t

cq

的区域(即稳态区),寄存器的假定工作点在寄存器建立松弛或保持松弛足够大时得到,此时对应的时钟端到输出端延时是寄存器在改变建立松弛和保持松弛时最小的t

cq

,记为同时在保持松弛设置为足够大值时,逐渐减小建立松弛,在一般情况下,以t

cq

恰好达到恰好达到时的建立松弛定为建立时间;同样的,在建立松弛设置为足够大值时,逐渐减小保持松弛,在一般情况下,以t

cq

恰好达到时的保持松弛定为保持时间。这种简化没有利用建立时间和保持时间之外的可行区域,忽略了建立松弛、保持松弛和寄存器延时之间的相互依赖关系,因此电路性能可能会被悲观估计。

4.另外,在建立松弛大于建立时间且保持松弛大于保持时间的区域内,存在着t

cq

大于的区域,但是在传统的sta中,仍然假定寄存器的延时为这就带来了即使满足了时序约束但是电路还是无法正常工作的风险。

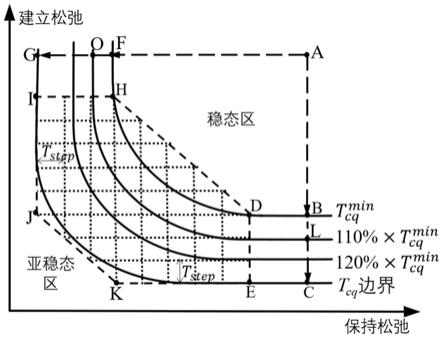

5.事实上,寄存器的建立松弛、保持松弛和寄存器延时之间有着相互依赖的关系。如图1所示,当建立松弛和保持松弛足够大时,寄存器时钟端到输出端的延时为寄存器最小延时。如果建立松弛和保持松弛变到足够小的话,寄存器延时会变大,直到寄存器进入亚稳态区。如果允许寄存器在建立松弛小于建立时间的区域工作,则电路的关键路径的时钟周期可以更小。即使这一级寄存器的建立松弛较小,会使这一级寄存器延时变大,但这个增加的延迟时间仅影响这一级寄存器和下一级寄存器之间的组合路径,若此组合路径延迟不大,则不会出现时序违规。

技术实现要素:

6.本发明目的在于提供一种寄存器时序约束灵活建模方法,以解决传统静态时序分析方法中的由于寄存器的建立松弛、保持松弛和时钟端到输出端延时三者之间相关性被忽略进而使得电路性能被悲观估计的技术问题和减小建立灵活模型所需的仿真开销的技术问题。

7.为解决上述技术问题,本发明的具体技术方案如下:

8.一种寄存器时序约束灵活建模方法,包括以下步骤:

9.步骤1、在每种s

q

、t

di

、t

ckj

、c

lk

组合的情况下分别仿真得到建立模型的时序约束范围,其中s

q

表示寄存器输出端状态;t

di

表示p种寄存器输入端的过渡时间t

d

,i为整数,1≤i≤p;t

ckj

表示q种寄存器时钟端的过渡时间t

ck

,j为整数,1≤j≤q;c

lk

表示m种寄存器输出负载电容c

l

,k为整数,1≤k≤m;

10.步骤2、在得到的每种s

q

、t

di

、t

ckj

、c

lk

组合下的时序约束范围中,设定t

step

为建立松弛和保持松弛的采样间距,对建立松弛和保持松弛均以设定的t

step

为间距提取出n个建立松弛和保持松弛的组合对,通过晶体管级仿真工具仿真分别得到n个寄存器时钟端到输出端的延时,之后将所有的s

q

、t

di

、t

ckj

、c

lk

组合下的所有仿真数据合并到一起得到n

s

组模型训练样本数据,其中每组训练样本数据都包括寄存器的输入端过渡时间、时钟端过渡时间、输出负载电容、建立松弛、保持松弛、输出端状态和时钟端到输出端延时参数;

11.步骤3、以寄存器输入端过渡时间、时钟端过渡时间、输出负载电容、建立松弛、保持松弛、输出端状态为模型特征,以对应的步骤2中得到的寄存器时钟端到输出端延时为模型标签,利用神经网络进行训练并建立寄存器的相互依赖的时序模型;

12.步骤4、通过静态时序分析工具获得时序约束,包括寄存器的输出端状态、输入端过渡时间、时钟端过渡时间和输出负载电容,通过步骤3中得到的寄存器相互依赖的时序模型,推理得到当建立松弛为时寄存器时钟端到输出端延时和保持松弛为时寄存器时钟端到输出端延时。

13.进一步的,所述步骤1具体包括以下步骤:

14.步骤1.1、在每一种s

q

、t

di

、t

ckj

、c

lk

组合下,先用晶体管级仿真工具仿真得到建立松弛足够大值t

su

(max)和保持松弛足够大值t

hd

(max)时的时钟端到输出端延时t

cq

,此处所述建立松弛足够大值指的是此时若继续增大t

su

,t

cq

并不会继续减小,所述保持松弛足够大值指的是此时若继续增大t

hd

,t

cq

并不会继续减小,具体来说,就是当建立松弛自t

su

(max)增大至δ

su

×

t

su

(max)和保持松弛自t

hd

(max)增大至δ

hd

×

t

hd

(max)时,t

cq

保持不变,其中δ

su

为建立松弛验证系数,1≤δ

su

≤1.1,δ

hd

为保持松弛验证系数,1≤δ

hd

≤1.1,此时寄存器工作在稳定区,记此时的t

cq

为保持松弛为建立松弛为

15.步骤1.2、以为固定的保持松弛,逐步减小建立松弛,直至晶体管级仿真失败,得到的建立松弛即为时序约束范围的最小的建立松弛,记此时的建立松弛为

16.步骤1.3、以为固定的保持松弛,使用二分法搜索建立松弛的值,开始搜索的区间为对特定的建立松弛通过晶体管级仿真工具仿真得到t

cq

,将t

cq

的目标值定为其中b

cq

为建立松弛第一目标系数,1≤b

cq

≤1.1,将二分搜索到的建立松弛的值记为

17.步骤1.4、以为固定的建立松弛,逐步减小保持松弛,直至晶体管级仿真失败,得到的保持松弛即为时序约束范围的最小的保持松弛,记此时的保持松弛为

18.步骤1.5、以为固定的建立松弛,使用二分法搜索保持松弛的值,开始搜索的区间为对特定的保持松弛可通过晶体管级仿真工具仿真得到时钟端到输出端延时t

cq

,将时钟端到输出端延时t

cq

的目标值定为其中f

cq

为保持松弛第一目标系数,1≤f

cq

≤1.1,将二分搜索到的保持松弛的值记为

19.步骤1.6、以为固定的建立松弛,使用二分法搜索保持松弛的值,开始搜索的区间为对特定的保持松弛可通过晶体管级仿真工具仿真得到时钟端到输出端延时t

cq

,将时钟端到输出端延时t

cq

的目标值定为其中d

cq

为保持松弛第二目标系数,b

cq

≤d

cq

≤1.1,将二分搜索到的保持松弛的值记为

20.步骤1.7、以为固定的保持松弛,使用二分法搜索建立松弛的值,开始搜索的区间为对特定的建立松弛可通过晶体管级仿真工具仿真得到时钟端到输出端延时t

cq

,将时钟端到输出端延时t

cq

的目标值定为其中h

cq

为建立松弛第二目标系数,f

cq

≤h

cq

≤1.1,将二分搜索到的建立时间的值记为

21.步骤1.8、在s

q

、t

di

、t

ckj

、c

lk

组合下保持松弛t

hd

和建立松弛t

su

对的模拟范围由以下各式组成约束条件:

[0022][0023]

上式即为在这种s

q

、t

di

、t

ckj

、c

lk

组合的情况下的建立模型的时序约束范围。

[0024]

进一步的,步骤2具体包括以下步骤:

[0025]

步骤2.1、设定t

step

为建立松弛和保持松弛的采样间距,对建立松弛和保持松弛均以设定的t

step

为间距提取出n个建立松弛和保持松弛的组合对,通过晶体管级仿真工具仿真分别得到n个寄存器的时钟端到输出端延时;此时得到的每组仿真数据包括输入端过渡时间、时钟端过渡时间、输出负载电容、建立松弛、保持松弛、输出端状态和时钟端到输出端延时共七个参数;

[0026]

步骤2.2、给定一个时钟端到输出端延时的阈值为其中m

th

为延时阈值系数,1≤m

th

≤10;将晶体管级仿真失败和时钟端到输出端延时大于时对应的这些组仿真数据去除掉,把去除之后的数据保存为神经网络模型的训练和测试样本,将上述

过程在每种不同的s

q

、t

di

、t

ckj

、c

lk

组合下重复进行;

[0027]

步骤2.3、将所有的寄存器输出端状态s

q

、输入端过渡时间t

di

、时钟端过渡时间t

ckj

、输出负载电容c

lk

组合下的所有仿真数据合并到一起得到n

s

组模型训练样本数据,其中每组训练样本数据都包括寄存器的输入端过渡时间、时钟端过渡时间、输出负载电容、建立松弛、保持松弛、输出端状态和时钟端到输出端延时共7个参数。

[0028]

进一步的,步骤1.3中二分搜索具体步骤如下:开始搜索的区间为进一步的,步骤1.3中二分搜索具体步骤如下:开始搜索的区间为在该搜索区间的中间位置仿真得到时钟端到输出端延时,如果此时时钟端到输出端延时为则搜索过程结束;如果此时时钟端到输出端延时大于则搜索区间更新为如果此时时钟端到输出端延时小于则搜索更新为然后以新的搜索区间重复上述过程,每次将搜索区间减半,直至某一次搜索过程中的中间位置通过晶体管级仿真工具仿真得到的时钟端到输出端延时为搜索结束;记最后一次二分搜索区间的中间位置即时钟端到输出端延时为时对应的建立松弛为

[0029]

进一步的,步骤1.5中二分搜索具体步骤如下:开始搜索的区间为进一步的,步骤1.5中二分搜索具体步骤如下:开始搜索的区间为在该搜索区间的中间位置仿真得到时钟端到输出端延时,如果此时时钟端到输出端延时为则搜索过程结束;如果此时时钟端到输出端延时大于则搜索区间更新为如果此时时钟端到输出端延时小于则搜索区间更新为则搜索区间更新为然后以新的搜索区间重复上述过程,每次将搜索区间减半,直至某一次搜索过程中的中间位置通过晶体管级仿真工具仿真得到的时钟端到输出端延时为搜索结束;记最后一次二分搜索区间的中间位置即时钟端到输出端延时为时对应的保持松弛为

[0030]

进一步的,步骤1.6中二分搜索具体步骤如下:开始搜索的区间为进一步的,步骤1.6中二分搜索具体步骤如下:开始搜索的区间为在该搜索区间的中间位置仿真得到时钟端到输出端延时,如果此时时钟端到输出端延时为则搜索过程结束;如果此时时钟端到输出端延时大于则搜索区间更新为如果此时时钟端到输出端延时小于则搜索区间更新为则搜索区间更新为然后以新的搜索区间重复上述过程,每次将搜索区间减半,直至某一次搜索过程中的中间元素通过晶体管级仿真工具仿真得到的时钟端到输出端延时为搜索结束,记最后一次二分搜索区间的中间位置即时钟端到输出端延时为时对应的保持松弛为

[0031]

进一步的,步骤1.7中二分搜索具体步骤如下:开始搜索的区间为进一步的,步骤1.7中二分搜索具体步骤如下:开始搜索的区间为在该搜索区间的中间位置仿真得到时钟端到输出端延时,如果此时时钟端到输出端延时为则搜索过程结束;如果此时时钟端到输出端延时大于则搜索区间更新为如果此时时钟端到输出端延时小于则搜索区间更新为则搜索区间更新为然后以新的搜索区间重复上述过程,每次将搜索区间减半,直至某一次搜索过程中的中间位置通过晶体管级仿真工具仿真得到的时钟端到输出端延时为搜索结束,记最后一次二分搜索区间的中间即时钟端到输出端延时为时对应的建立松弛为

[0032]

本发明的一种寄存器时序约束灵活建模方法,具有以下优点:

[0033]

1、本发明建立的寄存器时序模型将时钟端到输出端延时建模为输入端过渡时间、时钟端过渡时间、输出负载电容、建立松弛、保持松弛和输出端状态的函数,而传统寄存器时序约束模型中的时钟端到输出端延时为时钟端过渡时间、输出负载电容和输出端状态的函数,本发明建立的寄存器时序模型能有效表征寄存器的建立松弛、保持松弛和时钟端到输出端延时三者之间的相关性,且考虑了输入端过渡时间对时钟端到输出端延时的影响,更全面描述寄存器的时序约束,克服传统寄存器时序约束模型的悲观性,有益于提高静态时序分析的精度;

[0034]

2、本发明通过多次二分搜索不断缩小寄存器灵活时序约束建模的仿真范围,有效减少了稳态区的仿真,并且避免了亚稳态区的仿真,从而有效降低了仿真开销,缓解了寄存器时序约束灵活建模导致的仿真开销增长的问题,有益于该建模方法实际应用于静态时序分析流程。

附图说明

[0035]

图1为现有技术中寄存器建立松弛、保持松弛和时钟端到输出端延时相互依赖关系图;

[0036]

图2为本发明的寄存器灵活时序约束建模所需仿真范围的示意图;

[0037]

图3为本发明推理得到寄存器时钟端到输出端延时t

cq

的神经网络模型结构示意图。

具体实施方式

[0038]

为了更好地了解本发明的目的、结构及功能,下面结合附图,对本发明一种寄存器时序约束灵活建模方法做进一步详细的描述。

[0039]

本发明的一种寄存器时序约束灵活建模方法,包括以下步骤:

[0040]

步骤1、在每种s

q

、t

di

、t

ckj

、c

lk

组合的情况下分别仿真得到建立模型的时序约束范围,时序约束范围为图2所示的多边形dhijke,其中s

q

表示寄存器输出端状态;t

di

表示p种寄存器输入端的过渡时间t

d

,i为整数,1≤i≤p;t

ckj

表示q种寄存器时钟端的过渡时间t

ck

,j为整数,1≤j≤q;c

lk

表示m种寄存器输出负载电容c

l

,k为整数,1≤k≤m;

[0041]

而传统寄存器时序约束模型中,寄存器被假定工作在有恒定寄存器延时即时钟端到输出端延时t

cq

的区域(即稳态区),寄存器的假定工作点在寄存器建立松弛或保持松弛足够大时得到,此时对应的时钟端到输出端延时是寄存器在改变建立松弛和保持松弛时最小的t

cq

,记为同时在保持松弛设置为足够大值时,逐渐减小建立松弛,在一般情况下,以t

cq

恰好达到时的建立松弛定为建立时间,对应图2中l点的建立松弛;同样的,在建立松弛设置为足够大值时,逐渐减小保持松弛,在一般情况下,以t

cq

恰好达到时的保持松弛定为保持时间,对应图2中o点的保持松弛。

[0042]

步骤1具体包括以下步骤:

[0043]

步骤1.1、在每一种s

q

、t

di

、t

ckj

、c

lk

组合下,先用晶体管级仿真工具仿真得到建立松弛足够大值t

su

(max)和保持松弛足够大值t

hd

(max)时的时钟端到输出端延时t

cq

,此处所述建立松弛足够大值指的是此时若继续增大t

su

,t

cq

并不会继续减小,所述保持松弛足够大值指的是此时若继续增大t

hd

,t

cq

并不会继续减小,具体来说,就是当建立松弛自t

su

(max)增大至δ

su

×

t

su

(max)和保持松弛自t

hd

(max)增大至δ

hd

×

t

hd

(max)时,t

cq

保持不变,其中δ

su

为建立松弛验证系数,1≤δ

su

≤1.1,δ

hd

为保持松弛验证系数,1≤δ

hd

≤1.1,此时寄存器工作在稳定区,记此时的t

cq

为保持松弛为建立松弛为对应图2所示的a点;

[0044]

步骤1.2、以为固定的保持松弛,逐步减小建立松弛,直至晶体管级仿真失败,得到的建立松弛即为时序约束范围的最小的建立松弛,记此时的建立松弛为对应图2所示的c点;

[0045]

步骤1.3、以为固定的保持松弛,使用二分法搜索建立松弛的值,开始搜索的区间为对特定的建立松弛可通过晶体管级仿真工具仿真得到t

cq

,将t

cq

的目标值定为其中b

cq

为建立松弛第一目标系数,1≤b

cq

≤1.1,将二分搜索到的建立松弛的值记为对应图2所示的b点。二分搜索具体步骤如下:开始搜索的区间为在该搜索区间的中间位置仿真得到时钟端到输出端延时,如果此时时钟端到输出端延时为则搜索过程结束;如果此时时钟端到输出端延时大于则搜索区间更新为如果此时时钟端到输出端延时小于则搜索更新为然后以新的搜索区间重复上述过程,每次将搜索区间减半,直至某一次搜索过程中的中间位置通过晶体管级仿真工具仿真得到的时钟端到输出端延时为搜索结束;记最后一次二分搜索区间的中间位置即时钟端到输出端延时为时对应的建立松弛为对应图2所示的b点。

[0046]

步骤1.4、以为固定的建立松弛,逐步减小保持松弛,直至晶体管级仿真失败,

得到的保持松弛即为时序约束范围的最小的保持松弛,记此时的保持松弛为对应图2所示的g点;

[0047]

步骤1.5、以为固定的建立松弛,使用二分法搜索保持松弛的值,开始搜索的区间为对特定的保持松弛可通过晶体管级仿真工具仿真得到时钟端到输出端延时t

cq

,将时钟端到输出端延时t

cq

的目标值定为其中f

cq

为保持松弛第一目标系数,1≤f

cq

≤1.1,将二分搜索到的保持松弛的值记为对应图2所示的f点;二分搜索具体步骤如下:开始搜索的区间为在该搜索区间的中间位置仿真得到时钟端到输出端延时,如果此时时钟端到输出端延时为则搜索过程结束;如果此时时钟端到输出端延时大于则搜索区间更新为如果此时时钟端到输出端延时小于则搜索区间更新为然后以新的搜索区间重复上述过程,每次将搜索区间减半,直至某一次搜索过程中的中间位置通过晶体管级仿真工具仿真得到的时钟端到输出端延时为搜索结束;记最后一次二分搜索区间的中间位置即时钟端到输出端延时为时对应的保持松弛为对应图2所示的f点。

[0048]

步骤1.6、以为固定的建立松弛,使用二分法搜索保持松弛的值,开始搜索的区间为对特定的保持松弛可通过晶体管级仿真工具仿真得到时钟端到输出端延时t

cq

,将时钟端到输出端延时t

cq

的目标值定为其中d

cq

为保持松弛第二目标系数,b

cq

≤d

cq

≤1.1,将二分搜索到的保持松弛的值记为对应图2所示的d点;二分搜索具体步骤如下:开始搜索的区间为在该搜索区间的中间位置仿真得到时钟端到输出端延时,如果此时时钟端到输出端延时为则搜索过程结束;如果此时时钟端到输出端延时大于则搜索区间更新为如果此时时钟端到输出端延时小于则搜索区间更新为然后以新的搜索区间重复上述过程,每次将搜索区间减半,直至某一次搜索过程中的中间元素通过晶体管级仿真工具仿真得到的时钟端到输出端延时为搜索结束,记最后一次二分搜索区间的中间位置即时钟端到输出端延时为时对应的保持松弛为对应图2所示的d点。

[0049]

步骤1.7、以为固定的保持松弛,使用二分法搜索建立松弛的值,开始搜索的区

间为对特定的建立松弛可通过晶体管级仿真工具仿真得到时钟端到输出端延时t

cq

,将时钟端到输出端延时t

cq

的目标值定为其中h

cq

为建立松弛第二目标系数,f

cq

≤h

cq

≤1.1,将二分搜索到的建立时间的值记为对应图2所示的h点;二分搜索具体步骤如下:开始搜索的区间为在该搜索区间的中间位置仿真得到时钟端到输出端延时,如果此时时钟端到输出端延时为则搜索过程结束;如果此时时钟端到输出端延时大于则搜索区间更新为如果此时时钟端到输出端延时小于则搜索区间更新为然后以新的搜索区间重复上述过程,每次将搜索区间减半,直至某一次搜索过程中的中间位置通过晶体管级仿真工具仿真得到的时钟端到输出端延时为搜索结束,记最后一次二分搜索区间的中间即时钟端到输出端延时为时对应的建立松弛为对应图2所示的h点。

[0050]

步骤1.8、在s

q

、t

di

、t

ckj

、c

lk

组合下保持松弛t

hd

和建立松弛t

su

对的模拟范围由以下各式组成约束条件:

[0051][0052]

上式即为在这种s

q

、t

di

、t

ckj

、c

lk

组合的情况下的建立模型的时序约束范围,即为图2所示的多边形dhijke所在区域。

[0053]

步骤2、在得到的每种s

q

、t

di

、t

ckj

、c

lk

组合下的时序约束范围中,设定t

step

为建立松弛和保持松弛的采样间距,对建立松弛和保持松弛均以设定的t

step

为间距提取出n个建立松弛和保持松弛的组合对,如图2所示,建立松弛和保持松弛的组合对即为图2所示的多边形dhijke中的横虚线和竖虚线的n个交点的对应的建立松弛和保持松弛的组合,通过晶体管级仿真工具仿真分别得到n个寄存器时钟端到输出端的延时,之后将所有的s

q

、t

di

、t

ckj

、c

lk

组合下的所有仿真数据合并到一起得到n

s

组模型训练样本数据,其中每组训练样本数据都包括寄存器的输入端过渡时间、时钟端过渡时间、输出负载电容、建立松弛、保持松弛、输出端状态和时钟端到输出端延时参数;

[0054]

具体包括以下步骤:

[0055]

步骤2.1、如图2所示,设定t

step

为建立松弛和保持松弛的采样间距,对建立松弛和保持松弛均以设定的t

step

为间距提取出n个建立松弛和保持松弛的组合对,通过晶体管级

仿真工具仿真分别得到n个寄存器的时钟端到输出端延时;此时得到的每组仿真数据包括输入端过渡时间、时钟端过渡时间、输出负载电容、建立松弛、保持松弛、输出端状态和时钟端到输出端延时共七个参数;

[0056]

步骤2.2、给定一个时钟端到输出端延时的阈值为其中m

th

为延时阈值系数,1≤m

th

≤10;将晶体管级仿真失败和时钟端到输出端延时大于时对应的这些组仿真数据去除掉,把去除之后的数据保存为神经网络模型的训练和测试样本,将上述过程在每种不同的s

q

、t

di

、t

ckj

、c

lk

组合下重复进行;

[0057]

步骤2.3、将所有的寄存器输出端状态s

q

、输入端过渡时间t

di

、时钟端过渡时间t

ckj

、输出负载电容c

lk

组合下的所有仿真数据合并到一起得到n

s

组模型训练样本数据,其中每组训练样本数据都包括寄存器的输入端过渡时间、时钟端过渡时间、输出负载电容、建立松弛、保持松弛、输出端状态和时钟端到输出端延时共7个参数。

[0058]

步骤3、以寄存器输入端过渡时间、时钟端过渡时间、输出负载电容、建立松弛、保持松弛、输出端状态为模型特征,以对应的步骤2中得到的寄存器时钟端到输出端延时为模型标签,利用神经网络进行训练并建立寄存器的相互依赖的时序模型,神经网络模型结构如图3所示,神经网络输入层参数包括寄存器输入端过渡时间、时钟端过渡时间、输出负载电容、建立松弛、保持松弛、输出端状态,图3中所示神经网络包含2层隐含层(事实上隐含层层数和每层隐含层的神经元个数可根据具体情况进行调整),输出层为寄存器时钟端到输出端延时;

[0059]

步骤4、通过静态时序分析工具获得时序约束,包括寄存器的输出端状态、输入端过渡时间、时钟端过渡时间和输出负载电容通过步骤3中得到的寄存器相互依赖的时序模型,推理得到当建立松弛为时寄存器时钟端到输出端延时和保持松弛为时寄存器时钟端到输出端延时,如图3所示,将寄存器输入端过渡时间、时钟端过渡时间、输出负载电容、建立松弛、保持松弛、输出端状态作为神经网络模型输入,通过神经网络计算输出时钟端到输出端延时。

[0060]

可以理解,本发明是通过一些实施例进行描述的,本领域技术人员知悉的,在不脱离本发明的精神和范围的情况下,可以对这些特征和实施例进行各种改变或等效替换。另外,在本发明的教导下,可以对这些特征和实施例进行修改以适应具体的情况及材料而不会脱离本发明的精神和范围。因此,本发明不受此处所公开的具体实施例的限制,所有落入本技术的权利要求范围内的实施例都属于本发明所保护的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。