1.本发明涉及电子领域,更具体地说,涉及一种基于除法器的任务处理方法、装置、设备及存储介质。

背景技术:

2.目前,面对海量数据的存储要求,分布式存储以其成本低廉,可扩展性好等优势逐渐取代了统一存储的主导地位,在理论研究和实际应用方面得到了越来越多的关注。分布式存储系统多以廉价的磁盘作为存储节点,每个存储节点的可靠性往往不会很高,另一方面,一个分布式存储系统通常包含很多的节点,由于软硬件故障,人为失误等原因,系统常常发生节点失效的情况。为了提高分布式存储系统的数据可靠性,保证数据收集节点能以很高的概率实现原始文件的重构,需要在存储原始数据的基础上,额外存储一定数量的冗余,使得在出现部分节点失效的情况下,系统仍然可以正常运行,数据收集节点仍然可以对原始文件实现解码恢复。

3.存储的数据需要经过专有算法的压缩,存储的校验节点需要使用特殊的算法设计,通过对存储数据的加减乘除运算组合,以实现出最为少量的校验数据,最终实现出所有错误存储数据的恢复以及解压缩。常见的压缩解压缩算法有霍夫曼和lz77,常见的校验算法使用的是基于柯西或范德蒙矩阵的纠删码。因此,在存储系统中,为了实现以最小损耗为代价的数据安全存储,需要使用复杂算法,对数据进行大量的加减乘除运算,达到高速、大数据量的数据安全存储效果。因此在存储加速芯片中,为了实现高速大吞吐的硬件存储加速,需要设计专有的除法器、乘法器,以支持大量数据的高速运算需求。目前,电路系统中的除法器的运算所需要的时钟周期为固定的,这并不能满足运算速度需求很高的任务。

技术实现要素:

4.本发明的目的在于提供一种基于除法器的任务处理方法、装置、设备及存储介质,以调整除法器的时钟周期,提高除法器处理速度。

5.为实现上述目的,本发明提供一种基于除法器的任务处理方法,包括:

6.确定除法器执行当前任务的目标时钟周期数;

7.根据所述当前任务中被除数及除数的位数及所述目标时钟周期数确定每周期商的目标位数,以及所述被除数中有效被除数的有效被除位数;

8.利用所述目标位数及所述除数确定商取值映射关系;

9.在所述除法器的第一个时钟周期执行所述当前任务时,从所述被除数中选取所述有效被除位数的当前有效被除数,并根据所述商取值映射关系确定与当前有效被除数对应的商及余数;

10.将下一时钟周期作为当前时钟周期,对上一时钟周期的余数的高位补零,并从所述被除数的未选取数中向后取数组合生成当前有效被除数,继续根据所述商取值映射关系确定与当前有效被除数对应的商及余数,直至下一时钟周期为最后一个时钟周期为止;

11.若下一时钟周期为最后一个时钟周期,则将下一时钟周期作为当前时钟周期,将所述被除数的未选取数与上一时钟周期的余数组合生成当前有效被除数,并判断当前有效被除数的位数是否为所述有效被除位数;

12.若是,则根据所述商取值映射关系确定与当前有效被除数对应的商及余数;若否,则对所述目标位数、所述有效被除位数及所述有效被除位数更新后,继续执行所述判断当前有效被除数的位数是否为所述有效被除位数的步骤,直至运算结束为止。

13.其中,所述根据所述当前任务中被除数及除数的位数及所述目标时钟周期数确定每周期商的目标位数,包括:

14.利用第一位数确定规则确定目标位数,所述第一位数确定规则为:

15.其中,q

x

为目标位数,m为所述当前任务中被除数的位数,n为所述当前任务中除数的位数,k为目标时钟周期数,表示向上取整。

16.其中,所述被除数中有效被除数的有效被除位数的确定方法为:

17.利用第二位数确定规则确定有效被除位数,所述第二位数确定规则为:

18.x

x

=q

x

n

‑

1;其中,x

x

为有效被除位数。

19.其中,所述利用所述目标位数及所述除数确定商取值映射关系,包括:

20.基于所述目标位数确定不同情况下的目标商;

21.根据不同情况下的目标商及所述除数,确定每个目标商对应的阈值;

22.利用每个目标商及对应的阈值,确定每个目标商对应的有效被除数范围,从而生成与不同目标商对应的商取值映射关系。

23.其中,所述对所述目标位数、所述有效被除位数及所述有效被除位数更新,包括:

24.对所述目标位数减一,得到更新后的目标位数;

25.利用更新后的目标位数对所述有效被除位数进行更新;

26.利用更新后的目标位数及所述除数对商取值映射关系进行更新。

27.其中,所述对上一时钟周期的余数的高位补零,包括:

28.利用第三位数确定规则确定补零位数,所述第三位数确定规则为:

29.h0=q

x

‑

1;其中,h0为补零位数,q

x

为目标位数。

30.其中,所述从所述被除数的未选取数中向后取数组合生成当前有效被除数,包括:

31.利用第四位数确定规则确定取数位数,所述第四位数确定规则为:

32.l0=n

‑1‑

h0;其中,l0为取数位数,n为所述当前任务中除数的位数;

33.根据所述补零位数在上一时钟周期的余数的高位补零,并根据所述取数位数从所述被除数的未选取数中向后取数添加至所述余数的低位,生成当前时钟周期的当前有效被除数。

34.为实现上述目的,本发明进一步提供一种基于除法器的任务处理装置,包括:

35.时钟周期数确定模块,用于确定除法器执行当前任务的目标时钟周期数;

36.位数确定模块,用于根据所述当前任务中被除数及除数的位数及所述目标时钟周期数确定每周期商的目标位数,以及所述被除数中有效被除数的有效被除位数;

37.映射关系确定模块,用于利用所述目标位数及所述除数确定商取值映射关系;

38.有效被除数选取模块,用于在所述除法器的第一个时钟周期执行所述当前任务时,从所述被除数中选取所述有效被除位数的当前有效被除数;

39.商及余数确定模块,用于根据所述商取值映射关系确定与当前有效被除数对应的商及余数;

40.补零模块,用于将下一时钟周期作为当前时钟周期,对上一时钟周期的余数的高位补零;

41.第一组合模块,用于从所述被除数的未选取数中向后取数组合生成当前有效被除数,并触发所述商及余数确定模块根据所述商取值映射关系确定与当前有效被除数对应的商及余数,直至下一时钟周期为最后一个时钟周期为止;

42.第二组合模块,用于在下一时钟周期为最后一个时钟周期,将下一时钟周期作为当前时钟周期,将所述被除数的未选取数与上一时钟周期的余数组合生成当前有效被除数;

43.判断模块,用于判断当前有效被除数的位数是否为所述有效被除位数;若是,则触发所述商及余数确定模块;若是,触发更新模块;

44.所述更新模块,用于对所述目标位数、所述有效被除位数及所述有效被除位数更新,并触发所述商及余数确定模块,直至运算结束为止。

45.为实现上述目的,本发明进一步提供一种电子设备,包括:

46.存储器,用于存储计算机程序;

47.处理器,用于执行所述计算机程序时实现上述任意方法实施例所述的基于除法器的任务处理方法的步骤。

48.为实现上述目的,本发明进一步提供一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现上述任意方法实施例所述的基于除法器的任务处理方法的步骤。

49.通过以上方案可知,本发明实施例提供的一种基于除法器的任务处理方法、装置、设备及存储介质;在本方案中,除法器确定执行当前任务的目标时钟周期数后,便会确定在目标时钟周期数下的每周期商的目标位数、有效被除数的有效被除位数及商取值映射关系,这样在每个时钟周期,即会利用商取值映射关系确定有效被除数的商及余数,并对余数进行补零及取数后继续下一个时钟周期的处理,在最后一个周期,如果余数进行取数后可通过商取值映射关系得到结果,则任务处理完成,否则,需要对目标位数、有效被除位数及商取值映射关系更新后,再继续完成处理。可见,本方案可调整除法器的时钟周期,从而提高了除法器处理任务的速度,使得除法器在处理任务时,具有速度可控的优势。

附图说明

50.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

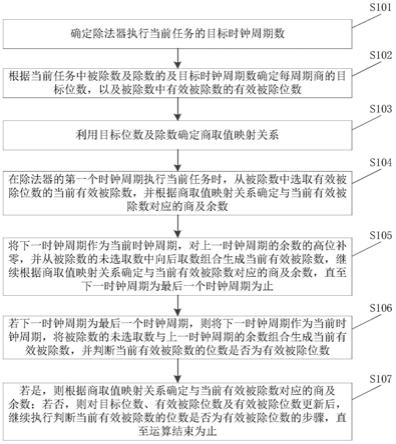

51.图1为传统二进制除法运算流程示意;

52.图2为本发明实施例公开的一种基于除法器的任务处理方法流程示意图;

53.图3为本发明实施例公开的时钟周期数可控的二进制整数除法器流程图;

54.图4为本发明实施例公开的一种基于除法器的任务处理装置结构示意图

55.图5为本发明实施例公开的一种电子设备结构示意图。

具体实施方式

56.目前,通过cpu(central processing unit,中央处理器)的软件方式可以实现各种除法运算,但是相比专用集成电路针对专用除法运算进行的设计,速度和功耗都都比较差。因此在存储加速芯片中,需要对使用较多的运算进行专用集成电路的设计。时钟周期(cycle)也称为振荡周期,定义为时钟频率的倒数。时钟周期是计算机中最基本的、最小的时间单位。在一个时钟周期内,电路仅完成一个最基本的动作。时钟周期是一个时间的量,更小的时钟周期就意味着更高的工作频率。

57.时钟周期的设置基于电路工作的方式,一个时钟周期可完成的工作通常是可以同时完成的,与下个时钟周期需要进行的工作没有相互依赖关系。因此算法硬件化简单的原理可以通过计算的依赖关系进行划分实现。而完成一个工作所需要的时钟周期数,即是常说的拍数,一般代表了工作所需要的时长,拍数越多,意味着划分的时钟周期数需要越多,整个工作的速度越慢,完成工作所需要的时长越大。此外,硬件电路的工作只有0和1,所有运算也需要通过二进制来实现。因此除法的设计需要基于二进制的运算考虑。

58.以除法器执行除法运算来说,被除数和除数转换成二进制后,被除数为m个比特,除数为n个比特,传统除法器需要m

‑

n 1个时钟周期完成除法运算,在此以被除数74除以除数8为例,对其运算流程进行说明。参见图1,为传统二进制除法运算流程示意图。如图1所示,74/8首先转化为二进制数,1001010/1000,因为被除数1001010是7(m)比特,除数1000是4(n)比特,因此完成该运算任务需要的拍数是7

‑

4 1=4拍。每一拍的运算分别为:

59.第一时钟周期:选择被除数的高4(除数位数)位,商1,进行减法,得到余数为1;

60.第二时钟周期:第一时钟周期的余数1和被除数的下一位0组合为10,因为10小于除数1000,因此商0,余数10。

61.第三时钟周期:第二时钟周期的余数10和被除数的下一位1组合为101,因为101小于除数1000,因此商0,余数101。

62.第四时钟周期:第三时钟周期的余数101和被除数的下一位0组合为1010,因为1010大于除数1000,因此商1,余数10。

63.此时被除数已经组合完,因此运算终止,商为前四个时钟周期运算得到的商的组合,即是1001,余数为最终余数,即是10。

64.如上所述,除法器的每一时钟周期运算的余数,需要作为下一时钟周期运算的前置条件,因此无法同时运行,只能分成4拍运算。这样的除法器速度较慢,运算因为拍与拍之间的依赖关系时间损耗较大。

65.因此,本发明实施例公开了一种基于除法器的任务处理方法、装置、设备及存储介质,在本方案中,除法器的时钟周期可自定义控制,从而通过减少时钟周期的方式提高除法器处理速度。

66.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于

本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

67.参见图2,本发明实施例提供的一种基于除法器的任务处理方法流程示意图,该方法具体包括:

68.s101、确定除法器执行当前任务的目标时钟周期数;

69.需要说明的是,除法器所在的电路系统可基于性能判定除法器执行当前任务的目标时钟周期,若该系统时钟频率为1ghz,除法器完成该目标任务所需要的时间长度乘以1ghz即是需求的目标时钟周期。设置的目标时钟周期数越大,则除法器执行当前任务的速度越快,花费的时间越少。因此,本技术依据电路系统所需要的目标时钟周期数,即可调整除法器的工作方式,从而实现不同时钟周期数的除法器,满足硬件系统的需求,具有速度可控的优势。

70.s102、根据当前任务中被除数及除数的及目标时钟周期数确定每周期商的目标位数,以及被除数中有效被除数的有效被除位数;

71.由于硬件电路的工作只有0和1,所有运算也需要通过二进制来实现,因此在本实施例中,实际是一种时钟周期数可控的二进制整数除法器。在本实施例中,被除数x和除数y转成二进制后,比特数分别是m和n。需要说明的是,在本实施例中,m与n的关系为:m≥n,若不满足,可以在高位补零达到满足即可。由于本方案针对的是专用除法器,为了达到最好的性能,需要考虑的m和n的情况即是最常出现,因此默认不满足m≥n的任务情况较少,不会影响本方案的性能,本方案也可以忽略m小于n的情况。

72.需要说明的是,若当前任务按照正常处理,则每周期商的位数q为:

73.q=m

‑

n 1

ꢀꢀꢀ

(1)

74.在本实施例中,若除法器根据需求完成运算的目标时钟周期数为k,则本实施例根据确定每周期商的目标位数时,具体是利用第一位数确定规则确定目标位数,该第一位数确定规则为:

[0075][0076]

其中,q

x

为目标位数,m为当前任务中被除数的位数,n为当前任务中除数的位数,k为目标时钟周期数,表示向上取整。通过公式2,可以实现将当前任务在小于或等于k个时钟周期完成处理。同样以74/8这一任务为例,若设置k=2,通过公知2可计算得出q

x

为2,q

x

表示每一个时钟周期所得到的商的位数。

[0077]

在本实施例中,被除数中有效被除数的有效被除位数的确定方法为:利用第二位数确定规则确定有效被除位数,所述第二位数确定规则为:

[0078]

x

x

=q

x

n

‑1ꢀꢀꢀ

(3)

[0079]

其中,x

x

为有效被除位数,有效被除数是在每个时钟周期参与运算的被除数,有效被除数位数是参与运算的被除数的位数;例如在上文所述的74/8这一任务中,x

x

为5。

[0080]

s103、利用目标位数及除数确定商取值映射关系;

[0081]

需要说明的是,在本实施例中,利用目标位数及除数确定商取值映射关系时,可基于目标位数确定不同情况下的目标商,然后根据不同情况下的目标商及除数,确定每个目

标商对应的阈值,再利用每个目标商及对应的阈值,确定每个目标商对应的有效被除数范围,从而生成与不同目标商对应的商取值映射关系。

[0082]

例如:当每一时钟周期得到的商的目标位数为2时,即表示每次得到2比特的商,因此其情况有22=4种,也即:目标商的共有4中情况,分别为:00,01,10,11,基于除数,计算四个判断阈值,分别为:

[0083][0084]

若除数为1000,则得到的阈值为:

[0085][0086]

由于在所得到的阈值中,除法运算后的商只会落在阈值范围内,第一个和最后一个阈值只会相等,而不会超出。因此可以得到商取值映射关为:

[0087][0088]

s104、在除法器的第一个时钟周期执行当前任务时,从被除数中选取有效被除位数的当前有效被除数,并根据商取值映射关系确定与当前有效被除数对应的商及余数;

[0089]

通过上述步骤,即完成了当前任务的准备工作。除法器在执行当前任务时,需要从被除数的高位起,选择当前有效被除数个比特位数作为当前有效被除数,对其基于公式6进行判定,得到一个部分商的输出。参见图3,本发明实施例提供的时钟周期数可控的二进制整数除法器流程图;通过图3可以看出,从被除数1001010的高5位选择了当前有效被除数10010,然后基于公式6,判断10010在哪个范围中,因为其在d

10

和d

11

之间,因此根据公式5可输出的部分商为10,余数为10。

[0090]

s105、将下一时钟周期作为当前时钟周期,对上一时钟周期的余数的高位补零,并从被除数的未选取数中向后取数组合生成当前有效被除数,继续根据商取值映射关系确定与当前有效被除数对应的商及余数,直至下一时钟周期为最后一个时钟周期为止;

[0091]

通过图3可以看出,将第一个时钟周期结束后,会将下一个周期作为当前时钟周期进行处理,在处理时,需要对上一时钟周期的余数的高位补零,如:利用第三位数确定规则确定补零位数,该第三位数确定规则为:

[0092]

h0=q

x

‑1ꢀꢀꢀ

(7)

[0093]

其中,h0为补零位数,q

x

为目标位数;参加图3,由于q

x

为2,则计算出补零位数为1,则在余数10前添加1个零,得到010。

[0094]

进一步,还需要从被除数的未选取数中向后取数组合生成当前有效被除数,具体

是利用第四位数确定规则确定取数位数,该第四位数确定规则为:

[0095]

l0=n

‑1‑

h0ꢀꢀꢀ

(8)

[0096]

其中,l0为取数位数,n为当前任务中除数的位数;然后根据补零位数在上一时钟周期的余数的高位补零,并根据取数位数从被除数的未选取数中向后取数添加至余数的低位,生成当前时钟周期的当前有效被除数。参见图3,n为4,h0为1,则可计算出l0为2,也即:从被除数的未选取数10中选择2位添加至010后,得到:01010。若下一时钟周期不是最后一个时钟周期,则继续执行根据商取值映射关系确定与当前有效被除数对应的商及余数这一步骤,如果下一时钟周期为最后一个时钟周期,则需要执行s106。

[0097]

s106、若下一时钟周期为最后一个时钟周期,则将下一时钟周期作为当前时钟周期,将被除数的未选取数与上一时钟周期的余数组合生成当前有效被除数,并判断当前有效被除数的位数是否为有效被除位数;

[0098]

s107、若是,则根据商取值映射关系确定与当前有效被除数对应的商及余数;若否,则对目标位数、有效被除位数及有效被除位数更新后,继续执行判断当前有效被除数的位数是否为有效被除位数的步骤,直至运算结束为止。

[0099]

需要说明的是,若下一时钟周期为最后一个时钟周期,则需要将最终得到的余数与剩余被除数进行组合,得到当前时钟周期的当前有效被除数,然后判断当前有效被除数的位数是否为有效被除位数x

x

,若是,则继续执行根据商取值映射关系确定与当前有效被除数对应的商及余数,任务处理完成;否则,说明当前有效被除数无法补齐x

x

,此时,需要对目标位数、有效被除位数及有效被除位数更新,如:对目标位数减一,得到更新后的目标位数q

x

'=q

x

‑

1;然后利用更新后的目标位数对有效被除位数进行更新,利用更新后的目标位数及所述除数对商取值映射关系进行更新,并继续判断当前有效被除数的位数是否为有效被除位数等后续步骤。如图3所示,余数为10,位数小于有效被除位数5,q

x

为2,q

x

减1后得到更新的目标位数为1,更新后的有效被除位数为4,可见,更新后的有效被除位数与余数(10)的位数还不相同,q

x

再减1为0,结束运算。参见图3,运算结束后,最终的商为每个时钟周期得到的商的组合,即是1001,余数为最终余数,即是10,并且,处理本次任务只需要花费2个时钟周期。

[0100]

综上可见,本实施例提出了一种时钟周期数可控的二进制数整数除法器实现方案,在方案基于被除数、除数和想要实现的完成运算时钟周期数进行配置,然后迭代输出多个商值,以达到减少迭代,减少运算需要的时钟周期的效果,提高速度。虽然本方案在最后需要判断当前有效被除数的位数是否为有效被除位数,但是在硬件电路中,多是以2为底的幂次值数量的被除数和除数,因此大部分情况下不需要额外判断,只有在不满足上述条件时,需要用到上述判断步骤,该判断简单有效,亦可快速实现,可有效实现除法运算的快速实现,提高除法器执行任务的速度

[0101]

下面对本发明实施例提供的处理装置、设备及存储介质进行介绍,下文描述的处理装置、设备及存储介质与上文描述的处理方法可以相互参照。

[0102]

参见图4,本发明实施例提供的一种基于除法器的任务处理装置结构示意图,包括:

[0103]

时钟周期数确定模块01,用于确定除法器执行当前任务的目标时钟周期数;

[0104]

位数确定模块02,用于根据所述当前任务中被除数及除数的位数及所述目标时钟

周期数确定每周期商的目标位数,以及所述被除数中有效被除数的有效被除位数;

[0105]

映射关系确定模块03,用于利用所述目标位数及所述除数确定商取值映射关系;

[0106]

有效被除数选取模块04,用于在所述除法器的第一个时钟周期执行所述当前任务时,从所述被除数中选取所述有效被除位数的当前有效被除数;

[0107]

商及余数确定模块05,用于根据所述商取值映射关系确定与当前有效被除数对应的商及余数;

[0108]

补零模块06,用于将下一时钟周期作为当前时钟周期,对上一时钟周期的余数的高位补零;

[0109]

第一组合模块07,用于从所述被除数的未选取数中向后取数组合生成当前有效被除数,并触发所述商及余数确定模块根据所述商取值映射关系确定与当前有效被除数对应的商及余数,直至下一时钟周期为最后一个时钟周期为止;

[0110]

第二组合模块08,用于在下一时钟周期为最后一个时钟周期,将下一时钟周期作为当前时钟周期,将所述被除数的未选取数与上一时钟周期的余数组合生成当前有效被除数;

[0111]

判断模块09,用于判断当前有效被除数的位数是否为所述有效被除位数;若是,则触发所述商及余数确定模块;若是,触发更新模块;

[0112]

所述更新模块10,用于对所述目标位数、所述有效被除位数及所述有效被除位数更新,并触发所述商及余数确定模块,直至运算结束为止。

[0113]

其中,所述位数确定模块包括:

[0114]

第一位数确定单元,用于利用第一位数确定规则确定目标位数,所述第一位数确定规则为:其中,q

x

为目标位数,m为所述当前任务中被除数的位数,n为所述当前任务中除数的位数,k为目标时钟周期数,表示向上取整。

[0115]

其中,所述位数确定模块包括:

[0116]

第二位数确定单元,用于利用第二位数确定规则确定有效被除位数,所述第二位数确定规则为:

[0117]

x

x

=q

x

n

‑

1;其中,x

x

为有效被除位数。

[0118]

其中,所述映射关系确定模块包括:

[0119]

目标商确定单元,用于基于所述目标位数确定不同情况下的目标商;

[0120]

阈值确定单元,用于根据不同情况下的目标商及所述除数,确定每个目标商对应的阈值;

[0121]

映射关系生成模块,用于利用每个目标商及对应的阈值,确定每个目标商对应的有效被除数范围,从而生成与不同目标商对应的商取值映射关系。

[0122]

其中,所述更新模块具体用于:对所述目标位数减一,得到更新后的目标位数,利用更新后的目标位数对所述有效被除位数进行更新,利用更新后的目标位数及所述除数对商取值映射关系进行更新。

[0123]

其中,所述补零模块具体用于:

[0124]

利用第三位数确定规则确定补零位数,所述第三位数确定规则为:

[0125]

h0=q

x

‑

1;其中,h0为补零位数,q

x

为目标位数。

[0126]

其中,所述第一组合模块包括:

[0127]

第三位数确定单元,用于利用第四位数确定规则确定取数位数,所述第四位数确定规则为:

[0128]

l0=n

‑1‑

h0;其中,l0为取数位数,n为所述当前任务中除数的位数;

[0129]

当前有效被除数生成单元,用于根据所述补零位数在上一时钟周期的余数的高位补零,并根据所述取数位数从所述被除数的未选取数中向后取数添加至所述余数的低位,生成当前时钟周期的当前有效被除数。

[0130]

参见图5,本发明实施例提供的一种电子设备结构示意图,包括:

[0131]

存储器21,用于存储计算机程序;

[0132]

处理器22,用于执行所述计算机程序时实现上述方法实施例所述的基于除法器的任务处理方法的步骤。

[0133]

在本实施例中,设备可以是pc(personal computer,个人电脑),也可以是智能手机、平板电脑、掌上电脑、便携计算机等终端设备。

[0134]

该设备可以包括存储器21、处理器22和总线23。

[0135]

其中,存储器21至少包括一种类型的可读存储介质,所述可读存储介质包括闪存、硬盘、多媒体卡、卡型存储器(例如,sd或dx存储器等)、磁性存储器、磁盘、光盘等。存储器21在一些实施例中可以是设备的内部存储单元,例如该设备的硬盘。存储器21在另一些实施例中也可以是设备的外部存储设备,例如设备上配备的插接式硬盘,智能存储卡(smart media card,smc),安全数字(secure digital,sd)卡,闪存卡(flash card)等。进一步地,存储器21还可以既包括设备的内部存储单元也包括外部存储设备。存储器21不仅可以用于存储安装于设备的应用软件及各类数据,例如执行任务处理方法的程序代码等,还可以用于暂时地存储已经输出或者将要输出的数据。

[0136]

处理器22在一些实施例中可以是一中央处理器(central processing unit,cpu)、控制器、微控制器、微处理器或其他数据处理芯片,用于运行存储器21中存储的程序代码或处理数据,例如执行任务处理方法的程序代码等。

[0137]

该总线23可以是外设部件互连标准(peripheral component interconnect,简称pci)总线或扩展工业标准结构(extended industry standard architecture,简称eisa)总线等。该总线可以分为地址总线、数据总线、控制总线等。为便于表示,图5中仅用一条粗线表示,但并不表示仅有一根总线或一种类型的总线。

[0138]

进一步地,设备还可以包括网络接口24,网络接口24可选的可以包括有线接口和/或无线接口(如wi

‑

fi接口、蓝牙接口等),通常用于在该设备与其他电子设备之间建立通信连接。

[0139]

可选地,该设备还可以包括用户接口25,用户接口25可以包括显示器(display)、输入单元比如键盘(keyboard),可选的用户接口25还可以包括标准的有线接口、无线接口。可选地,在一些实施例中,显示器可以是led显示器、液晶显示器、触控式液晶显示器以及oled(organic light

‑

emitting diode,有机发光二极管)触摸器等。其中,显示器也可以适当的称为显示屏或显示单元,用于显示在设备中处理的信息以及用于显示可视化的用户界面。

[0140]

图5仅示出了具有组件21

‑

25的设备,本领域技术人员可以理解的是,图5示出的结构并不构成对设备的限定,可以包括比图示更少或者更多的部件,或者组合某些部件,或者不同的部件布置。

[0141]

本发明实施例还提供一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现上述方法实施例所述的基于除法器的任务处理方法的步骤。

[0142]

其中,该存储介质可以包括:u盘、移动硬盘、只读存储器(read

‑

only memory,rom)、随机存取存储器(random access memory,ram)、磁碟或者光盘等各种可以存储程序代码的介质。

[0143]

本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。

[0144]

对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。