1.本发明涉及射频前端领域,尤其涉及一种低噪声放大器及基站射频前端。

背景技术:

2.随着无线通信技术的高速发展,基站的工作频率从最初的2g(800

‑

900mhz)、3g(1900

‑

2200mhz)、4g(2300

‑

2700mhz),到现在快速发展的5g(3300

‑

4200mhz),频率范围越来越宽。频率范围的拓展也让基站拥有的频谱容量不断的扩大,但是这也让基站工作系统面临更严峻的交替失真和邻近信道干扰。同时,基站工作的周围环境复杂,信号要求覆盖范围广,为此基站射频前端也必须要拥有一个高的接收灵敏度,而低噪声放大器作为基站射频前端电路中的关键模块,需要它能够同时满足时分复用(tdd)和频分复用(fdd)工作的需求,以及宽广的频段范围,可以降低基站射频前端的设计难度和成本;同时,低噪声放大器的噪声系数和增益也决定了基站射频前端系统的接收灵敏度,一个高的接收灵敏度,需要更低的噪声和更高的增益;低噪声放大器的高线性也是必不可少的,它可以让基站射频前端具有更强的抗干扰能力,提高频谱利用率,保证基站的频谱容量。因此,亟需一种满足上述需求的低噪声放大器。

技术实现要素:

3.本发明的目的在于通过一种低噪声放大器及基站射频前端,来解决以上背景技术部分提到的问题。

4.为达此目的,本发明采用以下技术方案:

5.一种低噪声放大器,其包括ttd控制电路、电流控制电路、输入匹配电路、输出匹配电路、第一级晶体管m001、第二级晶体管m002、反馈电路以及谐波抑制电路;其中,所述ttd控制电路的一端连接控制端口vsd,另一端与电阻r001的一端、电阻r002的一端、第二级晶体管m002的一端、谐波抑制电路的一端连接,电阻r001的另一端与第二级晶体管m002的第二接线端、输出匹配电路的一端连接,输出匹配电路的另一端连接输出端口rfout,第二级晶体管m002的第三接线端连接谐波抑制电路的第二接线端,所述电流控制电路的一端连接电流控制端口vb,另一端连接反馈电路的一端,所述反馈电路的第二接线端与输入匹配电路的一端、第一级晶体管m001的一端连接,输入匹配电路的另一端连接输入端口rfin,第一级晶体管m001的第二接线端与谐波抑制电路的第三接线端、电容c001的一端连接,电容c001的另一端连接谐波抑制电路的第四接线端,反馈电路的第三接线端连接谐波抑制电路的第五接线端,第一级晶体管m001的第三接线端与电感bl001的一端连接,电感bl001的另一端接地。

6.特别地,所述ttd控制电路由依次串接的n个反向器驱动下拉晶体管m003构成,其中,n为大于等于零的整数。

7.特别地,所述电流控制电路包括电容c031、电阻r031、电阻r032、晶体管m004、电阻r033;所述电容c031的一端接地,另一端接电流控制电路的a2端、电阻r031的一端、电阻

r032的一端连接,电阻r031的另一端接晶体管m004的一端,晶体管m004的第二接线端接地,晶体管m004的第三接线端与电阻r032的一端、电阻r033的一端连接,电阻r033的另一端接电流控制端口vb。

8.特别地,所述反馈电路包括电阻r003和电容c002;所述电阻r003的一端接输入匹配电路的一端,电阻r003的另一端接电容c002的一端,电容c002的另一端接谐波抑制电路。

9.特别地,所述谐波抑制电路包括电感l002、电感l003、电容c003、电容c004;所述电感l002的一端与电感l003、电容c004的一端连接,电容c004的另一端接地,电感l002的另一端与电容c003的一端连接,电容c003的另一端接地。

10.特别地,所述输入匹配电路采用但不限于金丝电感、片上有源或无源器件、片外分离器件任一种实现。

11.特别地,所述输出匹配电路采用但不限于金丝电感、片上有源或无源器件、片外分离器件任一种实现。

12.特别地,所述第一级晶体管m001、第二级晶体管m002均采用但不限于场效应管(fet)或双级晶体管(bjt)任一种。

13.特别地,所述谐波抑制电路采用但不限于l形滤波电路、t型滤波电路、π型滤波电路的任一种。

14.本发明还公开一种基站射频前端,该基站射频前端采用上述低噪声放大器。

15.本发明提出的低噪声放大器及基站射频前端通过tdd控制电路使低噪声放大器可以同时应用于基站的ttd系统和fdd系统中;通过两级放大和超宽带设计使低噪声放大器拥有高的增益和覆盖0.6

‑

4.2ghz的工作频段,从而使其能应用于2g、3g、4g以及正在快速发展的5g通信系统中,达到高集成、节约成本以及降低基站射频前端设计复杂度的目的;通过谐波抑制电路可以使低噪声放大器在0.6

‑

4.2ghz范围内,保证非常高的线性,从而改善交调失真和邻近信道干扰,同时通过电流控制电路,可以调节低噪声放大器总电流的大小来控制线性度,使用户可以根据不同的应用场景来折中低噪声放大器线性度和功耗。

附图说明

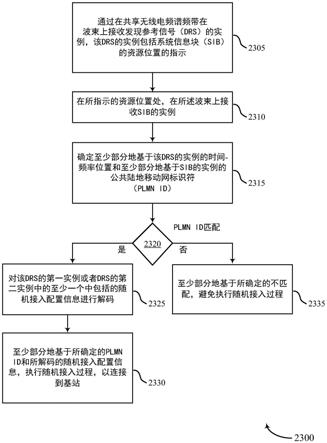

16.图1为本发明实施例提供的低噪声放大器结构框图;

17.图2为本发明实施例提供的tdd控制电路原理图;

18.图3为本发明实施例提供的电流控制电路原理图;

19.图4为本发明实施例提供的低噪声放大器电路结构图。

具体实施方式

20.为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的较佳实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容理解的更加透彻全面。需要说明的是,当一个元件被认为是“连接”另一个元件,它可以是直接连接到另一个元件或者可能同时存在居中元件。除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。本文所使用的术语

“

及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

21.实施例一

22.本实施例中低噪声放大器具体包括ttd控制电路001、输出匹配电路002、电流控制电路003、输入匹配电路004、第一级晶体管m001、第二级晶体管m002、反馈电路以及谐波抑制电路005。所述ttd控制电路001的一端连接控制端口vsd,另一端与电阻r001的一端、电阻r002的一端、第二级晶体管m002的一端、谐波抑制电路005的一端连接,电阻r001的另一端与第二级晶体管m002的第二接线端、输出匹配电路002的一端连接,输出匹配电路002的另一端连接输出端口rfout,第二级晶体管m002的第三接线端连接谐波抑制电路005的第二接线端,所述电流控制电路003的一端连接电流控制端口vb,另一端连接反馈电路的一端,所述反馈电路的第二接线端与输入匹配电路004的一端、第一级晶体管m001的一端连接,输入匹配电路004的另一端连接输入端口rfin,第一级晶体管m001的第二接线端与谐波抑制电路005的第三接线端、电容c001的一端连接,电容c001的另一端连接谐波抑制电路005的第四接线端,反馈电路的第三接线端连接谐波抑制电路005的第五接线端,第一级晶体管m001的第三接线端与电感bl001的一端连接,电感bl001的另一端接地。

23.实施例二

24.请参照图1所示,图1为本发明实施例提供的低噪声放大器结构框图。

25.本实施例中低噪声放大器具体包括ttd控制电路001、输出匹配电路002、电流控制电路003、输入匹配电路004、第一级晶体管m001、第二级晶体管m002、反馈电路以及谐波抑制电路005。所述ttd控制电路001的一端连接控制端口vsd,另一端与电阻r001的一端、电阻r002的一端、第二级晶体管m002的一端、谐波抑制电路005的一端连接,电阻r001的另一端与第二级晶体管m002的第二接线端、输出匹配电路002的一端连接,输出匹配电路002的另一端连接输出端口rfout,第二级晶体管m002的第三接线端连接谐波抑制电路005的第二接线端,所述电流控制电路003的一端连接电流控制端口vb,另一端连接反馈电路的一端,所述反馈电路的第二接线端与输入匹配电路004的一端、第一级晶体管m001的一端连接,输入匹配电路004的另一端连接输入端口rfin,第一级晶体管m001的第二接线端与谐波抑制电路005的第三接线端、电容c001的一端连接,电容c001的另一端连接谐波抑制电路005的第四接线端,反馈电路的第三接线端连接谐波抑制电路005的第五接线端,第一级晶体管m001的第三接线端与电感bl001的一端连接,电感bl001的另一端接地。

26.具体的,在本实施例中如图2所示,所述ttd控制电路001由021

‑

02n共计n个不等的反相器驱动下拉晶体管m003构成,其中,n为大于等于零的整数,n可以取0,根据逻辑控制决定,当低噪声放大器工作于tdd系统中时用于使能低噪声放大器,使低噪声放大器能够根据需要随时开启和关闭,并且ttd控制电路001也保证了低噪声放大器在关闭时,拥有非常高的隔离度。

27.在本实施例中电流控制电路003主要通过控制电流控制电路003端口的电压变化从而控制电流控制电路003里面的电流变化以实现对低噪声放大器电流的控制。具体的,在本实施例中如图3所示,在本实施例中所述电流控制电路003包括电容c031、电阻r031、电阻r032、晶体管m004、电阻r033;所述电容c031的一端接地,另一端接电流控制电路003的a2端、电阻r031的一端、电阻r032的一端连接,电阻r031的另一端接晶体管m004的一端,晶体管m004的第二接线端接地,晶体管m004的第三接线端与电阻r032的一端、电阻r033的一端

连接,电阻r033的另一端接电流控制端口vb。具体的,在本实施例中所述反馈电路包括电阻r003和电容c002;所述电阻r003的一端接输入匹配电路004的一端,电阻r003的另一端接电容c002的一端,电容c002的另一端接谐波抑制电路005。电流控制电路003工作时,通过控制vb端的电压来控制晶体管m004的电流大小,进而来控制低噪声放大器电流的大小,从而达到控制低噪声放大器线性度和功耗的目的。所述电流控制电路003的a2端与电阻r003和电容c002相连接。当工作系统中需要较高的线性度来抑制邻近通道干扰时,可以通过提高vb处的电压来提高工作电流,从而来提高线性度;当工作系统对功耗比较关心时,同时对线性度需求不太高时,可以通过降低vb的电压来降低工作电流,从而达到降低功耗的目的。

28.具体的,在本实施例中所述第一级晶体管m001、第二级晶体管m002均采用但不限于场效应管(fet)或双级晶体管(bjt)任一种。

29.具体的,在本实施例中所述谐波抑制电路005采用但不限于l形滤波电路、t型滤波电路、π型滤波电路的任一种。所述谐波抑制电路005主要作用是抑制第一级晶体管m001出来的谐波和交调分量。当信号从第一级晶体管m001出来后分两路到谐波抑制网络中,其中一部分高频信号通过电容c002进入谐波抑制网络进入第二级晶体管m002,其余信号直接进入谐波抑制电路005,谐波抑制电路005中的滤波网络将滤除掉大部分的交调分量和高次谐,从而改善线性,同时谐波抑制电路005也充当第一级晶体管m001和第二级晶体管m002级间匹配的一部分,从而拓展了带宽。

30.实施例三

31.请参照图4所示,图4为本发明实施例提供的低噪声放大器结构框图。

32.本实施例中低噪声放大器具体包括ttd控制电路001、输出匹配电路002、电流控制电路003、输入匹配电路004、第一级晶体管m001、第二级晶体管m002、反馈电路以及谐波抑制电路005。所述ttd控制电路001的一端连接控制端口vsd,另一端与电阻r001的一端、电阻r002的一端、第二级晶体管m002的一端、谐波抑制电路005的一端连接,电阻r001的另一端与第二级晶体管m002的第二接线端、输出匹配电路002的一端连接,输出匹配电路002的另一端连接输出端口rfout,第二级晶体管m002的第三接线端连接谐波抑制电路005的第二接线端,所述电流控制电路003的一端连接电流控制端口vb,另一端连接反馈电路的一端,所述反馈电路的第二接线端与输入匹配电路004的一端、第一级晶体管m001的一端连接,输入匹配电路004的另一端连接输入端口rfin,第一级晶体管m001的第二接线端与谐波抑制电路005的第三接线端、电容c001的一端连接,电容c001的另一端连接谐波抑制电路005的第四接线端,反馈电路的第三接线端连接谐波抑制电路005的第五接线端,第一级晶体管m001的第三接线端与电感bl001的一端连接,电感bl001的另一端接地。

33.具体的,在本实施例中所述反馈电路包括电阻r003和电容c002;所述电阻r003的一端接输入匹配电路004的一端,电阻r003的另一端接电容c002的一端,电容c002的另一端接谐波抑制电路005。具体的,在本实施例中所述输入匹配电路004采用但不限于金丝电感、片上有源或无源器件、片外分离器件任一种实现。所述输出匹配电路002采用但不限于金丝电感、片上有源或无源器件、片外分离器件任一种实现。如图4所示,bl002和bl003金丝电感构成了输入输出匹配。所述谐波抑制电路005包括电感l002、电感l003、电容c003、电容c004;所述电感l002的一端与电感l003、电容c004的一端连接,电容c004的另一端接地,电感l002的另一端与电容c003的一端连接,电容c003的另一端接地,其中c003、l002、c004、

l003为π型谐波抑制电路005,反馈电容c002连接于电感l002的右边。需要说明的是,反馈电容c002可以连接于电感l002左端或者右端。

34.需要说明的是本发明实例中所提供的低噪声放大器的制造工艺可以是cmos(complementary metal oxide semiconductor,互补金属氧化物半导体)、soi(silicon

‑

on

‑

insulator,绝缘衬底上的硅)、sige、gaas

‑

phemt(pseudomorphic hemt)、hbt(hetero

‑

junction bipolartransistor,异质结双极晶体管)、bjt(bipolar junction transistor,双极结型晶体管)、bicmos等多种工艺。

35.实施例四

36.本实施例提出一种基站射频前端,该基站射频前端采用但不限于上述实施例一至实施例三公开的任一低噪声放大器

37.本发明提出的技术方案通过tdd控制电路使低噪声放大器可以同时应用于基站的ttd系统和fdd系统中;通过两级放大和超宽带设计使低噪声放大器拥有高的增益和覆盖0.6

‑

4.2ghz的工作频段,从而使其能应用于2g、3g、4g以及正在快速发展的5g通信系统中,达到高集成、节约成本以及降低基站射频前端设计复杂度的目的;通过谐波抑制电路可以使低噪声放大器在0.6

‑

4.2ghz范围内,保证非常高的线性,从而改善交调失真和邻近信道干扰,同时通过电流控制电路,可以调节低噪声放大器总电流的大小来控制线性度,使用户可以根据不同的应用场景来折中低噪声放大器线性度和功耗。另外,采用phemt工艺和两级放大使该低噪声放大器拥有极低噪声系数和较高的增益,提高了基站射频前端系统的接收灵敏度。

38.注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。