面向wimax协议的qc

‑

ldpc译码器译码方法及系统

技术领域

1.本发明涉及一种面向wimax协议的qc

‑

ldpc译码器译码方法及系统,特别是涉及qc

‑

ldpc译码技术领域。

背景技术:

2.ldpc码的全称是低密度奇偶校验码(low density parity check code),是一种具有稀疏校验矩阵的线性分组码。其主要的特点是其校验矩阵的稀疏性,即校验矩阵中“1”的密度很低,并且码长越长,密度越低。ldpc码具有很好的误码性能,其误码性能可以逼近香农极限,近些年来ldpc码的各项相关技术发展迅速,被广泛用于通信领域,因此研究性能高、硬件实现简单的ldpc译码器显得尤为重要。

3.相较于软件实现ldpc编码,硬件实现ldpc译码显得格外复杂,因此早期的ldpc译码实现基本是在软件层面,很难映射到硬件层面。近些年来,随着研究人员对ldpc译码相关算法研究的突破,适用于硬件的ldpc译码算法不断出现,从最初的基于概率的ldpc迭代译码算法、基于对数的ldpc迭代译码算法到之后的最小和min

‑

sum算法,硬件实现ldpc译码器变得越来越容易。

4.然而,传统的ldpc译码器在硬件实现时过于看重对算法的映射实现,未考虑到ldpc码本身的诸多特性,在具体实现时不仅使用了大量的硬件存储资源,还占据了很多的计算资源,这对硬件实现过程中的布线和时序提出了更高的需求。

技术实现要素:

5.发明目的:提供一种面向wimax协议的qc

‑

ldpc译码器译码方法及系统,以解决现有技术存在的上述问题。通过存储的qc

‑

ldpc校验矩阵信息,简化了译码器的译码计算复杂度,从而节省了硬件计算资源,克服现有技术的不足。

6.技术方案:第一方面,提出了一种面向wimax协议的qc

‑

ldpc译码器,该译码器具体包括:译码控制器、存储单元和运算单元模块。其中译码控制器作为连接存储单元和运算单元模块之间的架构,用于实现彼此之间的数据交互。利用存储在存储单元中的校验矩阵信息,可以简化译码器的译码计算复杂度,同时节省硬件计算资源。

7.在第一方面的可实现方式中,译码控制器,被设置为实现译码运算所需数据的读取、分发、运算以及计算结果的存储,用于控制译码器的工作流程。进一步包括:运算控制模块、地址生成模块、分发模块。

8.存储单元,被设置为存储变量节点信息、校验节点信息和校验矩阵信息;该单元根据需求划分为三组数据存储块,第一组数据存储块用于存储所述变量节点信息;第二组数据存储块用于存储校验节点信息;第三组数据存储块用于存储校验矩阵信息。

9.运算模块,被设置为更新变量节点信息与校验节点信息,进一步包括节点更新单元,所述节点更新单元在译码过程中,采用流水设计实现更新校验节点信息的同时更新变量节点信息。

10.其中,节点更新单元包括:定点加法器、定点比较器、异或计算模块、以及绝对值计算模块。在进一步的实施例中,由于802.16标准中qc

‑

ldpc码的校验矩阵,行重6占比2/3,行重7占比1/3,因此该节点运算单元的输入输出的信息个数最大为14,最小为12。定点比较器用于最小值与次小值计算模块,该模块需要从输入的7个或6个变量节点的绝对值中找出最小值与次小值,由基本结构com2和com4构成,共包含13个比较器以及20个选择器,计算时分3级流水寻得最小值与次小值,为方便计算,该计算单元设置为8输入。

11.第二方面,提出一种面向wimax协议的qc

‑

ldpc译码方法,该方法具体包括以下步骤:

12.步骤一、预设迭代次数,并初始化校验节点信息、变量节点信息,并将当前迭代次数置为1;

13.步骤二、接收待进行译码的数据序列信息,并按照划分出的数据存储块区域存储至存储单元;

14.步骤三、译码控制器读取存储单元中的校验矩阵信息,结合运算模块分层更新校验节点信息与变量节点后验概率信息;

15.步骤四、迭代次数加1后,判断当前迭代值是否大于预设值,若判断结果为是,则跳转至步骤五;反之,跳转至步骤三;

16.步骤五、停止译码,输出译出的码字信息,并采用定点数据计算获取变量节点后验概率的符号位;

17.步骤六、将比变量节点后验概率的符号位搬运至存储单元,作为最终的结果码字,完成译码过程。

18.在第三方面的可实现方式中,采用行分层译码进行译码的过程如下:

19.译码器接收到的待进行译码的数据序列信息为y=(y0,y1,...,y

n

‑1),校验矩阵分为k层,每层子矩阵的列重至多为1。t表示迭代次数,k表示消息更新到第k层,初始化时t和k均为0;(t,k)表示第t次迭代中的第k层运算。表示运算到第t次迭代中的第k层时,变量节点l的后验概率;表示第t次迭代中,每层矩阵中的第m行第l列的校验节点传递给变量节点的消息;表示第t次迭代中的第k层时,每层矩阵中的第m行第l列的变量节点传递给校验节点的消息。在进一步的实施例中,译码过程包括初始化、迭代和比特判决的过程如下:

20.初始化包括后验概率初始化和校验节点消息初始化,即

[0021][0022][0023]

迭代过程通过分层更新的方式实现,更新内容包括:变量节点消息更新、校验节点消息更新和后验概率消息更新。其中,变量节点消息更新的表达式为:

[0024][0025]

校验节点消息更表达式为:

[0026][0027]

式中,l(m)\l表示与校验节点m相邻的变量节点出去节点l的集合;β表示offset min

‑

sum算法中的偏移因子。

[0028]

后验概率消息更新表达式为:

[0029][0030]

在进一步的实施例中,当译码迭代次数达到设定的最大值,停止译码并进行比特判决。判决时,如果则判决反之,其中表示变量节点后验概率的符号位。

[0031]

在第二方面的可实现方式中,在分层更新校验节点信息与变量节点后验概率信息时,针对其中第i次迭代、第j层的校验矩阵信息对应的信息节点更新步骤如下:

[0032]

译码控制器控制校验矩阵信息地址生成模块从校验矩阵信息存储区域取出第j层的校验矩阵数据信息;其中校验矩阵信息为稀疏矩阵,译码过程中,根据稀疏的校验矩阵信息定位每次需要更新的变量节点的位置,将变量节点更新位置的计算过程转化为数据映射关系。

[0033]

校验节点信息地址生成模块和变量节点信息地址生成模块根据所述校验矩阵数据信息找到当前层需要更新的校验节点以及变量节点并取出数据。

[0034]

校验节点信息分发模块和变量节点信息分发模块将取出的数据送至运算单元。

[0035]

运算单元运算完成后,将更新好的校验节点和变量节点值送至校验节点信息分发模块和变量节点信息分发模块。

[0036]

校验节点信息地址生成模块和变量节点信息地址生成模块再根据所述校验矩阵数据信息,原位存储校验节点和变量节点,完成第i次迭代第j层校验矩阵信息对应的信息节点更新。

[0037]

执行译码过程时,将后验概率初始化隐藏在数据的存储过程中,即将译码的源数据存储过程作为后验概率的初始化;将校验节点消息初始化隐藏在第一次迭代计算中,即第一次迭代计算取校验节点消息时,固定给数据0。

[0038]

在第二方面的一些可实现方式中,进一步是面向ieee 802.16e标准下1/2码率的ldpc译码,通过改变膨胀因子z,该方法支持1/2码率下的19种码长的译码,码长范围是576~2304,以96为间隔,相应地,z的范围是24~96,以4为间隔。

[0039]

在第二方面的一些可实现方式中,提出一种校验矩阵信息的稀疏化存储方法,用于译码器中的存储单元的数据存储,该方法具体为:将校验矩阵的每一行中“1”的位置信息用预设的比特数值表示出来。进一步的根据预设大小划分三个组别,第一组用于代表校验矩阵每一行中“1”在哪一个数据存储块中;第二组用于代表“1”在各数据存储块中的位置;第三组用于代表各数据存储块中1的位置信息在第二组的存储位置

[0040]

在第二方面的一些可实现方式中,ieee 802.16e标准下1/2码率的ldpc码校验信息矩阵为稀疏矩阵,其大小为12

×

24块,每一块大小为z

×

z,有用信息为每一行的“1”所在的位置信息,矩阵行重最高为7,最低为6。

[0041]

存储过程中将校验矩阵的每一行中“1”的位置信息用有限的(12

×

z)

×

152bit表

示出来,从而方便存储与利用。具体形式为:bit0~bit23表示校验矩阵每一行中“1”在哪一个块中;bit24~bit79以8bit为一组,共7组,代表“1”在各块中的位置;当块中有“1”时,bit80~bit151以3bit为一组,共24组,表示“1”的位置信息存储在bit24~bit79中的组别。

[0042]

第三方面,提出一种面向wimax协议的qc

‑

ldpc译码系统,该系统包括:

[0043]

初始化模块、被设置为初始化对应参数;所述对应参数包括预设迭代总系数、校验节点信息、变量节点信息,以及初始化当前迭代次数为1;

[0044]

数据接收模块,被设置为接收待进行译码的数据序列;

[0045]

译码器,被设置为接收数据接收模块获取到的数据序列,并进行译码;进一步包括译码控制器、存储单元和运算单元,所述译码器

[0046]

数据输出模块,被设置为输出译码器最终的译码结果。

[0047]

有益效果:本发明提出了一种面向wimax协议的qc

‑

ldpc译码器译码方法及系统,其包括以下有益效果:1、支持ieee802.16e通信协议下,1/2码率,19种码长的译码计算,可兼容性好,所支持的19种码长范围为576~2304,间隔96取值,属于中短码,在此范围内qc

‑

ldpc码有较优的误码性能表现。2、利用存储的qc

‑

ldpc校验矩阵信息,简化译码器的译码计算复杂度,从而节省了硬件计算资源。3、采用行分层译码方式作为译码方法,具有硬件友好、易于实现的优点。4、采用流水设计,在计算资源使用量小的情况下依旧有着较高的吞吐率。

[0048]

综上所述,本发明可以在保证ldpc译码性能的同时,提高存储资源利用率,降低计算复杂度与计算资源的使用。

附图说明

[0049]

图1是本发明中qc

‑

ldpc译码器的硬件结构图。

[0050]

图2是本发明中qc

‑

ldpc译码器的节点更新单元示意图。

[0051]

图3是本发明中节点更新单元加法器结构图。

[0052]

图4是本发明中节点更新单元最小值次小值寻值计算单元结构图。

[0053]

图5是本发明中qc

‑

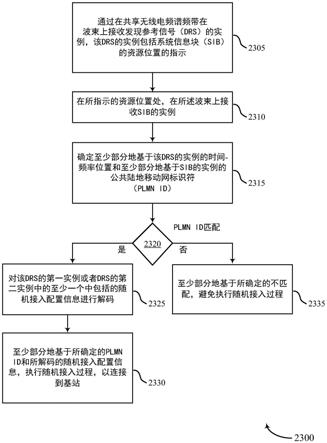

ldpc译码器译码流程图

具体实施方式

[0054]

在下文的描述中,给出了大量具体的细节以便提供对本发明更为彻底的理解。然而,对于本领域技术人员而言显而易见的是,本发明可以无需一个或多个这些细节而得以实施。在其他的例子中,为了避免与本发明发生混淆,对于本领域公知的一些技术特征未进行描述。

[0055]

实施例一

[0056]

由于传统的ldpc译码器在硬件实现过程中,过于看重对算法的映射实现,未考虑到ldpc码本身的诸多特性,占据大量存储资源的同时还浪费了较多的计算资源,提高了硬件实现时的布线和时序需求。本实施例提出一种面向wimax协议的qc

‑

ldpc译码器译码系统,利用存储的qc

‑

ldpc校验矩阵信息,简化了译码器的译码计算复杂度,从而节省了硬件计算资源。具体的,如图1所示,该系统中的qc

‑

ldpc译码器包括:

[0057]

译码控制器、存储单元和运算单元,其中,ldpc译码控制器用于控制译码器的工作

流程;存储单元用于存储校验矩阵信息、校验节点信息以及变量节点信息;运算单元用于更新变量节点与校验节点信息。

[0058]

译码控制器接收待进行译码的数据序列信息,并按照划分出的数据存储块区域存储至存储单元;译码控制器读取存储单元中的校验矩阵信息,结合运算模块分层更新校验节点信息与变量节点后验概率信息;迭代次数加1后,判断当前迭代值是否大于预设值,若判断结果为是,则停止译码,输出译出的码字信息,并采用定点数据计算获取变量节点后验概率的符号位;反之,译码控制器重新读取存储单元中的校验矩阵信息,并结合运算模块分层更新校验节点信息与变量节点后验概率信息,再次判断迭代值是否大于预设值;最后,将比变量节点后验概率的符号位搬运至存储单元,作为最终的结果码字,完成译码过程。

[0059]

实施例二

[0060]

在实施例一的基础上,译码控制器进一步包括运算控制模块、地址生成模块、分发模块。

[0061]

存储单元,被设置为存储变量节点信息、校验节点信息和校验矩阵信息;该单元根据需求划分为三组数据存储块,第一组数据存储块用于存储所述变量节点信息;第二组数据存储块用于存储校验节点信息;第三组数据存储块用于存储校验矩阵信息。在进一步的实施例中,存储单元包含40个bank,其中bank0~23用于存储24块变量节点信息,bank24~30用于存储校验节点信息,bank32~40用于存储校验矩阵信息。

[0062]

运算模块,被设置为更新变量节点信息与校验节点信息,进一步包括节点更新单元,所述节点更新单元在译码过程中,采用流水设计实现更新校验节点信息的同时更新变量节点信息。

[0063]

其中,如图2所示,节点更新单元包括:定点加法器、定点比较器、异或计算模块、以及绝对值计算模块。在进一步的实施例中,由于802.16标准中qc

‑

ldpc码的校验矩阵,行重6占比2/3,行重7占比1/3,因此该节点运算单元的输入输出的信息个数最大为14,最小为12,即校验节点信息与变量节点信息各一半。

[0064]

定点比较器用于最小值与次小值计算模块,该模块需要从输入的7个或6个变量节点的绝对值中找出最小值与次小值,由基本结构com2和com4构成,共包含13个比较器以及20个选择器,计算时分3级流水寻得最小值与次小值,为方便计算,该计算单元设置为8输入。

[0065]

以更新行重7的行为例,加法器的结构如图3所示,共需要7个定点加法器,节点更新单元共需要14个定点加法器。

[0066]

校验节点消息更新表达式表明校验节点在更新时,需要从输入的7个或6个变量节点的绝对值中找出最小值与次小值,使用定点比较器完成该计算过程。最小值与次小值的寻值计算单元基本结构如图4所示。可以看出,该计算单元由基本结构com2和com4构成,共包含13个比较器以及20个选择器,计算时分3级流水寻得最小值与次小值。为方便计算,该计算单元设置为8输入。

[0067]

利用存储的qc

‑

ldpc校验矩阵信息,简化译码器的译码计算复杂度,从而节省了硬件计算资源。

[0068]

实施例三

[0069]

提出一种面向wimax协议的qc

‑

ldpc译码方法,该方法具体包括以下步骤:

[0070]

步骤一、预设迭代次数,并初始化校验节点信息、变量节点信息,并将当前迭代次数置为1;

[0071]

步骤二、接收待进行译码的数据序列信息,并按照划分出的数据存储块区域存储至存储单元;

[0072]

步骤三、译码控制器读取存储单元中的校验矩阵信息,结合运算模块分层更新校验节点信息与变量节点后验概率信息;

[0073]

步骤四、迭代次数加1后,判断当前迭代值是否大于预设值,若判断结果为是,则跳转至步骤五;反之,跳转至步骤三;

[0074]

步骤五、停止译码,输出译出的码字信息,并采用定点数据计算获取变量节点后验概率的符号位;

[0075]

步骤六、将比变量节点后验概率的符号位搬运至存储单元,作为最终的结果码字,完成译码过程。

[0076]

在进一步的实施例中,采用qc

‑

ldpc译码器基于verilog hdl语言进行硬件设计,利用vcs以及fpga完成了基本的测试验证。以z=96,码长2304,迭代次数设置为5为例。具体的,实现过程包括以下步骤:

[0077]

步骤1、校验节点、变量节点初始化,迭代次数置为1;

[0078]

步骤2、根据公式步骤2、根据公式和分层更新校验节点信息与变量节点后验概率信息;式中,t表示迭代次数;k表示当前更新到第k层;(t,k)表示第t次迭代中的第k层运算;表示第t次迭代中的第k层时,每层矩阵中的第m行第l列的变量节点传递给校验节点的消息;表示运算到第t次迭代中的第k层时,变量节点l的后验概率;表示第t次迭代中,每层矩阵中的第m行第l列的校验节点传递给变量节点的消息;l(m)\l表示与校验节点m相邻的变量节点出去节点l的集合;β表示offset min

‑

sum算法中的偏移因子。

[0079]

步骤3、迭代次数加1,若迭代次数不大于设定的最大迭代次数5,跳回步骤2;

[0080]

步骤4、输出译出的码字信息;

[0081]

步骤5、完成译码运算。

[0082]

在进一步的实施例中,首先从ddr中将校验矩阵信息搬运至bank32

‑

bank40中,将待译码变量节点信息初始化至bank0

‑

bank23中;源数据就位后,开始译码运算,执行上述流程,完成译码运算;最后从bank0

‑

bank23将变量节点后验概率的符号位搬运至ddr中,作为最终的结果码字。

[0083]

采用基于行分层译码算法作为译码方法,具有硬件友好、易于实现的优点。同时节点更新单元,可流水地同时更新校验节点信息和变量节点信息,采用流水设计,在计算资源使用量小的情况下依旧有着较高的吞吐率。

[0084]

实施例四

[0085]

在实施例三的基础上,第i次迭代第j层校验矩阵信息对应的信息节点更新过程如下:

[0086]

控制器控制校验矩阵信息地址生成模块从校验矩阵信息存储区域取出第j层的152bit信息;

[0087]

校验节点信息地址生成模块和变量节点信息地址生成模块根据152bit信息找到当前层需要更新的校验节点以及变量节点并取出数据;

[0088]

校验节点信息分发模块和变量节点信息分发模块将2类数据送至nuu运算单元;

[0089]

nuu运算单元运算完成后,将更新好的校验节点和变量节点值送至校验节点信息分发模块和变量节点信息分发;

[0090]

校验节点信息地址生成模块和变量节点信息地址生成模块再根据之前的152bit信息,原位存储校验节点和变量节点,完成第i次迭代第j层校验矩阵信息对应的信息节点更新。

[0091]

在此实施例下,译码器完成译码需要6761cycle,译码器工作频率在1ghz时吞吐率为170.4mbps。本发明在保证性能的同时考虑减少计算资源以及存储资源,未将译码方式设置为行分层并行译码。若进一步增加存储资源以及计算资源,可极大的提升译码器的吞吐率,例如采用12路并行计算,译码器工作频率在1ghz时吞吐率可达2gbps。

[0092]

实施例五

[0093]

提出一种面向wimax协议的qc

‑

ldpc译码系统,该系统包括:

[0094]

初始化模块、被设置为初始化对应参数;所述对应参数包括预设迭代总系数、校验节点信息、变量节点信息,以及初始化当前迭代次数为1;

[0095]

数据接收模块,被设置为接收待进行译码的数据序列;

[0096]

译码器,包括译码控制器、存储单元和运算单元,译码器被设置为接收数据接收模块获取到的数据序列,并进行译码;

[0097]

数据输出模块,被设置为输出译码器最终的译码结果。

[0098]

综合以上实施例所述,本发明支持wimax协议的ieee802.16e标准通信协议下,1/2码率,19种码长的译码计算,可兼容性好;利用存储的qc

‑

ldpc校验矩阵信息,简化译码器的译码计算复杂度,从而节省了硬件计算资源;采用基于offset min

‑

sum的行分层译码算法作为译码方法,具有硬件友好、易于实现的优点;采用流水设计,在计算资源使用量小的情况下依旧实现了有着较高的吞吐率的译码运算。

[0099]

如上所述,尽管参照特定的优选实施例已经表示和表述了本发明,但其不得解释为对本发明自身的限制。在不脱离所附权利要求定义的本发明的精神和范围前提下,可对其在形式上和细节上做出各种变化。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。