1.本公开一般涉及模拟数字转换器(ad转换器)、使用该模拟数字转换器的传感器系统以及测试系统,更详细地涉及对模拟信号进行数字变换的ad转换器、使用了该ad转换器的传感器系统以及测试系统。

背景技术:

2.以往,已知有维持逐次比较型ad变换器的低功耗,谋求如δ∑型ad变换器那样的高分辨率化的噪声整形(noise shaping)型逐次比较ad变换器(ad转换器)(例如,参照专利文献1)。

3.专利文献1的噪声整形型逐次比较ad变换器是在通常的逐次比较型ad变换器中追加了积分电路的结构。在专利文献1的噪声整形型逐次比较ad变换器中,对将逐次比较动作进行到lsb(最下位比特)之后的电容dac(数字模拟转换器)的残差电压进行积分,并反馈到下一个采样,从而在输出数据中得到噪声整形特性。

4.在先技术文献

5.专利文献

6.专利文献1:日本特开2017

‑

147712号公报

技术实现要素:

7.在ad转换器中,为了谋求输出数据的高分辨率化,噪声整形型ad变换器的数字滤波器等的数字变换处理需要时间,因此等待时间(1atency)变大。因此,在使用ad转换器的输出数据进行判定传感器系统是否为异常状态的测试处理的情况下,存在测试处理的时间变长的担忧。

8.本公开是鉴于上述情形而完成的,其目的在于,提供一种能够谋求测试处理的时间的缩短的ad转换器以及使用该ad转换器的传感器系统以及测试系统。

9.本公开的一个方式涉及的ad转换器具备输入部、ad变换部、第1输出部、以及第2输出部。输入部被输入从传感器输出的模拟信号。ad变换部对模拟信号进行数字变换并生成第1数字数据以及第2数字数据。第1输出部将第1数字数据输出到控制电路。第2输出部在第1输出部输出第1数字数据之前,将第2数字数据输出到测试控制部。测试控制部在测试模式下,基于第2数字数据判定包含传感器的传感器系统是否为异常状态。

10.本公开的一个方式涉及的传感器系统具备:本公开的一个方式涉及的ad转换器;以及传感器。

11.本公开的一个方式涉及的测试系统具备:本公开的一个方式涉及的传感器系统;以及测试控制部。

12.在本公开中,具有能够谋求测试处理的时间的缩短这样的效果。

附图说明

13.图1是包含本公开的一个实施方式涉及的ad转换器的传感器系统以及测试系统的框图。

14.图2是本公开的一个实施方式涉及的ad转换器的动作说明图。

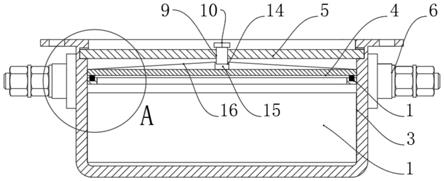

15.图3是包含本公开的一个实施方式的第1变形例以及第2变形例涉及的ad转换器的传感器系统以及测试系统的框图。

具体实施方式

16.以下说明的实施方式以及变形例只不过是本公开的一个例子,本公开并不限定于实施方式以及变形例。除了该实施方式以及变形例以外,只要不脱离本公开的技术的思想的范围,则也能够根据设计等进行各种变更。

17.(实施方式)

18.(1)结构

19.在图1示出具备本实施方式涉及的ad转换器1(ad:analog to digital,模拟到数字)的传感器系统100、测试系统300的框图。

20.本实施方式的ad转换器1构成为用于传感器系统100的模拟前端(传感器处理电路10),对来自传感器101的模拟信号进行数字变换。

21.传感器处理电路10具备ad转换器1和放大器11,对来自传感器101的信号进行信号处理并输出到控制电路200。

22.传感器系统100具备传感器101和传感器处理电路10。

23.测试系统300具备传感器系统100和测试控制部301。测试控制部301基于ad转换器1的输出数据判定传感器系统100是否为异常状态。

24.传感器101构成为对测定对象的物理量、或其变化量进行检测。传感器101将包含与检测结果对应的电压值、或电容器的电容值的变化在内的模拟信号输出到传感器处理电路10。也就是说,传感器101作为输出模拟信号的信号输出部发挥功能。传感器处理电路10对从传感器101输出的模拟信号进行数字变换并输出到控制电路200。

25.在本实施方式中,作为一个例子,传感器系统100应用于机动车等移动体。传感器101是将移动体的加速度作为测定对象进行检测的加速度传感器。收取传感器101的检测结果的控制电路200是搭载在机动车的ecu(electronic control unit,电子控制单元)。另外,这些是一个例子,传感器101并不限于加速度传感器,也可以是陀螺仪传感器、压力传感器、运动传感器等。此外,传感器系统100也可以应用于与机动车等移动体不同的装置。

26.传感器处理电路10是对来自传感器101的模拟信号进行信号处理并输出到控制电路200的模拟前端。

27.传感器处理电路10具备ad转换器1和放大器11。

28.放大器11构成为对来自传感器101的模拟信号进行放大。在放大器11被输入传感器101输出的模拟信号。放大器11在所输入的模拟信号为电压的情况下,以给定的放大率对振幅进行放大,或在模拟信号为电容值的变化的情况下,在将该电容值的变化变换为电压或电流的变化之后以给定的放大率进行放大,并输出到与后级连接的ad转换器1。

29.ad转换器1具备ad变换部2、输入部3、第1输出部41以及第2输出部42,将模拟信号

的振幅变换为给定比特数的数字数据并输出到控制电路200以及测试控制部301。在本实施方式中,作为一个例子,ad转换器1构成为将21比特的数字数据(第1数字数据)输出到控制电路200,将9比特的数字数据(第2数字数据)输出到测试控制部301。另外,第1数字数据以及第2数字数据的比特数是一个例子,并不限于该值。

30.输入部3与放大器11电连接。输入部3经由放大器11被输入从传感器101输出的模拟信号。

31.ad变换部2具备第1ad变换器21、第2ad变换器22和数字滤波器23。第1ad变换器21和第2ad变换器22级联连接(串联连接),第2ad变换器22设置在第1ad变换器21的前级。

32.第2ad变换器22是逐次比较型ad变换器(sar:successive approximation register)。第2ad变换器22具备电容da转换器(da:digital to analog,数字到模拟)。电容da转换器具有多个电容器(电容元件)。各电容器的一端与输入部3电连接,另一端选择性地与第1电压源和第2电压源中的任意一方电连接。第1电压源和第2电压源的输出电压相互不同。

33.第2ad变换器22通过逐次重复模拟信号的振幅电压与由电容da转换器生成的电压的比较动作,从而生成多比特的数字数据(第2数字数据)。具体地,ad变换部2具有比较器以及逐次比较控制电路。比较器将输入到输入部3的输入电压(模拟信号的振幅)与比较参照电压进行比较。然后,逐次比较控制电路基于比较器的比较结果生成下一比特的逐次比较控制信号并输出到电容da转换器。电容da转换器的各电容器根据逐次比较控制信号,将另一端选择性地与第1电压源和第2电压源中的任意一方电连接。第2ad变换器22通过重复进行该逐次比较动作,生成多比特的数字数据。在本实施方式中,作为一个例子,第2ad变换器22生成9比特的第2数字数据。

34.第1ad变换器21是δ∑型ad变换器。第1ad变换器21具有减法运算器、积分器、量化器以及da转换器,并进行δ∑调制。减法运算器是差动放大器,被输入进行了第2ad变换器22中的逐次比较动作后的电容da转换器的残差电压(相当于量化噪声)和基准信号。减法运算器从残差电压减去基准信号。积分器对减法运算器中的运算结果进行累积相加。量化器将积分器的运算结果与基准信号进行比较来决定1比特的数字值。该量化器的结果输出到后级的数字滤波器23以及da转换器。da转换器是1比特da转换器,基于量化器的结果决定反馈输出到减法运算器的基准信号。

35.另外,第1ad变换器21也可以是具备多个减法运算器以及积分器的高阶的δ∑型ad变换器。越是高阶,越能够使量化噪声向高频侧移动,能够提高变换精度。

36.数字滤波器23对第1ad变换器21的输出进行滤波处理。作为滤波处理,数字滤波器23具有频带限制功能和抽取(间隔提取)功能。作为δ∑ad变换器的第1ad变换器21的输出包含基于量化噪声的噪声整形的高频噪声,因过采样而数据速率比本来的采样频率高。因此,数字滤波器23通过频带限制功能减少高频噪声,通过抽取功能减少数据速率。数字滤波器23通过对第1ad变换器21的1比特的输出进行滤波处理,生成多比特的数字数据。在本实施方式中,作为一个例子,数字滤波器23通过对第1ad变换器21的输出进行滤波处理,生成将通过第2ad变换器22生成的9比特的第2数字数据作为上位比特的21比特的数字数据(第1数字数据)。

37.第1输出部41具有用于输出通过数字滤波器23生成的21比特的第1数字数据的输

出端口。第1输出部41将第1数字数据输出到控制电路200。控制电路200基于对从传感器101输出的模拟信号进行了数字变换的第1数字数据,对控制对象的外部装置进行控制。

38.第2输出部42具有用于输出通过第2ad变换器22生成的9比特的第2数字数据的输出端口。第2输出部42将第2数字数据输出到测试控制部301。

39.测试控制部301基于第2数字数据判定传感器系统100是否为异常状态。具体地,测试控制部301具备判定部302和信号输出部303。测试控制部301具有测试模式作为动作模式。在动作模式为测试模式的情况下,测试控制部301从信号输出部303向传感器101发送测试信号。传感器101若接收到测试信号,则输出与该测试信号对应的振幅的模拟信号。从传感器101输出的模拟信号在ad转换器1中被ad变换为第2数字数据,并输出到判定部302。判定部302通过将接收到的第2数字数据和与从信号输出部303输出的测试信号对应的基准值(基准范围)进行比较,判定传感器系统100是否为异常状态。如果传感器101以及ad转换器1为正常状态,则对测试控制部301输出与测试信号对应的第2数字数据。此外,在传感器101和ad转换器1中的至少一方为异常状态的情况下,第2数字数据成为偏离基准值(基准范围)的值。在该情况下,判定部302判定传感器系统100为异常状态。

40.在此,第1数字数据在第2ad变换器22完成了9比特的第2数字数据的生成之后,通过由第1ad变换器21进行的δ∑调制、以及由数字滤波器23进行的滤波处理而被生成。也就是说,在生成了第2数字数据之后,生成第1数字数据。因此,第2输出部42在第1输出部41输出第1数字数据之前,将第2数字数据输出到测试控制部301。也就是说,第2数字数据的等待时间(延迟时间)比第1数字数据的等待时间(延迟时间)小。

41.另外,也可以不是独立的测试模式,而是在通常动作中在传感器101上叠加测试信号,进行传感器系统100的测试。

42.(动作例)

43.参照图2对本实施方式的ad转换器1的动作例进行说明。

44.在此,对在时间点t0针对从接收到测试信号的传感器101向输入部3输出的模拟信号的振幅的ad变换处理进行说明。

45.ad变换部2的第2ad变换器22重复进行逐次比较动作。在时间点t1,第2ad变换器22完成9比特的第2数字数据的生成。第2输出部42将第2ad变换器22生成的9比特的第2数字数据输出到测试控制部301。另外,严格地说,在第2ad变换器22生成第2数字数据后到第2输出部42输出第2数字数据为止的期间,产生由第2输出部42的信号处理等引起的时间差,但是该时间差很小,因此在此忽视。

46.此外,在时间点t1,第1ad变换器21开始δ∑调制。此外,数字滤波器23开始第1ad变换器21的输出的滤波处理。

47.在时间点t2,数字滤波器23完成滤波处理。也就是说,完成将通过第2ad变换器22生成的9比特的第2数字数据作为上位比特的21比特的第1数字数据的生成。第1输出部41将生成的21比特的第1数字数据输出到控制电路200。另外,严格地说,在数字滤波器23生成第1数字数据后到第1输出部41输出第1数字数据为止的期间,产生由第1输出部41的信号处理等引起的时间差,但是该时间差很小,因此在此忽视。

48.这样,本实施方式的ad转换器1在将第1数字数据输出到控制电路200之前,将第2数字数据输出到测试控制部301。第2数字数据与第1数字数据相比,分辨率(比特数)低,但

是等待时间少。也就是说,在本实施方式的ad转换器1中,能够输出分辨率高的第1数字数据和等待时间少的第2数字数据,因此能够谋求输出数据的高分辨率化和低等待时间化的并存。

49.在本实施方式中,ad转换器1将分辨率高的第1数字数据输出到控制电路200,将等待时间少的第2数字数据输出到测试控制部301。因此,控制电路200能够基于分辨率高的第1数字数据,对控制对象的外部装置进行控制,因此能够谋求对外部装置的控制的高精度化。此外,在测试控制部301被输入等待时间少的第2数字数据,因此能够谋求缩短传感器系统100是否为异常状态的测试处理的时间。

50.此外,在本实施方式中,第1ad变换器21和第2ad变换器22串联连接,用于测试处理的第2数字数据相当于输出到控制电路200的第1数字数据的上位比特。因此,在由测试控制部301进行的测试处理中,能够判定第2ad变换器22是否为正常。

51.(变形例)

52.以下,对本实施方式的ad转换器1的变形例进行说明。

53.(第1变形例)

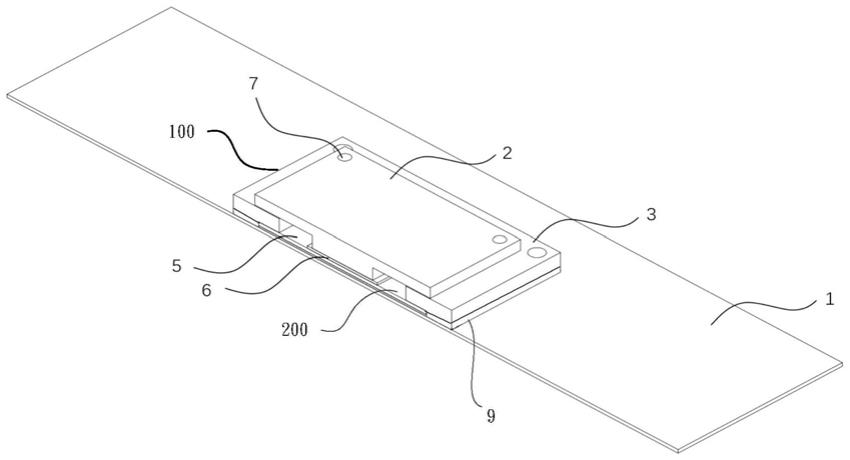

54.参照图3对第1变形例涉及的ad转换器1进行说明。

55.另外,对与上述的实施方式的ad转换器1相同的结构标注相同的附图标记并适当省略说明。

56.在上述的例子中,ad转换器1是ad变换部2具有多个ad变换器的ad转换器,但是并不限于此。

57.如图3所示,ad变换部2也可以是具备单个的ad变换器24的结构。本变形例的ad变换器24是噪声整形型逐次比较ad变换器。上述的第1ad变换器21(参照图1)是单比特δ∑ad变换器,是通过δ∑调制生成1比特的数字数据并输出到数字滤波器23的结构。另一方面,ad变换器24生成具有多比特(例如9比特)的噪声整形特性的数字数据。ad变换器24将所生成的9比特的数字数据作为第2数字数据输出到第2输出部42以及后级的数字滤波器23。

58.第2输出部42将通过ad变换器24生成的第2数字数据输出到测试控制部301。

59.数字滤波器23通过对由ad变换器24生成的9比特的数字数据(第2数字数据)进行滤波处理,生成21比特的数字数据(第1数字数据)。第1输出部41将通过数字滤波器23生成的第1数字数据输出到控制电路200。

60.也就是说,在本变形例中,第2输出部42将由数字滤波器23进行滤波处理前的第2数字数据输出到测试控制部301。因此,第2输出部42能够在第1输出部41输出第1数字数据之前,将第2数字数据输出到测试控制部301。也就是说,第2数字数据的等待时间(延迟时间)比第1数字数据的等待时间(延迟时间)小。

61.(第2变形例)

62.参照图3对第2变形例涉及的ad转换器1进行说明。

63.另外,对与上述的实施方式的ad转换器1相同的结构标注相同的附图标记并适当省略说明。

64.在上述的例子中,ad转换器1是ad变换部2具有多个ad变换器的ad转换器,但是并不限于此。

65.如图3所示,ad变换部2也可以是具备单个的ad变换器24的结构。本变形例的ad变

换器24是多比特δ∑型ad变换器。上述的第1ad变换器21(参照图1)是单比特δ∑ad变换器,是通过δ∑调制生成1比特的数字数据并输出到数字滤波器23的结构。另一方面,ad变换器24通过δ∑调制生成多比特(例如4比特)的数字数据。ad变换器24将生成的4比特的数字数据作为第2数字数据输出到第2输出部42以及后级的数字滤波器23。

66.第2输出部42将通过ad变换器24生成的第2数字数据输出到测试控制部301。

67.数字滤波器23通过对由ad变换器24生成的4比特的数字数据(第2数字数据)进行滤波处理,生成21比特的数字数据(第1数字数据)。第1输出部41将通过数字滤波器23生成的第1数字数据输出到控制电路200。

68.也就是说,在本变形例中,第2输出部42将由数字滤波器23进行滤波处理前的第2数字数据输出到测试控制部301。因此,第2输出部42能够在第1输出部41输出第1数字数据之前,将第2数字数据输出到测试控制部301。也就是说,第2数字数据的等待时间(延迟时间)比第1数字数据小。

69.(其他变形例)

70.在上述的例子中,第2ad变换器22(参照图1)是逐次比较型ad变换器,但是并不限于此,也可以是其他ad变换架构的ad变换器。例如,第2ad变换器22可以是闪速型ad变换器。

71.在闪速型ad变化器中,具备多个电阻器和多个比较器。多个电阻器串联连接在输出基准电压的基准电源与电路接地之间,生成将基准电压分压为多个的多个基准分压。多个基准分压与多个比较器一一对应。各比较器将对应的基准分压与输入到输入部3的模拟信号的振幅进行比较。闪速型ad变换器基于各比较器的输出生成第2数字数据。在闪速型ad变换器中,与逐次比较型ad变换器相比,能够谋求数字变换处理所需的时间的缩短。

72.另外,第2ad变换器22也可以是与逐次比较型ad变换器、快闪型ad变换器不同的ad变换架构的ad变换器。例如,第2ad变换器22可以是流水线(pipe line)型ad变换器、单斜率(single slope)型ad变换器、双积分型ad变换器、tdc型ad变换器(tdc:time to digital converter,时间数字转换器)、循环型ad变换器、增量型ad变换器等。此外,第2ad变换器22也可以是作为与第1ad变换器21相同的ad变换架构的δ∑型ad变换器。

73.此外,第1ad变换器21也可以是逐次比较型ad变换器、闪速型ad变换器、流水线型ad变换器、单斜率型ad变换器、双积分型ad变换器、tdc型ad变换器、循环型ad变换器、增量型ad变换器等。

74.此外,在上述的例子中,第1ad变换器21和第2ad变换器22串联连接,但是第1ad变换器21和第2ad变换器22也可以并联连接。

75.此外,ad变换部2具备的ad变换器并不限于两个,也可以是具备三个以上的ad变换器的结构。

76.此外,数字滤波器23能够根据ad变换部2具备的ad变换器的种类而适当省略。

77.(总结)

78.第1方式涉及的ad转换器(1)具备输入部(3)、ad变换部(2)、第1输出部(41)、以及第2输出部(42)。输入部(3)被输入从传感器(101)输出的模拟信号。ad变换部(2)对模拟信号进行数字变换并生成第1数字数据以及第2数字数据。第1输出部(41)将第1数字数据输出到控制电路(200)。第2输出部(42)在第1输出部(41)输出第1数字数据之前,将第2数字数据输出到测试控制部(301)。测试控制部(301)在测试模式下,基于第2数字数据判定包含传感

器(101)的传感器系统(100)是否为异常状态。

79.根据该方式,能够将等待时间少的第2数字数据输出到测试控制部(301),因此能够谋求测试控制部(301)中的测试处理的时间的缩短。

80.在第2方式涉及的ad转换器(1)中,在第1方式中,第2数字数据与第1数字数据相比比特数小。

81.根据该方式,能够使第2数字数据的等待时间更小。

82.在第3方式涉及的ad转换器(1)中,在第1或第2方式中,ad变换部(2)具有:串联连接的第1ad变换器(21)以及第2ad变换器(22);和数字滤波器(23)。第2ad变换器(22)设置在第1ad变换器(21)的前级,生成第2数字数据。第1ad变换器(21)是δ∑型ad变换器。数字滤波器(23)通过对第1ad变换器(21)的输出进行滤波处理,生成第1数字数据。

83.根据该方式,能够使第1数字数据的分辨率进一步提高。

84.在第4方式涉及的ad转换器(1)中,在第3方式中,第2ad变换器(22)是逐次比较型ad变换器。

85.根据该方式,能够使第2数字数据的等待时间更小。

86.在第5方式涉及的ad转换器(1)中,在第3方式中,第2ad变换器(22)是闪速型ad变换器。

87.根据该方式,能够使第2数字数据的等待时间更小。

88.在第6方式涉及的ad转换器(1)中,在第1或第2方式中,ad变换部(2)具有ad变换器(24)和数字滤波器(23)。ad变换器(24)生成作为多比特的数字数据的第2数字数据,输出到第2输出部(42)以及数字滤波器(23)。数字滤波器(23)通过对ad变换器(24)的输出进行滤波处理,生成第1数字数据。

89.根据该方式,能够使第1数字数据的分辨率进一步提高。

90.在第7方式涉及的ad转换器(1)中,在第6方式中,ad变换器(24)是噪声整形型逐次比较ad变换器、或多比特δ∑ad变换器。

91.根据该方式,能够使第2数字数据的等待时间更小。

92.第8方式涉及的传感器系统(100)具备:第1~第7方式中的任一方式的ad转换器(1);以及传感器(101)。

93.根据该方式,能够谋求测试控制部(301)中的测试处理的时间的缩短。

94.第9方式涉及的测试系统(300)具备:第8方式的传感器系统(100);以及测试控制部(301)。

95.根据该方式,能够谋求测试控制部(301)中的测试处理的时间的缩短。

96.产业上的可利用性

97.本公开的ad转换器、传感器系统以及测试系统能够谋求数字变换处理所需的时间的缩短并能够谋求测试处理的时间的缩短,在产业上是有用的。

98.附图标记说明

99.1:ad转换器;

100.2:ad变换部;

101.21:第1ad变换器(a∑型ad变换器);

102.22:第2ad变换器(逐次比较型ad变换器、闪速型ad变换器);

103.23:数字滤波器;

104.24:ad变换器(噪声整形型逐次比较ad变换器、多比特δ∑型ad变换器);

105.3:输入部;

106.41:第1输出部;

107.42:第2输出部;

108.100:传感器系统;

109.101:传感器;

110.200:控制电路;

111.300:测试系统;

112.301:测试控制部。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。