1.本发明涉及数字滤波领域,具体涉及一种并行总线抗干扰的数字滤波方法。

背景技术:

2.在嵌入式系统中,经常会在cpu和外设中存在并行总线的连接,如isa总线(industry standard architecture,工业标准体系结构),pci总线(peripheral component interconnect,外设部件互连标准)转local bus总线等。并行总线经常使用fpga(现场可编程门阵列)或cpld(复杂可编程逻辑器件)等进行时序功能的扩展,在总线传输数据的过程中,单端信号容易产生信号完整性的问题,表现在地址总线或者数据总线上出现干扰。而cmos(互补金属氧化物半导体)工艺的fpga/cpld芯片输入端vil(max)/vih(min)都较低,对干扰较为敏感,容易产生数据传输错误的现象。

3.若并行总线的地址信号采样错误,很可能会将数据存放到错误的地址;如果数据总线采样错误,很可能在该地址上存入错误的数据。同理,其他的信号可能会产生时序上的错误,导致总线故障发生。

技术实现要素:

4.为解决上述问题,本发明提供了一种并行总线抗干扰的数字滤波方法,具体包括以下内容:利用fpga或cpld的总线采样时钟采样干扰信号,并在测试引脚上输出该干扰信号;根据干扰信号宽度和采样时钟的周期确定信号滤波寄存器位数;编写滤波代码对所述干扰信号进行滤波处理;编写滤波代码对所述干扰信号进行滤波处理:信号滤波寄存器通过采样时钟存储上一周期的输入信号,在每个时钟采样周期内对信号滤波寄存器存储的的输入信号和当前周期的输入信号的组成值进行判断,如果组成值为相等的高电平或者低电平,则认为当前周期的输入信号是正确的无干扰的,信号滤波寄存器将当前的组成值移位输出到输出寄存器,当前周期的输入信号保存到信号滤波寄存器;如果存在不相等,则认为有干扰,则将当前周期的输入信号保存到信号滤波寄存器,但维持输出寄存器电平不变。

5.优选地,所述组成值指的是信号滤波寄存器存储的输入信号和当前周期的输入信号的合并信号。

6.其中,在利用fpga或cpld的总线采样时钟采样干扰信号前,先通过示波器波形测试,确定干扰信号宽度,参考采样时钟周期确定信号滤波寄存器的位数。

7.优选地,所述干扰信号包括:低电平上的凸形干扰信号以及高电平上的凹形干扰信号。

8.优选地,对于凸形干扰信号保证测试引脚采样得到m个采样时钟宽度的高电平;对于凹形干扰信号保证测试引脚采到n个采样时钟宽度的低电平;其中信号滤波寄存器位数等于m和n中的较大值,m、n均为正整数。

9.优选地,信号滤波寄存器根据滤波位数,若输入信号为高电平,若无干扰信号,若输入信号与信号滤波寄存器的组成值为全1,与上个周期的输入信号相等,则信号滤波寄存

器将当前的组成值移位输出到输出寄存器,当前周期的输入信号保存到信号滤波寄存器;若有干扰信号,即在高电平信号中出现凹形干扰,则输入信号与信号滤波寄存器的组成值不是全1,则将当前周期的输入信号保存到信号滤波寄存器,但维持输出寄存器电平不变。

10.优选地,信号滤波寄存器根据滤波位数,若输入信号为低电平,且无干扰信号,若输入信号与信号滤波寄存器的组成值为全0,则信号滤波寄存器将当前的组成值移位输出到输出寄存器,当前周期的输入信号保存到信号滤波寄存器;若有干扰信号,即在低电平信号中出现凸形干扰,则输入信号与信号滤波寄存器的组成值不是全0,则将当前周期的输入信号保存到信号滤波寄存器,但维持输出寄存器电平不变。

11.本发明具有以下有益效果:

12.1、本发明提供的滤波方法能够很好地滤除一些信号毛刺干扰,在总线时序裕度允许的范围内,提高总线的准确性和可靠性,同时并不会降低总线的速率;

13.2、相比于在硬件上进行布局的改进,这种方法简单灵活,只需要在fpga/cpld的代码上进行优化就可以很好地解决问题;

14.3、针对不同的干扰强度,可以灵活调整信号滤波寄存器的宽度,提高时序的可靠性;

15.4、并行总线易受干扰,本方案在并行总线接口中应用,但方法不权限于并行总线,可以灵活选择对特定信号做滤波。

附图说明

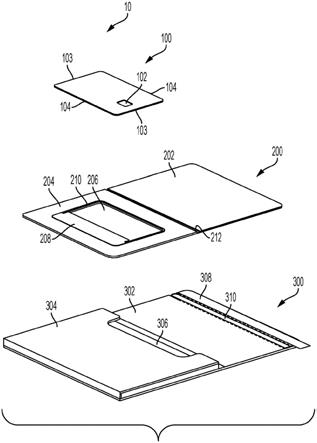

16.图1为本发明滤波方法流程图;

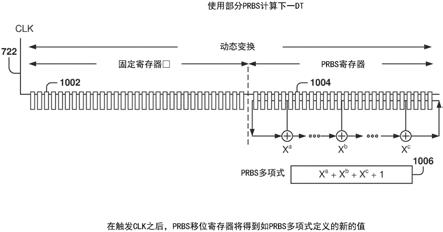

17.图2为发明实施例的cpld滤波电气原理图。

具体实施方式

18.以下结合附图和具体实施方式对本发明提出的一种并行总线抗干扰的数字滤波方法作进一步详细说明。根据下面说明,本发明的优点和特征将更清楚。

19.如图1所示,为本发明的数字滤波方法流程图,具体包含以下步骤:

20.1、通过示波器波形测试,通过设置示波器触发条件,用示波器捕捉干扰信号,并制定合适的示波器模型。发现某个高电平信号的地址线上出现低电平时,该低电平信号具有10ns左右的宽度,幅值最高达2.3v的凸形干扰信号,通过cpld(max v系列,vil(max)=0.8v,vih(min)=1.7v)50mhz的总线采样时钟去采样,有很大概率采到该干扰信号。一般工程上采样时钟的频率是被采样信号频率的10倍以上,本实施例中用的是50mhz的采样时钟(周期20ns),被采样的输入信号最窄处是250ns宽度。采样时钟采样信号后在测试引脚上输出,确保该引脚能采样到的最宽值是m=1个采样时钟(20ns)宽度的高电平。

21.2、通过示波器波形测试,发现某个低电平信号的地址线上出现高电平时,该低电平信号有具5ns左右的宽度,幅值最低达0.7v,针对该输入信号中的凹形干扰信号,通过cpld(如max v系列,vil(max)=0.8v,vih(min)=1.7v)50mhz的总线采样时钟去采样,有很大概率采样到该凹形干扰信号,然后在测试引脚上输出,确保该引脚能采样到的最宽值是n=1个时钟(20ns)宽度的低电平。

22.3、m和n的值需根据不同的总线采样时钟确定,信号滤波寄存器位数fbit=max(m,

n)=1。

23.4、如图2所示在cpld中增加滤波代码功能,对并行接口的所述输入信号进行采样,cpld中的信号滤波寄存器通过采样时钟存储上一周期的输入信号,在每个采样时钟周期内,通过信号滤波寄存器对其存储的上一周期的输入信号和当前的输入信号进行判断,即进行输入信号值比较判断,如果上一个周期的输入信号与当前周期的输入信号相等,则认为当前输入信号是正确的无干扰的,信号滤波寄存器将上一个周期的输入信号与当前周期的输入信号的组成值移位输出到输出寄存器,当前周期的输入信号保存到信号滤波寄存器;如果不相等,则认为有干扰,将当前周期的输入信号保存到信号滤波寄存器,但维持输出寄存器电平不变。当前周期的输入信号由于存在干扰,但输出寄存器的电平不变,相当于干扰被滤掉了。

24.因为每次信号输出寄存器都保存正确的输入信号,所以输出寄存器中存储的信号滤波寄存器的输出的信号,一定是正确无干扰的信号。信号滤波寄存器的滤波位数是1bit,若无干扰信号,每次采样到的输入信号i_ab与信号滤波寄存器sa1的值,为全1或全0,(其中1代表高电平,0代表低电平);若有干扰信号,即在高电平信号中出现凹形干扰或者在低电平信号中出现凸形干扰,则输入信号i_ab与信号滤波寄存器sa1的值不是全1或全0。

25.本发明提供的滤波方法能够很好地滤除一些信号毛刺干扰,在总线时序裕度允许的范围内,提高总线的准确性和可靠性,同时并不会降低总线的速率;相比于在硬件上进行布局的改进,这种方法简单灵活,只需要在fpga/cpld的代码上进行优化就可以很好地解决问题;针对不同的干扰强度,可以灵活调整滤波器的宽度,提高时序的可靠性;并行总线易受干扰,本方案在并行总线接口中应用,但方法不限于并行总线,可以灵活选择对特定信号做滤波。

26.综上所述,该滤波方法用于联锁产品板卡中,针对一些有干扰的信号进行滤波,证明完全能满足现场需求:有效避免某些干扰给系统带来的不良影响,保证了数据的正常传输,确保了系统的稳定运行。

27.尽管本发明的内容已经通过上述优选实施例作了详细介绍,但应当认识到上述的描述不应被认为是对本发明的限制。在本领域技术人员阅读了上述内容后,对于本发明的多种修改和替代都将是显而易见的。因此,本发明的保护范围应由所附的权利要求来限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。