1.本发明涉及开关电源设计领域,更为具体的,涉及一种动态跟踪准谐振谷底导通电路、方法及原边反馈开关电源。

背景技术:

2.随着新能效标准的普遍使用,市场领域对开关电源的效率要求越来越高。采用准谐振谷底导通的应用场景越来越普及,使用准谐振谷底导通可以有效提高开关电源的效率,降低开关电源温升,提供开关电源功率密度。

3.众所周知,开关电源的损耗主要来自于功率开关管mosfet的导通和关断过程中。开关电源在功率开关管mosfet的导通和关断过程中,存在重叠区间,因而会产生损耗。对应反激开关电源,功率开关管mosfet是在初级绕组电流最大时关断的,这就是mosfet的关断损耗。当功率开关管mosfet关断以后,存储在互感上的能量对次级转移,次级二极管导通,次级绕组电流通过二极管给输出的负载和输出的电容充电。当互感上的能量传递结束后,次级二极管截止,仍然有一部分能量会在耦合电感和功率开关管mosfet的寄生电容之间以交流桥式整流之后的直流电压为基准,产生衰减的阻尼振荡,一直到等到功率开关管mosfet下次开启。通常的,当mosfet再次开启时,mosfet的漏极电压drain可能在较低的水平,也可能漏极电压drain在高的水平,此时产生的就是功率开关管mosfet的导通损耗。

4.随着功率的升高,这种损耗的增加,一方面限制最高工作效率;另一方面,由于在转换过程中电压和电流短时间急剧变化,也会产生很大的开关噪声,形成大的电磁干扰。为了解决上面的缺点,现有技术逐渐采用准谐振模式。通过谐振技术,让功率开关管mosfet的漏极电压drain在最小电压,也就是谷底电压时导通,这样同时又能保持方波开关电源的高能量传输模式,又可以减少开关损耗,提高开关电源的效率。

5.然而,当互感上的能量传递结束后,mosfet的漏极电压以交流桥式整流之后的直流电压为基准,产生衰减的阻尼振荡,drain端的波谷电压并不是固定的,是在逐渐衰减的。因为drain都是高电压,常规的谐振技术都不会直接检测drain端电压,而是会检测反馈端fb电压。而同样的,fb电压以零电压为基准也在阻尼振荡,fb的负电压程度特别厉害时,负电压必然会被工艺上pn结电压钳位,因此前几个谷底,fb此时是被钳位在负0.6v,随着阻尼振荡幅值减小,fb端谷底电压才会逐渐增加。在常规的谐振技术谷底中,都是将fb端电压和一个固定的偏置电压,比如100mv比较,也不是检测fb端的谷底电压,对应的drain端也不是谷底电压。现有方案并没有完全达到准谐振谷底导通的目的。

技术实现要素:

6.本发明的目的在于克服现有技术的不足,提供一种动态跟踪准谐振谷底导通电路、方法及原边反馈开关电源,能够降低功率开关管mosfet的开关损耗,提高系统效率。

7.本发明的目的是通过以下方案实现的:

8.一种动态跟踪准谐振谷底导通电路,包括精准退磁信号检测电路、准谐振时间产

生电路、首次波谷信号产生电路和准谐振逻辑电路;精准退磁信号检测电路与准谐振时间产生电路、首次波谷信号产生电路连接,准谐振时间产生电路、首次波谷信号产生电路连接均与准谐振时间产生电路连接。

9.进一步地,所述精准退磁信号检测电路的输入端接入反馈端fb和内部偏置电压vb,且设有高通滤波电路,用于检测fb电压下降,并产生精准退磁信号。

10.进一步地,所述准谐振时间产生电路的输入端接入精准退磁信号和内部固定时间test。

11.进一步地,所述首次波谷信号产生电路的输入端接入反馈端fb和精准退磁信号检测电路输出的精准退磁信号,且设有电流比较电路,用于检测fb端电压第一个波谷上升状态,并产生首次谷底信号tfa,tfa为高脉冲信号。

12.进一步地,所述准谐振逻辑电路的输入端接入准谐振时间产生电路的输出信号qb或者qset信号,和首次谷底信号产生电路的输出信号tfa。

13.进一步地,包括误差放大器、调频时间产生电路、pwm开启逻辑电路、关断时间产生电路和pwm逻辑电路;误差放大器与调频时间产生电路连接,调频时间产生电路与pwm开启逻辑电路,pwm开启逻辑电路与pwm逻辑电路连接,pwm逻辑电路与关断时间产生电路连接;pwm开启逻辑电路与准谐振时间产生电路连接。在该实施方式中,误差放大器,将反馈端电压fb和内部基准电压vref比较,得到误差放大器输出电压ea。调频时间产生电路,根据不同的误差放大器输出电压,得到调频时间信号pfm。其特征在于pfm为逻辑高电平有效。pwm开启逻辑电路,将准谐振逻辑电路输出的qr信号接入pwm开启逻辑电路的输入端,将调频时间产生电路输出信号pfm接入pwm开启逻辑电路的输入端,通过逻辑运算,得到pwmon逻辑信号。当检测到pfm信号和qr信号同时为高电平,触发pwmon信号为逻辑高电平。关断时间产生电路,将电流检测电阻cs端接入关断时间产生电路,输出pwmoff逻辑信号,有效的pfmoff为高电平逻辑信号。pwm逻辑电路,pwmon信号pwmoff信号接入pwm逻辑电路输入端,pwm逻辑电路输出pwm信号,pwm信号控制功率开关管mosfet导通和关断,当pwmon信号为逻辑高电平时,触发pwm信号为逻辑高电平,pfmoff为高电平逻辑信号,触发pwm信号为逻辑低电平。当pwm信号为逻辑高电平,控制功率开关管mosfet导通;当pwm信号为逻辑低电平,控制功率开关管mosfet关闭。

14.一种基于所述动态跟踪准谐振谷底导通电路的方法,包括步骤:在所述精准退磁信号检测电路中,在fb的完整阻尼衰减周期内都会检测fb波峰电压下降斜率,并依次产生多个精准退磁信号,且产生的多个精准退磁信号均为逻辑高电平信号。

15.进一步地,在所述准谐振时间产生电路中,对相邻两个的精准退磁信号进行逻辑运算,得到相邻两个精准退磁信号的时间差值tea,阻尼振荡周期就是tea;然后将tb时间信号加上时间差值tea的一半,计算得到谷底信号qb,qb为高脉冲信号;当不能检测到tn信号时,此时tn

‑

1叠加固定的偏置时间tset,此时谐振时间产生电路输出为qset信号,并输出为qset时间,qset为高脉冲信号,固定的偏置时间tset大于阻尼振荡周期tea。

16.进一步地,在所述准谐振逻辑电路中根据系统状态判断得到准谐振逻辑信号qr,包括步骤:

17.若是第一种系统状态,即重载系统状态下,系统所需要的pwm周期短,频率高,调频时间产生电路产生的有效pfm逻辑高电平先触发,tfa高脉冲信号后触发,那么此时不会等

待第二个波峰信号tb,此时准谐振逻辑电路输出qr信号即为tfa信号,马上触发pwm信号逻辑高电平;

18.若是第二种系统状态,即带载系统状态下,当调频时间产生电路产生的pfm逻辑高电平在tfa高脉冲信号之后才会触发,在tfa需要第n个波谷发波,n>1,此时准谐振逻辑电路输出qr信号即为qn信号,需要等pfm逻辑高电平和qn同时为高时,触发pwm信号高电平;

19.若是第三种系统状态,即轻载系统状态下,系统的pwm频率非常小,pwm周期非常长时,此时调频时间产生电路产生有效的pfm逻辑高电平时,fb端阻尼振荡幅值太小,tn之后已经不能再检测tn 1的退磁信号,那么tn信号将叠加固定偏置时间tset,此时准谐振逻辑电路输出qr信号即为tn叠加固定偏置时间tset的时刻qset。

20.一种原边反馈开关电源,包括所述的动态跟踪准谐振谷底导通电路。

21.本发明的有益效果是:

22.本发明在精准退磁信号检测电路的基础上,通过计算退磁时间之后阻尼振荡的周期,综合各种负载状态,通过准谐振逻辑电路,检测出比较准确的波谷电压信号,使功率开关管每次导通时刻均在真正波谷,降低功率开关管mosfet的开关损耗,提高系统效率。

附图说明

23.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

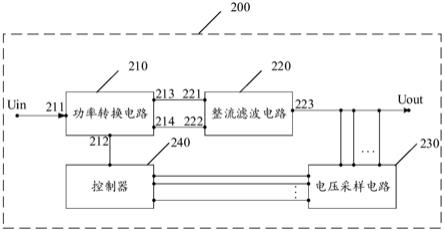

24.图1为典型的反激原边反馈ac/dc电路拓扑结构图;;

25.图2为传统准谐振谷底导通电路结构图;

26.图3为本发明实施例的动态跟踪准谐振谷底导通电路结构图;;

27.图4为本发明实施例的动态跟踪准谐振谷底导通信号示意图。

具体实施方式

28.本说明书中所有实施例公开的所有特征,或隐含公开的所有方法或过程中的步骤,除了互相排斥的特征和/或步骤以外,均可以以任何方式组合和/或扩展、替换。

29.传统的原边反馈ac/dc开关电源拓扑结构如附图2所示。反馈端fb和固定电压va进行比较,当fb电压小于va时,产生一个高脉冲qra信号。当退磁结束以后,一方面,在功率开关管mosfet的漏端电压drain,开始以桥式整流之后的直流电压为中心值,以输出电压加上输出二极管的导通电压之后,与匝比的乘积所产生的反射电压为幅值,开始阻尼振荡。振荡周期和驱动开关管mosfet的寄生电容以及初级绕组的漏感有关。必然的功率开关管mosfet的漏端电压drain如图4所示,振荡频率不会,振荡幅值逐渐衰减。

30.另一方面,当退磁结束以后,fb电压以零为基准点,fb的高电平电压为幅值,开始阻尼振荡,振荡频率和漏端电压drain保持一致性。在阻尼振荡初期,fb的谷底电压被钳位在负0.6v附近,随着阻尼振荡时间的增加,振荡幅值逐渐降低,fb在波谷端的负电压逐渐上升,同时fb在波峰端的正电压也逐渐降低,当pwm的关断时间过长,fb阻尼振荡幅值趋于零。

31.传统的谐振谷底导通技术,一般均检测反馈端fb谷底的电压,来间接达到检测

drain谷底电压的目的。为了兼顾fb谷底检测的准确性和尽量保证drain端电压接近波谷。va电压一般设置在零电压以上,100mv电压以下。那么此时对应的检测到的drain电压接近阻尼振荡的中心值,即交流电压桥式整流之后的直流电压。让交流电压在ac264v时,桥式整流电压能达到380v。此时,离真正的谷底导通还存在一定距离。

32.为达到上述目的,如图3~图4所示,本发明的实施例提供一种动态跟踪准谐振谷底导通电路,包括精准退磁信号检测电路、准谐振时间产生电路、首次波谷信号产生电路和准谐振逻辑电路;精准退磁信号检测电路与准谐振时间产生电路、首次波谷信号产生电路连接,准谐振时间产生电路、首次波谷信号产生电路连接均与准谐振时间产生电路连接。

33.本实施例的动态跟踪准谐振谷底导通电路,不会直接把反馈端fb电压和固定电压相比较。而是根据在阻尼振荡阶段频率保持不变这个原理,通过计算出相邻波峰之间的时间也就是阻尼振荡周期,然后在波峰时刻叠加一半的周期,那么结果必然就是在波谷时刻。

34.将反馈端fb和固定偏置电压vb引入到精准退磁信号检测电路,固定偏置电压vb并不是和fb进行comp比较,而是通过内部高通滤波器,判断fb电压下降斜率,当fb电压在波峰时刻快速下降一定幅度,触发ta为高脉冲信号,fb的每个波峰时刻都会检测。将ta,tb等高脉冲信号输入到准谐振时间产生电路中,通过逻辑运算或者模拟电路计算,均可以得到tb和ta的差值,该差值即是阻尼振荡的周期。继续在准谐振时间产生电路中,将tb高脉冲信号叠加周期的一半,就能得到qb信号。qb为计算得出的波谷高脉冲信号。

35.精准退磁信号检测电路的输出信号ta引入首次波谷信号产生电路。反馈端fb电压在第一个阻尼振荡周期,波谷电压必然是被pn结电压钳位到负0.6v,当fb检测到ta之后,fb电压快速下降,通过首次波谷信号产生电路,当fb电压上升到大于负0.6v左右,即可产生高脉冲信号tfa。

36.将高脉冲信号qb和高脉冲信号tfa引入准谐振逻辑电路,进行状态判断。第一种系统状态,当重度负载情况下,系统所需要的pwm周期短,频率高,调频时间产生电路产生的有效pfm逻辑高电平先触发,tfa高脉冲信号后触发,那么此时不会等待第二个波峰信号tb,此时准谐振逻辑电路输出qr信号即为tfa信号,马上触发pwm信号逻辑高电平。第二种系统状态,当调频时间产生电路产生的pfm逻辑高电平在tfa高脉冲信号之后才会触发,在tfa需要第n(n>1)个波谷发波(即最小电压时发波),此时准谐振逻辑电路输出qr信号即为qn信号,需要等pfm逻辑高电平和qn同时为高时,触发pwm信号高电平。第三种系统状态,当负载状态非常轻,系统的pwm频率非常小,pwm周期非常长时,此时调频时间产生电路产生有效的pfm逻辑高电平时,fb端阻尼振荡幅值太小,tn之后已经不能再检测tn 1的退磁信号,那么tn信号将叠加固定偏置时间tset,此时准谐振逻辑电路输出qr信号即为tn叠加固定偏置时间tset的时刻qset。因为第三种系统状态处于负载状态非常轻载,整个pwm周期很长,pwm发波频率很小,功率开关管mosfet开关损耗在此时对功率损耗较小,此时系统不会在波谷开启,此时也不会触发准谐振状态开启。

37.除以上实例以外,本领域技术人员根据上述公开内容获得启示或利用相关领域的知识或技术进行改动获得其他实施例,各个实施例的特征可以互换或替换,本领域人员所进行的改动和变化不脱离本发明的精神和范围,则都应在本发明所附权利要求的保护范围内。

38.本发明功能如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可

以存储在一个计算机可读存储介质中。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,在一台计算机设备(可以是个人计算机,服务器,或者网络设备等)以及相应的软件中执行本发明各个实施例所述方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、或者光盘等各种可以存储程序代码的介质,进行测试或者实际的数据在程序实现中存在于只读存储器(random access memory,ram)、随机存取存储器(random access memory,ram)等。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。