1.本发明涉及图像显示技术领域,尤其涉及一种微显示面板中输入信号极性自适应电路。

背景技术:

2.基于micro-led或micro-oled的微显示技术是指以自发光的微米量级的led或oled为发光像素单元,将其组装到驱动面板上形成高密度led阵列的显示技术。由于微显示芯片尺寸小、集成度高和自发光等特点,在显示的亮度、分辨率、对比度、能耗、使用寿命、响应速度和热稳定性等方面具有更大的优势。基于上述优势,基于微显示芯片的显示装置可以制造成微型且可便携的产品,这使得基于微显示芯片的显示装置可以应用于ar或vr显示装置中。

3.目前输入微显示面板的视频数据与用于液晶面板显示的显示数据具有相同的格式,显示数据中都包含场同步信号vs、行同步信号hs或有效显示数据选通信号de。行同步信号hs的作用是选择出显示面板上有效行信号区间;场同步信号vs的作用是选择出显示面板上有效场信号区间;有效显示数据选通信号de是为了区分有效和无效视频信号。但是现有技术中,所述同步信号vs、行同步信号hs或有效显示数据选通信号de均存在正负两种脉冲形式(高电平脉冲信号或低电平脉冲信号),另一方面微显示面板一般只识别一种形式的信号。因此在微显示面板使用时,要确定好显示数据输入侧给的信号极性,来决定微显示面板内部是否要对其进行反向。或规定系统要给确定极性的格式。这就导致微显示面板的自适应性变差,或者在同时接收到不同极性的信号源时,导致无法正常显示。

4.由此可见,现有技术中需要一种使微显示面板针对输入的信号极性能够自适应的技术手段,提高微显示面板自身对不同格式的显示数据的自适应性。

技术实现要素:

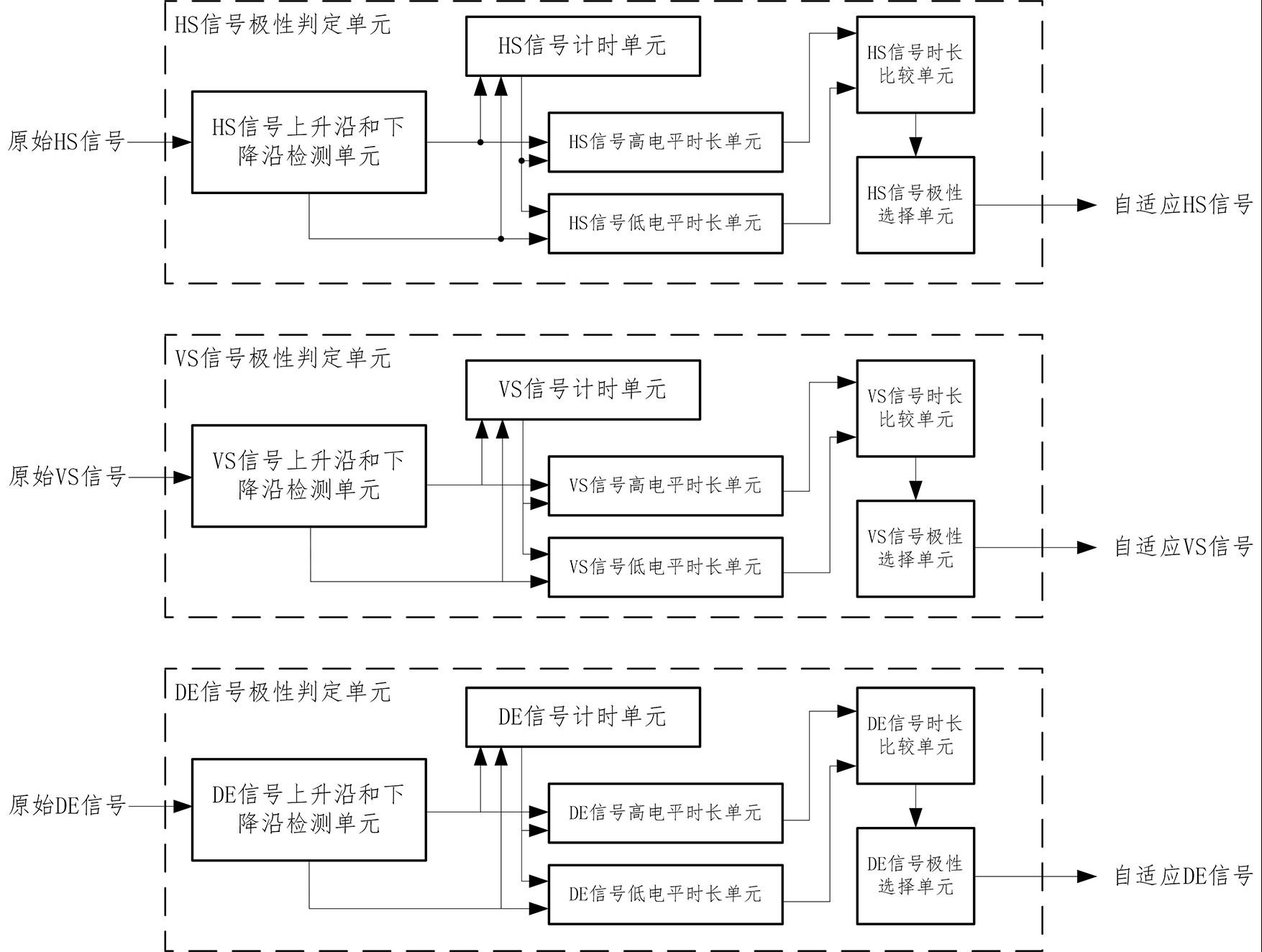

5.本发明所要实现的技术目的在于提供一种微显示面板中输入信号极性自适应电路,其包括:hs信号极性判定单元、vs信号极性判定单元和de信号极性判定单元至少之一;所述hs信号极性判定单元中包括hs信号上升沿及下降沿检测单元、hs信号计时单元、hs信号高电平时长单元、hs信号低电平时长单元、hs信号时长比较单元和hs信号极性选择单元;其中所述hs信号上升沿及下降沿检测单元用于检测原始hs信号的上升沿及下降沿,所述hs信号上升沿及下降沿检测单元具有两路输出,当原始hs信号出现上升沿时一路输出高电平,当原始hs信号出现下降沿时另一路输出高电平;所述hs信号计时单元用于对hs信号中的高电平持续时长及低电平持续时长进行计时,并将计时结果分别输入至hs信号高电平时长单元和hs信号低电平时长单元,由hs信号高电平时长单元和hs信号低电平时长单元将高电平计时结果和低电平计时结果输入至所述hs信号时长比较单元以比较高电平计时结果和低电平计时结果的时长大小;所述hs信号极性选择单元根据时长比较单元的比较结果将原始hs信号的极性调整为符合微显示面板内部显示协议规定的信号极性;

所述vs信号极性判定单元中包括vs信号上升沿及下降沿检测单元、vs信号计时单元、vs信号高电平时长单元、vs信号低电平时长单元、vs信号时长比较单元和vs信号极性选择单元;其中所述vs信号上升沿及下降沿检测单元用于检测原始vs信号的上升沿及下降沿,所述vs信号上升沿及下降沿检测单元具有两路输出,当原始vs信号出现上升沿时一路输出高电平,当原始vs信号出现下降沿时另一路输出高电平;所述vs信号计时单元用于对vs信号中的高电平持续时长及低电平持续时长进行计时,并将计时结果分别输入至vs信号高电平时长单元和vs信号低电平时长单元,由vs信号高电平时长单元和vs信号低电平时长单元将高电平计时结果和低电平计时结果输入至所述vs信号时长比较单元以比较高电平计时结果和低电平计时结果的时长大小;所述vs信号极性选择单元根据时长比较单元的比较结果将原始vs信号的极性调整为符合微显示面板内部显示协议规定的信号极性;所述de信号极性判定单元中包括de信号上升沿及下降沿检测单元、de信号计时单元、de信号高电平时长单元、de信号低电平时长单元、de信号时长比较单元和de信号极性选择单元;其中所述de信号上升沿及下降沿检测单元用于检测原始de信号的上升沿及下降沿,所述de信号上升沿及下降沿检测单元具有两路输出,当原始de信号出现上升沿时一路输出高电平,当原始de信号出现下降沿时另一路输出高电平;所述de信号计时单元用于对de信号中的高电平持续时长及低电平持续时长进行计时,并将计时结果分别输入至de信号高电平时长单元和de信号低电平时长单元,由高电平时长单元和低电平时长单元将高电平计时结果和低电平计时结果输入至所述de信号时长比较单元以比较高电平计时结果和低电平计时结果的时长大小;所述de信号极性选择单元根据时长比较单元的比较结果将原始de信号的极性调整为符合微显示面板内部显示协议规定的信号极性。

6.在一个实施例中,所述hs信号上升沿和下降沿分离单元、vs信号上升沿及下降沿检测单元和de信号上升沿及下降沿检测单元均包括第一d触发器、第一非门、第一与门、第二非门和第二与门;其中所述第一d触发器的信号输入端d连接所述hs信号;所述第一d触发器的第一输出端q连接于第一非门的输入端,所述第一非门的输出端连接于第一与门的第一输入端,所述第一与门的第二输入端连接所述第一d触发器的信号输入端d;所述第一与门13的输入端输出被检测信号的上升沿信息;所述第二非门的输入端与所述第一d触发器的信号输入端d相连,所述第二非门的输出端与第二与门的第一输入端相连,所述第二与门的第二输入端与所述第一d触发器的第一输出端q相连,所述第一与门的输入端输出被检测信号的下降沿信息。

7.在一个实施例中,所述hs信号计时单元包括第一或门、第一数据选择器、第一多位宽触发器和第一1位加法器;所述上升沿触发信号与下降沿触发信号被输入第一或门;所述第一或门的输出端连接第一数据选择器的通道选择端;所述第一数据选择器的输出端连接于第一多位宽触发器的d输入端,所述第一多位宽触发器的q输出端连接第一1位加法器的输入端,所述第一1位加法器的输出端连接第一数据选择器的0通道输入端;所述第一多位宽触发器的q输出端同时作为hs信号计时单元的计时输出端。

8.在一个实施例中,所述低电平时长单元包括第二数据选择器、第二多位宽触发器;所述第二数据选择器的1通道输入端连接hs信号计时单元、vs信号计时单元或de信号计时单元的计时输出,所述第二数据选择器的通道选择端连接上升沿触发信号;所述第二数据选择器的输出端连接第二多位宽触发器的d输入端,所述第二多位宽触发器的q输出端连接

所述第二数据选择器的0通道输入端。

9.在一个实施例中,高电平时长单元包括第三数据选择器、第三多位宽触发器;所述第三数据选择器的1通道输入端连接hs信号计时单元、vs信号计时单元或de信号计时单元的计时输出,所述第三数据选择器的通道选择端连接上升沿触发信号;所述第三数据选择器的输出端连接第三多位宽触发器的d输入端,所述第三多位宽触发器的q输出端连接所述第三数据选择器41的0通道输入端。

10.在一个实施例中,所述时长比较单元比较低电平时长单元输出的低电平时长数值与高电平时长单元输出的高电平时长数值,当低电平时长数值大于高电平时长数值时则说明原hs信号为高电平脉冲极性,反之则是原hs信号为低电平脉冲极性。

11.在一个实施例中,所述vs信号计时单元包括第二或门、第五数据选择器、第四多位宽触发器、第二1位加法器和第六数据选择器;vs上升沿触发信号与vs下降沿触发信号被输入至vs信号计时单元。

12.在一个实施例中,所述第六数据选择器的通道选择端连接hs信号上升沿触发信号。

13.与现有技术相比,本发明的一个或多个实施例可以具有如下优点:本发明中通过设置极性自适应电路对输入的hs/vs/de信号的极性进行转换,使其能够自动适应微显示面板芯片中视频信号传输协议所规定的信号极性。

14.本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过在说明书、权利要求书以及附图中所特别指出的结构来实现和获得。

附图说明

15.附图用来提供对本发明的进一步理解,并且构成说明书的一部分,与本发明的实施例共同用于解释本发明,并不构成对本发明的限制。在附图中:图1是本发明的一实施例的输入信号极性自适应电路结构示意图;图2是本发明的一实施例的hs信号上升沿及下降沿检测单元的电路结构示意图;图3是本发明的一实施例的hs信号上升沿及下降沿检测单元的时序示意图;图4是本发明的一实施例的hs信号计时单元的结构示意图;图5是本发明的一实施例的低电平时长单元的结构示意图;图6是本发明的一实施例的高电平时长单元的结构示意图;图7是本发明的一实施例的时长比较单元的结构示意图;图8是本发明的一实施例的极性选择单元的结构示意图;图9是本发明的一实施例的vs信号计时单元的结构示意图。

具体实施方式

16.为使本发明的目的、技术方案和优点更加清楚,以下结合附图对本发明作进一步地详细说明。

17.应当明白,当元件或层被称为“在

……

上”、“与

……

相邻”、“连接到”或“耦合到”其 它元件或层时,其可以直接地在其它元件或层上、与之相邻、连接或耦合到其它元件或层,

或者可以存在居间的元件或层。相反,当元件被称为“直接在

……

上”、“与

……

直接相邻”、“直接连接到”或“直接耦合到”其它元件或层时,则不存在居间的元件或层。应当明白,尽管可使用术语第一、第二、第三等描述各种元件、部件、区、层和/或部分,这些元件、部件、区、层和/或部分不应当被这些术语限制。这些术语仅仅用来区分一个元件、部件、区、层或部分与另一个元件、部件、区、层或部分。因此,在不脱离本发明教导之下,下面讨论的第一元件、部件、区、层或部分可表示为第二元件、部件、区、层或部分。而当讨论的第二元件、部件、区、层或部分时,并不表明本发明必然存在第一元件、部件、区、层或部分。

18.空间关系术语例如“在

……

下”、“在

……

下面”、“下面的”、“在

……

之下”、“在

……

之上”、“上面的”等,在这里可为了方便描述而被使用从而描述图中所示的一个元件或特征与其它元件或特征的关系。应当明白,除了图中所示的取向以外,空间关系术语意图还包括使用和操作中的器件的不同取向。例如,如果附图中的器件翻转,然后,描述为“在其它元件下面”或“在其之下”或“在其下”元件或特征将取向为在其它元件或特征“上”。因此,示例性术语“在

……

下面”和“在

……

下”可包括上和下两个取向。器件可以另外地取向(旋转90度或其它取向)并且在此使用的空间描述语相应地被解释。

19.在此使用的术语的目的仅在于描述具体实施例并且不作为本发明的限制。在此使用时,单数形式的“一”、“一个”和“所述/该”也意图包括复数形式,除非上下文清楚指出另外的方式。还应明白术语“组成”和/或“包括”,当在该说明书中使用时,确定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或更多其它的特征、整数、步骤、操作、元件、部件和/或组的存在或添加。在此使用时,术语“和/或”包括相关所列项目的任何及所有组合。

实施例

20.如图1所示,本发明的微显示面板中输入信号极性自适应电路包括:hs信号极性判定单元、vs信号极性判定单元和de信号极性判定单元。

21.所述hs信号极性判定单元中包括hs信号上升沿及下降沿检测单元、hs信号计时单元、高电平时长单元、低电平时长单元、时长比较单元和极性选择单元;其中所述hs信号上升沿及下降沿检测单元用于检测原始hs信号的上升沿及下降沿,所述hs信号上升沿及下降沿检测单元具有两路输出,当原始hs信号出现上升沿时一路输出高电平,当原始hs信号出现下降沿时另一路输出高电平。

22.本实施例中的hs信号上升沿及下降沿检测单元的电路结构图如图2所示,本实施例的hs信号上升沿和下降沿分离单元1包括第一d触发器11、第一非门12、第一与门13、第二非门14和第二与门15。其中所述第一d触发器11的信号输入端d连接所述vs/hs/de信号。随后,所述第一d触发器11的第一输出端q连接于第一非门12的输入端,所述第一非门12的输出端连接于第一与门13的第一输入端,所述第一与门13的第二输入端连接所述第一d触发器11的信号输入端d。所述第一与门13的输入端输出被检测信号的上升沿信息。

23.同时,所述第二非门14的输入端与所述第一d触发器11的信号输入端d相连,所述第二非门14的输出端与第二与门15的第一输入端相连,所述第二与门15的第二输入端与所述第一d触发器11的第一输出端q相连。所述第一与门13的输入端输出被检测信号的下降沿信息。

24.如3所示的时序图所示,当所述行同步信号hs中出现上升沿跳变时,如a通道所示;所述第一与门13的第二输入端即与a通道信号保持一致;而在该上升沿之后的下一个时钟的上升沿到来时,所示第一d触发器11的第一输出端q发生变化,经过第一非门12后,其信号如图3中通道b所示。经过所述第一与门13的运算,所述第一与门13的输出即为通道c所示,即当所述行同步信号hs中出现上升沿跳变时所述第一与门13即输出高电平,且该高电平仅维持到所述第一d触发器11的第一输出端q因该上升沿的出现发生跳变为止,本实施例中称该c通道信号为上升沿触发信号。

25.同样地,当所述行同步信号hs中出现下降沿跳变时,在该下降沿之后的下一个时钟的上升沿到来时,所述第一d触发器11的第一输出端q发生变化,其信号如图3中通道a所示。当所述行同步信号hs经过第二非门14输入至第二与门15的第二输入端,其信号如图3中通道b所示。经过所述第二与门15的运算,所述第二与门15的输出即为通道c所示,即当所述行同步信号hs中出现下降沿跳变时所述第二与门13即输出高电平,且该高电平仅维持到所示第一d触发器11的第一输出端q因该下降沿的出现发生跳变为止,本实施例中称该c通道信号为下降沿触发信号。

26.所述上升沿触发信号与下降沿触发信号被输入至hs信号计时单元2,所述hs信号计时单元2包括第一或门21、第一数据选择器22、第一多位宽触发器23和第一1位加法器24。如图4所示,所述上升沿触发信号与下降沿触发信号被输入第一或门21,所述第一或门21的输出端连接第一数据选择器22的通道选择端,当上升沿触发信号与下降沿触发信号之一为高电平时,则选择1通道,所述1通道的输入为低电平。当上升沿触发信号与下降沿触发信号均为低电平时,则选择0通道。所述第一数据选择器22的输出端连接于第一多位宽触发器23的d输入端,所述第一多位宽触发器23的q输出端连接第一1位加法器24的输入端,所述第一1位加法器24的输出端连接第一数据选择器22的0通道输入端。所述第一多位宽触发器23的q输出端同时作为hs信号计时单元2的计时输出端。

27.本实施例的hs信号计时单元2中,当hs上升沿触发信号与hs下降沿触发信号之一为高电平时,1通道的低电平信号被输入第一多位宽触发器23的d输入端,此时第一1位加法器24被重置。同时在该上升沿触发信号与下降沿触发信号之一为高电平到来之前的原始hs信号的低电平持续时长或高电平持续时长被第一多位宽触发器23的q输出端作为计时输出给低电平时长单元或高电平时长单元。

28.如图5所示,本实施例的低电平时长单元3包括第二数据选择器31、第二多位宽触发器32。所述第二数据选择器31的1通道输入端连接hs信号计时单元2的计时输出,所述第二数据选择器31的通道选择端连接上升沿触发信号。所述第二数据选择器31的输出端连接第二多位宽触发器32的d输入端,所述第二多位宽触发器32的q输出端连接所述第二数据选择器31的0通道输入端。即当hs信号计时单元2中由于接入上升沿触发信号的高电平,而被计时重置时,所述上升沿触发信号的高电平之前计时的低电平持续时长被保持进入低电平时长单元3。

29.如图6所示,本实施例的高电平时长单元4包括第三数据选择器41、第三多位宽触发器42。所述第三数据选择器41的1通道输入端连接hs信号计时单元2的计时输出,所述第三数据选择器41的通道选择端连接上升沿触发信号。所述第三数据选择器41的输出端连接第三多位宽触发器42的d输入端,所述第三多位宽触发器42的q输出端连接所述第三数据选

择器41的0通道输入端。即当hs信号计时单元2中由于接入下降沿触发信号的高电平,而被计时重置时,所述下降沿触发信号的高电平之前计时的高电平持续时长被保持进入高电平时长单元3。

30.如图7所示,所述时长比较单元5比较低电平时长单元3输出的低电平时长数值与高电平时长单元3输出的高电平时长数值,当低电平时长数值大于高电平时长数值时则说明原hs信号为高电平极性(高电平脉冲信号),则时长比较单元5输出0,反之则是原hs信号为低电平极性(低电平脉冲信号),则时长比较单元5输出1。

31.如图8所示,所述极性选择单元6包括第四数据选择器61和第一非门62,以微显示芯片内部设定的hs信号为高电平极性为例,所述第四数据选择器61的0通道输入端接入原hs信号,所述第四数据选择器61的1通道输入端接入原hs信号经第一非门62取反的信号。所述第四数据选择器61的数据选择端连接所述时长比较单元5的输出信号。所述第四数据选择器61输出的信号即为适用于微显示芯片内部协议规定的信号极性的自适应hs信号。

32.本实施例中,所述vs信号极性判定单元中包括vs信号上升沿及下降沿检测单元、vs信号计时单元、高电平时长单元、低电平时长单元、时长比较单元和极性选择单元;其中所述vs信号上升沿及下降沿检测单元用于检测原始vs信号的上升沿及下降沿,所述vs信号上升沿及下降沿检测单元具有两路输出,当原始vs信号出现上升沿时一路输出高电平,当原始vs信号出现下降沿时另一路输出高电平。

33.本实施例中,所述vs信号上升沿及下降沿检测单元与hs信号上升沿及下降沿检测单元具有完全相同的电路结构。

34.如图9所示,本实施例的vs信号计时单元7中,所述vs上升沿触发信号与vs下降沿触发信号被输入至vs信号计时单元7,所述vs信号计时单元7包括第二或门71、第五数据选择器72、第四多位宽触发器73、第二1位加法器74和第六数据选择器75。

35.如图9所示,所述vs上升沿触发信号与vs下降沿触发信号被输入第二或门71,所述第二或门71的输出端连接第五数据选择器72的通道选择端,当vs上升沿触发信号与vs下降沿触发信号之一为高电平时,则选择1通道,所述1通道的输入为低电平。当vs上升沿触发信号与vs下降沿触发信号均为低电平时,则选择0通道。所述第五数据选择器72的输出端连接于第四多位宽触发器73的d输入端,所述第四多位宽触发器73的q输出端连接第二1位加法器74的输入端,所述第二1位加法器74的输出端连接第六数据选择器75的1通道输入端。同时所述第四多位宽触发器73的q输出端直接连接第六数据选择器75的0通道输入端。所述第六数据选择器75的输出端连接所述第五数据选择器72的0通道输入端。所述第六数据选择器75的通道选择端连接hs信号上升沿触发信号。

36.所述第四多位宽触发器73的q输出端同时作为vs信号计时单元7的计时输出端。

37.本实施例的vs信号计时单元7中,当vs上升沿触发信号与vs下降沿触发信号之一为高电平时,1通道的低电平信号被输入所述第四多位宽触发器73的d输入端,同时,当hs信号上升沿触发信号为高电平时,此时第二1位加法器74被重置。同时在该上升沿触发信号与下降沿触发信号之一为高电平到来之前的原始vs信号的低电平持续时长或高电平持续时长被所述第四多位宽触发器73的q输出端作为计时输出给低电平时长单元或高电平时长单元。

38.本实施例中,所述vs信号极性判定单元中的高电平时长单元、低电平时长单元、时

长比较单元和极性选择单元的电路结构与前述hs信号极性判定单元中的高电平时长单元、低电平时长单元、时长比较单元和极性选择单元的电路结构完全一直。在此不在重复描述。

39.本实施例中,所述de信号极性判定单元中包括de信号上升沿及下降沿检测单元、de信号计时单元、高电平时长单元、低电平时长单元、时长比较单元和极性选择单元;其中所述de信号上升沿及下降沿检测单元用于检测原始de信号的上升沿及下降沿,所述de信号上升沿及下降沿检测单元具有两路输出,当原始de信号出现上升沿时一路输出高电平,当原始de信号出现下降沿时另一路输出高电平。

40.本实施例中,所述de信号极性判定单元中包括de信号上升沿及下降沿检测单元、de信号计时单元、高电平时长单元、低电平时长单元、时长比较单元和极性选择单元与前述hs信号极性判定单元中的hs信号上升沿及下降沿检测单元、高电平时长单元、低电平时长单元、时长比较单元和极性选择单元的电路结构完全一直。在此不在重复描述。

41.以上所述,仅为本发明的具体实施案例,本发明的保护范围并不局限于此,任何熟悉本技术的技术人员在本发明所述的技术规范内,对本发明的修改或替换,都应在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。