技术特征:

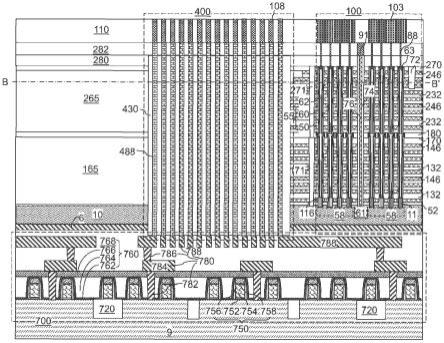

1.一种半导体结构,包括:存储器层级组件,位于半导体衬底之上且包含至少一个交替堆叠体和垂直延伸穿过所述至少一个交替堆叠体的存储器堆叠体结构,其中所述至少一个交替堆叠体包含相应的绝缘层和相应的导电层的交替层;多个横向伸长的接触通孔结构,垂直延伸穿过所述存储器层级组件,沿着第一水平方向横向延伸,并将所述至少一个交替堆叠体横向分为横向间隔开的多个块,其中所述多个块包括一组三个相邻块,所述一组三个相邻块依次包含沿着垂直于所述第一水平方向的第二水平方向布置的第一块、第二块和第三块,并且其中第一子组的所述存储器堆叠体结构延伸穿过所述第一块,第二子组的所述存储器堆叠体结构延伸穿过所述第二块,并且第三子组的所述存储器堆叠体结构延伸穿过所述第三块;以及贯穿存储器层级通孔区域,位于相邻于所述第二块的纵向端部且在所述第一块的阶梯区域与所述第三块的阶梯区域之间,其中所述贯穿存储器层级通孔区域包括嵌入在电介质填充材料部分中的垂直延伸的贯穿存储器层级通孔结构。2.根据权利要求1所述的半导体结构,还包括:至少一个下层级电介质层,覆盖所述半导体衬底;以及平面半导体材料层,覆盖所述至少一个下层级电介质层且包含水平半导体沟道,所述水平半导体沟道电连接到所述存储器堆叠体结构内的垂直半导体沟道。3.根据权利要求2所述的半导体结构,还包括:半导体器件,位于所述半导体衬底上;以及下层级金属互连结构,电短接到所述半导体器件的节点并嵌入在所述至少一个下层级电介质层中,所述至少一个下层级电介质层在所述平面半导体材料层之下,其中所述贯穿存储器层级通孔结构接触所述下层级金属互连结构。4.根据权利要求3所述的半导体结构,其中:所述存储器堆叠体结构中的每一个包括位于所述导电层的每个层级处的存储器元件的垂直堆叠体;所述导电层包括用于所述存储器元件的字线;并且所述半导体器件包括字线开关器件,所述字线开关器件配置为控制对相应的字线的偏置电压。5.根据权利要求4所述的半导体结构,还包括:字线接触通孔结构,延伸穿过后向阶梯电介质材料部分并接触所述字线,所述后向阶梯电介质材料部分覆盖所述第一块和第三块的所述阶梯区域;以上层级金属互连结构,电短接相应的对的字线接触通孔结构和贯穿存储器层级通孔结构,其中所述上层级金属互连结构覆盖所述存储器层级组件,并且跨过所述第二块以及所述第一块和所述第三块之一。6.根据权利要求5所述的半导体结构,其中所述贯穿存储器层级通孔结构中的每一个接触相应的覆盖的上层级金属互连结构。7.根据权利要求5所述的半导体结构,其中所述半导体衬底上的所述半导体器件的子组位于所述平面半导体材料层的区域下方。8.根据权利要求1所述的半导体结构,其中所述电介质填充材料部分至少从包含所述

存储器层级组件的最顶部表面的第一水平平面垂直延伸到位于所述存储器层级组件的最底部表面下方的第二水平平面。9.根据权利要求8所述的半导体结构,还包括平面半导体材料层,所述平面半导体材料层在所述存储器层级组件下方且包含电连接到所述存储器堆叠体结构内的垂直半导体沟道的水平半导体沟道,其中所述第二水平平面位于所述平面半导体材料层的底部表面下方。10.根据权利要求9所述的半导体结构,其中:所述电介质填充材料部分包括实质上垂直的侧壁,所述实质上垂直的侧壁延伸穿过所述存储器层级组件和所述平面半导体材料层;所述第一块和所述第三块的每个阶梯区域包含阶梯,在所述阶梯中每个下方的导电层沿着所述第一水平方向比所述存储器层级组件内的任何覆盖的导电层延伸更远;并且所述存储器堆叠体结构中的每一个包括存储器膜和垂直半导体沟道,所述垂直半导体沟道邻接所述存储器层级组件下方的平面半导体材料层内的相应的水平沟道。11.根据权利要求10所述的半导体结构,还包括多个位线,所述多个位线电耦合到所述存储器堆叠体结构的漏极区域。12.根据权利要求8所述的半导体结构,其中所述电介质填充材料部分具有矩形水平截面形状和实质上垂直的侧壁,所述实质上垂直的侧壁从所述第一水平平面垂直延伸到所述第二水平平面。13.根据权利要求12所述的半导体结构,其中所述贯穿存储器层级通孔结构中的每一个从所述第一水平平面垂直延伸到所述第二水平平面。14.根据权利要求1所述的半导体结构,其中:所述存储器堆叠体结构包括垂直nand器件的存储器元件;所述导电层包括或电连接到所述垂直nand器件的相应的字线;所述半导体衬底包括硅衬底;所述垂直nand器件包括所述硅衬底之上的单片三维nand串的阵列;所述单片三维nand串的阵列的第一器件层级中的至少一个存储器单元位于所述单片三维nand串的阵列的第二器件层级中的另一存储器单元之上;所述硅衬底含有集成电路,所述集成电路包括用于所述存储器器件的所述字线驱动器电路和位线驱动器电路;并且所述单片三维nand串的阵列包括:多个半导体沟道,其中所述多个半导体沟道中的每一个的至少一个端部实质上垂直于所述半导体衬底的顶表面延伸;多个电荷存储元件,每个电荷存储元件位于相邻于所述多个半导体沟道中的相应的一个;以及多个控制栅电极,所述多个控制栅电极具有条形状,所述条形状实质上平行于所述半导体衬底的顶表面延伸,所述多个控制栅电极至少包括位于所述第一器件层级中的第一控制栅电极和位于所述第二器件层级中的第二控制栅电极。15.根据权利要求1所述的半导体结构,还包括界面,延伸穿过所述存储器层级组件的所述电介质填充材料部分的实质上垂直的侧壁在所述界面处与所述第二块的实质上垂直

的侧壁物理接触且沿着所述第二水平方向横向延伸。16.根据权利要求15所述的半导体结构,其中沿着所述第一水平方向在所述第一块的阶梯区域的阶梯表面的最底部垂直表面与包含所述界面的平面之间的横向分离距离大于所述贯穿存储器层级通孔结构与所述界面之间沿着所述第一水平方向的横向分离距离。17.根据权利要求15所述的半导体结构,还包括平面半导体材料层,所述平面半导体材料层在所述至少一个交替堆叠体和所述存储器堆叠体结构下方且与所述半导体衬底垂直间隔开,其中所述电介质填充材料部分的实质上垂直的侧壁接触所述平面半导体材料层的侧壁。18.根据权利要求1所述的半导体结构,其中所述至少一个交替堆叠体包括:第一绝缘层和第一导电层的第一交替堆叠体;以及第二绝缘层和第二导电层的第二交替堆叠体,其中层间电介质层位于所述第一交替堆叠体和所述第二交替堆叠体之间。19.根据权利要求18所述的半导体结构,还包括:第一后向阶梯电介质材料部分,包含第一阶梯底部表面,所述第一阶梯底部表面接触所述第一块的阶梯区域的下部和所述第三块的阶梯区域的下部;以及第二后向阶梯电介质材料部分,包含第二阶梯底部表面,所述第二阶梯底部表面接触所述第一块的阶梯区域的上部和所述第三块的阶梯区域的上部,其中所述层间电介质层在所述第一后向阶梯电介质材料部分与所述第二后向阶梯电介质材料部分之间横向延伸。20.根据权利要求19所述的半导体结构,其中所述电介质填充材料部分接触所述第一后向阶梯电介质材料部分实质上垂直的侧壁、所述第二后向阶梯电介质材料部分的实质上垂直的侧壁和所述层间电介质层的实质上垂直的侧壁。21.根据权利要求1所述的半导体结构,其中沿着所述第一水平方向在所述贯穿存储器层级通孔结构之一与所述第二子组的所述存储器堆叠体结构之间的横向分离距离小于沿着所述第一水平方向在所述第一块的阶梯区域内的阶梯表面的最底部垂直表面与所述第一子组的所述存储器堆叠体结构之间的横向分离距离。22.根据权利要求21所述的半导体结构,其中沿着所述第一水平方向在所述贯穿存储器层级通孔结构之一与所述第二子组的所述存储器堆叠体结构之间的所述横向分离距离大于沿着所述第一水平方向在所述第一块的阶梯区域内的阶梯表面的最顶部垂直表面与所述第一子组的所述存储器堆叠体结构之间的横向分离距离。23.一种三维nand存储器器件,包括:字线驱动器器件,位于衬底上或之上;字线和绝缘层的交替堆叠体,位于所述字线驱动器器件之上;多个存储器堆叠体结构,延伸穿过所述交替堆叠体,每个存储器堆叠体结构包括存储器膜和垂直半导体沟道;多个横向伸长的接触通孔结构,垂直延伸穿过所述交替堆叠体,沿着第一水平方向横向延伸,并且将所述至少一个交替堆叠体横向分为多个横向间隔开的存储器块,其中所述多个存储器块包括一组三个相邻块,所述一组三个相邻块依次包含沿着垂直于所述第一水平方向的第二水平方向布置的第一存储器块、第二存储器块和第三存储器块,并且其中第

一子组的所述存储器堆叠体结构延伸穿过所述第一存储器块,第二子组的所述存储器堆叠体结构延伸穿过所述第二存储器块,第三子组的所述存储器堆叠体结构延伸穿过所述第三存储器块;以及贯穿存储器层级通孔结构,将所述第一存储器块中的字线电耦合到所述字线驱动器器件;其中所述贯穿存储器层级通孔结构延伸穿过电介质填充材料部分,所述电介质填充材料部分位于接近于所述第二存储器块的纵向端部且在所述第一存储器块的阶梯区域和所述第三存储器块的阶梯区域之间并与所述第一存储器块的阶梯区域和所述第三存储器块的阶梯区域中的每一个横向间隔开。24.根据权利要求23所述的器件,还包括:字线接触通孔结构,延伸穿过电介质材料部分并接触所述第一存储器块中的字线,所述电介质材料部分覆盖所述第一存储器块的阶梯区域;以及上层级金属互连结构,电短接相应的对的字线接触通孔结构和贯穿存储器层级通孔结构,其中所述上层级金属互连结构覆盖所述交替堆叠体,并且跨过所述第一存储器块和所述电介质填充材料部分;其中所述第一存储器块的阶梯区域和所述第三存储器块的阶梯区域在相同对角线方向上上升。25.根据权利要求23所述的器件,还包括界面,延伸穿过所述存储器层级组件的所述电介质填充材料部分的实质上垂直的侧壁在所述界面处与所述第二存储器块的实质上垂直的侧壁物理接触且沿着所述第二水平方向横向延伸,其中沿着所述第一水平方向在所述第一存储器块的阶梯区域的阶梯表面的最底部垂直表面与包含所述界面的平面之间的横向分离距离大于所述贯穿存储器层级通孔结构与所述界面之间沿着所述第一水平方向的横向分离距离。

技术总结

公开了一种半导体结构,包括:存储器层级组件,位于半导体衬底之上且包含至少一个交替堆叠体和垂直延伸穿过至少一个交替堆叠体的存储器堆叠体结构;多个横向伸长的接触通孔结构,垂直延伸穿过存储器层级组件,沿着第一水平方向横向延伸,并将至少一个交替堆叠体横向分为横向间隔开的多个块,包括一组三个相邻块,包含沿着垂直于第一水平方向的第二水平方向布置的第一块、第二块和第三块,并且其中第一子组的存储器堆叠体结构延伸穿过第一块,第二子组的存储器堆叠体结构延伸穿过第二块,并且第三子组的存储器堆叠体结构延伸穿过第三块;以及贯穿存储器层级通孔区域。还公开了一种三维NAND存储器器件。种三维NAND存储器器件。种三维NAND存储器器件。

技术研发人员:F.富山 Y.水谷 小川裕之 Y.降幡 J.于 J.卡伊 J.刘 J.阿尔斯梅尔

受保护的技术使用者:桑迪士克科技有限责任公司

技术研发日:2016.09.27

技术公布日:2022/11/18

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。