1.本公开涉及半导体装置。

2.本技术主张基于2020年9月7日的日本技术第2020-149904号的优先权,并引用在所述日本技术中记载的所有的记载内容。

背景技术:

3.专利文献1中记载了一种内部匹配型高输出场效应晶体管(内部匹配型fet)。内部匹配型fet具备配置于管壳内的两个gaasfet芯片和输入输出匹配电路用的氧化铝基板。内部匹配型fet具备输入侧的氧化铝基板和输出侧的氧化铝基板。在输入侧的氧化铝基板和输出侧的氧化铝基板的每一个氧化铝基板设有用于取得阻抗匹配的匹配电路。

4.现有技术文献

5.专利文献

6.专利文献1:日本特开昭63-86904号公报

技术实现要素:

7.一个实施方式的半导体装置具备:半导体芯片,具有设于基板上的晶体管和电极焊盘;电容器,具有夹着电介质的上部电极和下部电极;第一中继焊盘;以及第二中继焊盘,设于半导体芯片的基板上。该半导体装置还具备:第一引线,将第一中继焊盘与半导体芯片的电极焊盘相互连接;第二引线,将第二中继焊盘与电容器的上部电极相互连接;以及第三引线,将第一中继焊盘与第二中继焊盘相互连接。

附图说明

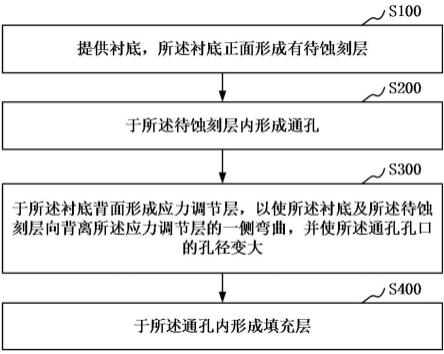

8.图1是表示一个实施方式的半导体装置的内部构成的俯视图。

9.图2是表示图1的半导体装置的半导体芯片、电容器以及引线的俯视图。

10.图3是表示引线长度与电流的关系的例子的图。

11.图4是表示图1的半导体装置的半导体芯片、电容器以及引线的图。

12.图5是表示图1的半导体装置的半导体芯片、电容器以及引线的俯视图。

13.图6是表示第一变形例的半导体装置的半导体芯片、电容器以及引线的俯视图。

14.图7是表示图6的半导体芯片、电容器以及引线的图。

15.图8是将引线放大的立体图。

16.图9是表示第二变形例的半导体装置的半导体芯片、电容器以及引线的俯视图。

17.图10是表示图9的半导体芯片的背面和电容器的背面的背面图。

18.图11是表示第三变形例的半导体装置的半导体芯片、第一中继焊盘、电容器以及引线的俯视图。

具体实施方式

19.在以往的内部匹配型fet中,gaasfet芯片和匹配电路通过接合线相互连接。再者,在高频放大器中处理的信号的频率低的情况下,有时要求减少连接于漏极焊盘等半导体芯片的电极焊盘的引线的条数,并且延长各引线的引线长度。在每条引线的电流大且引线长度长的情况下,担心引线会熔断。

20.本公开的目的在于,提供一种能缩短连接于半导体芯片的电极焊盘的引线的半导体装置。

21.[本公开的实施方式的说明]

[0022]

首先,列举本公开的实施方式的内容进行说明。一个实施方式的半导体装置具备:半导体芯片,具有设于基板上的晶体管和电极焊盘;电容器,具有夹着电介质的上部电极和下部电极;第一中继焊盘;以及第二中继焊盘,设于半导体芯片的基板上。该半导体装置还具备:第一引线,将第一中继焊盘与半导体芯片的电极焊盘相互连接;第二引线,将第二中继焊盘与电容器的上部电极相互连接;以及第三引线,将第一中继焊盘与第二中继焊盘相互连接。

[0023]

在该半导体装置中,半导体芯片在基板上具备晶体管和电极焊盘,电容器具备夹着电介质的上部电极和下部电极。第一引线将半导体芯片的电极焊盘与第一中继焊盘相互连接。第三引线将第一中继焊盘与第二中继焊盘相互连接。第二引线将第二中继焊盘与电容器的上部电极相互连接。由此,半导体芯片和电容器经由从半导体芯片延伸的第一引线、第一中继焊盘、第三引线、半导体芯片上的第二中继焊盘以及朝向电容器延伸的第二引线相互连接。因此,通过具备第一引线、第一中继焊盘、第三引线、第二中继焊盘以及第二引线,能将连接于半导体芯片的电极焊盘的引线仅作为第一引线。能通过各引线经由第一中继焊盘和第二中继焊盘相互连接来缩短各引线。

[0024]

第一中继焊盘也可以配置于电容器的电介质上的与上部电极分离的位置。第二中继焊盘也可以沿着半导体芯片的一边配置。在该情况下,能将第一中继焊盘配置于电容器的电介质上,并且能沿着与电容器对置的半导体芯片的一边配置第二中继焊盘。

[0025]

电极焊盘也可以沿着半导体芯片的一边配置。第二中继焊盘也可以与电极焊盘邻接地配置。在该情况下,能以沿着与电容器对置的半导体芯片的一边排列的方式配置半导体芯片上的电极焊盘和第二中继焊盘。

[0026]

上述的半导体装置也可以具备:多个第一中继焊盘,沿着电容器的一边排列;以及多个第二中继焊盘和多个电极焊盘,沿着半导体芯片的一边排列。也可以是多个第二中继焊盘的每一个与电极焊盘邻接地配置。在该情况下,能沿着与半导体芯片对置的电容器的一边排列多个第一中继焊盘,并且能沿着与电容器对置的半导体芯片的一边排列电极焊盘和第二中继焊盘。

[0027]

上述的半导体装置也可以具备多个第一引线和多个第二引线,也可以是相互邻接的多个第一引线的每一个连接于共用的第一中继焊盘。也可以是相互邻接的多个第二引线的每一个连接于共用的第二中继焊盘。在该情况下,在第一中继焊盘和第二中继焊盘的每一个连接有多条引线,因此,能更有效利用第一中继焊盘和第二中继焊盘来作为引线的连接部。

[0028]

上述的半导体装置也可以在电容器的电介质的背面具备设于与第一中继焊盘对

置的区域以外的区域的背面电极。在该情况下,能通过不在第一中继焊盘的背面设置背面电极来抑制在第一中继焊盘产生的寄生电容。

[0029]

上述的半导体装置也可以在半导体芯片的背面或基板的背面具备设于与第二中继焊盘对置的区域以外的区域的背面电极。在该情况下,能通过不在第二中继焊盘的背面设置背面电极来抑制在第二中继焊盘产生的寄生电容。

[0030]

第一中继焊盘也可以设于电容器与半导体芯片之间。在该情况下,能将第一中继焊盘配置于与电容器和半导体芯片双方分离的场所。

[0031]

基板也可以由碳化硅(sic)、金刚石或金属构成。在该情况下,能由散热性高的材料构成基板。

[0032]

[本公开的实施方式的详细内容]

[0033]

以下,参照附图对本公开的半导体装置的具体例子进行说明。需要说明的是,本发明不限定于下述的示例,意图包括在技术方案中示出、与技术方案等同的范围内的所有变更。在附图的说明中,对相同或相当的要素附加相同的附图标记,并适当省略重复的说明。就附图而言,为了容易理解,对一部分进行简化或夸张地描绘,尺寸比率等不限定于附图中所记载的尺寸比率。

[0034]

图1是表示一个实施方式的半导体装置1的内部构成的图。如图1所示,半导体装置1具备输入端子2、输出端子3、半导体芯片10、分支电路基板20、合成电路基板30、滤波电路40、电容器50以及电容器60。半导体装置1例如具备两个滤波电路40、两个电容器50、60。

[0035]

例如,半导体芯片10是包括两个放大元件11的放大元件部。作为一个例子,每个放大元件11的输出为30w,半导体芯片10整体的输出为60w。半导体装置1例如是具备封装件4的高频放大器。封装件4容纳半导体芯片10、分支电路基板20、合成电路基板30、滤波电路40以及电容器50、60。

[0036]

封装件4为金属制,连接于基准电位。例如,封装件4的平面形状为长方形。封装件4具有在第一方向a1上相互对置的端壁4a、4b以及在第二方向a2上相互对置的侧壁4c、4d。第一方向a1与第二方向a2相互交叉,作为一个例子相互正交。封装件4具有长方形的平坦的底板4e。

[0037]

底板4e例如具有在第一方向a1和第二方向a2双方延伸的平面。端壁4a、4b沿着底板4e的一对边(沿着第二方向a2延伸的边)立起设置。侧壁4c、4d沿着底板4e的另一对边(沿着第一方向a1延伸的边)立起设置。封装件4还具有未图示的盖部。该盖部对由端壁4a、4b以及侧壁4c、4d形成的开口进行密封。

[0038]

输入端子2是金属制的布线图案,从半导体装置1的外部输入高频信号。高频信号例如是基于多载波传输方式的信号,是将载波信号的频率互不相同的多个信号叠加而成的。载波信号的频率频带例如为500mhz以下。输入端子2设于第二方向a2上的端壁4a的中央部。输入端子2从封装件4的外部向内部延伸。

[0039]

例如,半导体芯片10配置于封装件4的底板4e上且包括第一方向a1上的封装件4的中央的区域。半导体芯片10的各放大元件11内置有晶体管。晶体管是场效应晶体管(fet),作为一个例子,是高电子迁移率晶体管(hemt)。各放大元件11具有栅极焊盘、源极焊盘以及漏极焊盘。

[0040]

例如,在各放大元件11的输入端子2侧的一边(端边)交替排列有栅极焊盘(信号输

入端)和源极焊盘。在各放大元件11的输出端子3侧的端边排列有漏极焊盘(信号输出端)。各源极焊盘经由过孔与封装件4的底板4e电连接,被设为基准电位。该过孔在厚度方向(例如,与图1的纸面正交的方向)上贯通放大元件11。各放大元件11将输入至各栅极焊盘的高频信号放大,并从各漏极焊盘输出放大后的高频信号。需要说明的是,在后文对放大元件11的漏极焊盘的周边的构成加以详述。

[0041]

分支电路基板20配置于封装件4的底板4e上。分支电路基板20沿着第一方向a1与输入端子2和半导体芯片10并列配置。分支电路基板20位于输入端子2与半导体芯片10之间。分支电路基板20具有陶瓷制的基板21和设于基板21的主面上的分支电路22。例如,基板21的平面形状为长方形。

[0042]

例如,分支电路基板20的一个长边21a与输入端子2对置,分支电路基板20的另一个长边21b隔着电容器50与半导体芯片10对置。基板21的背面与封装件4的底板4e对置。基板21的一个短边21c与封装件4的侧壁4c对置,基板21的另一个短边21d与封装件4的侧壁4d对置。

[0043]

分支电路22包括设于基板21的主面上的布线图案23。布线图案23经由接合线9a与输入端子2电连接。高频信号从第二方向a2上的输入端子2的中央部经由接合线9a输入至布线图案23。布线图案23例如相对于沿着第一方向a1的基板21的中心线具有线对称的形状。

[0044]

布线图案23以与接合线9a的连接点为起点反复进行2分支,最终到达八个金属焊盘23a。八个金属焊盘23a沿着长边21b排列配置。彼此相邻的金属焊盘23a彼此经由膜电阻相互连接,构成威尔金森型耦合器。由此,确保半导体芯片10的多个栅极焊盘间的隔离,并且谋求从输入端子2观察到的半导体芯片10的输入阻抗的匹配。作为一个例子,在图1中仅示出了一个膜电阻23b。八个金属焊盘23a经由接合线9b与电容器50电连接。

[0045]

电容器50配置于封装件4的底板4e上。电容器50配置于分支电路基板20与半导体芯片10之间。电容器50例如是平行平板型电容器(管芯电容器:die capacitor),在电介质基板的主面上具有多个金属焊盘(未图示)。电容器50的金属焊盘的数量例如与金属焊盘23a的数量相同。电容器50的多个金属焊盘沿着第二方向a2排列成一列。该金属焊盘经由接合线9b与对应的金属焊盘23a电连接。该金属焊盘经由接合线9c与半导体芯片10的对应的栅极焊盘电连接。

[0046]

在电容器50中,由接合线9b、9c所产生的电感分量和连接于该电感分量之间的节点与基准电位(底板4e)之间的金属焊盘的电容构成t型滤波电路。电容器50通过该t型滤波电路进行阻抗转换。通常,在半导体芯片10中根据栅极焊盘来看向晶体管内部的阻抗与传输线的特性阻抗(例如50ω)不同。电容器50是通过t型滤波电路将该阻抗转换成从输入端子2看向晶体管内部而得到的50ω的匹配电路。

[0047]

电容器60配置于封装件4的底板4e上。电容器60配置于半导体芯片10与合成电路基板30之间。电容器60与电容器50同样,例如是平行平板电容器(晶片电容器)。电容器60具有夹着电介质的上部电极和下部电极。即,电容器60也与电容器50同样,在电介质基板的主面上具有多个金属焊盘(未图示)。

[0048]

电容器60的金属焊盘的数量例如与金属焊盘23a的数量相同。电容器60的多个金属焊盘沿着第二方向a2排列成一列。该金属焊盘经由后述的引线组70与半导体芯片10的对应的漏极焊盘电连接。该金属焊盘经由接合线9e与合成电路基板30的对应的金属焊盘33a

电连接。需要说明的是,在图1中简化了引线组70的图示。

[0049]

在电容器60中,由引线组70和接合线9e所产生的电感分量和连接于这些电感分量之间的节点与基准电位(底板4e)之间的金属焊盘的电容构成t型滤波电路。电容器60通过该t型滤波电路进行阻抗转换。通常,在半导体芯片10中从漏极焊盘看向晶体管内部的阻抗与传输线的特性阻抗(例如50ω)不同,多为小于50ω的值。电容器60是通过t型滤波电路将该阻抗转换成从输出端子3看向晶体管内部而得到的50ω的匹配电路。

[0050]

合成电路基板30配置于封装件4的底板4e上。合成电路基板30沿着第一方向a1与半导体芯片10和输出端子3并列配置。合成电路基板30位于半导体芯片10与输出端子3之间。合成电路基板30具有陶瓷制的基板31和设于基板31的主面上的合成基板32。基板31的平面形状例如是长方形。

[0051]

基板31的一个长边31a隔着电容器60与半导体芯片10对置,基板31的另一个长边31b与输出端子3对置。基板31的背面与封装件4的底板4e对置。基板31的一个短边31c与封装件4的侧壁4c对置,基板31的另一个短边31d与封装件4的侧壁4d对置。

[0052]

合成基板32将从半导体芯片10的多个漏极焊盘输出的信号合成为一个输出信号。合成基板32包括设于基板31的主面上的布线图案33。布线图案33例如相对于沿着第一方向a1的基板31的中心线具有线对称的形状。布线图案33包括四个金属焊盘33a。四个金属焊盘33a沿着基板31的长边31a并列配置。

[0053]

彼此相邻的金属焊盘33a彼此经由膜电阻相互连接,构成威尔金森型耦合器。由此,确保半导体芯片10的多个漏极焊盘间的隔离,并且谋求从输出端子3观察到的半导体芯片10的输出阻抗的匹配。需要说明的是,作为一个例子,在图1中仅图示了一个膜电阻33b。

[0054]

各金属焊盘33a经由接合线9e与电容器60的对应的两个金属焊盘电连接。布线图案33反复进行来自四个金属焊盘33a的耦合,并且最终到达与接合线9f的连接点。布线图案33经由接合线9f与输出端子3电连接。放大后的高频信号从第二方向a2上的基板31的中央部输出至输出端子3。

[0055]

输出端子3是金属制的布线图案。输出端子3向半导体装置1的外部输出放大后的高频信号。输出端子3设于第二方向a2上的端壁4b的中央部。输出端子3从封装件4的内部向外部延伸。

[0056]

例如,半导体装置1具备一对滤波电路40。滤波电路40例如为了减少输出信号中所包含的3次互调失真而设置。一个滤波电路40配置于第二方向a2上的基板31的中央部与在基板31中位于半导体芯片10的相反侧的一个角部31e之间。

[0057]

另一个滤波电路40配置于第二方向a2上的基板31的中央部与在基板31中位于半导体芯片10的相反侧的另一个角部31f之间。即,一个滤波电路40相对于基板31的主面的中心配置于靠近角部31e的位置。另一个滤波电路40相对于基板31的主面的中心配置于靠近角部31f的位置。

[0058]

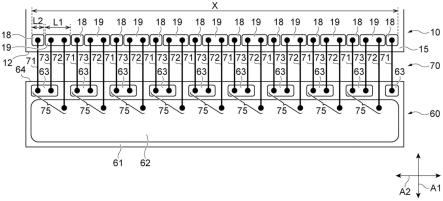

接着,参照图2对半导体芯片10和电容器60的详细内容进行说明。图2是表示半导体芯片10和电容器60的俯视图。半导体芯片10呈细长地延伸的矩形。半导体芯片10具有与电容器60对置的长边12(一边)。

[0059]

例如,长边12沿着第二方向a2延伸。半导体芯片10具备基板15、栅极焊盘、有源区、漏极焊盘18(电极焊盘)以及空焊盘19(第二中继焊盘)。基板15呈具备上述的长边12的长方

形。

[0060]

半导体芯片10例如具备多个漏极焊盘18和多个空焊盘19。漏极焊盘18和空焊盘19的每一个被配置为沿着与电容器60对置的长边12排列。能通过半导体芯片10具备空焊盘19来缩短引线组70的各引线的引线长度。

[0061]

如上所述,电容器60具备电介质61、上部电极62、下部电极(未图示)以及焊盘63(第一中继焊盘)。电容器60(电介质61)具有与半导体芯片10对置的长边64(一边)。例如,长边64沿着第二方向a2延伸。

[0062]

上部电极62和焊盘63配置于电介质61上。焊盘63设于比上部电极62靠半导体芯片10侧。电介质61呈具备上述的长边64的长方形。电容器60具备多个焊盘63。多个焊盘63设于上部电极62的半导体芯片10侧。例如,沿着长边64排列有多个焊盘63。各焊盘63呈具有沿着第二方向a2延伸的长边的长方形。

[0063]

如上所述,半导体芯片10和电容器60经由引线组70相互电连接。引线组70包括第一引线71、第二引线72以及第三引线73。第一引线71将焊盘63与半导体芯片10的漏极焊盘18相互连接。第二引线72将电容器60的上部电极62与空焊盘19相互连接。第三引线73将空焊盘19与焊盘63相互连接。

[0064]

例如,将漏极焊盘18与焊盘63相互连接的第一引线71、将空焊盘19与焊盘63相互连接的第三引线73以及将空焊盘19与上部电极62相互连接的第二引线72依次沿着第二方向a2排列。作为一个例子,第一引线71、第二引线72以及第三引线73中的至少任一个引线的引线长度为0.6mm。需要说明的是,第二引线72也可以比第一引线71和第三引线73长。

[0065]

如此,在本实施方式中,将半导体芯片10与电容器60相互连接的引线组70具备第一引线71、第二引线72以及第三引线73。由此,能缩短构成引线组70的各引线的引线长度。如图3所例示的那样,引线长度(l)短,由此各引线的熔断电流(i)变高。

[0066]

图4是表示半导体芯片10、电容器60以及第三引线73的图。如图4所示,半导体芯片10例如包括ag-p层10b、au层10c、sic层10d以及gan层10f。半导体芯片10具备在ag-p层10b上设有au层10c、在au层10c上设有sic层10d、在sic层10d上设有gan层10f的结构。

[0067]

空焊盘19设于gan层10f上。空焊盘19例如含有金(au)。在半导体芯片10中,热从空焊盘19经由gan层10f流入至sic层10d。来自引线组70(例如第三引线73)的热被散热,从而能抑制由发热引起的引线组70的熔断。作为一个例子,底板4e的厚度t1为1000μm,ag-p层10b的厚度t2为30μm,au层10c和sic层10d的厚度t3为100μm。gan层10f的厚度t4为0.6μm,空焊盘19的厚度t5为10μm,从空焊盘19起的焊盘63的立起的高度h为100μm。

[0068]

例如,半导体芯片10的基板15包括ag-p层10b、au层10c以及sic层10d。如上所述,基板15作为将通过元件产生的热进行散热的散热板发挥功能。基板15例如由散热性高的材料构成。例如,基板15也可以与sic层10d一起具备金刚石层或金属层或者具备金刚石层或金属层来代替sic层10d。基板15的金属层的材料例如是含有铜或金的红色系金属材料或者含有银、镍或铝的银白色系金属材料。

[0069]

电容器60例如包括ag-p层60b、au层60c以及陶瓷层60d。电容器60具备在ag-p层60b上设有au层60c、在au层60c上设有陶瓷层60d的结构。焊盘63设于陶瓷层60d上。焊盘63例如含有金(au)。在电容器60中,来自引线组70(例如第三引线73)的热从焊盘63散热至陶瓷层60d。其结果是,能抑制由发热引起的引线组70的熔断。

[0070]

图5是表示图1所示的半导体芯片10、电容器60以及引线组70的整体的俯视图。如图5所示,引线组70包括多个第一引线71、多个第二引线72以及多个第三引线73。引线组70也可以具备由第一引线71、第二引线72以及第三引线73构成的多个组75。例如,多个组75沿着第二方向a2排列。

[0071]

例如,在各组75中,第一引线71、第三引线73以及第二引线72被配置为依次沿着第二方向a2排列。作为一个例子,组75的数量为9。例如,空焊盘19的第二方向a2的长度l1比漏极焊盘18的第二方向a2的长度l2长。作为一个例子,空焊盘19的长度l1为250μm,漏极焊盘18的长度l2为150μm。从位于第二方向a2的一端的漏极焊盘18起到位于第二方向a2的另一端的漏极焊盘18为止的长度x为5.34mm。

[0072]

接着,对从实施方式的半导体装置1获得的作用效果进行说明。在半导体装置1中,半导体芯片10在基板15上具备晶体管和漏极焊盘18。电容器60具备夹着电介质61的上部电极62和下部电极。第一引线71将半导体芯片10的漏极焊盘18与焊盘63相互连接。第三引线73将焊盘63与空焊盘19相互连接。第二引线72将空焊盘19与电容器60的上部电极62相互连接。由此,半导体芯片10和电容器60经由从半导体芯片10延伸的第一引线71、焊盘63、第三引线73、半导体芯片10上的空焊盘19以及朝向电容器60延伸的第二引线72相互连接。

[0073]

通过具备第一引线71、焊盘63、第三引线73、空焊盘19以及第二引线72,能将连接于半导体芯片10的漏极焊盘18的引线仅作为第一引线71。能通过各引线经由焊盘63和空焊盘19相互连接来缩短各引线。

[0074]

焊盘63也可以配置于电容器60的电介质61上的与上部电极62分离的位置。空焊盘19也可以沿着半导体芯片10的长边12配置。在该情况下,能将焊盘63配置于电容器60的电介质61上。能沿着与电容器60对置的半导体芯片10的长边12配置空焊盘19。

[0075]

也可以是,漏极焊盘18沿着半导体芯片10的长边12配置,空焊盘19与漏极焊盘18邻接地配置。在该情况下,能以沿着与电容器60对置的半导体芯片10的长边12排列的方式配置半导体芯片10上的漏极焊盘18和空焊盘19。

[0076]

半导体装置1也可以具备:多个焊盘63,沿着电容器60的长边64排列;以及多个空焊盘19和多个漏极焊盘18,沿着半导体芯片10的长边12排列。也可以是多个空焊盘19的每一个与漏极焊盘18邻接地配置。在该情况下,能沿着与半导体芯片10对置的电容器60的长边64排列多个焊盘63,并且能沿着与电容器60对置的半导体芯片10的长边12排列漏极焊盘18和空焊盘19。

[0077]

基板15也可以由碳化硅(sic)、金刚石或金属构成。在该情况下,能由散热性高的材料构成基板15。

[0078]

接着,参照图6对第一变形例的半导体装置进行说明。如图6所示,第一变形例的半导体装置具备漏极焊盘18a、空焊盘19b、焊盘63a以及引线组70a。漏极焊盘18a与漏极焊盘18不同,空焊盘19b与空焊盘19不同。焊盘63a与焊盘63不同,引线组70a与引线组70不同。以下,适当省略与上述的半导体装置1的说明重复的说明。

[0079]

图7是表示图6所示的第一变形例的半导体装置的半导体芯片10a和电容器60a的第二方向a2的整体的俯视图。如图7所示,第一变形例的半导体芯片10a具备空焊盘19a和空焊盘19b。空焊盘19a设于半导体芯片10a的第二方向a2上的两端的每一端。空焊盘19a的形状、大小以及功能例如与上述的空焊盘19相同。空焊盘19b从空焊盘19a观察配置于半导体

芯片10a的第二方向a2的中央侧。多个空焊盘19b被夹入一对空焊盘19a之间。

[0080]

在第一变形例的半导体装置中,在漏极焊盘18a连接有一条或两条第一引线71。在空焊盘19b连接有两条第二引线72和两条第三引线73,在焊盘63a连接有一条或两条第一引线71和一条或两条第三引线73。在第一变形例的半导体装置中,空焊盘19b和焊盘63a被通用为供多个引线连接的焊盘。

[0081]

引线组70a具备多个第一组75a和多个第二组75b,在第一组75a和第二组75b中引线的排列顺序互不相同。第一组75a和第二组75b例如沿着第二方向a2交替排列。在第一组75a中,第二引线72、第三引线73以及第一引线71被配置为依次沿着第二方向a2排列。在第二组75b中,第一引线71、第三引线73以及第二引线72被配置为依次沿着第二方向a2排列。作为一个例子,第一组75a的数量和第二组75b的数量为6。例如,空焊盘19b的第二方向a2的长度l3和焊盘63a的第二方向a2的长度为500μm。

[0082]

以上,第一变形例的半导体装置具备多个第一引线71和多个第二引线72。相互邻接的多个第一引线71的每一个连接于共用的焊盘63a。相互邻接的多个第二引线72的每一个连接于共用的空焊盘19b。因此,能更有效利用焊盘63a和空焊盘19b来作为引线的连接部。此外,能进一步缩短引线组70a的各引线的引线长度。引线组70a的各引线的间隔变短而互感增加,因此能使各引线的引线长度缩短互感的增加的量。因此,能进一步降低引线组70a的各引线的熔断的可能性。

[0083]

更具体而言,如图8所例示的那样,位于第二方向a2的端部的引线w1主要受单侧最接近的引线w2和下一个邻接的引线w3的影响。另一方面,引线w4受两侧的引线w2、引线w3、引线w5以及引线w6的影响,因此,基于互感的有效引线长度与引线w1相比大幅变化。若将各引线的长度设为l,将各引线的半径设为r,将各引线的距离接地的高度设为h,将引线的间隔设为d,将真空的导磁率设为μ0,则互感如以下的算式(1)这样表示。

[0084]

[数式1]

[0085][0086]

根据上述的算式(1),互感m与引线的长度l成比例,并且引线的间隔d越窄则互感m越大。因此,引线的间隔越窄则互感m越大,因此能缩短引线的长度l。

[0087]

接下来,参照图9和图10对第二变形例的半导体装置进行说明。图9示出了第二变形例的半导体芯片10c和电容器60c的表面。图10示出了半导体芯片10c和电容器60c的背面。半导体芯片10c具备漏极焊盘18a、漏极焊盘18b以及空焊盘19a、19b。

[0088]

在本变形例中,漏极焊盘18a设于半导体芯片10c的第二方向a2上的两端的每一端。在漏极焊盘18a例如连接有一条第一引线71。在漏极焊盘18b连接有两条第一引线71。在空焊盘19b连接有两条第二引线72和两条第三引线73。

[0089]

电容器60c具备电介质61、上部电极62、焊盘63a以及焊盘63b。焊盘63b设于电容器60c的第二方向a2上的两端的每一端。在焊盘63a连接有两条第一引线71和两条第三引线73。在焊盘63b连接有一条第一引线71和一条第三引线73。第二变形例的引线组70c具备沿着第二方向a2排列的多个第一组75a和多个第二组75b。第二组75b和第一组75a沿着第二方向a2交替排列。

[0090]

半导体芯片10c还具备背面电极10g,电容器60c还具备背面电极67。背面电极10g

例如呈沿着半导体芯片10的长边12、长边13以及短边14的长方形。背面电极10g设于栅极焊盘16和有源区17的半导体芯片10c的背面。背面电极10g未设于漏极焊盘18a、18b以及空焊盘19b的半导体芯片10c的背面。即,背面电极10g从半导体芯片10c的漏极焊盘18a、18b以及空焊盘19b的背侧被削除。

[0091]

电容器60c的背面电极67设于上部电极62的背面。背面电极67未设于焊盘63a和焊盘63b的电容器60c的背面。即,背面电极67从电容器60c的焊盘63a和焊盘63b的背侧被削除。

[0092]

以上,第二变形例的半导体装置在电容器60c的背面具备设于与焊盘63a和焊盘63b对置的区域以外的区域的背面电极67。如此,能通过不在焊盘63a和焊盘63b的背面设置背面电极67来抑制在焊盘63a和焊盘63b产生的寄生电容。

[0093]

第二变形例的半导体装置在半导体芯片10c的背面或基板15的背面具备设于与空焊盘19b对置的区域以外的区域的背面电极10g。如此,能通过不在空焊盘19b的背面设置背面电极10g来抑制在空焊盘19b产生的寄生电容。

[0094]

接着,参照图11对第三变形例的半导体装置进行说明。如图11所示,第三变形例的半导体装置具备半导体芯片10、电容器60d以及中继基板80。电容器60d在不具有焊盘63这一点上与上述的电容器60不同。第三变形例的半导体装置具备设于与半导体芯片10和电容器60d分体的中继基板80的中继焊盘81(第一中继焊盘)来代替焊盘63。

[0095]

中继基板80被设为具有在第二方向a2延伸的长边和在第一方向a1延伸的短边的长方形。中继焊盘81被设为具有沿着中继基板80的长边延伸的长边和沿着中继基板80的短边延伸的短边的长方形。在中继焊盘81连接有从多个漏极焊盘18的每一个延伸的多个第一引线71和从多个空焊盘19延伸的多个第三引线73。

[0096]

以上,在第三变形例的半导体装置中,中继焊盘81设于电容器60d与半导体芯片10之间。因此,能将中继焊盘81配置于与电容器60d和半导体芯片10双方分离的场所。

[0097]

以上,对本公开的半导体装置的实施方式进行了说明。然而,本发明不限定于上述的实施方式或变形例。即,本领域技术人员容易认识到本发明能在不变更技术方案中记载的主旨的范围内进行各种变形和变更。例如,半导体装置的各部件的形状、大小、数量、材料以及配置方案不限于上述的内容,可以适当进行变更。

[0098]

例如,在上述的实施方式中,对半导体芯片10具备两个放大元件11的例子进行了说明。然而,放大元件11的数量也可以为一个,还可以为三个以上,可以适当进行变更。

[0099]

在上述内容中,对具备设于与半导体芯片10和电容器60d分体的中继基板80的中继焊盘81来代替电容器60的焊盘63的例子进行了说明。然而,也可以具备设于与半导体芯片10和电容器60分体的中继基板的中继焊盘来代替半导体芯片10的空焊盘19。如此,中继焊盘既可以与半导体芯片10或电容器60一体地设置,也可以分体地设置。可以对中继焊盘的配置方案适当进行变更。也可以对第一引线71、第二引线72以及第三引线73的数量和配置方案适当进行变更。

[0100]

附图标记说明:

[0101]1……

半导体装置

[0102]2……

输入端子

[0103]3……

输出端子

[0104]4……

封装件

[0105]

4a、4b

……

端壁

[0106]

4c、4d

……

侧壁

[0107]

4e

……

底板

[0108]

9a、9b、9c、9e、9f

……

接合线

[0109]

10、10a、10c

……

半导体芯片

[0110]

10b

……

ag-p层

[0111]

10c

……

au层

[0112]

10d

……

sic层

[0113]

10f

……

gan层

[0114]

10g

……

背面电极

[0115]

11

……

放大元件

[0116]

12

……

长边(一边)

[0117]

13

……

长边

[0118]

14

……

短边

[0119]

15

……

基板

[0120]

16

……

栅极焊盘

[0121]

17

……

有源区

[0122]

18、18a、18b

……

漏极焊盘(电极焊盘)

[0123]

19、19a、19b

……

空焊盘(第二中继焊盘)

[0124]

20

……

分支电路基板

[0125]

21

……

基板

[0126]

21a、21b

……

长边

[0127]

21c、21d

……

短边

[0128]

22

……

分支电路

[0129]

23

……

布线图案

[0130]

23a

……

金属焊盘

[0131]

23b

……

膜电阻

[0132]

30

……

合成电路基板

[0133]

31

……

基板

[0134]

31a、31b

……

长边

[0135]

31c、31d

……

短边

[0136]

31e、31f

……

角部

[0137]

32

……

合成基板

[0138]

33

……

布线图案

[0139]

33a

……

金属焊盘

[0140]

33b

……

膜电阻

[0141]

40

……

滤波电路

[0142]

50

……

电容器

[0143]

60、60a、60c、60d

……

电容器

[0144]

60b

……

ag-p层

[0145]

60c

……

au层

[0146]

60d

……

陶瓷层

[0147]

61

……

电介质

[0148]

62

……

上部电极

[0149]

63、63a、63b

……

焊盘(第一中继焊盘)

[0150]

64

……

长边(一边)

[0151]

65

……

长边

[0152]

66

……

短边

[0153]

67

……

背面电极

[0154]

70、70a、70c

……

引线组

[0155]

71

……

第一引线

[0156]

72

……

第二引线

[0157]

73

……

第三引线

[0158]

75

……

组

[0159]

75a

……

第一组

[0160]

75b

……

第二组

[0161]

80

……

中继基板

[0162]

81

……

中继焊盘(第一中继焊盘)

[0163]

a1

……

第一方向

[0164]

a2

……

第二方向

[0165]d……

间隔

[0166]m……

互感

[0167]

w1、w2、w3、w4、w5、w6

……

引线。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。