1.本发明的实施例涉及半导体器件及其形成方法。

背景技术:

2.将半导体器件用于各种电子应用,例如,诸如个人电脑、手机、数码相机和其他电子设备。通常通过在半导体衬底上方依次沉积绝缘或介电层、导电层和半导体材料层,以及使用光刻图案化各个材料层以在其上形成电路组件和元件来制造半导体器件。

3.半导体行业通过不断减小最小部件尺寸来不断改善各个电子组件(例如晶体管、二极管、电阻器、电容器等)的集成密度,这允许将更多的组件集成到给定区域中。然而,随着最小部件尺寸的减小,出现了应解决的额外的问题。

技术实现要素:

4.本发明的一些实施例提供了一种半导体器件,包括:衬底,包括有源区域;栅极堆叠件,位于有源区域上方;以及硬掩模,位于栅极堆叠件上方,硬掩模包括:覆盖层;支撑层,沿着覆盖层的侧壁和底部延伸,其中,支撑层包括金属氧化物材料或金属氮化物材料;以及衬垫层,沿着支撑层的侧壁和底部延伸。

5.本发明的另一些实施例提供了一种半导体器件,包括:衬底,包括有源区域;第一间隔件结构和第二间隔件结构,位于有源区域上方,第一间隔件结构的第一侧壁面向第二间隔件结构的第二侧壁;栅极堆叠件,位于有源区域上方以及位于第一间隔件结构和第二间隔件结构之间,其中,栅极堆叠件的顶表面低于第一间隔件结构的顶表面和第二间隔件结构的顶表面;硬掩模,位于栅极堆叠件上方以及位于第一间隔件结构和第二间隔件结构之间,硬掩模包括:衬垫层,沿着栅极堆叠件的顶表面、第一间隔件结构的第一侧壁和第二间隔件结构的第二侧壁延伸,衬垫层包括第一氮化物材料;支撑层,位于衬垫层上方,支撑层包括第二氮化物材料或第一氧化物材料;以及覆盖层,位于支撑层上方,覆盖层包括第三氮化物材料;外延源极/漏极区,嵌入在与第一间隔件结构相邻的有源区域中;以及源极/漏极接触件,位于外延源极/漏极区上方并且与第一间隔件结构相邻,源极/漏极接触件的顶表面与硬掩模的顶表面齐平。

6.本发明的又一些实施例提供了一种形成半导体器件的方法,包括:在衬底的有源区域上方形成伪栅极结构,伪栅极结构具有第一侧壁和与第一侧壁相对的第二侧壁;在伪栅极结构的第一侧壁上形成第一间隔件结构;在伪栅极结构的第二侧壁上形成第二间隔件结构;用替换栅极结构替换伪栅极结构;使替换栅极结构凹进以形成嵌入在第一间隔件结构和第二间隔件结构之间的凹槽;以及在凹槽中形成硬掩模,其中,形成硬掩模包括:沿着凹槽的侧壁和底部形成衬垫层;在凹槽中的衬垫层上方形成支撑层,支撑层包括金属氮化物材料或金属氧化物材料;以及在凹槽中的支撑层上方形成覆盖层。

7.本发明的一些实施例提供了半导体器件的自对准接触件硬掩模结构及其形成方法。

附图说明

8.当结合附图进行阅读时,从以下详细描述可最佳理解本发明的方面。需要强调的是,根据工业中的标准实践,各个部件未按比例绘制。实际上,为了清楚的讨论,各个部件的尺寸可以任意地增大或减小。

9.图1至图13、图15至图17以及图21至图26是根据一些实施例的制造半导体器件中的中间阶段的截面图。

10.图14是示出根据一些实施例的用于自对准接触件硬掩模的各个层的各个可能的材料的表格。

11.图18是示出根据一些实施例的原子层蚀刻工艺的流程图。

12.图19和图20是根据一些实施例的在执行原子层蚀刻工艺时候的中间阶段的截面图。

13.图27是根据一些实施例的半导体器件的截面图。

具体实施方式

14.以下公开内容提供了许多用于实现本发明的不同部件的不同实施例或实例。下面描述了组件和布置的具体实例以简化本发明。当然,这些仅仅是实例,而不旨在限制本发明。例如,以下描述中,在第二部件上方或者上形成第一部件可以包括第一部件和第二部件直接接触形成的实施例,并且也可以包括可以在第一部件和第二部件之间形成的额外的部件,从而使得第一部件和第二部件可以不直接接触的实例。此外,本发明可以在各个实例中重复参考标号和/或字符。该重复是为了简单和清楚的目的,并且其本身不指示所讨论的各个实施例和/或配置之间的关系。

15.而且,为便于描述,在此可以使用诸如“在

…

之下”、“在

…

下面”、“下部”、“在

…

之上”、“上部”等空间相对术语,以描述如图所示的一个元件或部件与另一个(或另一些)原件或部件的关系。除了图中所示的方位外,空间相对术语旨在包括器件在使用或操作中的不同方位。装置可以以其他方式定向(旋转90度或在其他方位上),而本文使用的空间相对描述符可以同样地作出相应的解释。

16.将针对特定背景描述实施例,即,半导体器件的自对准接触件(sac)硬掩模及其形成方法。在使用后栅极工艺形成的平面场效应晶体管(fet)器件的背景下讨论本文展现的各个实施例。在其他实施例中,可以使用先栅极工艺。然而,可以将各个实施例应用至包括其他类型的晶体管(例如,finfet、全环栅(gaa)晶体管(例如,诸如纳米fet)等)的管芯来代替平面fet或与平面fet组合。本文讨论的各个实施例允许形成包括支撑层并且具有改进的抗蚀刻性的sac硬掩模,使得在形成用于源极/漏极接触件的开口的蚀刻工艺期间,减少了sac硬掩模的角部损失并且保持了相邻的源极/漏极接触件之间的良好的绝缘。

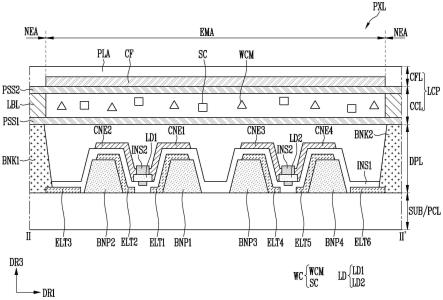

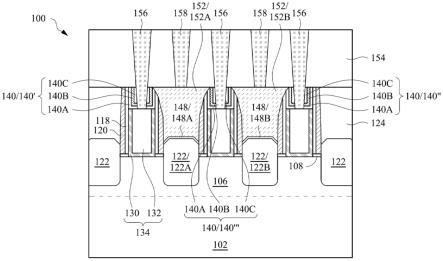

17.图1至图13、图15至图17和图21至图26是根据一些实施例的制造半导体器件100的中间阶段的截面图。在图1中,提供了衬底102。衬底102可以是诸如块状半导体的半导体衬底、绝缘体上半导体(soi)衬底等,其可以是被掺杂的(例如,用p型或n型掺杂剂)或未被掺杂的。衬底102可以是诸如硅晶圆的晶圆。通常,soi衬底是形成在绝缘层上的一层半导体材料。绝缘层可以是例如掩埋氧化物(box)层、氧化硅层等。在衬底上提供绝缘层,通常是硅或玻璃衬底。也可以使用其他衬底,诸如多层或梯度衬底。在一些实施例中,衬底102的半导体

材料可以包括硅;锗;包括碳化硅、砷化镓、磷化镓、磷化铟、砷化铟和/或锑化铟的化合物半导体;包括sige、gaasp、alinas、algaas、gainas、gainp和/或gainasp的合金半导体;或其组合。

18.衬底102具有区域100n和区域100p。可以将区域100n用于形成n型器件,诸如n型晶体管。可以将区域100p用于形成p型器件,诸如p型晶体管。区域100n可以与区域100p物理地分隔开(如分隔件104所示),并且可以在区域100n和区域100p之间设置任意数量的器件部件(例如,其他有源器件、掺杂区域、隔离结构等)。

19.衬底102包括有源区域106。在一些实施例中,当半导体器件100是平面fet器件时,有源区域106包括衬底102的上平面部分。在其他实施例中,当半导体器件100是平面fet器件时,有源区域106是形成在衬底102上方的半导体层,使得半导体层和衬底102包括不同的半导体材料。在一些实施例中,当半导体器件100是finfet器件时,有源区域106包括一个或多个半导体条。半导体条也可以被称为鳍。在一些实施例中,半导体条和衬底102包括相同的半导体材料。在其他实施例中,半导体条和衬底102包括不同的半导体材料。可以通过隔离区域将半导体条彼此分隔开并且彼此隔离。在一些实施例中,当半导体器件100是诸如纳米fet器件的gaa器件时,有源区域106包括一个或多个纳米结构。纳米结构可以包括纳米片、纳米线等。在一些实施例中,纳米结构和衬底102包括相同的半导体材料。在其他实施例中,纳米结构和衬底102包括不同的半导体材料。

20.进一步在图1中,可以在衬底102的有源区域106中形成适当的阱(未示出)。在一些实施例中,可以在区域100n中形成p阱,并且可以在区域100p中形成n阱。在一些实施例中,在区域100n和区域100p两者中形成p阱或n阱。在具有不同阱类型的实施例中,可以使用光刻胶或其他掩模(未示出)来实现区域100n和区域100p的不同的注入步骤。例如,可以在区域100n和区域100p两者中的衬底102的有源区域106上方形成第一光刻胶。图案化第一光刻胶以暴露区域100p。可以通过使用旋涂技术形成第一光刻胶并且可以使用可接受的光刻技术来图案化第一光刻胶。一旦图案化第一光刻胶,在区域100p中执行n型掺杂物注入,同时第一光刻胶的剩余部分作为掩模以基本上防止n型掺杂物被注入到区域100n中。n型掺杂物可以是磷、砷、锑、它们的组合等。在注入之后,例如,通过可接受的灰化工艺随后进行湿清洁工艺来去除第一光刻胶。

21.在区域100p的注入以后,在区域100p和区域100n两者中的衬底102的有源区域106上方形成第二光刻胶。图案化第二光刻胶以暴露区域100n。可以通过使用旋涂技术形成第二光刻胶并且可以使用可接受的光刻技术来图案化第二光刻胶。一旦图案化第二光刻胶,可以在区域100n中执行p型掺杂物注入,同时第二光刻胶的剩余部分作为掩模以基本上防止p型掺杂物被注入到区域100p中。p型掺杂物可以是硼、bf2、铟、它们的组合等。在注入之后,例如,可以通过可接受的灰化工艺随后进行湿清洁工艺来去除第二光刻胶。在执行区域100n和区域100p的注入之后,可以执行退火工艺以激活注入的p型和/或n型掺杂物。

22.在图2中,在衬底102的有源区域106上方形成伪介电层108。伪介电层108可以是例如氧化硅、氮化硅、它们的组合等,并且可以根据可接受的技术来沉积或热生长伪介电层108。随后,在伪介电层108上方形成伪栅极层110,以及在伪栅极层110上方形成掩模层112。

23.可以在伪介电层108上方沉积伪栅极层110,然后使用例如化学机械抛光(cmp)工艺平坦化伪栅极层110。伪栅极层110可以是导电材料并且可以选自包括非晶硅、多晶态硅

(多晶硅)、多晶硅锗(多晶sige)、金属氮化物、金属硅化物、金属氧化物和金属的组。可以通过物理气相沉积(pvd)、化学气相沉积(cvd)、溅射沉积或本领域已知且用于沉积导电材料的其他技术来沉积伪栅极层110。

24.可以在伪栅极层110上方沉积掩模层112。掩模层112可以包括例如一层或多层氧化硅、氮化硅、氮氧化硅、它们的组合等。在一些实施例中,掩模层112可以包括氮化硅层和位于氮化硅层上方的氧化硅层。

25.在一些实施例中,在区域100n和区域100p两者的上方形成单个伪介电层108、单个伪栅极层110以及单个掩模层112。在其他实施例中,在区域100n中形成第一伪介电层、第一伪栅极层和第一掩模层,并且在区域100p中形成第二伪介电层、第二伪栅极层和第二掩模层,使得第一伪介电层与第二伪介电层包括不同的材料,第一伪栅极层与第二伪栅极层包括不同的材料,以及第一掩膜层与第二掩膜层包括不同的材料。

26.图3至图13、图15至图17和图21至图26示出了根据一些实施例的制造半导体器件100的各个额外的步骤。图3至图13、图15至图17和图21至图26示出了区域100n和区域100p中的任何一个中的部件。例如,可以将图3至图13、图15至图17和图21至图26所示的结构应用于区域100n和区域100p两者。在每个图所附的文本中描述区域100n和区域100p的结构的差异(如果有的话)。

27.在图3中,可以使用可接受的光刻和蚀刻技术来图案化掩模层112(见图2)以形成掩模116。在一些实施例中,蚀刻技术可以包括一种或多种各向异性蚀刻工艺,诸如反应离子蚀刻(rie)、中性束蚀刻(nbe)、它们的组合等。随后,可以将掩模116的图案转移到伪栅极层110(见图2)以形成伪栅极114。在一些实施例中,还可以通过可接受的蚀刻技术来将掩模116的图案转移到伪介电层108。如以下更详细描述的,伪栅极114是牺牲栅极并且随后被替换栅极替换。由此,也可以将伪栅极114称为牺牲栅极。在其他实施例中,一些伪栅极114没有被替换并且保留在半导体器件100的最终结构中。

28.进一步在图3中,可以在伪栅极114和相应的掩模116的侧壁上形成栅极密封间隔件118。热氧化或沉积随后进行各向异性蚀刻可以形成栅极密封间隔件118。栅极密封间隔件118可以包括氧化硅、氮化硅、氮氧化硅、sicn、sioc、siocn、它们的组合等。

29.在形成栅极密封间隔件118之后,可以执行用于轻掺杂源极/漏极(ldd)区(未明确示出)的注入。在具有不同器件类型的实施例中,类似于以上在图1中讨论的注入,可以在区域100n上方形成诸如光刻胶的掩模,同时暴露区域100p,以及可以将适当类型(例如,p型)的掺杂物注入到区域100p中的衬底102的有源区域106中。然后,可以去除掩膜。随后,可以在区域100p上方形成诸如光刻胶的掩模,同时暴露区域100n,以及可以将适当类型的掺杂物(例如,n型)注入到区域100n中的衬底102的有源区域106中。然后可以去除掩膜。n型掺杂物可以是前面讨论的任何n型掺杂物,并且p型掺杂物可以是前面讨论的任何p型掺杂物。可以使用退火来激活注入的掺杂物。

30.在图4中,在沿着伪栅极114和掩模116的侧壁的栅极密封间隔件118上形成栅极间隔件120。可以通过毯式或共形沉积绝缘材料以及随后各向异性地蚀刻绝缘材料来形成栅极间隔件120。栅极间隔件120的绝缘材料可以包括氧化硅、氮化硅、氮氧化硅、sicn、sioc、siocn、或它们的组合等。在一些实施例中,栅极间隔件120中的每个可以包括多个层(未示出),使得这些层包括不同的材料。

31.值得注意的是,以上公开内容概括地描述了形成间隔件和ldd区的工艺。可以使用其他工艺和顺序。例如,可以利用更少的或额外的间隔件,可以利用不同顺序的步骤(例如,在分别形成栅极间隔件120之前可以不蚀刻栅极密封间隔件118,从而产生“l形”栅极密封间隔件,可以形成和去除间隔件,和/或类似步骤)。此外,可以使用不同的结构和步骤来形成n型和p型器件。例如,可以在形成栅极密封间隔件118之前,形成区域100n中的n型器件的ldd区,而可以在形成栅极密封间隔件118之后,形成区域100p中的p型器件的ldd区。

32.在图5中,在有源区域106中形成外延源极/漏极区122以在相应的沟道区中施加应力,从而改善器件性能。在有源区域106中形成外延源极/漏极区122,使得每个伪栅极114设置在相应的邻近的外延源极/漏极区122对之间。在一些实施例中,外延源极/漏极区122可以延伸到有源区域106中并且还可以穿透有源区域106。在一些实施例中,将栅极间隔件120用于将外延源极/漏极区122与伪栅极114分隔开适当的横向距离,从而使得外延源极/漏极区122不会使随后形成的半导体器件100的栅极短路。

33.可以通过掩蔽区域100p以及蚀刻区域100n中的有源区域106的暴露部分以在有源区域106中形成凹槽来形成区域100n中的外延源极/漏极区122。然后,在凹槽中外延生长区域100n中的外延源极/漏极区122。外延源极/漏极区122可以包括诸如适用于n型晶体管的任何可接受的材料。例如,如果有源区域106由硅制成,则区域100n中的外延源极/漏极区122可以包括在半导体器件100的相应的沟道区中施加拉伸应变的材料,诸如硅、sic、sicp、sip、它们的组合等。区域100n中的外延源极/漏极区122可以具有小平面。

34.可以通过掩蔽区域100n以及蚀刻区域100p中的有源区域106的暴露部分以在有源区域106中形成凹槽来形成区域100p中的外延源极/漏极区122。然后,在凹槽中外延生长区域100p中的外延源极/漏极区122。外延源极/漏极区122可以包括诸如适用于p型晶体管的任何可接受的材料。例如,如果有源区域106由硅制成,则区域100p中的外延源极/漏极区122可以包括在半导体器件100的相应的沟道区中施加压缩应变的材料,诸如sige、sigeb、ge、gesn、它们的组合等。区域100p中的外延源极/漏极区122可以具有小平面。

35.可以用掺杂剂注入外延源极/漏极区122以形成源极/漏极区,类似于先前讨论的用于形成轻掺杂源极/漏极区的工艺,随后进行退火。用于外延源极/漏极区122的n型和/或p型掺杂物可以是先前讨论的任何掺杂物。在一些实施例中,可以在生长期间原位掺杂外延源极/漏极区122。

36.在图6中,在图5所示的结构上方沉积ild 124。ild 124可以由介电材料形成,并且可以通过诸如cvd、等离子体增强cvd(pecvd)、可流动cvd(fcvd)、它们的组合等的任何合适的方法来沉积ild 124。介电材料可以包括磷硅酸盐玻璃(psg)、硼硅酸盐玻璃(bsg)、硼掺杂的磷硅酸盐玻璃(bpsg)、未掺杂的硅酸盐玻璃(usg)、它们的组合等。也可以使用通过任何可接受的工艺形成的其他绝缘材料。在一些实施例中,可以在ild 124和外延源极/漏极区122、掩模116以及栅极间隔件120之间设置接触蚀刻停止层(未示出)。接触蚀刻停止层可以包括具有与上面的ild 124的材料不同的蚀刻速率的介电材料,诸如氮化硅、氧化硅、氮氧化硅、它们的组合等。

37.在图7中,可以执行诸如cmp工艺的平坦化工艺,以使ild 124的顶表面与掩模116的顶表面齐平。在一些实施例中,平坦化工艺还可以去除伪栅极114上的掩模116,以及沿着掩模116的侧壁的栅极密封间隔件118和栅极间隔件120的部分。在示出的实施例中,在平坦

化工艺之后,掩模116、栅极密封间隔件118、栅极间隔件120和ild 124的顶表面在平坦化工艺的工艺变化内彼此基本上共面或齐平。由此,掩模116的顶表面通过ild 124暴露。在当还去除掩模116时的实施例中,平坦化工艺使ild 124的顶表面与伪栅极114的顶表面齐平。

38.在图8中,在ild 124上方形成保护层126。保护层126保护ild 124免受随后的工艺步骤的损坏。保护层126也可以被称为蚀刻停止层。在一些实施例中,使ild 124向下凹进至掩模116的顶表面之下,在形成的凹槽中沉积保护层126的材料,并且执行诸如cmp工艺的平坦化工艺以使保护层126的顶表面与掩膜116的顶表面齐平。在一些实施例中,保护层126可以包括sin、sic、sicn、sico、它们的组合等,并且可以使用ald、cvd、它们的组合等来沉积保护层126。

39.在图9中,在一个(多个)蚀刻步骤中去除伪栅极114和掩模116(参见图8),从而形成开口128。在一些实施例中,还可以去除开口128中的伪介电层108的部分。在其他实施例中,仅去除伪栅极114,同时保留伪介电层108并且伪介电层108被开口128暴露。在一些实施例中,从管芯的第一区域(例如,核心逻辑区域)中的开口128去除伪介电层108并且在管芯的第二区域(例如,输入/输出区域)中的开口128中保留伪介电层108。在一些实施例中,通过各向异性干蚀刻工艺去除伪栅极114和掩模116。例如,蚀刻工艺可以包括使用一种(多种)选择性地蚀刻伪栅极114和掩模116而不蚀刻保护层126、栅极密封间隔件118和栅极间隔件120的反应气体的干蚀刻工艺。每个开口128暴露有源区域106的相应的沟道区。每个沟道区设置在相邻的外延源极/漏极区122对之间。在去除期间,当蚀刻伪栅极114和掩模116时,可以将伪介电层108用作蚀刻停止层。然后可以在伪栅极114和掩模116的去除之后,可选地去除伪介电层108。

40.在图10中,在开口128(参见图9)中形成栅极介电层130和栅电极132以形成栅极堆叠件134。栅极堆叠件134也可以被称为替换栅极堆叠件。图11示出了图10的区域136的详细视图。在一些实施例中,在开口128中(参见图9)形成栅极介电层130的材料。还可以在保护层126的顶表面上形成栅极介电层130的材料。在一些实施例中,栅极介电层130包括氧化硅、氮化硅或它们的多层。在一些实施例中,栅极介电层130包括高k介电材料,并且在这些实施例中,栅极介电层130可以具有大于约7.0的k值,并且可以包括铪、铝、锆、镧、锰、钡、钛、铅以及它们的组合的金属氧化物或硅酸盐。栅极介电层130的形成方法可以包括分子束沉积(mbd)、ald、pecvd、它们的组合等。

41.随后,在栅极介电层130上方沉积栅电极132的材料并且填充开口128(参见图9)的剩余部分。尽管在图10中示出了单层栅电极132,但栅电极132可以包括任意数量的衬垫层132a、任意数量的功函数调整层132b以及导电填充层132c,如图11所示。衬垫层132a可以包括tin、tio、tan、tac、它们的组合、它们的多层等,并且可以使用pvd、cvd、ald、它们的组合等形成衬垫层132a。在区域100n中,功函数调整层132b可以包括ti、ag、al、tial、tialn、tialc、tac、tacn、tasin、taalc、mn、zr、它们的组合、它们的多层等,并且可以使用pvd、cvd、ald、它们的组合等来形成功函数调整层132b。在区域100p中,功函数调整层132b可以包括tin、wn、tan、ru、co、它们的组合、它们的多层等,并且可以使用pvd、cvd、ald、它们的组合等来形成功函数调整层132b。在一些实施例中,导电填充层132c可以包括co、ru、al、ag、au、w、ni、ti、cu、mn、pd、re、ir、pt、zr、它们的合金、它们的组合、它们的多层等,并且可以使用pvd、cvd、ald、电、镀、它们的组合等形成导电填充层132c。

42.在填充开口128(参见图9)之后,可以执行诸如cmp的平坦化工艺,以去除栅极介电层130和栅电极132的多余部分,这些多余部分位于保护层126的顶表面上方。栅电极132和栅介电层130的剩余部分因此形成半导体器件100的栅极堆叠件134。

43.可以同时发生区域100n和区域100p中的栅极介电层130的形成,使得每个区域中的栅极介电层130由相同的材料形成。在其他实施例中,可以通过不同的工艺形成每个区域中的栅极介电层130,使得不同区域中的栅极介电层130可以由不同的材料形成。可以同时发生区域100n和区域100p中的导电填充层132c的形成,使得每个区域中的导电填充层132c由相同的材料形成。在其他实施例中,可以通过不同的工艺形成每个区域中的导电填充层132c,使得不同区域中的导电填充层132c可以由不同的材料形成。当使用不同的工艺时,可以使用各个掩蔽步骤来掩蔽和暴露适当的区域。

44.在图12中,使栅极堆叠件134向下凹进至保护层126的顶表面之下以形成凹槽138。在一些实施例中,凹进工艺包括一个或多个蚀刻工艺。一个或多个蚀刻工艺可以包括对栅极堆叠件134的材料具有选择性并且基本上不蚀刻保护层126、栅极密封间隔件118以及栅极间隔件120的材料的蚀刻工艺。凹槽138在保护层126的顶表面之下延伸至深度d1。在一些实施例中,深度d1在约25nm至约150nm之间。

45.图13和图15是根据一些实施例的在栅极堆叠件134上方制造硬掩模140的中间阶段的截面图。在图13中,沿着凹槽138(见图12)的侧壁和底部以及在保护层126上方形成第一层140a,在第一层140a上方形成第二层140b,以及在第二层140b上方形成第三层140c。在一些实施例中,第三层140c过填充凹槽138(参见图12)。在其他实施例中,第三层140c被省略。在这样的实施例中,第二层140b过填充凹槽138(参见图12)。第一层140a也可以被称为衬垫层,第二层140b也可以被称为支撑层,第三层140c也可以被称为覆盖层,以及硬掩模140也可以被称为自对准接触件(sac)硬掩模。在一些实施例中,第一层140a具有约2nm至约10nm之间的厚度。在一些实施例中,第二层140b具有约2nm至约10nm之间的厚度。在一些实施例中,第三层140c具有约10nm至约30nm之间的厚度。

46.图14是示出根据一些实施例的用于硬掩模140的第一层140a、第二层140b和第三层140c(见图13和图15)的各个可能材料的表格。在实施例#1中,第一层140a包括sin,第二层140b包括si、金属氮化物材料(诸如tan、tin、aln或zrn)或金属氧化物材料(诸如tio、hfo、alo、或zro),并且第三层140c包括sin。在实施例#2中,第一层140a包括tin,第二层140b包括aln,并且第三层140c包括sin。在实施例#3中,第一层140a包括aln,第二层140b包括tin,并且第三层140c包括sin。在实施例#4中,第一层140a包括金属氮化物材料(诸如tin、aln或zrn)或金属氧化物材料(诸如tio、hfo、alo或zro),第二层140b包括sin,并且省略了第三层140c。在实施例#5中,第一层140a包括sin,第二层140b包括金属氮化物材料(诸如tan、aln或tin),并且省略了第三层140c。在一些实施例中,包括金属氧化物材料的硬掩模140具有比包括金属氮化物材料的硬掩模140更好的绝缘特性。

47.返回参考图13,可以使用等离子体增强ald(peald)工艺、热ald工艺等来形成第一层140a、第二层140b和第三层140c。在一些实施例中,使用等离子体系统执行peald工艺,诸如13.56hz电容耦合等离子体(ccp)系统,功率在约100w至800w之间,以及工艺温度在约200℃至约500℃之间。在一些实施例中,在约100℃至约400℃之间的工艺温度下执行ald工艺。

48.在一些实施例中,当第一层140a、第二层140b或第三层140c由sin制成时,使用包

括硅前体气体、氮前体气体、以及额外的气体的工艺气体混合物来执行peald或ald工艺。在一些实施例中,硅前体气体包括sih2i2(二碘硅烷)气体、氮前体气体包括n2气体、以及额外气体包括h2气体。在其他实施例中,硅前体气体包括sih2cl2(二氯硅烷)气体、氮前体气体包括n2气体、nh3气体或它们的混合物、以及额外气体包括ar气体。

49.在一些实施例中,当第一层140a或第二层140b由tan制成时,使用包括钽前体气体、氮前体气体和额外气体的工艺气体混合物来执行peald或ald工艺。在一些实施例中,钽前体气体包括tacl5、ta(nme2)5、ta(oet)5、ta(n

t

bu)(net2)3、ta(n

t

pn)(nme2)3、ta(nme2)5、taf5、ta(n

t

bu)(netme)3,或ta(nipr)(netme)3,氮前体气体包括n2气体、nh4气体或它们的混合物,以及额外气体包括h2气体。

50.在一些实施例中,当第一层140a或第二层140b由tin制成时,使用包括钛前体气体、氮前体气体以及附加气体的工艺气体混合物来执行peald或ald工艺。在一些实施例中,钛前体气体包括ticl4或ti(nme2)4,氮前体气体包括n2气体、nh3气体或它们的混合物,以及额外气体包括h2气体。

51.在一些实施例中,当第一层140a或第二层140b由hfo制成时,使用包括铪前体气体、氧前体气体以及额外气体的工艺气体混合物来执行peald或ald工艺。在一些实施例中,铪前体气体包括hf(net2)4、hf(netme)4、hf(nme2)4、hf(oh)3nh2、hf(mp)4、hf(o

t

bu)4,氧前体气体包括o2气,以及额外气体包括n2气。

52.在一些实施例中,当第一层140a或第二层140b由tio制成时,使用包括钛前体气体和氧前体气体的工艺气体混合物来执行peald或ald工艺。

53.在一些实施例中,钛前体气体包括ticl4或ti(nme2)4,以及氧前体气体包括o2气体、h2o气体或它们的混合物。

54.在一些实施例中,当第一层140a或第二层140b由alo制成时,使用包括铝前体气体和氧前体气体的工艺气体混合物来执行peald或ald工艺。

55.在一些实施例中,铝前体气体包括alh3(menc4h4)或alme3,以及氧前体气体包括co2气体、o2气体、h2o气体或它们的混合物。

56.在一些实施例中,当第一层140a或第二层140b由aln制成时,使用包括铝前体气体、氮前体气体和额外气体的工艺气体混合物来执行peald或ald工艺。在一些实施例中,铝前体气体包括alh3(menc4h4)或alme3,氮前体气体包括n2气体、nh3气体或它们的混合物,以及额外气体包括h2气体。

57.在一些实施例中,当第一层140a或第二层140b由zro制成时,使用包括锆前体气体、氧前体气体和额外气体的工艺气体混合物来执行peald或ald工艺。在一些实施例中,锆前体气体包括zr(net2)4、zr(netme)4或zr(otbu)4,氧前体气体包括o2气体,以及额外气体包括n2气体。

58.在图15中,在填充凹槽138(参见图12)之后,可以执行诸如cmp的平坦化工艺,以去除第一层140a、第二层140b和第三层140c的多余部分,这些多余部分位于ild 124的顶表面的上方。在一些实施例中,平坦化工艺还去除保护层126,使得ild 124的顶表面被暴露。第一层140a、第二层140b和第三层140c的剩余部分形成硬掩模140。在执行平坦化工艺之后,硬掩模140的顶表面在平坦化工艺的工艺变化内与ild 124的顶表面基本共面或齐平。在一些实施例中,硬掩模140具有在约50nm至约90nm之间的高度h1。在其他实施例中,硬掩模140

具有在约10nm至约30nm之间的高度h1。

59.通过使用如以上参考图14所述的材料形成第一层140a和/或第二层140b,硬掩模140的侧壁和拐角被加强并且在随后的形成用于源极/漏极接触件的开口的蚀刻工艺中降低或避免侧壁和拐角损失。

60.在图16中,在硬掩模140和ild 124上方形成ild 142,并且在ild 142上方形成硬掩模144。在一些实施例中,可以使用与ild 124类似的材料和方法形成ild 142,并且在此不再重复该描述。在一些实施例中,ild 124和ild142包括相同的材料。在其他实施例中,ild 124和ild 142包括不同的材料。在一些实施例中,硬掩模144可以包括tin、wc、w、wcn、wn、ti、sin、sic、sicn、sico、它们的组合等,并且可以使用cvd、ald、它们的组合等来形成硬掩模144。

61.在图17中,图案化硬掩模144以及ild 124和142以形成开口146。在示出的实施例中,开口146完全暴露外延源极/漏极区122a和122b,完全暴露插入在外延源极/漏极区122a和外延源极/漏极区122b之间的硬掩模140

”’

,部分地暴露与外延源极/漏极区122a相邻的硬掩模140’,以及部分地暴露与外延源极/漏极区122b相邻的硬掩模140”。特别地,开口146包括暴露外延源极/漏极区122a的第一开口146a、暴露外延源极/漏极区122b的第二开口146b和暴露硬掩模140’、140”、以及140”的第三开口146c。在其他实施例中,开口146可以根据半导体器件100的设计要求暴露任意数量的外延源极/漏极区122和任意数量的硬掩模140。

62.在一些实施例中,用于形成开口146的图案化工艺可以包括用于图案化硬掩模144的第一图案化工艺和用于图案化ild 124和142的第二图案化工艺。在一些实施例中,第一图案化工艺包括合适的光刻和蚀刻工艺。第一图案化工艺的第一蚀刻工艺可以是干蚀刻工艺、湿蚀刻工艺等。第一蚀刻工艺可以是各向异性的。

63.在一些实施例中,第二图案化工艺包括使用图案化的硬掩模144作为蚀刻掩模并将图案化的硬掩模144的图案转移到ild 124和142的第二蚀刻工艺。在一些实施例中,第二蚀刻工艺是原子层蚀刻(ale)工艺并且使用包括碳氟化合物(具有化学式c

xfy

,诸如cf2、c4f6、c3f8、ch3f等)、o2、co2、ar、或n2、它们的组合等的蚀刻剂来执行第二蚀刻工艺。在一些实施例中,第二蚀刻工艺可以是各向异性的。

64.进一步在图17中,在一些实施例中,第二蚀刻工艺还蚀刻暴露的硬掩模140’、140”和140

”’

,使得暴露的硬掩模140’和140”的拐角被去除并且降低了暴露的硬掩模140

”’

的高度。在完成第二次蚀刻工艺之后,暴露的硬掩模140

”’

具有高度h2。在一些实施例中,暴露的硬掩模140

”’

的高度h2小于未蚀刻的硬掩模140的高度h1(参见图15)。在一些实施例中,高度h2在约5nm至约25nm之间。在一些实施例中,高度h2与高度h1(见图15)的比率在约0.055和至约1之间。通过使用以上参考图14所述的材料形成硬掩模140的第一层140a和/或第二层140b,硬掩模140’、140”和140

”’

的侧壁和角部被加强并且降低或避免了侧壁、拐角和高度损失。

65.此外,在一些实施例中,第二蚀刻工艺还蚀刻与外延源极/漏极区122a和122b相邻设置的栅极密封间隔件118和栅极间隔件120。在一些实施例中,在完成第二蚀刻工艺之后,蚀刻的栅极密封间隔件118的宽度随着蚀刻的栅极密封间隔件118延伸远离有源区域106而减小,并且蚀刻的栅极间隔件120的宽度随着蚀刻的栅极间隔件120延伸远离有源区域106

而减小。

66.图18是示出根据一些实施例的ale工艺200的流程图。图19和图20是根据一些实施例在执行ale工艺200时的中间阶段的截面图。参考图18和图19,ale工艺200包括执行n次ale循环202。在一些实施例中,n在1至50之间。在一些实施例中,ale循环202包括执行步骤204,其中,在将被蚀刻的层212(例如,诸如如图17所示的ild层124和142)上方引入第一气体214。在一些实施例中,第一气体214可以包括碳氟化合物气体并且可以离子化第一气体214。在一些实施例中,第一气体214被吸附在层212的暴露表面上。在一些实施例中,引入第一气体214的时间在约0.1秒至约20秒之间。在一些实施例中,第一气体214的流速在约0.1sccm至约200sccm之间。

67.在一些实施例中,吸附的碳氟化合物气体在层212上方形成碳氟聚合物层216。在一些实施例中,碳氟聚合物层216的厚度取决于层212的材料,如图20所示。在一些实施例中,当层212由氧化硅制成时,碳氟聚合物层216具有在约0nm至约5nm之间的厚度t1。在一些实施例中,当层212由氮化硅制成时,碳氟聚合物层216具有在约0nm至约15nm之间的厚度t2。在一些实施例中,当层212由硅制成时,碳氟聚合物层216具有在约0nm至约20nm之间的厚度t3。在一些实施例中,当层212由金属氧化物或金属氮化物制成时,碳氟聚合物层216具有在约0nm至约40nm之间的厚度t4。在一些实施例中,厚度t1小于厚度t2,厚度t2小于厚度t3,以及厚度t3小于厚度t4。如以下更详细描述的,碳氟聚合物层216的厚度影响层212的蚀刻速率,使得具有较厚碳氟聚合物层的层212具有较低的蚀刻速率。

68.进一步参考图18和图19,在步骤206中,使用诸如n2、ar、它们的组合等的非反应性气体吹扫第一气体214的未吸附部分。在一些实施例中,执行吹扫的时间在1秒至约10秒之间。在一些实施例中,非反应性气体的流速可以在约200sccm至约5000sccm之间。

69.在步骤208中,在层212上方引入第二气体220。在一些实施例中,第二气体220包括被离子化以获得ar

离子的ar气体。在一些实施例中,使ar

离子加速朝向层212并轰击层212。由于轰击,层212的原子之间的键被破坏。在一些实施例中,当层212由氧化硅制成时,用ar

离子的轰击破坏了硅原子218和氧原子(未示出)之间的键。随后,吸附在层212上的第一气体214的分子(例如,诸如碳氟化合物分子)与硅原子218反应以形成挥发性副产物222。

70.在一些实施例中,形成在层212上方的碳氟聚合物层216保护层212免受ar

离子轰击的损坏。在一些实施例中,其上形成有较厚的碳氟聚合物层的材料具有较少的被破坏的键,这引起了产生较少的挥发性副产物222,并且随后引起较低的蚀刻速率。

71.在步骤210中,使用诸如n2、ar、它们的组合等的非反应性气体来吹扫挥发性副产物222。在一些实施例中,执行吹扫的时间在1秒至约10秒之间。在一些实施例中,非反应性气体的流速可以在约200sccm至约5000sccm之间。在一些实施例中,ale循环202蚀刻层212的原子层212a。可以通过改变ale循环n的数量来调整层212的被去除的原子层的数量。

72.返回参考图17,选择硬掩模140的材料,使得在使用ale工艺200蚀刻ild 124和142(参见图18和图19)时硬掩模140不会被显着蚀刻。在一些实施例中,通过如以上参考图14所描述的选择第一层140a和/或第二层140b的材料,硬掩模140的蚀刻速率低于ild 124和142的蚀刻速率。在一些实施例中,如以上参考图14所描述的第一层140a和/或第二层140b的材料具有高离子轰击抵抗性以及低溅射产率(由于高结合能和高密度),以及允许形成厚的非挥发性碳氟聚合物层,以进一步保护免受离子轰击破坏。

73.在图21中,对暴露的外延源极/漏极区122a和122b执行清洁工艺。在一些实施例中,清洁工艺去除在形成开口146之后可能保留在暴露的外延源极/漏极区122a和122b上的任何残留氧化物。在一些实施例中,清洁工艺还去除硬掩模144(见图17)并暴露ild142。如以下更详细描述的,在一些实施例中,清洁工艺包括使用蚀刻系统300(参见图22)执行蚀刻工艺,然后使用热装置400(参见图23)执行热处理。

74.在图22中,在一些实施例中,将包括图17的结构的晶圆303引入蚀刻系统300的腔室301中。蚀刻系统300包括腔室301内的平台305,并且晶圆303放置在平台305上。在一些实施例中,平台305包括诸如水管线的冷却管线307,其被配置为将晶圆303的温度保持在期望的温度范围内。在一些实施例中,晶圆303的温度在约20℃至约90℃之间。在一些实施例中,蚀刻系统300还包括入口309a和309b,以及出口311a和311b。将入口309a和309b配置为将工艺气体引入腔室301。将出口311a和311b配置为从腔室301中排出反应副产物。在一些实施例中,入口309a将nh3气体引入腔室301,并且入口309b将hf气体引入腔室301。在一些实施例中,在将气体混合物引入腔室301之前混合nh3气体和hf气体。

75.在一些实施例中,nh3和hf分子被吸附到晶圆303的表面上并且与残留的氧化物反应,例如,诸如氧化硅。nh3和hf分子与氧化硅通过反应(1)和(2)反应:

76.sio2 4f 4nh3‑‑

》sif4 2h2o 4nh3(1)

77.sif4 2hf 2nh3‑‑

》(nh4)2sif6(2)

78.作为反应(1)和(2)的结果,化合物层313形成在晶圆303的表面上残留氧化物的位置处。在一些实施例中,化合物层313包括(nh4)2sif6。

79.在图23中,将晶圆303转移到热装置400中。热装置400包括位于腔室401内的平台403,并且晶圆303放置在平台403上。在一些实施例中,平台403包括配置为将晶圆303的温度升高到期望温度的加热器405。加热器405可以包括一个或多个加热元件,例如,诸如电阻加热元件。在一些实施例中,将晶圆303加热至约100℃至约200℃之间的温度并且持续时间在约7秒至约120秒之间。在一些实施例中,对晶圆303执行热处理通过化学反应(3)将化合物层313分解成挥发性组分

80.(nh4)2sif6‑‑

》sif4 2hf 2nh3。(3)

81.随后,通过出口407a和407b从腔室401排出挥发性组分。在一些实施例中,例如,在非反应性气体气氛中执行热处理工艺,诸如n2气体气氛。

82.在图24和图25中,在外延源极/漏极区122a和122b上方分别形成源极/漏极接触件152a和152b。在图24中,在执行清洁工艺之后,在外延源极/漏极区122a和122b上方通过开口146(见图21)分别形成硅化物层148a和148b。在一些实施例中,在开口146中沉积金属材料。金属材料可以包括ti、co、ni、nico、pt、nipt、ir、ptir、er、yb、pd、rh、nb、它们的组合等,并且可以使用pvd、溅射、它们的组合等形成该金属材料。随后,执行退火工艺以形成硅化物层148a和148b。在外延源极/漏极区122包括硅的一些实施例中,退火工艺使金属材料与硅发生反应以在金属材料和外延源极/漏极区122之间的界面处形成金属材料的硅化物。在形成硅化物层148a和148b之后,例如,使用诸如合适的蚀刻工艺的合适的去除工艺来去除金属材料的未反应部分。

83.在形成硅化物层148a和148b之后,在开口146(参见图21)中和ild142上方形成导电层150。在一些实施例中,导电层150过填充开口146。在一些实施例中,通过首先在开口

146中和ild 142上方形成阻挡层(未单独示出)来形成导电层150。阻挡层可以沿着开口146的底部和侧壁延伸。阻挡层可以包括钛、氮化钛、钽、氮化钽、它们的组合、它们的多层等,并且可以通过ald、cvd、pvd、溅射、它们的组合等形成阻挡层。随后,在开口146内和ild 142上方的阻挡层上方形成粘附层(未单独示出)。粘附层可以包括钴、钌、它们的合金、它们的组合、它们的多层等,并且可以通过ald、cvd、pvd、溅射、它们的组合等形成粘附层。在形成粘附层之后,在开口146内和ild 142上方的粘附层上方形成晶种层(未单独示出)。晶种层可以包括铜、钛、镍、金、锰、它们的组合、它们的多层等,并且可以通过ald、cvd、pvd、溅射、它们的组合等形成晶种层。随后,在开口146内和ild 142上方的晶种层上方形成导电填充材料(未单独示出)。在一些实施例中,导电填充材料过填充开口146。导电填充材料可以包括铜、铝、钨、钌、钴、它们的组合、它们的合金、它们的多层等,并且可以使用例如镀、ald、cvd、pvd或其他合适的方法来形成导电填充材料。

84.在图25中,在形成导电层150(参见图24)之后,执行平坦化工艺以去除导电层150的过填充开口146(参见图21)的部分。在一些实施例中,平坦化工艺还去除了ild 142(见图24)、ild 124的部分、硬掩模140的部分、栅极密封间隔件118的部分以及栅极间隔件120的部分。导电层150的剩余部分在开口146a(见图21)中形成源极/漏极接触件152a以及在开口146b中形成源极/漏极接触件152b。平坦化工艺可以包括cmp工艺、回蚀刻工艺、研磨工艺、它们的组合等。在执行平坦化工艺之后,源极/漏极接触件152a的顶表面、源极/漏极接触件152b的顶表面、ild 124的顶表面、硬掩模140的顶表面、栅极密封间隔件118的顶表面以及栅极间隔件120的顶表面在平坦化工艺的工艺变化内是基本上彼此齐平或共面的。通过使用如以上参考图13至图15所述的材料形成硬掩模140,硬掩模140

”’

基本上没有被蚀刻并且在源极/漏极接触件152a和源极/漏极接触件152b之间实现了良好的隔离。

85.在一些实施例中,由于以上参考图17描述的蚀刻工艺,硬掩模140’的宽度随着硬掩模140’延伸远离相应的栅极堆叠件134的顶表面而减小,硬掩模140”的宽度随着硬掩模140”延伸远离相应的栅极堆叠件134的顶表面而减小,以及硬掩模140

”’

的宽度随着硬掩模140

”’

延伸远离相应的栅极堆叠件134的顶表面而减小。在一些实施例中,源极/漏极接触件152a的宽度随着源极/漏极接触件152a延伸远离外延源极/漏极区122a而增大,并且源极/漏极接触件152b的宽度随着源极/漏极接触件152b延伸远离外延源极/漏极区122b而增大。

86.在图26中,在ild 124、硬掩模140和源极/漏极接触件152上方形成ild154。在一些实施例中,可以使用与ild 124类似的材料和方法形成ild 154,并且在此处不再重复该描述。在一些实施例中,ild 124和154包括相同的材料。在其他实施例中,ild 124和154包括不同的材料。在一些实施例中,将栅极接触件156形成为与相应的栅极堆叠件134电接触,并且将导电通孔158形成为与相应的源极/漏极接触件152电接触。在一些实施例中,图案化ild 154和硬掩模140以形成用于栅极接触件156和导电通孔158的开口。在一些实施例中,图案化工艺包括合适的光刻和蚀刻工艺。合适的蚀刻工艺可以包括一种或多种干蚀刻工艺。蚀刻工艺可以是各向异性的。用于栅极接触件156的开口延伸穿过ild 154以及相应的硬掩模140,并暴露相应的栅极堆叠件134。用于导电通孔158的开口延伸穿过ild 154并暴露相应的源极/漏极接触件152。在形成开口之后,在相应的开口中形成栅极接触件156和导电通孔158。在一些实施例中,可以使用与源极/漏极接触件152类似的材料和方法形成栅极接触件156和导电通孔158,并且在此不再重复该描述。

87.图27示出了根据一些实施例的半导体器件500的截面图。半导体器件500与半导体器件100(见图26)类似,类似的部件用类似的参考标号标记,并且在此不再重复类似部件的描述。在一些实施例中,可以使用类似于以上参考图1至图16描述的工艺步骤的工艺步骤来形成半导体器件500,并且在此不再重复该描述。在示出的实施例中,形成硬掩模140,使得层140c(参见图26)被省略。

88.根据实施例,器件包括包含有源区域的衬底,有源区域上方的栅极堆叠件以及栅极堆叠件上方的硬掩模。硬掩模包括覆盖层、沿覆盖层的侧壁和底部延伸的支撑层、以及沿着支撑层的侧壁和底部延伸的衬垫层。支撑层包括金属氧化物材料或金属氮化物材料。

89.实施例可以包括以下部件中的一个或多个。在器件中,衬垫层包括与金属氮化物材料不同的第一氮化物材料。在器件中,覆盖层包括不同于金属氮化物材料的第二氮化物材料。在器件中,第一氮化物材料与第二氮化物材料相同。在器件中,第一氮化物材料与第二氮化物材料不同。该器件还包括延伸到与栅极堆叠件相邻的有源区域中的外延源极/漏极区。该器件还包括位于外延源极/漏极区上方的源极/漏极接触件,源极/漏极接触件的顶表面与硬掩模的顶表面齐平。

90.根据另一实施例,器件包括包含有源区域的衬底、位于有源区域上方的第一间隔件结构和第二间隔件结构、位于有源区域上方以及位于第一间隔件结构和第二间隔件结构之间的栅极堆叠件,以及位于栅极堆叠件上方以及位于第一间隔件结构和第二间隔件结构之间的硬掩模。第一间隔件结构的第一侧壁面向第二间隔件结构的第二侧壁。栅极堆叠件的顶表面低于第一间隔件结构的顶表面和第二间隔件结构的顶表面。硬掩模包括沿着栅极堆叠件的顶表面、第一间隔件结构的第一侧壁和第二间隔件结构的第二侧壁延伸的衬垫层、位于衬垫层上方的支撑层、以及位于支撑件上方的覆盖层。衬垫层包括第一氮化物材料。支撑层包括第二氮化物材料或第一氧化物材料。覆盖层包括第三氮化物材料。该器件还包括嵌入在与第一间隔件结构相邻的有源区域中的外延源极/漏极区以及位于外延源极/漏极区上方并且与第一间隔件结构相邻的源极/漏极接触件。源极/漏极接触件的顶表面与硬掩模的顶表面齐平。

91.实施例可以包括以下部件中的一个或多个。在器件中,第一间隔件结构的宽度随着第一间隔件结构延伸远离有源区域而减小。在器件中,第二间隔件结构的宽度随着第二间隔件结构延伸远离有源区域而减小。在器件中,源极/漏极接触件的宽度随着源极/漏极接触件延伸远离外延源极/漏极区而增加。在器件中,第一氮化物材料包括sin,第二氮化物材料包括tan、tin、aln或zrn,以及第三氮化物材料包括sin。在器件中,第一氮化物材料包括sin,第一氧化物材料包括tio、hfo、alo或zro,以及第三氮化物材料包括sin。在器件中,第一氮化物材料包括tin或aln,第二氮化物材料包括tin或aln,以及第三氮化物材料包括sin。

92.根据又一实施例,一种方法包括在衬底的有源区域上方形成伪栅极结构,该伪栅极结构具有第一侧壁和与第一侧壁相对的第二侧壁,在伪栅极结构的第一侧壁上形成第一间隔件结构,在伪栅极结构的第二侧壁上形成第二间隔件结构,用替换栅极结构替换伪栅极结构,使替换栅极结构凹进以形成嵌入在第一间隔件结构和第二间隔件结构之间的凹槽,以及在凹槽中形成硬掩模。形成硬掩模包括沿着凹槽的侧壁和底部形成衬垫层,在凹槽中的衬垫层上方形成支撑层,以及在凹槽中的支撑层上方形成覆盖层。支撑层包括金属氮

化物材料或金属氧化物材料。

93.实施例可以包括以下部件中的一个或多个。该方法还包括在与第一间隔件结构相邻的有源区域中形成外延源极/漏极区。该方法还包括在外延源极/漏极区上方并且与第一间隔件结构相邻地形成源极/漏极接触件,源极/漏极接触件的顶表面与硬掩模的顶表面齐平。在该方法中,衬垫层和支撑层包括不同材料。其中覆盖层和支撑层包括不同材料。在该方法中,金属氮化物材料为tan、tin、aln或zrn,并且其中金属氧化物材料为tio、hfo、alo或zro。

94.前面概述了落干实施例的特征,使得本领域技术人员可以更好地理解本发明的方面。本领域技术人员应该理解,他们可以容易地使用本发明作为基础来设计或修改用于实施与在此所介绍实施例相同的目的和/或实现相同优势的其他工艺和结构。本领域技术人员也应该意识到,这种等同构造并不背离本发明的精神和范围,并且在不背离本发明的精神和范围的情况下,在此他们可以做出多种变化、替换以及改变。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。