1.本发明涉及显示领域,具体涉及一种显示面板及其制作方法、显示装置。

背景技术:

2.目前,随着人们对显示面板需求的日益提升,对其性能的关注度也与日俱增。如何提高显示面板的性能也是的业内研究人员的研究热点,其中,对于薄膜晶体管的改善是显示面板的性能的一大研究方向,一直受到研究人员的广泛关注。发明人研究发现,薄膜晶体管在形成过程中,由于半导体层的导体部载流子浓度较高易导致载流子向沟道部的扩散,导致实际形成的沟道部长度远小于预期的沟道部长度,存在导致薄膜晶体管存在失效问题。

3.因此,亟需一种显示面板及其制作方法、显示装置以解决上述技术问题。

技术实现要素:

4.本发明提供一种显示面板及其制作方法、显示装置,可以缓解目前薄膜晶体管由于半导体层的沟道部实际形成的长度远小于预期的沟道部长度导致薄膜晶体管失效的技术问题。

5.本发明提供一种显示面板,包括衬底以及位于所述衬底上的多个薄膜晶体管,所述薄膜晶体管包括:

6.半导体层,位于所述衬底上,所述半导体层包括沟道部、位于所述沟道部两侧的导体部;

7.第一栅极,位于所述半导体层上;

8.其中,所述沟道部在所述衬底上的正投影位于所述第一栅极在所述衬底上的正投影内,所述第一栅极具有第一长度,所述沟道部具有第二长度,所述第二长度与所述第一长度之比大于0.7,所述第二长度与所述第一长度之比小于或等于1。

9.优选的,所述导体部包括第一浓度区以及第二浓度区,所述第一浓度区位于所述导体部靠近所述沟道部的一侧,所述第二浓度区位于所述第一浓度区远离所述沟道部一侧;

10.其中,所述第一浓度区内的所述导体部的载流子浓度低于所述第二浓度区内的所述导体部的载流子浓度。

11.优选的,所述显示面板还包括位于所述第一栅极与所述半导体层之间的栅极绝缘层,所述栅极绝缘层包括位于所述第一栅极两侧的阻挡部;

12.其中,在所述显示面板的俯视方向上,所述阻挡部位于所述第一浓度区内。

13.优选的,所述阻挡部包括位于所述第一栅极一侧的第一阻挡子部以及相对设置于所述第一栅极另一侧的第二阻挡子部,在所述显示面板的俯视方向上,所述第一阻挡子部具有第三长度,所述第二阻挡子部具有第四长度;

14.其中,所述第三长度大于0.85微米,所述第三长度小于或等于1.8微米;

15.所述第四长度大于0.85微米,所述第四长度小于或等于1.8微米。

16.优选的,所述第三长度大于或等于1.2微米,所述第三长度小于或等于1.8微米;

17.所述第四长度大于或等于1.2微米,所述第四长度小于或等于1.8微米。

18.优选的,所述显示面板还包括层间绝缘层,所述层间绝缘层覆盖部分所述半导体层、所述阻挡部以及所述第一栅极;

19.其中,所述阻挡部内的离子浓度大于所述层间绝缘层内的离子浓度。

20.优选的,所述第二长度与所述第一长度之比大于或等于0.8,且所述第二长度与所述第一长度之比小于或等于1。

21.优选的,所述薄膜晶体管的阈值电压为-0.76v至0.22v。

22.本发明还提供一种显示装置,所述显示装置包括如任一上述的显示面板及装置主体,所述装置主体与所述显示面板组合为一体,

23.本发明还提供一种显示面板的制作方法,包括:

24.在衬底上形成半导体材料层;

25.在所述半导体材料层上形成阻挡材料层;

26.在所述阻挡材料层上形成第一金属层;

27.对所述第一金属层以及所述阻挡材料层进行图案化处理以形成第一栅极以及栅极绝缘层并使部分所述半导体材料层裸露;

28.对所述半导体材料层进行导体化处理以形成半导体层;

29.其中,所述半导体层包括沟道部、分别位于所述沟道部两侧的导体部;

30.所述沟道部在所述衬底上的正投影位于所述第一栅极在所述衬底上的正投影内,所述第一栅极具有第一长度,所述沟道部具有第二长度,所述第二长度与所述第一长度之比大于0.7,所述第二长度与所述第一长度之比小于或等于1。

31.本发明通过在显示面板的俯视方向上,控制沟道部的第二长度与第一栅极的第一长度之比大于0.7并且小于或等于1,使薄膜晶体管的阈值电压更接近于0,改善了薄膜晶体管由于阈值电压过于偏负造成的失效问题,提高了薄膜晶体管的器件性能。

附图说明

32.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅是本发明的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

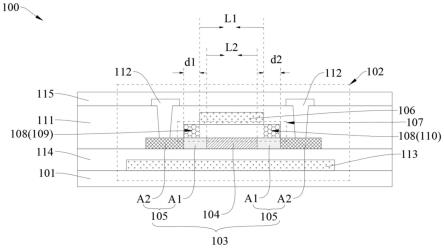

33.图1是本发明实施例提供的显示面板的第一种结构示意图;

34.图2是本发明实施例提供的显示面板的第二种结构示意图;

35.图3是本发明实施例提供的显示面板的第三种结构示意图;

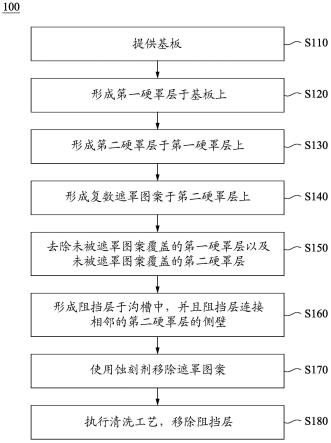

36.图4是本发明实施例提供的显示面板的制作方法的步骤流程图;

37.图5a至图5f是本发明实施例提供的显示面板制作方法的流程示意图;

38.图6是本发明实施例提供的显示装置的结构示意图。

具体实施方式

39.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完

整地描述,显然,所描述的实施例仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。此外,应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明,并不用于限制本发明。在本发明中,在未作相反说明的情况下,使用的方位词如“上”和“下”通常是指装置实际使用或工作状态下的上和下,具体为附图中的图面方向;而“内”和“外”则是针对装置的轮廓而言的。

40.目前,由于薄膜晶体管的半导体层中的导体部在制程中存在载流子向沟道部扩散,沟道部的实际长度远小于预期长度,导致薄膜晶体管阈值电压偏负,存在失效问题。

41.请参阅图1至图3,本发明实施例提供了一种显示面板100,包括衬底101以及位于所述衬底101上的多个薄膜晶体管102,所述薄膜晶体管102包括:

42.半导体层103,位于所述衬底101上,所述半导体层103包括沟道部104、位于所述沟道部104两侧的导体部105;

43.第一栅极106,位于所述半导体层103上;

44.其中,所述沟道部104在所述衬底101上的正投影位于所述第一栅极106在所述衬底101上的正投影内,所述第一栅极106具有第一长度l1,所述沟道部104具有第二长度l2,所述第二长度l2与所述第一长度l1之比大于0.7,所述第二长度l2与所述第一长度l1之比小于或等于1。

45.当所述第二长度l2与所述第一长度l1之比小于或等于0.7时,难以实际提升所述薄膜晶体管102的性能,改善所述薄膜晶体管102的失效问题;当所述第二长度l2与所述第一长度l1之比大于1时,易导致所述薄膜晶体管102的开关失控,影响所述薄膜晶体管102的产品质量。

46.所述显示面板100的俯视方向,为垂直于所述显示面板100的出光面、且与所述显示面板100的出光方向相逆的方向。

47.在所述显示面板100的俯视方向上,所述第一栅极106包括相对的第一侧以及第二侧,所述半导体层103包括平行于所述第一侧以及所述第二侧的第三侧以及第四侧,所述第一长度l1即为所述第一侧与所述第二侧之间的间距。其中,在所述显示面板100的俯视方向上,所述第一侧靠近所述第三侧,所述第二侧靠近所述第四侧。在所述显示面板100的俯视方向上,所述沟道部104包括靠近所述第三侧的第五侧,以及所述沟道部104包括靠近所述第四侧的第六侧,所述第二长度l2即为所述第五侧与所述第六侧之间的间距。

48.发明人经实验研究发现,实际形成的所述沟道部104的所述第二长度l2与所述第一栅极106的所述第一长度l1之比小于或等于0.7,导致所述薄膜晶体管的阈值电压偏负,所述薄膜晶体管易发生失效问题。例如,所述第二长度l2与所述第一长度l1之比在0.65至0.7时,在所述显示面板100制程中的显示母板进行不同点位的薄膜晶体管的阈值电压进行采样测量,发现:采样得到的薄膜晶体管的阈值电压在-19.7v至-3.7v之间,即,不同采样点获得的薄膜晶体管的阈值电压整体均偏负,且不同采样点之间的薄膜晶体管之间的阈值电压相差较大,不仅存在薄膜晶体管失效问题,还存在显示母板上的不同显示面板100之间产品质量难以控制的问题。

49.本发明通过在显示面板100的俯视方向上,控制沟道部104的第二长度l2与第一栅极106的第一长度l1之比大于0.7并且小于或等于1,使薄膜晶体管102的阈值电压更接近于

0,改善了薄膜晶体管102由于阈值电压过于偏负造成的失效问题,提高了薄膜晶体管的器件性能。

50.现结合具体实施例对本发明的技术方案进行描述。

51.请参阅图1至图3,本实施例中,所述导体部105包括第一浓度区a1以及第二浓度区a2,所述第一浓度区a1位于所述导体部105靠近所述沟道部104的一侧,所述第二浓度区a2位于所述第一浓度区a1远离所述沟道部104一侧;其中,所述第一浓度区a1内的所述导体部105的载流子浓度低于所述第二浓度区a2内的所述导体部105的载流子浓度。

52.通过降低靠近所述沟道部104的所述第一浓度区a1内的载流子浓度,有利于减少在半导体层103的导体化制程中从导体部105靠近沟道部104的区域向沟道部104的载流子扩散,减小实际形成的沟道部104的长度与预期的沟道部104的长度之间的长度差异,控制实际形成的所述沟道部104的所述第二长度l2与所述第一栅极106的第一长度l1之比大于0.7,小于或等于1,有利于改善薄膜晶体管102由于阈值电压过于偏负造成的失效问题,提高薄膜晶体管的器件性能。

53.请参阅图1,所述第二长度l2与所述第一长度l1之比可以为1。请参阅图2,所述第二长度l2与所述第一长度l1之比可以小于1,当所述第二长度l2与所述第一长度l1之比小于1时,所述第二长度l2与所述第一长度l1之比大于0.7且小于1。

54.在一些实施例中,所述第二长度l2与所述第一长度l1之比大于或等于0.8,所述第二长度l2与所述第一长度l1之比小于或等于1,优选的,所述第二长度l2与所述第一长度l1之比为0.8128至1。发明人经实验研究发现,所述第二长度l2与所述第一长度l1之比为0.8至1,优选的,所述第二长度l2与所述第一长度l1之比为0.8128至1时,所述薄膜晶体管102的阈值电压易于控制在趋近于0v的位置,有利于改善薄膜晶体管由于阈值电压过于偏负造成的失效问题,提高薄膜晶体管的器件性能。例如,当所述第二长度l2与所述第一长度l1之比为0.8128至1时,在所述显示面板100制程中的显示母板进行不同点位的薄膜晶体管的阈值电压进行采样测量,发现:采样得到的薄膜晶体管的阈值电压在-0.76v至0.22v之间,不同采样点获得的薄膜晶体管的阈值电压整体均趋近于0,且不同采样点之间的薄膜晶体管之间的阈值电压相差较小,不仅改善了薄膜晶体管的失效问题,还减小了显示母板上的不同显示面板100之间产品质量差异,提高了所述显示面板100的产品质量。

55.在所述显示面板100的俯视方向上,所述第一长度l1可以为8微米,所述第二长度l2可以为5.6微米至8微米,优选的,所述第二长度l2可以为6.4微米至8微米,进一步优选的,所述第二长度l2可以为6.5024微米至8微米。

56.在一些实施例中,所述显示面板100还包括位于所述第一栅极106与所述半导体层103之间的栅极绝缘层107,所述栅极绝缘层107包括位于所述第一栅极106两侧的阻挡部108;其中,在所述显示面板100的俯视方向上,所述阻挡部108位于所述第一浓度区a1内。

57.通过所述栅极绝缘层107的设置,在所述薄膜晶体管制程工艺中,所述阻挡部108在半导体层的导体化制程中对其下方对应的区域内的半导体层起到保护作用,避免该区域直接导体化,以使形成的所述第一浓度区a1内的导体部的载流子浓度小于所述第二浓度区a2内的载流子浓度,避免造成靠近所述沟道部104的所述导体部105的载流子浓度过高而向所述沟道部104扩散,造成在所述显示面板100的俯视方向上的所述沟道部104的长度小于预期长度,导致薄膜晶体管失效问题。

58.由于所述阻挡部108在半导体层的导体化制程中对所述第一浓度区a1的遮挡作用,在最终形成的所述显示面板100中,所述第一浓度区a1内的所述导体部105的载流子源于所述第二浓度区a2内的所述导体部105的载流子扩散作用,因此,所述第一浓度区a1内靠近所述第二浓度区a2一侧的所述导体部105的载流子浓度大于所述第一浓度区a1内靠近所述沟道部104一侧的所述导体部105的载流子浓度,有利于进一步减少在半导体层的导体化制程中从导体部105靠近沟道部的区域向沟道部的载流子扩散,减小实际形成的沟道部的长度与预期的沟道部的长度之间的长度差异,控制实际形成的所述沟道部104的所述第二长度l2与所述第一栅极106的第一长度l1之比大于0.7,且小于或等于1,有利于改善薄膜晶体管由于阈值电压过于偏负造成的失效问题,提高薄膜晶体管的器件性能。

59.所述栅极绝缘层107的材料可以为氧化硅或氮化硅,所述栅极绝缘层107的厚度优选为1000埃米至3000埃米,能在半导体层的导体化制程中有效阻挡所述导体部105对应区域的直接导体化。

60.在一些实施例中,所述阻挡部108包括位于所述第一栅极106一侧的第一阻挡子部109以及相对设置于所述第一栅极106另一侧的第二阻挡子部110,所述导体部105包括位于所述沟道部104一侧的第一导体子部以及相对设置于所述沟道部104另一侧的第二导体子部。

61.在所述显示面板100的俯视方向上,所述第一阻挡子部109位于所述第一导体子部的所述第一浓度区a1内,所述第二阻挡子部110位于所述第二导体子部的所述第一浓度区a1内。

62.在所述显示面板100的俯视方向上,所述第一阻挡子部109具有第三长度d1,所述第二阻挡子部110具有第四长度d2。

63.在所述显示面板100的俯视方向上,所述第一阻挡子部109包括靠近所述第一栅极106的第七侧以及远离所述第一栅极106的第八侧,所述第三长度d1即为所述第七侧与所述第八侧之间的间距;所述第二阻挡子部110包括靠近所述第一栅极106的第九侧以及远离所述第一栅极106的第十侧,所述第四长度d2即为所述第九侧与所述第十侧之间的间距。

64.通过对所述第三长度d1、所述第四长度d2的控制,控制所述第一浓度区a1的最终形成的长度,从而控制实际的所述沟道部104的所述第二长度l2。所述第三长度d1大于0.85微米,所述第三长度d1小于或等于1.8微米;所述第四长度d2大于0.85微米,所述第四长度d2小于或等于1.8微米。当所述第三长度d1和/或所述第四长度d2小于0.85微米时,所述第一阻挡子部109和/或所述第二阻挡子部110的长度过短,起到的阻挡效果较差,导致实际形成的所述沟道部104的长度较短,甚至与所述第一栅极106的长度的比值小于或等于0.7,难以实际提升所述薄膜晶体管102的性能;当所述第三长度d1和/或所述第四长度d2大于1.8微米时,所述第一阻挡子部109和/或所述第二阻挡子部110的长度过长,易导致实际形成的所述沟道部104的长度过长,甚至与所述第一栅极106的长度的比值大于1,易导致所述薄膜晶体管102的开关失控,影响所述薄膜晶体管102的产品质量。

65.具体的,发明人经实验发现,当所述第三长度d1以及所述第四长度d2小于或等于0.85微米时,由于所述第一阻挡子部109、所述第二阻挡子部110的长度过短,实际形成的所述沟道部104的所述第二长度l2与所述第一栅极106的所述第一长度l1之比小于或等于0.7,导致所述薄膜晶体管的阈值电压偏负,所述薄膜晶体管易发生失效问题。例如,所述第

三长度d1、所述第四长度d2为0.85微米时,所述第二长度l2与所述第一长度l1之比在0.65至0.7,在所述显示面板100制程中的显示母板进行不同点位的薄膜晶体管的阈值电压进行采样测量,发现:采样得到的薄膜晶体管的阈值电压在-19.7v至-3.7v之间,即,不同采样点获得的薄膜晶体管的阈值电压整体均偏负,且不同采样点之间的薄膜晶体管之间的阈值电压相差较大,不仅存在薄膜晶体管失效问题,还存在显示母板上的不同显示面板之间产品质量难以控制的问题。

66.同时,发明人经实验发现,所述第二浓度区a2内的载流子向所述第一浓度区a1扩散的距离有限,其扩散距离在1.2微米至1.8微米,通常为1.5微米,即,所述第一浓度区a1的长度在1.2微米至1.8微米,通常为1.5微米。当所述第三长度d1、所述第四长度d2与扩散距离相匹配,在1.2微米至1.8微米之间时,所述沟道部104的所述第二长度l2与所述第一栅极106的第一长度l1的比值为0.8至1,所述薄膜晶体管的阈值电压更趋近于0,所述薄膜晶体管的失效问题得到改善,且由于阈值电压更趋近于0,减小了所述薄膜晶体管的开关所需的功耗,有利于降低所述显示面板100的功耗,提高所述显示面板100的产品质量。例如,当所述第三长度d1、所述第四长度d2为1.4微米时,所述第二长度l2与所述第一长度l1之比在0.8至1,更具体的,所述第二长度l2与所述第一长度l1之比为0.812至1,在所述显示面板100制程中的显示母板进行不同点位的薄膜晶体管的阈值电压进行采样测量,发现:采样得到的薄膜晶体管的阈值电压在-0.76v至0.22v之间,不同采样点获得的薄膜晶体管的阈值电压整体均趋近于0,且不同采样点之间的薄膜晶体管之间的阈值电压相差较小,不仅改善了薄膜晶体管的失效问题,还减小了显示母板上的不同显示面板之间产品质量差异,提高了所述显示面板100的产品质量。

67.在一些实施例中,所述半导体层103还包括连接所述第三侧以及所述第四侧的第十一侧,所述第十一侧之间的间距为所述半导体层103的宽度,所述半导体层103的宽度可以为10微米。

68.在一些实施例中,所述薄膜晶体管102的类型为金属氧化物薄膜晶体管或者低温多晶硅薄膜晶体管。当所述薄膜晶体管102为金属氧化物薄膜晶体管时,所述半导体层103的材料可以包括igzo;当所述薄膜晶体管102为低温多晶硅薄膜晶体管时,所述半导体层103的材料可以包括多晶硅。所述半导体层103的厚度可以为200埃米至800埃米。

69.所述薄膜晶体管102的半导体层的导体化工艺制程可以通过等离子体工艺形成,等离子体可以为含cf4的等离子体或者含cf4以及o2等离子体;或者,等离子体为含p或含b的等离子体。当等离子体为含p或含b的等离子体时,所述显示面板100还包括层间绝缘层111,所述层间绝缘层111覆盖部分所述半导体层103、所述阻挡部108以及所述第一栅极106;其中,所述阻挡部108内的离子浓度大于所述层间绝缘层111内的离子浓度。

70.所述层间绝缘层111的材料可以为氧化硅或氮化硅,所述层间绝缘层111的厚度为2000埃米至8000埃米。同一所述显示面板100中,所述栅极绝缘层107的材料与所述层间绝缘层111的材料可以相同也可以不同。

71.所述薄膜晶体管102还包括位于所述半导体层103上的源漏极112,所述源漏极112通过贯穿所述层间绝缘层111的过孔与所述导体部105电连接。所述源漏极112包括源极以及漏极,所述源极以及所述漏极分别位于所述第一栅极106两侧,所述源极与所述第一导体子部连接,所述漏极与所述第二导体子部连接。所述源漏极112的材料可以包括mo、al、cu、

ti等金属或合金中的至少一种,所述源漏极112的厚度可以为2000埃米至80000埃米。

72.所述显示面板100还包括与所述第一栅极106同层设置的第一栅极106信号线,所述第一栅极106信号线包括扫描信号线。所述扫描信号线与所述第一栅极106连接以向所述第一栅极106提供扫描信号。所述第一栅极106的材料可以包括mo、al、cu、ti等金属或合金中的至少一种,所述第一栅极106的厚度可以为2000埃米至80000埃米。

73.所述显示面板100还包括与所述源漏极112同层设置的源漏极信号线,所述源漏极信号线包括数据信号线。所述数据信号线与所述源极或所述漏极连接以向所述源漏极112提供数据信号。在所述显示面板100的俯视方向上,所述扫描信号线与所述数据信号线相交。

74.所述显示面板100还包括位于所述源漏极112上的钝化层115,所述钝化层115的材料可以为氧化硅或氮化硅,所述钝化层115的厚度为1000埃米至5000埃米。

75.所述发光器件层还包括位于所述钝化层115上的发光器件层,所述发光器件层包括位于所述钝化层115上的阳极层、位于所述阳极层上的发光材料层及位于所述发光材料层上的阴极层。所述显示面板100包括显示区,所述阳极层包括位于所述显示区内的阳极,一所述阳极与所述显示区内的一所述薄膜晶体管的所述漏极或所述源极中不与所述数据信号线直接连接的一者相连接。

76.所述显示面板100还包括与所述发光材料层同层设置的像素定义层、位于所述发光器件层上的偏光层、位于所述偏光层上的盖板,所述显示面板100还包括位于所述偏光层与所述盖板之间对应粘结层。所述盖板可以为柔性盖板,所述柔性盖板的材料可以为聚酰亚胺。所述偏光层可以包括偏光片,或者,所述偏光层可以包括色阻以及位于所述色阻两侧的黑色矩阵。

77.在一些实施例中,所述薄膜晶体管102还包括位于所述衬底101与所述半导体层103之间的第二栅极113,在所述显示面板100的俯视方向上,所述半导体层103位于所述第二栅极113内,所述第二栅极113用于遮挡来自所述衬底101一侧的外界光线对所述半导体层103的干扰,有利于提升所述薄膜晶体管102的性能。所述第二栅极113可以包括mo、al、cu、ti等金属或合金中的至少一种,所述第二栅极113的厚度可以为2000埃米至80000埃米。

78.所述显示面板100还包括位于所述第二栅极113与所述半导体之间的缓冲层114,所述缓冲层114的材料可以为氧化硅或氮化硅,所述缓冲层114的厚度可以为5000埃米至10000米。

79.本发明实施例通过在所述显示面板100的俯视方向上,控制所述沟道部104的第二长度l2与所述第一栅极106的第一长度l1之比大于0.7并且小于或等于1,使所述薄膜晶体管102的阈值电压更接近于0,改善了所述薄膜晶体管102由于阈值电压过于偏负造成的失效问题,提高了所述薄膜晶体管的器件性能。

80.请参阅图1至图4,以及图5a至图5f,本发明实施例还提供了一种显示面板100的制作方法,包括:

81.请参阅图5a至图5b,s100、在衬底101上形成半导体材料层1031。

82.在一些实施例中,步骤s100包括:

83.s101、对所述衬底101进行清洗以及预烘烤。

84.s102、在所述衬底101上形成第二栅极113。

85.s103、在所述第二栅极113上形成第一材料层。

86.s104、对所述第一材料层进行图案化处理以形成所述半导体材料层。

87.其中,所述第二栅极113可以包括mo、al、cu、ti等金属或合金中的至少一种,所述第二栅极113的厚度可以为2000埃米至80000埃米。

88.请参阅图5c,s200、在所述半导体材料层1031上形成阻挡材料层1071。

89.在一些实施例中,步骤s200包括:

90.s201、在所述半导体材料层1031上整层覆盖阻挡材料以形成所述阻挡材料层1071。

91.请参阅图5c,s300、在所述阻挡材料层1071上形成第一金属层1061。

92.在一些实施例中,步骤s300包括:

93.s301、在所述阻挡材料层1071上整层覆盖第一金属以形成所述第一金属层1061。

94.请参阅图5d至图5e,s400、对所述第一金属层1061以及所述阻挡材料层1071进行图案化处理以形成第一栅极106以及栅极绝缘层107并使部分所述半导体材料层1031裸露。

95.在一些实施例中,步骤s400包括:

96.s401、对所述第一金属层1061进行第一图案化处理形成所述第一栅极106。

97.步骤s401包括:

98.s401a、在所述第一金属层1061上形成光阻层116。

99.所述光阻层116的材料为光阻材料,材料成分不是本发明的重点,不做具体限定。

100.s401b、利用图案化工艺,将所述光阻层116、所述第一金属层1061以及所述阻挡材料层1071形成第一图案,其中,所述光阻层形成图案化光阻,所述第一金属层1061形成所述第一栅极106。

101.步骤s401b中,所述图案化工艺包括对所述第一金属层1061进行刻蚀,采用的刻蚀工艺可以为湿法刻蚀。

102.当所述第一金属层1061通过湿法刻蚀形成所述第一栅极106时,由于存在过量刻蚀,所述第一图案中,所述图案化光阻在所述衬底101上的正投影覆盖所述第一栅极106在所述衬底上的正投影。同时,湿法刻蚀的过量刻蚀程度可以通过湿法刻蚀的刻蚀时间控制,因此,实际形成的所述第一栅极106的第一长度可控;所述图案化光阻具有与所述第一栅极106的所述第一长度l1对应的第五长度,所述第五长度可控且所述第五长度大于所述第一长度l1。

103.s402、对所述阻挡材料层1071进行第二图案化处理形成所述栅极绝缘层107并使部分所述半导体材料层1031裸露。

104.在一些实施例中,所述第二图案化处理包括对所述阻挡材料层1071进行干法刻蚀以形成所述栅极绝缘层107。

105.在一些实施例中,由于步骤s401b中的湿法刻蚀存在过刻导致所述图案化光阻的所述第五长度大于所述第一长度l1,因此,经干法刻蚀形成的所述栅极绝缘层在所述衬底101上的正投影覆盖所述第一栅极106在所述衬底101上的正投影。具体的,在所述显示面板100的俯视方向上,所述栅极绝缘层107超出所述第一栅极106的部分为阻挡部108,所述阻挡部108包括位于所述第一栅极106一侧的第一阻挡子部109以及相对设置于所述第一栅极106另一侧的第二阻挡子部110,在所述显示面板100的俯视方向上,所述第一阻挡子部109

具有第三长度d1,所述第二阻挡子部110具有第四长度d2。所述第三长度d1大于0.85微米,所述第三长度d1小于或等于1.8微米;所述第四长度d2大于0.85微米,所述第四长度d2小于或等于1.8微米。优选的,所述第三长度d1大于或等于1.2微米,所述第三长度d1小于或等于1.8微米;所述第四长度d2大于或等于1.2微米,所述第四长度d2小于或等于1.8微米。

106.在一些实施例中,所述第一栅极106的材料可以为igzo或者为多晶硅,所述半导体层103的厚度可以为200埃米至800埃米。

107.所述第一栅极106的材料可以包括mo、al、cu、ti等金属或合金中的至少一种,所述第一栅极106的厚度可以为2000埃米至80000埃米。所述栅极绝缘层107的材料可以为氧化硅或氮化硅,所述栅极绝缘层107的厚度优选为1000埃米至3000埃米。

108.在一些实施例中,步骤s400还包括:

109.s403、去除所述光阻层116。

110.请参阅图5f,s500、对所述半导体材料层1031进行导体化处理以形成半导体层103。

111.其中,所述半导体层103包括沟道部104、分别位于所述沟道部104两侧的导体部105。

112.所述沟道部104在所述衬底101上的正投影位于所述第一栅极106在所述衬底101上的正投影内,所述第一栅极106具有第一长度l1,所述沟道部104具有第二长度l2,所述第二长度l2与所述第一长度l1之比大于0.7,所述第二长度l2与所述第一长度l1之比小于或等于1。

113.在一些实施例中,步骤s500包括:

114.s501、利用等离子体工艺,对裸露的所述半导体材料层1031进行导体化以形成所述半导体层103。

115.本实施例中,利用等离子气体进行轰击降阻的工艺,例如可以是he、ar、cf4,或者,可以是he、ar、cf4、o2等,cf4或o2可以在最终的产品中测得所述半导体层103中的f含量或氧空穴含量,而对于he、ar,不易检测含量,故可以氧空位浓度作为不同区的区分。

116.所述导体部包括第一浓度区以及第二浓度区,所述第一浓度区位于所述导体部靠近所述沟道部的一侧,所述第二浓度区位于所述第一浓度区远离所述沟道部一侧;所述第一浓度区内的所述导体部的载流子浓度低于所述第二浓度区内的所述导体部的载流子浓度。

117.在一些实施例中,所述显示面板100的制作方法还包括:

118.s600、在所述半导体层103、所述栅极绝缘层107以及所述第一栅极106上形成层间绝缘层111,所述层间绝缘层111包括过孔,所述过孔使所述导体部105裸露。

119.所述层间绝缘层111的材料可以为氧化硅或氮化硅,所述层间绝缘层111的厚度为2000埃米至8000埃米。同一所述显示面板100中,所述栅极绝缘层107的材料与所述层间绝缘层111的材料可以相同也可以不同。

120.s700、在所述层间绝缘层111上形成源漏极112,所述源漏极112包括源极以及漏极。

121.所述源极以及所述漏极通过所述过孔与所述半导体层103连接。所述源漏极112的材料可以包括mo、al、cu、ti等金属或合金中的至少一种,所述源漏极112的厚度可以为2000

埃米至80000埃米。

122.s800、在所述源漏极112上形成钝化层115。

123.所述钝化层115的材料可以为氧化硅或氮化硅,所述钝化层115的厚度为1000埃米至5000埃米。

124.本发明提供的显示面板100的制作方法,通过在显示面板100的俯视方向上,控制沟道部104的第二长度l2与第一栅极106的第一长度l1之比大于0.7并且小于或等于1,使薄膜晶体管102的阈值电压更接近于0,改善了薄膜晶体管102由于阈值电压过于偏负造成的失效问题,提高了薄膜晶体管的器件性能。

125.请参阅图6,本发明实施例还提供了一种显示装置10,包括如任一上述的显示面板100及装置主体200,所述装置主体200与所述显示面板100组合为一体。

126.所述显示面板100的具体结构请参阅任一上述显示面板的实施例及附图,在此不再赘述。

127.本实施例中,所述装置主体200可以包括中框、框胶等,所述显示装置10可以为手机、平板、电视等显示终端,在此不做限定。

128.本发明实施例公开了一种显示面板及其制作方法、显示装置,该显示面板包括衬底以及位于该衬底上的多个薄膜晶体管,薄膜晶体管包括:该衬底上的半导体层,包括沟道部、位于该沟道部两侧的导体部,该半导体层上的第一栅极,该沟道部在该衬底上的正投影位于该第一栅极在该衬底上的正投影内,该第一栅极具有第一长度,该沟道部具有第二长度,第二长度与第一长度之比大于0.7,该第二长度与该第一长度之比小于或等于1,本发明通过在显示面板的俯视方向上,控制沟道部的第二长度与第一栅极的第一长度之比大于0.7并且小于或等于1,使薄膜晶体管的阈值电压更接近于0,改善了薄膜晶体管由于阈值电压过于偏负造成的失效问题,提高了薄膜晶体管的器件性能。

129.以上对本发明实施例所提供的一种显示面板及其制作方法、显示装置进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。