技术特征:

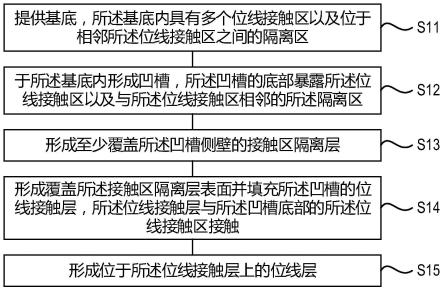

1.一种半导体结构,其特征在于,包括:衬底,包括多个分立的器件区和位于所述器件区之间的电源轨道区;凸起部,分立于所述器件区的衬底上;沟道结构,位于所述凸起部上;隔离层,位于所述衬底上且围绕所述凸起部且露出所述沟道结构;掩埋电源轨,贯穿于所述电源轨道区的隔离层和部分厚度衬底内,所述掩埋电源轨与凸起部之间平行间隔设置;栅极结构,位于所述隔离层上且横跨所述沟道结构;源漏掺杂区,位于所述栅极结构两侧的沟道结构中;层间介质层,位于所述栅极结构的侧部的隔离层上且覆盖所述源漏掺杂区;源漏互连层,贯穿所述源漏掺杂区和掩埋电源轨顶部上的所述层间介质层,所述源漏互连层与所述源漏掺杂区相接触,并且所述源漏互连层的底部与所述掩埋电源轨的顶面相接触。2.如权利要求1所述的半导体结构,其特征在于,所述掩埋电源轨的顶面与所述隔离层的顶面相齐平;或者,所述掩埋电源轨的顶面高于所述衬底的顶面,且低于所述隔离层的顶面;所述半导体结构还包括:覆盖介质层,位于所述隔离层中且位于所述掩埋电源轨顶面;所述源漏互连层贯穿所述源漏掺杂区顶部上的层间介质层,以及所述掩埋电源轨顶部上的覆盖介质层和所述层间介质层。3.如权利要求1或2所述的半导体结构,其特征在于,所述源漏互连层的底部与所述掩埋电源轨的顶面相齐平;或者,所述源漏互连层的底部低于所述掩埋电源轨的顶面,且高于所述衬底的顶面。4.如权利要求1所述的半导体结构,其特征在于,所述掩埋电源轨和沟道结构均沿横向延伸,与所述横向相垂直的方向为纵向;所述源漏互连层沿所述纵向延伸;所述半导体结构还包括:分割层,贯穿位于所述电源轨道区的部分源漏互连层,所述分割层沿纵向分割位于相邻器件区的所述源漏互连层。5.如权利要求4所述的半导体结构,其特征在于,位于所述分割层任意一侧的所述源漏互连层的底面与所述掩埋电源轨的顶面相接触;或者,位于所述分割层两侧的所述源漏互连层的底面均与所述掩埋电源轨的顶面相接触。6.如权利要求1所述的半导体结构,其特征在于,所述掩埋电源轨的顶面低于或齐平于隔离层的顶面;沿垂直于衬底表面的方向,所述掩埋电源轨的顶面与所述隔离层顶面之间的距离为0nm至15nm。7.如权利要求1所述的半导体结构,其特征在于,所述衬底的材料包括:单晶硅、锗、锗化硅、碳化硅、氮化镓、砷化镓和镓化铟中的一种或多种;所述凸起部和沟道结构的材料包括:单晶硅、锗、锗化硅、碳化硅、氮化镓、砷化镓和镓化铟中的一种或多种;所述掩埋电源轨的材料包括:co、w、ni和ru中的一种或多种。8.如权利要求2所述的半导体结构,其特征在于,所述半导体结构还包括:栅介质层,位于所述栅极结构与所述沟道结构之间、以及所述栅极结构与所述隔离层之间;所述掩埋电源轨的顶面与所述隔离层的顶面相齐平,所述栅介质层还位于所述掩埋电

源轨与所述栅极结构之间;或者,所述掩埋电源轨的顶面高于所述衬底的顶面,且低于所述隔离层的顶面;所述栅介质层还位于所述覆盖介质层与所述栅极结构之间。9.如权利要求8所述的半导体结构,其特征在于,所述栅介质层的材料包括:hfo2、zro2、hfsio、hfsion、hftao、hftio、hfzro、la2o3、al2o3、氧化硅和掺氮氧化硅中的一种或多种。10.如权利要求1所述的半导体结构,其特征在于,所述栅极结构的材料包括:tial、tialc、taaln、tialn、mon、tacn、aln、ta、tin、tan、tasin、tisin、w、co、al、cu、ag、au、pt和ni中的任意一种或多种;所述源漏互连层的材料包括:w、co、cu、ru以及ni中的一种或几种。11.如权利要求1所述的半导体结构,其特征在于,所述沟道结构为鳍部;所述栅极结构横跨所述鳍部且覆盖所述鳍部的部分顶部和部分侧壁;或者,所述沟道结构为沟道结构层,沟道结构层与凸起部之间间隔设置,沟道结构层包括一个或多个依次间隔设置的沟道层;所述栅极结构横跨所述沟道结构层且包围所述沟道层。12.一种半导体结构的形成方法,其特征在于,包括:提供衬底,包括多个分立的器件区和位于所述器件区之间的电源轨道区,所述器件区的衬底上形成有分立的凸起部,所述凸起部上形成有沟道结构,所述衬底上形成有围绕所述凸起部的隔离层,所述隔离层暴露出所述沟道结构,所述电源轨道区的隔离层和部分厚度衬底中形成有掩埋电源轨,所述掩埋电源轨与所述凸起部之间平行间隔设置;形成位于所述隔离层上且横跨所述沟道结构的栅极结构、位于所述栅极结构两侧的沟道结构中的源漏掺杂区,以及位于所述栅极结构侧部的隔离层上且覆盖所述源漏掺杂区的层间介质层;形成贯穿所述源漏掺杂区和掩埋电源轨顶部上的所述层间介质层的源漏互连层,所述源漏互连层与所述源漏掺杂区相接触,并且所述源漏互连层的底部与所述掩埋电源轨的顶面相接触。13.如权利要求12所述的半导体结构的形成方法,其特征在于,提供衬底的步骤中,所述掩埋电源轨的顶面与所述隔离层的顶面相齐平;或者,所述掩埋电源轨的顶面高于所述衬底的顶面,且低于所述隔离层的顶面,所述隔离层中还形成有位于所述掩埋电源轨顶面的覆盖介质层;在形成所述源漏互连层的步骤中,所述源漏互连层贯穿所述源漏掺杂区顶部上的层间介质层,以及所述掩埋电源轨顶部上的所述覆盖介质层和所述层间介质层。14.如权利要求12所述的半导体结构的形成方法,其特征在于,形成所述源漏互连层的步骤包括:形成贯穿所述源漏掺杂区和掩埋电源轨顶部上的所述层间介质层的源漏互连槽,所述源漏互连槽暴露出所述掩埋电源轨的顶面和源漏掺杂区;在所述源漏互连槽中填充所述源漏互连层。15.如权利要求14所述的半导体结构的形成方法,其特征在于,形成所述源漏互连槽的步骤包括:对所述源漏掺杂区和掩埋电源轨顶部上的层间介质层进行主刻蚀,形成初始互连槽,暴露出所述源漏掺杂区;对所述初始互连槽的底部进行过刻蚀,使所述初始互连槽暴露出所述掩埋电源轨的顶部,形成所述源漏互连槽。16.如权利要求14所述的半导体结构的形成方法,其特征在于,所述掩埋电源轨和沟道结构均沿横向延伸,与所述横向相垂直的方向为纵向;在形成所述源漏互连槽的步骤中,所述源漏互连槽沿所述纵向延伸,所述源漏互连槽中形成有凸出于源漏互连槽底部的分割

层,所述分割层沿所述纵向分割位于掩埋电源轨两侧的源漏互连槽;沿所述纵向,相邻所述器件区的所述源漏互连层由所述分割层隔离。17.如权利要求12所述的半导体结构的形成方法,其特征在于,所述半导体结构的形成方法还包括:在形成所述源漏互连层之后,形成贯穿位于相邻器件区之间的部分源漏互连层的分割层,所述分割层沿纵向分割位于相邻所述器件区的所述源漏互连层。18.如权利要求16或17所述的半导体结构的形成方法,其特征在于,位于所述分割层任意一侧的所述源漏互连层与所述掩埋电源轨相接触。19.如权利要求12所述的半导体结构的形成方法,其特征在于,所述源漏互连层的底部与所述掩埋电源轨的顶面相齐平;或者,所述源漏互连层的底部低于所述掩埋电源轨的顶面,且高于衬底的顶面。20.如权利要求12所述的半导体结构的形成方法,其特征在于,所述提供衬底的步骤包括:提供衬底、分立于器件区衬底上的凸起部、以及位于凸起部上的沟道结构;在所述衬底上形成围绕所述凸起部且覆盖所述沟道结构的隔离材料层;形成贯穿所述电源轨道区的所述隔离材料层以及部分厚度衬底的沟槽;在所述沟槽中形成所述掩埋电源轨,所述掩埋电源轨的顶面高于所述衬底的顶面且低于或齐平于所述凸起部的顶面;在所述掩埋电源轨上形成填充所述沟槽的介质材料层;当所述掩埋电源轨的顶面低于所述凸起部的顶面时,去除部分厚度的所述介质材料层以及所述隔离材料层,剩余的所述隔离材料层用于作为隔离层,剩余位于掩埋电源轨顶面上的介质材料层用于作为覆盖介质层;当所述掩埋电源轨的顶面齐平于所述凸起部的顶面时,去除高于所述掩埋电源轨顶面的介质材料层和隔离材料层,剩余的所述隔离材料层用于作为隔离层。

技术总结

一种半导体结构及其形成方法,半导体结构包括:凸起部,分立于器件区的衬底;沟道结构,位于凸起部上;隔离层,位于衬底上且围绕凸起部且露出沟道结构;掩埋电源轨,贯穿电源轨道区的隔离层和部分厚度衬底,掩埋电源轨与凸起部平行间隔设置;栅极结构,位于隔离层上且横跨沟道结构;源漏掺杂区,位于栅极结构两侧的沟道结构中;层间介质层,位于栅极结构侧部的隔离层上且覆盖源漏掺杂区;源漏互连层,贯穿源漏掺杂区和掩埋电源轨顶部上的层间介质层,源漏互连层与源漏掺杂区相接触,且源漏互连层的底部与掩埋电源轨的顶面相接触,从而源漏互连层与掩埋电源轨之间无需通过接触插塞(Via)实现电连接,优化源漏互连层和掩埋电源轨之间的电连接性能。的电连接性能。的电连接性能。

技术研发人员:金吉松

受保护的技术使用者:中芯国际集成电路制造(北京)有限公司

技术研发日:2021.06.02

技术公布日:2022/12/5

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。