半导体装置

1.相关申请的交叉引用

2.于2021年6月2日提交的包括说明书、附图和摘要的日本专利申请no.2021-093165的该公开内容通过引用全部并入本文。

背景技术:

3.本发明涉及一种半导体装置。

4.微控制器单元(mcu:微控制器单元)被应用于所有领域,例如被应用于应用程序领域。在许多情况下,mcu需要诸如数据传送和数据缩减等功能。例如,在数据传送和数据缩减被周期性地执行的情况下,需要执行数据传送和数据缩减,其中使所获得的数据可高速使用。

5.在mcu中,例如诸如cpu(中央处理单元)等处理器执行对诸如数据传送到主存储器(ram等)的控制。此处,假设存储在作为mcu中的外围功能而提供的寄存器中的数据被传送到主存储器。

6.cpu指明寄存器的预定地址,并且经由总线从所指明的地址读取数据作为传送数据。然后,cpu指定主存储器的任意地址,并且将所读取的数据写入到指定的地址。因此,cpu将数据从寄存器传送到主存储器。在所读取的数据被写入到主存储器之后执行。

7.此外,数据传送可以通过例如专利文献1所示的直接存储器访问dma控制器或专利文献2所示的数据传送控制器dtc控制器来执行。例如,dma/dtc控制器指定数据的数量、传送源地址(寄存器)、传送目的地地址(主存储器)、传送模式等,并且经由总线将数据从传送源地址(寄存器)传送到目的地地址(主存储器)。

8.下面列举了所公开的技术。

9.[专利文献1]日本未经审查的专利申请公告no.2020-107990

[0010]

[专利文献2]日本未经审查的专利申请公告no.1-125644

技术实现要素:

[0011]

然而,当cpu被使用时,须要为每次传送指定传送源地址和传送目的地地址。此外,由于cpu参与数据传送,所以数据传送时间变长。而且,在数据传送期间,cpu无法执行其他处理。

[0012]

另一方面,当dma/dtc被使用时,可以针对每个寄存器指定传送源地址和传送目的地地址。然而,由于在数据传送之后需要使用cpu来执行数据缩减,所以如果数据缩减的时间被包括在内,则处理时间可能比仅由cpu执行处理的时间长。

[0013]

本发明的目的是提供一种能够减少数据传送和数据组织所需时间的半导体装置。

[0014]

[用于解决问题的手段]

[0015]

本技术中公开的本发明中的代表性发明的发明内容将在下面简要描述。典型的固态装置包括处理器、存储器、外部接口、存储由外部接口接收的数据的寄存器、镜像寄存器缓冲器(mirror register buffer)以及耦合至处理器、存储器、外部接口、寄存器和镜像寄

存器缓冲器的内部总线。寄存器将数据输出到镜像寄存器缓冲器而不通过内部总线。镜像寄存器缓冲器将与分配给寄存器的地址不同的镜像寄存器缓冲器中的地址给与从寄存器输入的数据,并且将数据传送到存储器而不通过内部总线。

[0016]

如果简要描述由本技术中公开的本发明中的典型发明获得的效果,其可以缩短数据传送和数据组织所需的时间。

附图说明

[0017]

图1是示出了根据本发明的第一实施例的半导体装置的示例的框图。

[0018]

图2是具体图示了寄存器和存储在寄存器中的数据的配置的图。

[0019]

图3a是示出了根据本发明的第一实施例的镜像寄存器缓冲器的配置示例的框图。

[0020]

图3b是示出了图3a中的地址设置寄存器和中断设置寄存器的配置的图。

[0021]

图3c是图示了图3a的示例性操作的示意图。

[0022]

图4是图示了镜像寄存器缓冲器的数据传送的具体示例的图。

[0023]

图5a是具体图示了对应于图4的数据配置的图。

[0024]

图5b是具体图示了对应于图4的数据配置的图。

[0025]

图5c是具体图示了对应于图4的数据配置的图。

[0026]

图6a是用于解释数据布置的应用示例的图。

[0027]

图6b是用于解释数据布置的应用示例的图。

[0028]

图7是用于解释数据布置的另一应用示例的图。

[0029]

图8是用于解释数据布置的再一应用示例的图。

[0030]

图9a是示出了用于将本实施例和比较性示例进行对比的时序图的图。

[0031]

图9b是示出了用于将本实施例和比较性示例进行对比的时序图的图。

[0032]

图10a是用于关于功耗将本实施例和比较性示例进行对比的图。

[0033]

图10b是用于关于功耗将本实施例和比较性示例进行对比的图。

[0034]

图11是示出了根据本发明的第二实施例的镜像寄存器缓冲器的配置示例的图。

[0035]

图12是用于解释比较性示例中的数据传送和数据布置的图。

[0036]

图13a是具体图示了对应于图12的数据配置的图。

[0037]

图13b是具体图示了对应于图12的数据配置的图。

具体实施方式

[0038]

在下文中,将参照附图详细描述本发明的实施例。在用于解释实施例的所有附图中,相同的部分原则上由相同的附图标记表示,并且省略了其重复性描述。

[0039]

(第一实施例)

[0040]

《半导体装置的配置》

[0041]

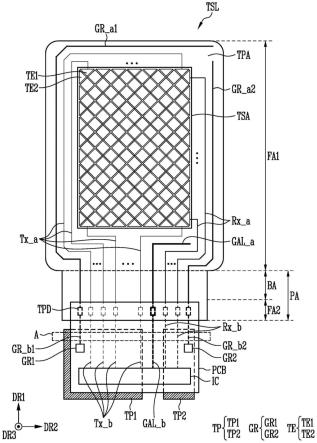

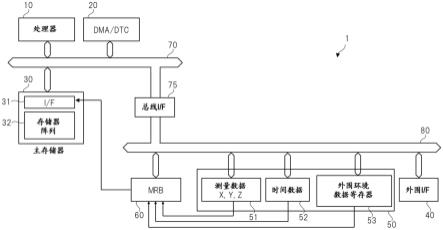

图1是示出了根据本发明的实施例1的半导体装置的示例的框图。如图1所示,半导体装置1包括处理器10、dma/dtc控制器20、主存储器30、外部接口40、寄存器组50、镜像寄存器缓冲器(mrb)60、第一内部总线70、总线接口75、第二内部总线80等。半导体装置1的示例是mcu等。

[0042]

处理器10是包括例如cpu的算术处理单元。处理器10例如通过第二内部总线80和

第一内部总线70从寄存器组50读取数据。处理器10通过第一内部总线70将所读取的数据写入到主存储器30。通过这种方式,处理器10将存储在寄存器组50中的数据传送到主存储器30。

[0043]

例如,处理器10读取并且执行包括存储在主存储器30中的各种程序和参数的各种种类的数据,以实现通过软件执行诸如数据传送的各种功能的功能块。处理器10可以实现其中硬件和软件协作的功能块,或者可以仅通过硬件来实现功能块的一部分。

[0044]

代替处理器10,dma/dtc控制器20经由第二内部总线80和第一内部总线70将数据从寄存器组50传送到主存储器30。

[0045]

主存储器30是易失性存储器,诸如例如sram(静态随机存取存储器)。主存储器30包括接口31和保存各种数据的存储器阵列32,如图1所示。接口31连接至第一内部总线70和镜像寄存器缓冲器60。处理器10、dma/dtc控制器20和镜像寄存器缓冲器60经由接口31访问主存储器30。

[0046]

主存储器30使用处理器10或dma/dtc控制器20作为主机,来保存通过总线(第二内部总线80和第一内部总线70)从寄存器组50或镜像寄存器缓冲器60传送的数据,并且寄存器组50的数据从镜像寄存器缓冲器60直接被写入而不通过总线。主存储器30保存各种数据,诸如处理器10的程序、参数和操作结果。

[0047]

半导体装置1可以包括存储装置(未示出)。存储装置的示例包括诸如闪存存储器和eeprom的非易失性存储器。根据诸如容量的条件适当地选择要被使用的非易失性存储器。当存储装置被提供时,用于操作半导体装置1的程序、参数等被存储在存储装置中。

[0048]

第一内部总线70耦合至处理器10、dma/dtc控制器20和主存储器30。第一内部总线70通过总线接口75连接至第二内部总线80。

[0049]

外部接口40、寄存器组50、镜像寄存器缓冲器60、第二内部总线80等构成半导体装置1中的外围功能。外部接口40、寄存器组50和镜像寄存器缓冲器60连接至第二内部总线80。如上所述,第二内部总线80通过总线接口75连接至第一内部总线70。

[0050]

外部接口40是用于向外部装置发送数据并且从外部装置接收数据的接口。外部接口40连接至外部装置,诸如例如测量装置或传感器。外部装置将所获取的测量数据发送到半导体装置1。外部接口40接收从外部装置发送的测量数据。外部接口40经由第二内部总线80将接收到的测量数据传送到寄存器组50的预定存储区域。

[0051]

寄存器组50例如是存储装置,其存储由外部接口40从外部装置接收的各种类型的数据,诸如测量数据、时间数据和外围环境数据。寄存器组50包括用于要被存储的每种类型的数据的不同寄存器。例如,寄存器组50包括用于存储测量数据的测量数据寄存器51、用于存储时间数据的时间数据寄存器52,诸如外围环境数据寄存器53的每个寄存器用于存储外围环境数据。数据经由第二内部总线80等被写入到每个寄存器和从每个寄存器被读取。

[0052]

如图1所示,寄存器组50的每个寄存器连接至镜像寄存器缓冲器60。每个寄存器与镜像寄存器之间的连接将在稍后详细描述。

[0053]

图2是具体图示了寄存器和存储在寄存器中的数据的配置的图。图2分别示出了测量数据寄存器51、时间数据寄存器52和存储在外围环境数据寄存器53中的数据。

[0054]

测量数据寄存器51存储例如多个测量装置x、y和z的测量数据,所有这些测量装置x、y和z都未示出。如图2所示,测量数据寄存器51存储测量装置x的测量数据(仪表(meter)x

[23:0])、测量装置y的测量数据(仪表y[23:0])和测量装置z的测量数据(仪表z[23:0])。

[0055]

例如[23:16]、[15:8]、[7:0]等这些测量数据被存储,以便能够读取划分的每个预定位数(例如8位、16位)。另外,每个测量仪器的测量数据是几乎同时测量的数据。尽管仅在特定时间测量的测量数据在图2中示出,但是在后续时间测量的测量数据可以被接连地存储。

[0056]

测量数据寄存器51可以包括分别对应于测量装置x、y和z的寄存器51a、51b和51c。在该实例中,寄存器51a存储测量装置x的测量数据(仪表x[23:0])。寄存器51b存储测量装置y的测量数据(仪表y[23:0])。寄存器51c存储测量装置z的测量数据(仪表z[23:0])。

[0057]

时间数据寄存器52将与存储在测量数据寄存器51中的测量数据相对应的测量时间存储为测量时间数据。在图2中,测量数据被显示为“日历”。测量时间可以是测量数据被接收的时间或测量数据被存储在测量数据寄存器51中的时间。时间数据寄存器52可以存储多个时钟数据。

[0058]

外围环境数据寄存器53存储外围环境数据。周围环境数据包括例如温度和湿度。环境数据寄存器53存储例如温度数据(温度)和湿度数据(湿度)。存储在外围环境数据寄存器53中的外围环境数据是指示在上述测量时间的温度和湿度的数据。

[0059]

外围环境数据寄存器53可以包括分别与温度数据和湿度数据相对应的外围环境寄存器53a和53b。外围环境寄存器53a存储温度数据。外围环境寄存器53b存储湿度数据。

[0060]

《《镜像寄存器缓冲器》》

[0061]

镜像寄存器缓冲器60是将连续地址添加到存储在寄存器组50中的数据并且将数据传送到主存储器30而不通过内部总线70的电路。存储在寄存器组50中的数据被寻址到寄存器或寄存器内的存储区域。然而,地址在寄存器之间或寄存器内可能不是连续的。因此,因为地址不是连续的,所以需要额外的处理来将数据传送到主存储器30,这增加了传送时间。如果数据的地址不是连续的,则数据必须被排序,以便数据可以被写入到连续地址。

[0062]

因此,在本实施例中,在镜像寄存器缓冲器60中,通过分组添加连续地址,以便减少数据传送和数据缩减所需的时间。此外,通过提供用于将被分组的数据传送到主存储器30的电路,数据可以从镜像寄存器缓冲器60直接被写入到主存储器30。

[0063]

图3a是示出了根据本公开的第一实施例的镜像寄存器缓冲器的示例性配置的框图。图3b是图示了图3a中的地址设置寄存器和中断设置寄存器的配置的图。图3a示出了包括镜像寄存器缓冲器60及其外围的配置。如附图3a所示,镜像寄存器缓冲器60包括多个地址分配电路65(65a0到65a2、

…

、65c0、

…

、65d、65e、65f)、数据输出控制电路64(64h、64l)、缓冲器电路66、中断设置寄存器68和数据写入控制电路69。

[0064]

提供与图2的寄存器组50中所包括的每个寄存器相对应的地址分配电路65。在该示例中,提供了与测量数据寄存器51a相对应的地址分配电路65a0至65a2,并且地址分配电路65a0至65a2被提供为分别与测量数据寄存器51a中所包括的8位单元中的三个寄存器51a0至51a2相对应。

[0065]

类似地,提供了与图2的测量数据寄存器51c相对应的地址分配电路65c0至65c2,并且地址分配电路65c0至65c2被提供为分别与测量数据寄存器51c中所包括的8位单元中的三个寄存器51c0至51c2相对应。注意,65c1、65c2、51c1和51c2的图示被省略。提供了分别与图2的外围环境寄存器53a、53b相对应的地址分配电路65d、65e。提供了与图2的时间数据

寄存器52相对应的地址分配电路65f。

[0066]

如图3a所示,每个地址分配电路65包括地址设置寄存器61、地址比较电路62、数据选择电路63h和63l。地址设置寄存器61包括例如触发器电路(flip-flop circuit)。如图3b所示,地址设置寄存器61设置有要被给与镜像寄存器的任何镜像寄存器地址madr,保存镜像寄存器地址madr。镜像寄存器是对对应寄存器进行镜像的寄存器,例如虚拟寄存器。作为示例,地址分配电路65d中所包括的镜像寄存器虚拟地对外围环境寄存器53a进行镜像。

[0067]

如图3b所示,在地址设置寄存器61中设置的镜像寄存器地址madr,例如组地址gadr被设置为高4位([7:4]),低4位([3:0])被设置为组中的连续地址。在这种情况下,可以执行16种分组,并且16个数据可以被指派给每个组。

[0068]

例如,如图3a所图示的,当外围环境寄存器53a和53b被设置在相同的组中时,相同的组地址gadr可以被设置为地址分配电路65d中的地址设置寄存器61的高4位和地址分配电路65e中的地址设置寄存器61的高4位。另外,“0x0”可以设置在地址分配电路65d中的地址设置寄存器61的低4位中,并且“0x1”可以设置在地址分配电路65e中的地址设置寄存器61的低4位中。即,地址设置寄存器61的低4位可以被设置为组中的连续地址。

[0069]

响应于外部事件,例如来自包括寄存器组50的测量电路的中断信号int,数据写入控制电路69基于中断设置寄存器68的设置内容,来控制到主存储器30的写入到目的地地址radr和写入数据wdt。外部事件除了包括中断的接收之外,还包括服务器日志数据的接收。

[0070]

中断设置寄存器68如图3b所示,设置到主存储器30的写入目的地地址,详细地,写入的开始地址(基础地址)radrb、组地址gadr、组中的数据数量num、中断数量intn和使能位en。在该示例中,基础地址radrb是16位,组地址gadr、数据数量num和中断数量intn分别是4位,并且使能位en是1位。

[0071]

当接收与中断数量intn相匹配的中断信号int时,数据写入控制电路69将基础地址radrb输出到主存储器30,并且将例如8位被选地址sadr输出到每个地址分配电路65。此时,数据写入控制电路69基于组地址gadr和中断设置寄存器68中的数据数量num顺序地确定被选地址sadr。

[0072]

更具体地,数据写入控制电路69将高4位设置为组地址gadr的设定值,并且输出被选地址sadr,同时顺序地递增低4位,直到达到数据数量num的设定值为止。响应于被选地址sadr的递增,数据写入控制电路69从基础地址radrb向主存储器30顺序地递增写入到目的地地址radr。

[0073]

在图3a中,写入目的地地址radr是字节地址,并且写入数据wdt是字(16位)单元。在这种情况下,基础地址radrb和写入目的地地址radr的最低有效位([0])被固定为“0”。数据写入控制电路69每隔输出被选地址sadr的一个循环,递增写入目的地地址radr的第二位([1])。

[0074]

写入数据wdt的数据宽度可以被适当地改变,例如32位或64位。例如,当写入数据wdt的数据宽度是双字(32位)时,基础地址radrb和写入目的地地址radr的低2位([0]、[1])被固定为“0”。此外,在图3a中,虽然详细示出一个中断设置寄存器68,但是其对应于多个事件,即,具有中断数量intn的中断信号int,也可以提供多个中断设置寄存器68。然后,针对多个中断设置寄存器68中的每个中断设置寄存器68,设置不同的可选组地址gadr和基础地址radrb。

[0075]

在图3a所图示的地址分配电路65中,地址比较电路62将由地址设置寄存器61保存的镜像寄存器地址madr和来自数据写入控制电路69的被选地址sadr进行比较。更具体地,地址比较电路62将例如镜像寄存器地址madr中的8位的高7位与被选地址sadr中的8位的高7位进行比较。当比较结果相匹配时,地址比较电路62输出“1”电平,并且当比较结果不匹配时,输出“0”电平。

[0076]

数据选择电路63h、63l包括例如三输入与门。来自地址比较电路62的输出和来自对应寄存器的8位数据d[7:0]作为三个输入中的两个输入被输入到数据选择电路63h和63l。镜像寄存器地址madr的最低有效位([0])的值作为三个输入中的剩余一个输入被输入到数据选择电路63h,并且最低有效位([0])的反相值被输入到数据选择电路63l。

[0077]

因此,当地址比较电路62的比较结果相匹配时,数据选择电路63h和63l基于镜像寄存器地址madr的最低有效位([0])的值来选择是将来自对应寄存器的8位数据d[7:0]输出到16位写入数据wdt的高8位还是低8位。具体地,当镜像寄存器地址madr的最低有效位([0])的值为“1”电平时,数据选择电路63h输出数据d[7:0],并且当最低有效位([0])的值为“0”电平时,数据选择电路63l输出数据d[7:0]。

[0078]

例如,假设相同的组a在地址分配电路65d和65e中的地址设置寄存器61中被设置,在地址分配电路65d中的组a中的地址被设置为“0x0”,并且在地址分配电路65e中的组a中的地址被设置为“0x1”。此外,作为被选地址sadr,假设输出组a和组a中的地址“0x0”。

[0079]

在这种情况下,地址分配电路65d中的数据选择电路63l输出外围环境寄存器53a的8位数据,并且并行地,地址分配电路65e中的数据选择电路63h输出外围环境寄存器53b的8位数据。如果输出“0x0”之后的被选地址sadr,则在最低有效位[0]根据字节数据和字数据之间的关系固定为“0”的假设下,被选地址sadr变为“0x2”。

[0080]

数据输出控制电路64h、64l包括例如或门。数据输出控制电路64h接收来自多个地址分配电路65中的高位侧的数据选择电路63h的输出,并且实质上,来自数据选择电路63h中的任何一个的输出被输出到后续级。另一方面,数据输出控制电路641来自多个地址分配电路65中的低位侧的数据选择电路631的输出,并且实质上,来自数据选择电路631中的任何一个的输出被输出到后续级。

[0081]

缓冲器电路66例如由触发器电路形成。缓冲器电路66锁存总共16位数据,其中来自数据输出控制电路64h的8位数据作为高位,并且来自数据输出控制电路641的8位数据作为低位。然后,响应于来自数据写入控制电路69的控制信号,缓冲器电路66将锁存的16位数据作为写入数据wdt输出到主存储器30。

[0082]

在与经由第一内部总线70的访问冲突的情况下,例如当从镜像寄存器缓冲器60到主存储器30的数据传送(即,传送数据的写入)被执行时,提供缓冲器电路66以暂时地保存传送数据。即,通过提供缓冲器电路66,可以使传送数据的写入计时偏移,并且可以执行经由总线对主存储器30的访问以及从镜像寄存器缓冲器60到主存储器30的数据传送。

[0083]

如上所述,地址分配电路65通过地址设置寄存器61,将从寄存器组50中的每个寄存器(例如外围环境寄存器53a等)输入的数据分配给不同于分配给该寄存器的地址的镜像寄存器缓冲器中的地址,即,镜像寄存器地址madr。镜像寄存器缓冲器60将从寄存器输入的数据传送到存储器30而不通过内部总线。因此,可以显著地减少数据传送时间。而且在该实施例中,如在常规情况下,数据可以经由总线从寄存器传送到主存储器30。

[0084]

图3c是图示了图3a的示例性操作的示意图。图3c示出了多个地址设置寄存器61a至61g、中断设置寄存器68、寄存器组50中的真实寄存器rreg、镜像寄存器mreg和主存储器30之间的关系的示例。为了便于解释,假设地址设置寄存器61和实际寄存器rreg中的每一个的数量均为7。

[0085]

地址设置寄存器61a-61g被包括在图3a所示的多个地址分配电路65的每个寻址电路系统65中。其中,例如“0x21”、“0x20”、“0x22”和“0x23”分别在地址设置寄存器61a、61b、61d、61e中设置。即,在地址设置寄存器61a、61b、61d、61e中设置相同的组地址“0x2”。

[0086]

实际寄存器rreg对应于图3a所示的测量电路系统中的多个寄存器。预定地址adr被预先分配给多个寄存器。其中,例如“0xf0400”、“0xf0401”、“0xf0600”和“0xf0601”分别被分配给寄存器“a”、“b”、“d”和“e”。即,寄存器“a”、“b”、“d”和“e”的地址adr可以包括不连续地址。

[0087]

地址设置寄存器61a、61b、61d、61e分别对应于寄存器“a”、“b”、“d”和“e”。因此,“0xf0721”、“0xf0720”、“0xf0722”和“0xf0723”作为镜像寄存器地址madr被分配给分别对应于寄存器“a”、“b”、“d”和“e”的镜像寄存器mreg“a”、“b”、“d”和“e”。顺便提及,镜像寄存器地址madr“0xf07”中的高12位的部分旨在预先固定,低8位的部分由地址设置寄存器61任意定义。

[0088]

例如,“0x8123-3050”在中断设置寄存器68中设置。在这种情况下,基础地址radrb是“0x3050”,组地址adr是“0x2”,组中的数据数量num是“3”,中断数量inin是“0x1”。对地址设置寄存器61a-61g和中断设置寄存器68的设置例如由处理器10等预先执行。

[0089]

当具有“0x1”的中断数量intn的中断信号int被生成时,数据写入控制电路69基于中断设置寄存器68输出被选地址sadr和写入目的地地址radr。在该示例中,为了方便起见,写入数据wdt的数据宽度应该是8位以便于图示。

[0090]

在这种情况下,基于组地址adr和组中的数据数量num,数据写入控制电路69在第一传送周期(第一)中的四个循环内按照该顺序输出被选地址sadr“0x20”、“0x21”、“0x22”和“0x23”。因此,在4个循环中,作为写入数据wdt,寄存器“b”、“a”、“d”和“e”的数据按顺序输出。

[0091]

在四个循环中,数据写入控制电路69基于基础地址radrb以该顺序输出写入目的地地址radr“0x3050”、“0x3051”、“0x3052”和“0x3053”。因此,寄存器“b”、“a”、“d”和“e”的数据被分别传送到主存储器30的写入目的地地址radr“0x3050”、“0x3051”、“0x3052”和“0x3053”。

[0092]

此后,当中断数量inin再次接收到“0x1”的中断信号int时,数据写入控制电路69以与第一传送循环(第一)的情况相同的方式,执行第二传送循环(第二)处理。在这种情况下,与第一传送循环(第一)的情况不同,数据写入控制电路69保存作为在第一传送循环(第一)中输出的最后写入目的地地址radr的“0x3053”,并且将下一地址“0x3054”设置为基础地址。

[0093]

通过这种方式,镜像寄存器缓冲器60通过给与相同的组地址gadr“0x2”和该组中的连续地址来对从多个寄存器“b”、“a”、“d”、“e”输入的多个数据进行分组。在这种情况下,分组之前的多个寄存器“b”、“a”、“d”和“e”的地址可以是不连续的。然后,镜像寄存器缓冲器60,例如当中断信号int被生成时,外部事件选择对应于该外部事件的组(组地址gadr“0x2”组),并且将属于所选组的数据传送到主存储器30。

[0094]

《《镜像寄存器缓冲器操作》》

[0095]

此处,由镜像寄存器缓冲器60进行数据传送的具体示例。图4是用于解释由镜像寄存器缓冲器进行的数据传送的具体示例的图。图5是具体示出了对应于图4的数据结构的图。图5a是示出了在数据缩减之前存储在每个寄存器中的数据的图。图5b是示出了通过分组组织的数据结构的图。图5(c)是示出了在传送到主存储器30之后的传送数据的数据配置的图。

[0096]

首先,测量装置x、y和z的测量数据(仪表x、仪表y、仪表z)、计时数据(日历)、温度数据(温度)和湿度数据(湿度)被存储在相应寄存器中。存储在寄存器中的数据被给与针对每个寄存器的预定地址(图5a)。

[0097]

然后,镜像寄存器缓冲器60例如对这些数据进行分组(图5b)。具体地,镜像寄存器缓冲器60与要被分组的数据具有相同的组地址,并且通过给与该组中的连续地址来执行分组。即,在与要被分组的数据相对应的地址设置寄存器61中设置相同组地址和该组中的连续镜像寄存器地址。此外,在图5b中,“0xf300”被固定设置为这些镜像寄存器的开始地址(基础地址)。

[0098]

在图5b的情况下,测量数据(仪表x)和计时数据(日历)被首先传送。接下来,测量数据(仪表y)和温度数据(温度)被传送。接下来,测量数据(仪表z)和湿度数据(湿度)被传送。

[0099]

具体地,测量数据(仪表x)被写入地址(1)(基础地址),时钟数据(日历)被写入地址(1)和连续地址(2)(图4)。因此,测量数据(仪表x)和计时数据(日历)被连续地写入主存储器30(图5c)。

[0100]

接下来,测量数据(仪表y)被写入地址(2)和连续地址(3),温度数据(温度)被写入地址(3)和连续地址(4)(图4)。因此,测量数据(仪表x)、计时数据(日历)、测量数据(仪表y)和温度数据(温度)被连续地写入主存储器30(图5c)。

[0101]

测量数据(仪表z)被写入地址(4)和连续地址(5),湿度数据(湿度)被写入地址(5)和连续地址(6)(图4)。因此,测量数据(仪表x)、时间测量数据(日历)、测量数据(仪表y)、温度数据(温度)、测量数据(仪表z)和湿度数据(湿度)被连续地写入主存储器30(图5c)。

[0102]

通过重复这些操作,镜像寄存器缓冲器60将在不同时间测量的测量数据等连续地写入主存储器30中作为传送数据(图5c)。

[0103]

《《数据缩减的应用示例1》》

[0104]

接下来,将描述数据缩减的应用示例。图6是用于解释数据缩减的应用示例的图。图6a和图6b例示了具有不同引脚数量的mcu中的数据组织方法。图6中的pl0、pl1指示用于存储每个引脚的数据的寄存器(端口锁存寄存器)。例如,分别地,pl0是存储端口0的数据的寄存器,并且pl1是存储端口1的数据的寄存器。

[0105]

在图6a和图6b中,示出了组织连续端口的数据的方法。连续端口寄存器的地址是连续的,但是因为一些位被禁用,所以地址作为数据不是连续的。因此,在图6a的示例中,镜像寄存器缓冲器60,4个数据端口被概括为两次传送数据。此外,在图6b的示例中,镜像寄存器缓冲器60,4个数据端口被概括为一次传送数据。

[0106]

《《数据缩减的应用示例2》》

[0107]

图7是图示了数据缩减的另一应用示例的图。在图7中,示出了用于组织多个非连续端口的数据的方法。如图7所示,端口0和端口5寄存器的地址是不连续的。即,分组之前的多个数据的寄存器的地址是不连续的。因此,镜像寄存器缓冲器60共同生成传送数据,并且端口5的数据和端口0的数据彼此分离。

[0108]

《《数据缩减的应用示例3》》

[0109]

图8是用于解释数据缩减的再一应用示例的图。此处,示出了用户灵活地组织数据的情况。在图8中,地址f0400、f0500、f0600、f0601的数据被概括为传送数据。地址f0700-f0703被分配给要传送数据的概括数据。因此,通过将远程地址的数据分配给相邻地址,这些数据将被写入到连续地址,并且促进数据缩减。

[0110]

《本实施例的主要效果》

[0111]

根据本实施例,镜像寄存器缓冲器60将分配给该寄存器的地址之外的另一镜像寄存器缓冲器中的地址给与该寄存器中的数据,并且将该地址所给与的数据作为传送数据,从镜像寄存器缓冲器60直接写入到主存储器30。此时,镜像寄存器缓冲器60将被分组的数据写入到主存储器30中的连续地址。根据该配置,可以在短时间内执行从寄存器到主存储器30的数据传送和数据缩减。

[0112]

另外,由于数据被写入到连续地址,所以可以有效地执行数据处理。

[0113]

[比较性示例]

[0114]

此处,示出了相对于本实施例的比较性示例。比较性示例将与上述图4和图5a至图5c进行比较来描述。

[0115]

图12是用于解释比较性示例中的数据传送和数据缩减的图。图13a和图13b是具体示出了对应于图12的数据结构的图。图13a是示出了在数据缩减之前写入到主存储器的数据配置的图。图13b是示出了在数据被组织之后的数据结构的图。

[0116]

在比较性示例中,如图12所示,数据由dma/dtc控制器20从寄存器传送到主存储器。dma/dtc控制器20读取测量数据(仪表x),将测量数据(仪表x)的传送目的地地址设置为地址(1),并且传送到主存储器。接下来,dma/dtc控制器20读取测量数据(仪表y),将测量数据(仪表y)的传送目的地地址设置为地址(2),并且传送到主存储器。然后,dma/dtc控制器20读取出测量数据(仪表z),将测量数据(仪表z)的传送目的地地址设置为地址(3),并且将其传送到主存储器(图12、图13a)。

[0117]

类似地,dma/dtc控制器20分别将温度数据(温度)传送到地址(4),将湿度数据(湿度)传送到地址(5),并且将计时数据(日历)传送到地址(6)(图12和图13a)。

[0118]

处理器从主存储器读取数据,组织所读取的数据,并且将所组织的数据写入到主存储器(图12和图13b)。

[0119]

如上所述,在比较性示例中,数据从寄存器被传送到主存储器,数据从存储器被读取,数据被重新组织,并且数据被写入到存储器,使得数据传送和数据缩减花费较长时间。

[0120]

《本实施例和比较性示例之间的比较》

[0121]

图9是示出了将本实施例和比较性示例进行比较的时序图。图9a是用于在数据传送被执行一次的情况下将本实施例与比较性示例进行比较的时序图。图9b是用于在数据传送被连续执行两次的情况下将本实施例与比较性示例进行比较的时序图。

[0122]

在图9a中,当在dtc控制器中传送数据时,从激活请求到第五时钟执行命令处理。

然后,数据在第六时钟中从寄存器被读取,数据在第七时钟中被写入到主存储器。然后,在第八时钟中执行回写。然后,dtc控制器的操作结束。

[0123]

在图9a中,当数据由dma控制器传送时,在第一时钟中执行总线判优(bus arbitration)的命令处理。然后,数据在第二时钟中被读取,数据被在第三时钟中被写入到主存储器。然后,dma控制器的操作结束。

[0124]

在图9a中,当在镜像寄存器缓冲器60中传送数据时,在第一时钟中执行总线判优的命令处理。然后,在第二时钟中,数据由镜像寄存器缓冲器60被写入到主存储器。然后,镜像寄存器缓冲器60的操作完成。

[0125]

比较它们,当使用dtc控制器时,数据传送花费最多时间。此外,当使用dma控制器时,数据传送时间与使用镜像寄存器缓冲器60的情况仅有一个时钟不同。然而,即使使用dma控制器执行数据传送,也有必要由处理器执行数据缩减。因此,考虑到直到数据缩减结束的时间,本实施例使用镜像寄存器缓冲器60,可以在非常短的时间内结束处理。

[0126]

在图9b的示例中,数据传送所需的时间差被进一步扩展。当使用镜像寄存器缓冲器60时,可以并行传送多个数据,数据传送时间与图9a中的相同。而且,dma控制器无法执行连续的数据传送。

[0127]

图10是示出了关于功耗的本实施例和比较性示例之间的比较的图。图10a示出了的处理器的操作和功耗的比较。图10a图示了间歇操作。图10b通过比较本实施例和比较性示例示出了图10a中的功耗。

[0128]

在间歇操作中,处理器的操作模式在正常模式、停止模式和睡眠模式之间切换。睡眠模式是处理器未被使用而仅外围功能被操作的模式。

[0129]

在使用镜像寄存器缓冲器60的该实施例中,在待机释放之后,数据传送以睡眠模式执行。然而,当cpu被使用时,因为数据传送无法在睡眠模式下执行,所以数据传送在正常模式下执行。此外,当使用cpu时,数据传送时间最长。

[0130]

因此,如图10b所示,数据传送所需的功耗在本实施例中是最低的,并且在使用cpu的情况下是最高的。图10b是r78架构的估计。如上所述,从功耗的观点来看,本实施例比现有技术更有效。

[0131]

(第二实施例)

[0132]

接下来,第二实施例将被描述。如先前提及的,镜像寄存器缓冲器可以对寄存器中的数据进行分组来组织数据。在第一实施例中,数据直接从镜像寄存器缓冲器传送到主存储器30而不通过总线,但是在本实施例中,响应于来自处理器10或dma/dtc控制器20的访问,来自镜像寄存器缓冲器的数据被输出到总线。

[0133]

图11是示出了根据本发明的第二实施例的镜像寄存器缓冲器的配置示例的图。图11的镜像寄存器缓冲器160,在该配置中,从图3的镜像寄存器缓冲器60中删除了缓冲器电路66、中断设置寄存器68和数据写入控制电路69。

[0134]

例如,从处理器10或dma/dtc控制器20访问镜像寄存器缓冲器160,并且来自处理器10或dma/dtc控制器20的被选地址sadr通过第二内部总线80输入。任何镜像寄存器地址madr被预先设置在多个地址分配电路65中的地址设置寄存器61中,以便便于数据传送、数据组织等。

[0135]

镜像寄存器缓冲器160将由地址设置寄存器61保存的镜像寄存器地址madr与通过

相应地址分配电路65中的总线输入的被选地址sadr进行比较。然后,数据从对应于地址分配电路65的寄存器输出,在地址分配电路65的寄存器中镜像寄存器地址madr和被选地址sadr彼此重合。输出数据可以经由第二内部总线80传送到各个位置。即,传送目的地不限于主存储器30。

[0136]

根据该实施例,所组织的数据从镜像寄存器缓冲器160输出到总线。根据该配置,即使在处理器10或dma/dtc控制器20等被使用时,也可以减少数据传送和数据缩减所需的时间。

[0137]

尽管本发明人做出的本发明已经基于实施例进行了具体描述,但是本发明不限于上述实施例,并且不言而喻,在不脱离其要旨的情况下,可以进行各种修改。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。