1.本公开涉及一种显示面板,特别涉及一种适用于任意裁切比例的显示面板。

背景技术:

2.在一些实施例中,在大玻璃基板上制作相同尺寸的像素、栅极驱动器以及相应的走线后,将大玻璃基板进行切割可得到一或多个面板。

3.为了独立驱动自大玻璃基板裁切出的面板,会须要在大玻璃基板上设置对应数量的栅极驱动器,而使裁切出的一或多个面板均可独立运行。并且,各个栅极驱动器所包含的栅极驱动电路的数量通常会依据大玻璃基板于垂直方向上的像素数量决定,驱动芯片的数量会依据大玻璃基板于水平方向上的像素数量决定。

4.然而,若栅极驱动器的数量与驱动芯片的数量不成比例,会造成扇出型封装对接的问题。再者,若栅极驱动器中的驱动电路的数量与驱动芯片的数量不成比例,亦会造成扇出型封装对接的问题。因此,如何提供一种显示面板以解决上述问题为本领域中重要的议题。

技术实现要素:

5.本公开文件提供一种显示面板。显示面板包含像素阵列以及栅极驱动器。像素阵列包含y条栅极线以及多个条辅助栅极线。像素阵列的规格是x*y个像素。像素阵列包含y条栅极线以及多个条辅助栅极线。该些条辅助栅极线中的一部分电性耦接该y条栅极线,并且该些条辅助栅极线中的另一部分与该些条栅极线电性隔绝。栅极驱动器包含(y z)个栅极驱动电路,并且该(y z)个栅极驱动电路分别对应于该些条辅助栅极线,其中所述z为正整数。

6.综上所述,本公开文件提供的显示面板包含多余的栅极驱动电路,从而改善与驱动芯片之间对接的问题。并且,多余的栅极驱动电路会具有相应的辅助栅极线。因此,本公开文件的显示面板中多余的垂直辅助栅极线与水平的栅极线电性绝缘,进一步降低多余走线对像素阵列的影响。

附图说明

7.为使本公开的上述和其他目的、特征、优点与实施例能更明显易懂,说明书附图的说明如下:

8.图1a为依据本公开文件的一些实施例所示出的显示面板的示意图。

9.图1b为依据本公开文件的一些实施例所示出的栅极驱动器的示意图。

10.图2为依据本公开文件的一些实施例所示出的栅极驱动电路以及驱动芯片与辅助栅极线、栅极线、信号线以及数据线组的电路布局的示意图。

11.图3为依据本公开文件的一些实施例所示出的栅极驱动电路与辅助栅极线、栅极线以及信号线的电路布局的示意图。

12.图4为依据本公开文件的一些实施例所示出的栅极驱动电路的电路架构的示意图。

13.图5为依据本公开文件的一些实施例所示出的栅极驱动电路的电路架构的示意图。

14.图6为依据本公开文件的一些实施例所示出的栅极驱动电路与辅助栅极线、栅极线以及信号线的电路布局的示意图。

15.图7为依据本公开文件的一些实施例所示出的栅极驱动电路与辅助栅极线、栅极线以及信号线的电路布局的示意图。

16.附图标记说明:

17.为使本公开的上述和其他目的、特征、优点与实施例能更明显易懂,所附符号的说明如下:

18.30:通孔

19.31,32,33,34:走线

20.100:显示面板

21.110:基板

22.112,114,116:栅极驱动器

23.122,124,126:驱动芯片组

24.130:像素阵列

25.410,510:上拉控制电路

26.420,520:上拉电路

27.430,440,530,540:下拉电路

28.450,460,550,560:下拉控制电路

29.goa,goar,goa(n),goar(n):栅极驱动电路

30.cof:驱动芯片

31.g1,g2~gy-1,gy:栅极线

32.vg1,vg2~vgy-1,vgy,vgp-1,vgp:辅助栅极线

33.aa:显示区域

34.d1~db,db~dq:数据线组

35.d11~d13,d21~d23:数据线

36.busl1,busl2,dc:信号线

37.hc1,hc2,hc7:时钟信号

38.t11,t12,t21,t32~t35,t41~t44,t51~t56,t61~t66:晶体管

39.lc1,lc2:低频时钟信号

40.q(n):操作节点

41.p(n),k(n):稳压节点

42.vss,vssq:系统低电压端

43.q(n-6),q(n-2),st,s(n 6),s(n):控制信号

44.vf:电位

45.g(n):栅极控置信号

46.sv(n):稳压信号

47.r,g,b:子像素

48.pix:像素

具体实施方式

49.下列是举实施例配合所附图示做详细说明,但所提供的实施例并非用以限制本公开所涵盖的范围,而结构运行的描述非用以限制其执行顺序,任何由元件重新组合的结构,所产生具有均等技术效果的装置,皆为本公开所涵盖的范围。另外,图示仅以说明为目的,并未依照原尺寸作图。为使便于理解,下述说明中相同元件或相似元件将以相同的符号标示来说明。

50.在全篇说明书与权利要求所使用的用词(terms),除有特别注明除外,通常具有每个用词使用在此领域中、在此公开的内容中与特殊内容中的平常意义。

51.此外,在本文中所使用的用词“包含”、“包括”、“具有”、“含有”等等,均为开放性的用语,即意指“包含但不限于”。此外,本文中所使用的“及/或”,包含相关列举项目中一或多个项目的任意一个以及其所有组合。

52.于本文中,当一元件被称为“耦接”或“耦接”时,可指“电性耦接”或“电性耦接”。“耦接”或“耦接”亦可用以表示二或多个元件间相互搭配操作或互动。此外,虽然本文中使用“第一”、“第二”、

…

等用语描述不同元件,该用语仅是用以区别以相同技术用语描述的元件或操作。

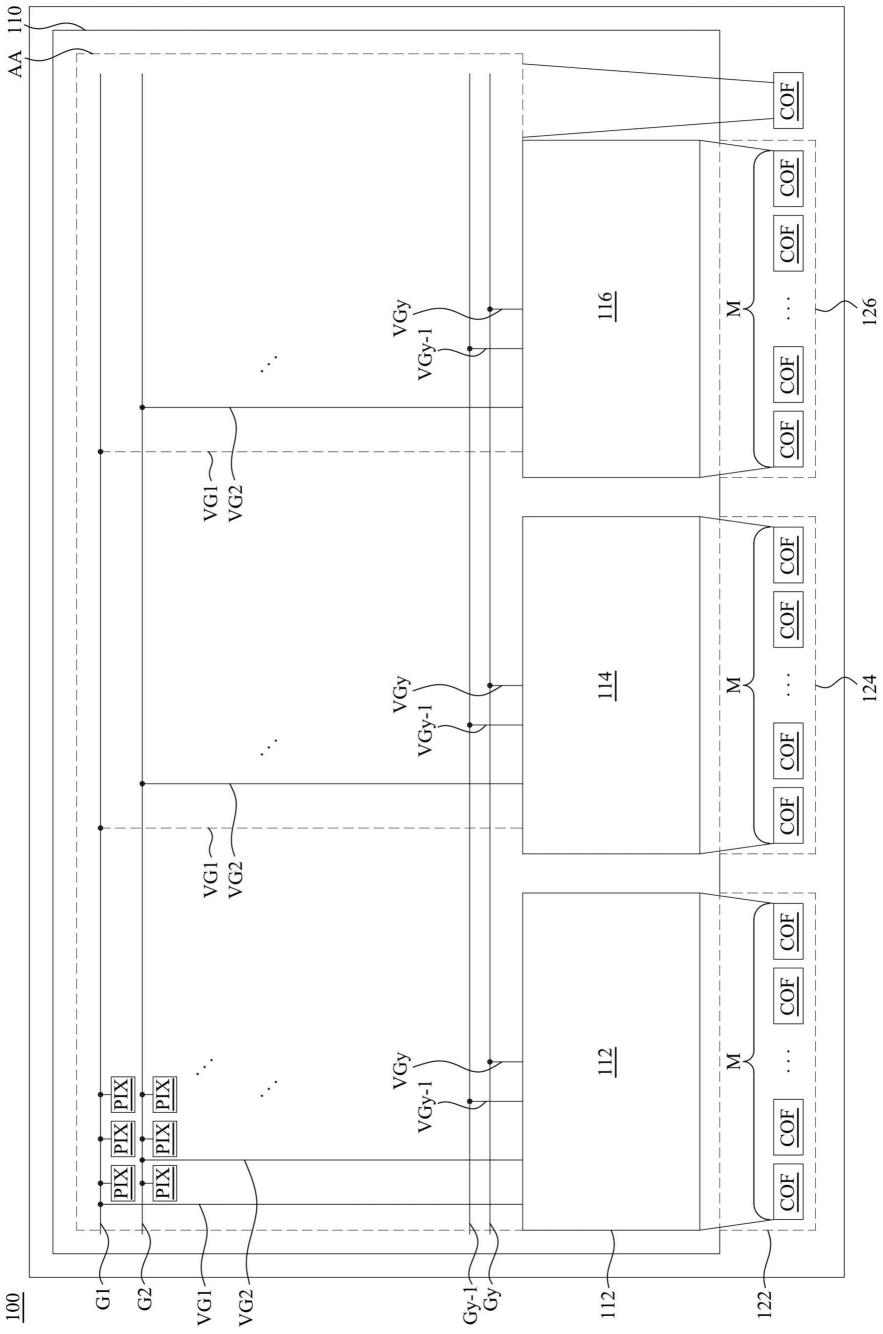

53.请参阅图1a,图1a为依据本公开文件的一些实施例所示出的显示面板100的示意图。如图1a所示,显示面板100包含基板110、像素阵列130、栅极驱动器112、114以及116以及驱动芯片组122、124以及126。在一些实施例中,基板110可由玻璃基板实施。像素阵列130以及栅极驱动器112、114以及116经设置于基板110上,并且像素阵列130经设置于基板110上的显示区域aa。

54.为了减少显示面板中左右边框的宽度,辅助栅极线vg1~vgy会自驱动芯片组122、124以及126于显示面板100中的一侧(例如,上/下侧)延伸,使设置于显示面板100中与驱动芯片组122、124以及126位于相同侧的栅极驱动器112、114以及116经由垂直的辅助栅极线vg1~vgy相应连接至水平栅极线g1~gy。水平栅极线g1~gy中每一者电性耦接像素阵列130中位于同一列的像素pix,使栅极驱动器112、114以及116中至少一者经由辅助栅极线vg1~vgy中的对应者传送相应的栅极控制信号至水平栅极线g1~gy。

55.在本公开的实施例中,为了扇出型封装的完整对接,会依据栅极驱动器的数量(例如,3个栅极驱动器112、114以及116)将部分的驱动芯片cof划分为群(例如,3组驱动芯片组122、124以及126),以分别对应各个栅极驱动器,并将剩余的驱动芯片cof作为不须对接栅极驱动器的数据驱动芯片实施。

56.举例而言,若显示面板100共需16个驱动芯片cof以驱动16*256个通道(像素行),由于16个驱动芯片cof无法平均的对应于3个栅极驱动器112、114以及116。因此,将15个驱动芯片cof分为3组驱动芯片组122、124以及126,从而分别对应至3个栅极驱动器112、114以及116。并且,剩余的第16个驱动芯片cof为不须对接栅极驱动器的数据驱动芯片。

57.请参阅图1a以及图1b,图1b为依据本公开文件的一些实施例所示出的栅极驱动器

112的示意图。如图1b所示,栅极驱动器112包含驱动电路goa以及goar。

58.栅极驱动器112的栅极驱动电路goa以及goar的总数会依据前述驱动芯片组122包含的驱动芯片cof数量决定,使栅极驱动器112中的驱动电路goa以及goar的数量为驱动芯片组122包含的驱动芯片cof的数量的倍数,而使栅极驱动器112与相应的驱动芯片组122所包含的驱动芯片cof之间的扇出型封装可完整对接。

59.在这样的架构下,栅极驱动电路goa以及goar的总数会大于像素阵列130所包含的像素列/栅极线的数量。因此,栅极驱动器112中的y个栅极驱动电路goa分别经由辅助栅极线vg1~vgy电性耦接相应的栅极线g1~gy,并且栅极驱动器112中的z个栅极驱动电路goar可以由剩余栅极驱动电路理解。如何配置剩余栅极驱动电路goar及其相关布局将于后续实施例中详细说明。

60.具体而言,假设像素阵列130于水平方向上具有x个像素,于垂直方向上具有y个像素,其规格为x*y个像素。像素阵列130会包含y条栅极线g1~gy,栅极线g1~gy分别经由辅助栅极线vg1~vgy与相应的y个栅极驱动电路goa电性耦接。

61.栅极驱动器112所包含的y个栅极驱动电路goa以及z个栅极驱动电路goar的总数“(y z)”会由前述驱动芯片组122中的m个驱动芯片cof的数量“m”的倍数实施。换言之,所述“m”为所述“(y z)”的因数。并且,所述“m”、“y”以及“z”皆为正整数。

62.如此,栅极驱动器112中的栅极驱动电路goa以及goar会平均的对应/分配至驱动芯片组122中的驱动芯片cof,而使栅极驱动器112所包含的栅极驱动电路goa以及goar与驱动芯片组122所包含的驱动芯片cof之间扇出型封装可以完整对接。

63.栅极驱动器114以及116的架构大致上类似/相似于栅极驱动器112。栅极驱动器114以及116所包含的栅极驱动电路亦可平均的对应/分配至驱动芯片组124以及126中的驱动芯片cof,栅极驱动器114以及116各自的栅极驱动电路与驱动芯片组124以及126所包含的驱动芯片cof的对应关系类似于栅极驱动器112所包含的栅极驱动电路goa以及goar与驱动芯片组122所包含的驱动芯片cof的对应关系,故在此不再赘述。

64.在一些实施例中,栅极驱动电路goar用以提供稳压信号。在另一些实施例中,栅极驱动电路goar与像素阵列130电性隔绝。栅极驱动电路goar与像素阵列130的布局及其作动方式将于后续实施例中详细说明。

65.请参阅图2,图2为依据本公开文件的一些实施例所示出的栅极驱动电路goa以及goar以及驱动芯片cof与辅助栅极线vg1~vgy、栅极线g1~gy、信号线busl1、busl2以及数据线组d1~dq的电路布局的示意图。如图2所示,栅极驱动电路goa分别电性耦接配置于显示区域aa的辅助栅极线vg1~vgy,并且栅极驱动电路goar分别电性耦接配置于显示区域aa的辅助栅极线vgp-1~vgp。辅助栅极线vg1~vgy分别电性耦接对应的栅极线g1~gy,并且辅助栅极线vg1~vgy与栅极线g1~gy电性绝缘。

66.栅极驱动电路goa电性耦接对应的信号线busl1、busl2。信号线busl1以及busl2分别用以传送时钟信号hc1以及hc2。在一些实施例中,显示面板100会具有更多数量的信号线分别传送更多数量的时钟信号,例如,7条信号线分别用于传送7个时钟信号。因此,本公开不以此为限。

67.驱动芯片组122所包含的驱动芯片cof分别电性耦接对应的数据线组d1~db以及db 1~dq。数据线组d1包含数据线d11、d12以及d13。类似地,数据线组d2包含数据线d21、

d22以及d23,依此类推。

68.如此,在栅极驱动器112所包含的栅极驱动电路goa以及goar的总数为驱动芯片组122所包含的驱动芯片cof的数量的倍数的情形下,栅极驱动器112所包含的栅极驱动电路goa以及goar与驱动芯片组122所包含的驱动芯片cof之间的扇出型封装可以完整对接。

69.请一并参阅图3,图3为依据本公开文件的一些实施例所示出的栅极驱动电路goa以及goar与辅助栅极线vg1、vg2、vgp-1及vgp、栅极线g1及g2以及信号线busl1、busl2的电路布局的示意图。如图3所

70.示,栅极驱动电路goa的走线31与辅助栅极线vg1、vg2的重叠处经设5置通孔30,使栅极驱动电路goa与辅助栅极线vg1、vg2电性耦接。栅极驱动电路goar的走线33与辅助栅极线vgp-1、vg-p的重叠处经设置通孔30,使栅极驱动电路goar与辅助栅极线vgp-1、vg-p电性耦接。

71.栅极驱动电路goa的走线32与信号线busl1、busl2的重叠处经设置通孔30,使栅极驱动电路goa与信号线busl1、busl2电性耦接。另0一方面,栅极驱动电路goar的走线34与信号线busl1、busl2的重叠处不设置通孔,使栅极驱动电与信号线busl1、busl2电性绝缘。

72.在一些实施例中,数据线组d2所包含数据线d21、d22以及d23每一者分别电性耦接像素阵列130中位于同一子像素行中的子像素r、g或b。

73.数据线组d3、dq-1以及dq与子像素r、g或b的连接关系类似于数据线5组d2所包含数据线d21、d22以及d23与对应的子像素r、g或b的连接关系,故在此不再赘述。

74.请参阅图3以及图4,图4为依据本公开文件的一些实施例所示出的栅极驱动电路goa(n)的电路架构的示意图。在图3所示的栅极驱动电路goa

75.每一者对应于图4的栅极驱动电路goa(n)。如图4所示,栅极驱动电路0goa(n)包含上拉控制电路410、上拉电路420、下拉控制电路450以及460、第一下拉电路430以及第二下拉电路440。

76.上拉控制电路410包含晶体管t12以及t11。晶体管t12的第一端用以接收时钟信号hc7,晶体管t12的二端电性耦接晶体管t11的栅极端,

77.并且晶体管t12的栅极端用以接收控制信号q(n-6)。晶体管t12用以依据5控制信号q(n-6)导通时钟信号hc7至晶体管t11的栅极端的电路路径。

78.晶体管t11的第一端电性耦接系统高电压端vdd,晶体管t11的第二端电性耦接操作节点q(n)。当晶体管t11依据时钟信号hc7而导通时,系统高电压端vdd的电压经由晶体管t11传送至操作节点q(n)。

79.上拉电路420包含晶体管t21。晶体管t21的第一端用以接收时钟信0号hc1,晶体管t21的第二端电性耦接走线31,用以输出栅极控制信号g(n),晶体管t21的栅极端电性耦接操作节点q(n)。晶体管t21用以依据操作节点q(n)的电位导通或关断时钟信号hc1与栅极控制信号g(n)之间的电路路径。

80.当晶体管t21导通时钟信号hc1与栅极控制信号g(n)之间的电路路径且时钟信号hc1具有高逻辑电平时,栅极控制信号g(n)具有高逻辑电平,并且栅极控制信号g(n)会经由走线31、相应的辅助栅极线(例如,辅助栅极线vg1)传送至对应的栅极线(例如,栅极线vg1),从而导通位于像素阵列130同一列中的像素各自内部设定数据电压的电路路径,如图2以及图3所示。

81.下拉控制电路450包含晶体管t51~t56。晶体管t51的第一端以及栅极端用以接收低频时钟信号lc1,晶体管t51的第二端电性耦接晶体管t53的栅极端。晶体管t51用以依据低频时钟信号lc1导通低频时钟信号lc1至晶体管t55的第一端以及晶体管t53的栅极端的电路路径。

82.晶体管t52的第一端电性耦接晶体管t53的栅极端,晶体管t52的第二端电性耦接系统低电压端vssq,晶体管t52的栅极端电性耦接操作节点q(n)。晶体管t52用以依据操作节点q(n)的电位导通晶体管t53的栅极端至系统低电压端vssq的电路路径。

83.晶体管t53的第一端用以接收低频时钟信号lc1,晶体管t53的栅极端电性耦接晶体管t51的第二端以及晶体管t55的第一端,晶体管t53的第二端电性耦接稳压节点p(n)。当操作节点q(n)的电位具有低逻辑电平且晶体管t51依据低频时钟信号lc1导通时,低频时钟信号lc1经由晶体管t51传送至晶体管t53的栅极端,使晶体管t53导通低频时钟信号lc1至稳压节点p(n)的电路路径,从而上拉稳压节点p(n)的电位。

84.晶体管t55的第一端电性耦接晶体管t53的栅极端,晶体管t55的栅极端用以接收控制信号q(n-2),晶体管t55的第二端电性耦接系统低电压端vssq,晶体管t55用以依据控制信号q(n-2)导通晶体管t53的栅极端至系统低电压端vssq的电路路径。当控制信号q(n-2)具有高逻辑电平时,晶体管t55导通晶体管t53的栅极端至系统低电压端vssq的电路路径,使晶体管t53关断低频时钟信号lc1至稳压节点p(n)的电路路径。

85.晶体管t56以及t54皆是电性耦接在稳压节点p(n)以及系统低电压端vssq之间,晶体管t56以及t54的栅极端分别用以接收控制信号q(n-2)以及q(n)。晶体管t56以及t54分别用以依据控制信号q(n-2)以及q(n)导通稳压节点p(n)至系统低电压端vssq之间的电路路径。当控制信号q(n-2)或q(n)具有高逻辑电平时,晶体管t56以及t54中的相应者导通,从而下拉稳压节点p(n)的电位。

86.第一下拉电路430包含晶体管t32~t35。第一下拉电路430用以下拉栅极控制信号g(n)的电位以及上拉控制电路410中的晶体管t11的栅极端的电位。第二下拉电路440包含晶体管t41~t44。第二下拉电路440用以下拉操作节点q(n)的电位。晶体管t44以及晶体管t41分别依据控制信号st以及s(n 6)导通操作节点q(n)至系统电压端vssq的电路路径。

87.稳压节点p(n)电性耦接晶体管t42、t32以及t34的栅极端。当稳压节点p(n)的电位具有高逻辑电平时,晶体管t42导通系统低电压端vssq至操作节点q(n)的电路路径,使晶体管t21依据操作节点q(n)的电位关断时钟信号hc1至栅极控制信号g(n)的电路路径。此时,晶体管t34导通晶体管t11的栅极端(晶体管t11的栅极端的电位由控制信号s(n)示意)至系统低电压端vssq的电路路径。并且,晶体管t32导通栅极控制信号g(n)至系统低电压端vss的电路路径,从将系统低电压端vss的电压作为栅极控制信号g(n)输出。

88.下拉控制电路460中的晶体管t61~t66之间的连接关系分别类似于下拉控制电路450中的晶体管t51~t55之间的连接关系。相较于下拉控制电路450,下拉控制电路460的不同之处在于,时钟信号lc1由lc2取代,并且稳压节点p(n)由k(n)取代。于下拉控制电路460中的晶体管t61~t66的其余连接关系以及作动方式大致上类似于下拉控制电路450中的晶体管t51~t55的连接关系以及作动方式,故在此不再赘述。

89.类似地,稳压节点k(n)电性耦接晶体管t43、t33以及t35的栅极端。当稳压节点p(n)的电位具有高逻辑电平时,晶体管t43导通系统低电压端vssq至操作节点q(n)的电路路

径,使晶体管t21依据操作节点q(n)的电位关断时钟信号hc1至栅极控制信号g(n)的电路路径。此时,晶体管t35导通晶体管t11的栅极端(晶体管t11的栅极端的电位由控制信号s(n)示意)至系统低电压端vssq的电路路径。并且,晶体管t33导通栅极控制信号g(n)至系统低电压端vss的电路路径,从将系统低电压端vss的电压作为栅极控制信号g(n)输出。

90.请参阅图3以及图5,图5为依据本公开文件的一些实施例所示出的栅极驱动电路goar(n)的电路架构的示意图。在图3所示的栅极驱动电路goar每一者对应于图5的栅极驱动电路goar(n)。如图5所示,栅极驱动电路goar(n)包含上拉控制电路510、上拉电路520、下拉控制电路550以及560、第一下拉电路530以及第二下拉电路540。上拉控制电路510包含晶体管t11以及t12、上拉电路520包含晶体管t21。

91.在图3的实施例中,栅极驱动电路goar(n)的走线34与信号线bus1以及bus2的重叠处并未设置通孔,而使栅极驱动电路goar(n)与用于传送时钟信号hc1的信号线busl1以及hc7的信号线(未示出)电性绝缘。因此,相较于图4中的栅极驱动电路goa(n)的架构,栅极驱动电路goar(n)的架构的不同之处在于,晶体管t12的第一端未接收时钟信号hc7而是浮接导线,并且晶体管t21的第一端未接收时钟信号hc1而是浮接导线。

92.如此,晶体管t11依据晶体管t12传送的电位vf(例如,低逻辑电平)而不作动,在晶体管t11不作动的情形下,晶体管t21亦会保持关断的状态。

93.如此,栅极驱动电路goar(n)中的上拉控制电路510以及上拉电路520保持关断且不作动,从而不会上拉栅极驱动电路goar(n)的输出端的电位。

94.在一些实施例中,栅极驱动电路goar(n)更用以输出稳压信号sv(n)。具体而言,栅极驱动电路goar(n)中的下拉控制电路550、560以及下拉电路530以及540仍持续运行,并提供于低逻辑电平稳定的稳压信号sv(n)至相应的辅助栅极线(例如,图3所示的辅助栅极线vgp-1或vgp)。

95.于图5的实施例中,栅极驱动电路goar(n)中的下拉控制电路550、560以及下拉电路530以及540的连接关系以及操作方式大致上类似于图4中的栅极驱动电路goa(n)中的下拉控制电路450、460以及下拉电路430以及440的连接关系以及操作方式,故在此不再赘述。

96.请参阅图6,图6为依据本公开文件的一些实施例所示出的栅极驱动电路goa以及goar与辅助栅极线vg1、vg2、vgp-1及vgp、栅极线g1及g2以及信号线busl1、busl2的示意图。于图6的实施例中,剩余的栅极驱动电路goar(n)的走线33与辅助栅极线vgp-1以及vgp的重叠处未设置通孔,因此栅极驱动电路goar(n)与辅助栅极线vgp-1以及vgp电性隔绝。在一些实施例中,辅助栅极线vgp-1以及vgp是浮接导线。

97.在图6的实施例中,由于栅极驱动电路goar(n)与辅助栅极线vgp-1以及vgp电性隔绝,栅极驱动电路goar(n)经由通孔30与信号线busl1以及busl2电性耦接,仍不会传送信号至辅助栅极线vgp-1以及vgp。

98.在另一些实施例中,栅极驱动电路goar(n)的走线34与信号线busl1以及busl2的重叠处亦可不设置通孔30。因此,本公开不以此为线。

99.于图6中栅极驱动电路goa(n)、栅极线g1以及g2、辅助栅极线vg1、vg2、vgp-1以及vgp的布局大致上类似于图3中栅极驱动电路goa(n)、栅极线g1以及g2、辅助栅极线vg1、vg2、vgp-1以及vgp的布局,故在此不再赘述。

100.请参阅图7,图7为依据本公开文件的一些实施例所示出的栅极驱动电路goa以及

goar与辅助栅极线vg1、vg2、vgp-1及vgp、栅极线g1及g2以及信号线busl1、busl2及信号线dc的电路布局的示意图。于图7的实施例中,剩余的栅极驱动电路goar(n)的走线33与辅助栅极线vgp-1以及vgp的重叠处未设置通孔,因此栅极驱动电路goar(n)与辅助栅极线vgp-1以及vgp电性隔绝。

101.再者,在进入显示区域aa之前,辅助栅极线vgp-1以及vgp与直流信号的信号线dc的重叠处可设置通孔30,使辅助栅极线vgp-1以及vgp与直流信号的信号线dc电性耦接,从而传送直流信号至辅助栅极线vgp-1以及vgp,进而对辅助栅极线vgp-1以及vgp进行稳压。

102.在图7的实施例中,由于栅极驱动电路goar(n)与辅助栅极线vgp-1以及vgp电性隔绝,栅极驱动电路goar(n)可与信号线busl1以及busl2电性耦接,仍不会输出信号至辅助栅极线vgp-1以及vgp。

103.在另一些实施例中,栅极驱动电路goar(n)的走线34与信号线busl1以及busl2的重叠处亦可不设置通孔30。因此,本公开不以此为限。

104.于图7中栅极驱动电路goa(n)、栅极线g1以及g2、辅助栅极线vg1、vg2、vgp-1以及vgp的布局大致上类似于图3中栅极驱动电路goa(n)、栅极线g1以及g2、辅助栅极线vg1、vg2、vgp-1以及vgp的布局,故在此不再赘述。

105.综上所述,本公开文件提供的显示面板100包含多余的栅极驱动电路goar,从而改善扇出型封装的问题。并且,多余的栅极驱动电路goar会具有相应的辅助栅极线(例如,辅助栅极线vgp-1以及vgp),本公开文件的显示面板100中多余的垂直辅助栅极线vgp-1以及vgp与水平的栅极线g1~gy电性绝缘,从而降低多余走线对对像素阵列130的影响。再者,本公开文件可提供稳压信号sv(n)或直流信号予中多余的垂直辅助栅极线vgp-1以及vgp,进一步降低多余走线(例如,垂直辅助栅极线vgp-1以及vgp)对像素阵列130的影响。

106.虽然本公开已以实施方式公开如上,然其并非用以限定本公开,任何本领域通具通常知识者,在不脱离本公开的构思和范围内,当可作各种的变动与润饰,因此本公开的保护范围当视权利要求所界定者为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。