技术特征:

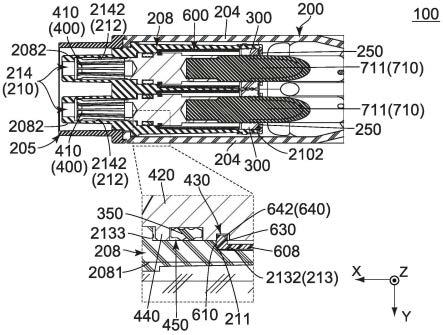

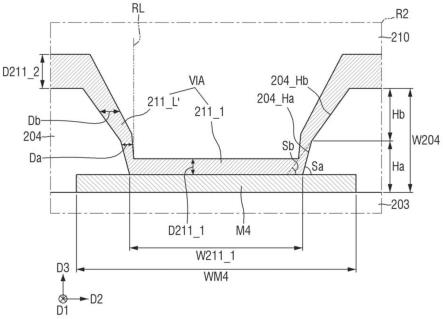

1.一种半导体器件,包括:衬底;导电层,设置在所述衬底上并且沿第一方向延伸;绝缘层,设置在所述导电层上并且通过其中限定的通路孔暴露所述导电层的至少一部分,其中,所述通路孔包括:第一面,相对于所述导电层的顶面以第一坡度延伸;以及第二面,相对于所述导电层的顶面以第二坡度延伸,所述第二坡度小于所述第一坡度;以及再分布导电层,包括:第一焊盘区域,设置在所述通路孔中;以及线路区域,至少部分地沿着所述第一面和所述第二面延伸,其中,所述第一面直接接触所述导电层,并且所述第二面在垂直于所述衬底的顶面的第三方向上位于比所述第一面的高度高的高度处。2.根据权利要求1所述的半导体器件,其中,所述线路区域以比所述第三方向的坡度小的坡度延伸。3.根据权利要求1所述的半导体器件,其中,所述第一坡度在60

°

至90

°

的范围内。4.根据权利要求3所述的半导体器件,其中,所述通路孔还包括第三面,所述第三面在所述第三方向上位于比所述第二面的高度高的高度处,其中,所述第三面相对于所述导电层的顶面以第三坡度延伸,所述第三坡度小于所述第二坡度。5.根据权利要求3所述的半导体器件,其中,所述线路区域设置在所述第一面上的部分在第二方向上的第一厚度小于所述线路区域设置在所述第二面上的部分在所述第二方向上的第二厚度,其中,所述第二方向与所述第一方向相交。6.根据权利要求5所述的半导体器件,其中,所述第一厚度在0.3um至3um的范围内,其中,所述第二厚度在0.3um至10um的范围内。7.根据权利要求1所述的半导体器件,其中,所述绝缘层在所述第三方向上的厚度在2um至10um的范围内。8.根据权利要求1所述的半导体器件,其中,所述再分布导电层还包括:第二焊盘区域,设置在所述绝缘层的顶面上;以及钝化层,覆盖所述再分布导电层并且暴露所述第二焊盘区域的至少一部分。9.根据权利要求8所述的半导体器件,其中,所述器件还包括:再分布凸块,设置在所述第二焊盘区域的由所述钝化层暴露的所述至少一部分上,其中,所述再分布导电层将所述再分布凸块和所述第二焊盘区域电连接到所述导电层。10.根据权利要求1所述的半导体器件,其中,所述再分布导电层包括铝al。11.一种半导体器件,包括:衬底;导电层,设置在所述衬底上并且沿第一方向延伸;绝缘层,设置在所述导电层上并且通过其中限定的通路孔暴露所述导电层的至少一部分,其中,所述通路孔包括:

第一面,相对于所述导电层的顶面以第一坡度延伸;以及第二面,相对于所述导电层的顶面以第二坡度延伸,所述第二坡度小于所述第一坡度;以及再分布导电层,包括:第一焊盘区域,设置在所述通路孔中;以及线路区域,至少部分地沿着所述第一面和所述第二面延伸,其中,所述线路区域以比垂直于所述衬底的顶面的第三方向的坡度小的坡度延伸。12.根据权利要求11所述的半导体器件,其中,所述第一面直接接触所述导电层,并且所述第二面在所述第三方向上位于比所述第一面的高度高的高度处。13.根据权利要求11所述的半导体器件,其中,所述绝缘层在所述第三方向上的厚度在2um至10um的范围内。14.根据权利要求11所述的半导体器件,其中,所述线路区域不向内朝向所述第一焊盘区域延伸超过限制线,所述限制线从所述第一焊盘区域的外边缘沿所述第三方向延伸。15.一种用于制造半导体器件的方法,所述方法包括:设置衬底;在所述衬底上形成导电层;在所述导电层上形成绝缘层;在所述绝缘层上形成光刻胶层;使用包括图案组的掩模将所述光刻胶层曝光,并且显影曝光的光刻胶层以形成光刻胶孔图案;使用所述光刻胶孔图案作为蚀刻掩模来蚀刻所述绝缘层,以形成限定在所述绝缘层中的通路孔,所述通路孔暴露所述导电层的至少一部分;以及形成再分布导电层,所述再分布导电层包括设置在所述通路孔中的第一焊盘区域和至少部分地沿着所述通路孔的侧壁延伸的线路区域,其中,所述图案组包括:主图案,具有与所述通路孔的平面形状相同的平面形状;以及多个寄生图案,顺序地向外布置以围绕所述主图案,其中,所述多个寄生图案中的每一个在平面图中具有闭合环形状。16.根据权利要求15所述的方法,其中,所述通路孔具有:第一面,相对于所述导电层的顶面以第一坡度延伸;以及第二面,相对于所述导电层的顶面以第二坡度延伸,所述第二坡度小于所述第一坡度,其中,所述线路区域至少部分地沿着所述通路孔的所述第一面和所述第二面延伸,其中,所述第一坡度在60

°

至90

°

的范围内。17.根据权利要求16所述的方法,其中,所述第一面直接接触所述导电层,并且所述第二面在垂直于所述衬底的顶面的第三方向上位于比所述第一面的高度高的高度处。18.根据权利要求15所述的方法,其中,所述多个寄生图案包括:第一寄生图案,与所述主图案直接相邻设置并且围绕所述主图案;以及第二寄生图案,与所述第一寄生图案间隔开并且围绕所述主图案和所述第一寄生图案。

19.根据权利要求18所述的方法,其中,在平面图中,所述第一寄生图案的宽度小于所述第二寄生图案的宽度。20.根据权利要求15所述的方法,其中,所述再分布导电层是使用选自物理气相沉积pvd工艺或包括物理气相沉积的铝回流工艺的至少一种工艺来形成的。

技术总结

一种半导体器件包括衬底。导电层设置在衬底上并且沿第一方向延伸。绝缘层设置在导电层上并且通过通路孔暴露导电层的至少一部分。通路孔包括相对于导电层的顶面以第一坡度延伸的第一面。第二面相对于导电层的顶面以小于第一坡度的第二坡度延伸。再分布导电层包括设置在通路孔中的第一焊盘区域。线路区域至少部分地沿着第一面和第二面延伸。第一面直接接触导电层。第二面在垂直于衬底的顶面的第三方向上位于比第一面高的高度处。位于比第一面高的高度处。位于比第一面高的高度处。

技术研发人员:姜旼声 文泂烈 秦浚禑 金甫贤 赵星东 赵原熙

受保护的技术使用者:三星电子株式会社

技术研发日:2022.07.01

技术公布日:2023/2/6

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。