touch mcu的低功耗管理系统

技术领域

1.本发明是关于集成touchkey功能的mcu低功耗管理领域,特别是关于一种touch mcu的低功耗管理系统。

背景技术:

2.随着智能物联、智能监测、智能管控集成技术的发展,低功耗mcu\soc产品应用以及智能家居、智能家电和智能健康监测、智能物联等技术发展。目前实现touch mcu的低功耗管理电路系统或将touckey作为特定的ip模块电路集成于soc/mcu系统中存在功耗高、成本高、集成度低、通用性低等特点,难以满足社会发展带来的技术需求。

3.公开于该背景技术部分的信息仅仅旨在增加对本发明的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现要素:

4.本发明的目的在于提供一种touch mcu的低功耗管理系统,其能够降低系统的功耗、成本以及提高集成度、通用性。

5.为实现上述目的,本发明的实施例提供了一种touch mcu的低功耗管理系统,包括:cpu内核模块、电源管理单元pmu、时钟产生及控制逻辑模块、复位产生及控制逻辑模块、低功耗工作ip模块、touch ip及控制逻辑模块、唤醒控制逻辑模块。

6.cpu内核模块用于产生多个模式信号;电源管理单元基于模式信号产生对应的供电电压并同时产生用于表征供电正常的表征信号;复位产生及控制逻辑模块用于产生多个复位信号;时钟产生及控制逻辑模块用于接收复位信号和表征信号并输出第一时钟信号clk_cpu至cpu内核模块以及输出第二时钟信号clk_per至低功耗工作ip模块和touch ip及控制逻辑模块,并在对应的模式信号的控制下控制第一时钟信号clk_cpu和第二时钟信号clk_per的产生以及自身的关断;低功耗工作ip模块基于第一中断事件产生第一控制信号;touch ip及控制逻辑模块接收第二时钟信号clk_per基于第二中断事件产生第二控制信号;唤醒控制逻辑模块接收第一控制信号和/或第二控制信号而产生唤醒逻辑信号。

7.在本发明的一个或多个实施例中,所述低功耗管理系统还包括寄存器模块,所述寄存器模块基于自身的配置位控制cpu内核模块以产生对应的模式信号。

8.在本发明的一个或多个实施例中,所述低功耗管理系统还包括中断控制器,所述中断控制器用于清除第一中断事件和第二中断事件。

9.在本发明的一个或多个实施例中,所述时钟产生及控制逻辑模块包括时钟源控制逻辑模块、晶体/陶瓷振荡器、高频rc振荡器、低频rc振荡器、外部时钟源、mux选择器、分频器、第一门控逻辑电路和第二门控逻辑电路;所述时钟源控制逻辑模块用于基于复位信号、表征信号和模式信号输出控制信号以对晶体/陶瓷振荡器、高频rc振荡器、低频rc振荡器和外部时钟源进行控制,所述mux选择器用于对晶体/陶瓷振荡器、高频rc振荡器、低频rc振荡器和外部时钟源输出的时钟信号进

行选择,所述分频器用于对mux选择器输出的信号进行选择性分频;所述第一门控逻辑电路用于对分频器输出的信号进行控制而输出第一时钟信号,所述第二门控逻辑电路用于对分频器输出的信号进行控制而输出第二时钟信号。

10.在本发明的一个或多个实施例中,所述电源管理单元包括低vdd电压电源、高vdd电压电源和低功耗控制逻辑,所述低功耗控制逻辑用于基于模式信号控制低vdd电压电源和高vdd电压电源的切换。

11.在本发明的一个或多个实施例中,所述touch ip及控制逻辑模块包括touch控制逻辑模块和模拟touch电容及adc电路模块,所述touch控制逻辑模块用于基于时钟信号和模式信号进行工作模式和工作时钟信号的选择并产生供模拟touch电容及adc电路模块运行的运行信号和通道信号,所述adc电路模块用于产生有效数据和有效信号至touch控制逻辑模块。

12.在本发明的一个或多个实施例中,所述touch控制逻辑模块用于产生控制信号以控制唤醒控制逻辑模块产生唤醒逻辑信号。

13.在本发明的一个或多个实施例中,所述低功耗管理系统还包括与cpu内核模块相连的jtag/ip模块、储存器模块和ip模块,所述jtag/ip模块用于程序的加载和调试,所述储存器模块用于数据的储存。

14.在本发明的一个或多个实施例中,所述复位信号包括上电复位信号、低电压复位信号、复位信号、暖复位信号和冷复位信号。

15.在本发明的一个或多个实施例中,所述模式信号包括空闲模式信号、停止模式信号和睡眠模式信号。

16.与现有技术相比,根据本发明的touch mcu的低功耗管理系统,可作为需要内置touchkey ip的mcu的低功耗系统,或者多种低功耗模式以及需要快速唤醒等特性的mcu或soc系统。

17.根据cpu内核模块运行时,寄存器模块配置低功耗模式实现mcu/soc系统进入空闲、停止、睡眠中的一种低功耗模式,并根据不同的低功耗模式进行相应的电源管理单元、时钟产生及控制逻辑模块、复位产生及控制逻辑模块的管理和控制,进而实现低功耗模式下控制电源管理单元的运行以及时钟产生及控制逻辑模块的时钟信号的关断和开启等;本发明的touch ip及控制逻辑模块的低功耗管理和快速唤醒,可作为一个通用的需要touch功能的mcu或soc中的ip模块的低功耗管理;可用于集成于soc或mcu系统等具有touch功能的低功耗、通用性强、占用面积小、节约成本等需求的系统中。

附图说明

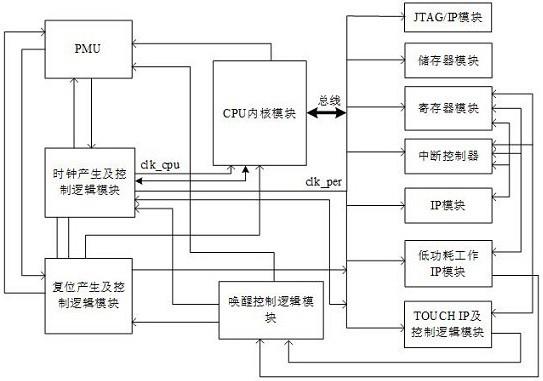

18.图1是根据本发明一实施例的touch mcu的低功耗管理系统的系统图。

19.图2是根据本发明一实施例的时钟产生及控制逻辑模块的系统图。

20.图3a是根据本发明一实施例的复位产生与控制逻辑模块的第一电路原理图。

21.图3b是根据本发明一实施例的复位产生与控制逻辑模块的第二电路原理图。

22.图4是根据本发明一实施例的时钟产生及控制逻辑模块以及复位产生与控制逻辑模块中各信号的时序图。

23.图5是根据本发明一实施例的电源管理单元的系统图。

24.图6是根据本发明一实施例的电源管理单元的低功耗控制逻辑图。

25.图7是根据本发明一实施例的touch ip及控制逻辑模块的系统图。

26.图8是根据本发明一实施例的touch ip及控制逻辑模块的电路原理图。

27.图9是根据本发明一实施例的唤醒逻辑控制示意图。

具体实施方式

28.下面结合附图,对本发明的具体实施例进行详细描述,但应当理解本发明的保护范围并不受具体实施例的限制。

29.除非另有其它明确表示,否则在整个说明书和权利要求书中,术语“包括”或其变换如“包含”或“包括有”等等将被理解为包括所陈述的元件或组成部分,而并未排除其它元件或其它组成部分。

30.应当理解,在以下的描述中,“电路”可包括单个或多个组合的硬件电路、可编程电路、状态机电路和/或能存储由可编程电路执行的指令的元件。当称元件或电路“连接到”另一元件,或与另一元件“相连”,或称元件/电路“连接在”两个节点之间时,它可以直接耦合或连接到另一元件或者可以存在中间元件,元件之间的连接可以是物理上的、逻辑上的、或者其结合。相反,当称元件“直接耦合到”或“直接连接到”另一元件时,意味着两者不存在中间元件。

31.下面结合附图和实施例对本发明进一步说明。

32.如图1所示,一种touch mcu的低功耗管理系统,包括:cpu内核模块、电源管理单元pmu、时钟产生及控制逻辑模块、复位产生及控制逻辑模块、低功耗工作ip模块、touch ip及控制逻辑模块、唤醒控制逻辑模块、ip模块、中断控制器、寄存器模块、储存器模块和jtag/ip模块。

33.在本实施例中,具有touch ip及控制逻辑模块的mcu的低功耗管理系统,通过设计cpu内核模块在不同功耗模式下,进行时钟产生及控制逻辑模块的关闭和控制、进行对应的唤醒逻辑的控制、以及进行电源管理单元pmu的供电电压运行管理,同时还设计在低功耗模式下,对低功耗工作ip模块、touch ip及控制逻辑模块的唤醒功能检测和唤醒逻辑控制。

34.具体的,cpu内核模块、电源管理单元pmu、时钟产生及控制逻辑模块和复位产生及控制逻辑模块之间相互连接进行信号通讯;电源管理单元pmu、时钟产生及控制逻辑模块和复位产生及控制逻辑模块均与唤醒控制逻辑模块相连进行信号通讯;低功耗工作ip模块、touch ip及控制逻辑模块、唤醒控制逻辑模块、ip模块、中断控制器、寄存器模块、储存器模块和jtag/ip模块均与cpu内核模块、时钟产生及控制逻辑模块和复位产生及控制逻辑模块相连进行信号通讯;唤醒控制逻辑模块与低功耗工作ip模块和touch ip及控制逻辑模块相连进行信号通讯;ip模块、中断控制器和寄存器模块之间相互连接进行信号通讯;中断控制器、寄存器模块和低功耗工作ip模块之间相互连接进行信号通讯;中断控制器、寄存器模块和touch ip及控制逻辑模块相连进行信号通讯。

35.其中,cpu内核模块用于产生多个模式信号;电源管理单元基于模式信号产生对应的供电电压并同时产生用于表征供电正常的表征信号;复位产生及控制逻辑模块用于产生多个复位信号;时钟产生及控制逻辑模块用于接收复位信号和表征信号并输出第一时钟信号clk_cpu至cpu内核模块以及输出第二时钟信号clk_per至低功耗工作ip模块和touch ip

及控制逻辑模块,并在对应的模式信号的控制下控制第一时钟信号clk_cpu和第二时钟信号clk_per的产生以及自身的关断;低功耗工作ip模块基于第一中断事件产生第一控制信号;touch ip及控制逻辑模块接收第二时钟信号clk_per基于第二中断事件产生第二控制信号;唤醒控制逻辑模块接收第一控制信号和/或第二控制信号而产生唤醒逻辑信号;jtag/ip模块用于程序的加载和调试,储存器模块用于数据的储存,ip模块用于实现不同功能。

36.在本实施例中,通过配置寄存器模块的配置位以控制cpu内核模块进入不同的低功耗模式,cpu内核模块产生对应低功耗模式的不同模式信号,如空闲模式信号idle、停止模式信号stop和睡眠模式信号sleep。通过模式信号控制电源管理单元pmu以及控制时钟产生及控制逻辑模块的时钟信号的产生与关断,并在停止模式信号stop和睡眠模式信号sleep的控制下,通过复位产生及控制逻辑模块的暖复位计数器重新计数暖复位计数值,进行暖复位信号warm_done的产生和控制。

37.在低功耗工作ip模块和touch ip及控制逻辑模块进入低功耗模式后,产生的中断事件都通过唤醒控制逻辑模块进行唤醒逻辑信号的产生,通过唤醒逻辑信号进行唤醒使能cpu内核模块和时钟产生及控制逻辑模块,使cpu内核模块和相关的低功耗工作ip模块和touch ip及控制逻辑模块进入正常模式下进行工作。

38.在本实施例中,以三种不同的低功耗模式(空闲、停止、睡眠)为例进行说明,这些模式可以通过寄存器模块进行配置。关于在三种低功耗模式下的时钟产生及控制逻辑模块和电源管理单元pmu的运行方式如下:(1)配置寄存器模块使管理系统进入空闲模式,即产生的空闲模式信号idle使得时钟产生及控制逻辑模块停止输出供给cpu内核模块的第一时钟信号clk_cpu,而在空闲模式下为了能够产生中断事件唤醒cpu内核模块,时钟产生及控制逻辑模块继续输出第二时钟信号clk_per给低功耗工作ip模块和touch ip及控制逻辑模块。

39.(2)配置寄存器模块使管理系统进入停止模式,除特殊需求的touch ip及控制逻辑模块仍继续工作,即产生的停止模式信号stop使得时钟产生及控制逻辑模块停止输出第一时钟信号clk_cpu和第二时钟信号clk_per,另外除有特殊低功耗需求工作的时钟源需求外,停止所有时钟振荡器的工作。

40.(3)配置寄存器模块使管理系统进入睡眠模式,除特殊需求的touch ip及控制逻辑模块仍继续工作,即产生的睡眠模式信号sleep使得停止输出第一时钟信号clk_cpu和第二时钟信号clk_per以及停止所有时钟振荡器的工作;为了减小睡眠模式下的系统功耗,电源管理单元pmu产生的供电电压会从1.5v降低到1.2v左右。

41.在本实施例中,低功耗管理系统主要根据cpu内核模块在低功耗模式下对电源管理单元pmu、时钟产生及控制逻辑模块和复位产生及控制逻辑模块等的控制和管理,另外需要对进入低功耗模式的低功耗工作ip模块、touch ip及控制逻辑模块和唤醒控制逻辑模块产生的唤醒逻辑信号进行控制和处理。根据cpu内核模块产生的模式信号和时钟产生及控制逻辑模块的时钟源控制逻辑模块以及需要特殊低功耗需求运行的touch ip及控制逻辑模块等产生控制各时钟源的控制逻辑信号。

42.如图2所示,时钟产生及控制逻辑模块内部主要设置有四个时钟源,分别为片上晶体/陶瓷振荡器、4/8/12/16mhz配置4档可选的高频rc振荡器、32khz的低频rc振荡器和外部

时钟源,通过硬件代码配置字和软件寄存器配置选择的时钟产生一个作为整个管理系统工作的主要时钟。

43.具体的,片上晶体/陶瓷振荡器产生时钟信号clk_xtal,外部时钟源产生时钟信号clk_ext、高频rc振荡器产生时钟信号clk_hirc、低频rc振荡器产生时钟信号clk_32k。时钟产生及控制逻辑模块还包括mux选择器和分频器,mux选择器用于对四个时钟源进行选择,分频器对选择的时钟源产生的时钟信号根据分频比选择是否分频。时钟产生及控制逻辑模块还包括用于基于分频器输出的分频信号产生第一时钟信号clk_cpu的第一门控逻辑电路clk_cpu_gate和用于基于分频器输出的分频信号产生第二时钟信号clk_per的第二门控逻辑电路clk_per_gate。

44.如图2所示,时钟源控制逻辑模块接收来自于复位产生与控制逻辑模块的上电复位电路在系统上电后产生的上电复位信号por、复位产生与控制逻辑模块的低电压复位电路产生的低电压复位信号lvr以及复位产生与控制逻辑模块产生的用于内部控制系统和ip模块、低功耗工作ip模块以及touch ip及控制逻辑模块的模块复位信号reset(rstff);时钟源控制逻辑模块同时接收来自于电源管理单元pmu的信号pmu_ready,信号pmu_ready用于在上电后或者睡眠模式下标志电源管理单元pmu的供电正常的信号。时钟源控制逻辑模块同时接收来自于cpu内核模块的停止模式信号stop和睡眠模式信号sleep。

45.结合图3a、图3b和图4,在本实施例中,上电复位信号por主要控制系统的启动复位或检测主供电电源失效,芯片在上电过程中能够初始化复位。上电复位口通过复位控制逻辑产生相应的复位释放序列,主要分冷复位和热复位的产生和释放等,以及进入不同低功耗模式下的复位逻辑的处理。

46.上电复位信号por是复位产生与控制逻辑模块中的上电复位电路产生,pmu_ready是系统上电电源ok后产生的电源管理单元pmu稳定好的信号。时钟信号clk_32k为低频rc振荡器产生的时钟信号,在上电开始其控制信号clk_32_pd为低,即上电后即开启时钟信号clk_32k,并通过时钟信号clk_32k进行相应的冷复位计数器的计数。上电后冷复位计数器开启计数,当以时钟信号clk_32k计数到相应个数后,冷复位信号tout_rst_n进行释放,当冷复位信号tout_rst_n释放时,通过eeprom区的配置字进行时钟源选择。

47.图4以选择时钟信号clk_hirc配置为主系统时钟源为例进行说明,控制时钟信号clk_hirc,控制信号clk_hirc_pd在冷复位信号tout_rst_n释放后也进行释放,即时钟信号clk_hirc开启工作。而产生的冷复位信号tout_rst_n经时钟信号clk_32k同步后并计数相应计数个数后进行信号tout_done的释放。当信号tout_cone释放后,经信号clk_hirc控制开启计数,进行暖复位信号warm_done的计数,当暖复位计数器计数到相应数值后,进行暖复位信号warm_done的释放,同时信号clk_system即系统时钟信号产生,同时相应的时钟信号clk_cpu和时钟信号clk_per也经相应门控逻辑电路后产生,再经时钟信号clk_per同步后,进行cpu内核模块和低功耗工作ip模块、touch ip及控制逻辑模块以及相关控制逻辑复位的复位信号即图3a、图4中的模块复位信号rstff(reset)的释放和产生。

48.关于低功耗模式,当系统进入空闲模式,只进行时钟信号clk_cpu的管理(关断、开启)等;而进入停止以及睡眠模式下,对于时钟信号clk_cpu和clk_per的管理相同,对于复位系统管理,从停止/睡眠模式启动时,仅包含热启动时间。停止和睡眠模式下,对于相应的时钟源,除特殊需求的低功耗工作ip模块的时钟源进行关断处理。唤醒逻辑发生后,进行时

序序列仍以图4为例中的时序关系进行,先信号clk_hirc_pd的释放,接下来后续的相应的暖复位信号warm_done、时钟信号clk_cpu以及时钟信号clk_per的释放等,从而恢复到正常模式运行。

49.如图5所示,管理系统进入空闲模式下,主要以关断第一时钟信号clk_cpu进行低功耗模式处理,而进入停止模式以及睡眠模式则进行电源的关断和处理。如图5所示,电源管理单元pmu主要受来自于cpu内核模块输出的停止模式信号stop和睡眠模式信号sleep以及touch ip及控制逻辑模块输出的数字控制逻辑信号tkc_bg_en的影响,而产生系统的供电电压以及标志电源ok的信号pmu_ready。

50.电源管理单元pmu主要产生两个供电电压即1.5v(即高vdd电压)和1.2v(即低vdd电压),在正常和空闲模式下,提供1.5v和1.2v的两个电源都正常工作,提供1.5v的电源工作在模式1下;当进入停止模式,提供1.5v的电源进入另一种工作模式下运行,相对空闲和正常模式,提供1.5v的电源产生的功耗有所下降。当进入睡眠模式并且数字控制逻辑信号tkc_bg_en为0即touch ip及控制逻辑模块没有开启使能运行,提供1.5v的电源会关断,而提供1.2v的电源作为供电电压提供给系统的cpu内核模块和存储器模块;当唤醒逻辑发生时,系统从睡眠模式退出,高vdd电压即提供1.5v的电源又恢复正常工作。

51.如图6所示,当工作在停止或睡眠模式下,并且数字控制逻辑信号tkc_bg_en为0,即没有开启touch ip及控制逻辑模块,此时控制高vdd电压即提供1.5v的电源脱离模式1,使其工作在另一种低功耗模式下;当开启touch ip及控制逻辑模块的功能,此时tck_bg_en为1时,此时,提供1.5v的电源工作在模式1下。当进入睡眠模式,并且没有开启touch ip及控制逻辑模块的功能时,此时高vdd电压即提供1.5v的电源的基准电源信号将关断即关断提供1.5v的电源的供电,此时,电源管理单元pmu的信号pmu_ready变为低电平;在没有开启touch ip及控制逻辑模块的功能,并且退出睡眠模式时,此时高vdd电压即提供1.5v的电源的基准电源信号将再次开启即也再次开启提供1.5v的电源的供电,进入正常模式下的供电。当检测高vdd电压产生电路产生的1.5v即1.5v供电ok后,信号pmu_ready也再次变为高电平逻辑。而如进入睡眠模式,此时选择开启touch ip及控制逻辑模块的功能并且当数字控制逻辑信号tck_bg_en为高电平时,此时高vdd电压即1.5v电压的基准电源信号将开启,并且提供1.5v的电源仍正常供电。

52.如图7所示,touch ip及控制逻辑模块主要根据需求对三个时钟信号clk_per、clk_hirc、clk_32k进行选择;在正常和空闲模式下,通过时钟信号clk_per进行touch ip及控制逻辑模块的touch控制逻辑模块的运行;当在停止或睡眠模式下,根据寄存器模块配置的需求,选择低功耗模式下的touch控制逻辑模块的工作时钟信号,如果配置快速唤醒功能,在停止或睡眠模式下,touch控制逻辑模块以时钟信号clk_hirc为低功耗运行时钟进行相应touch控制逻辑模块的功能特性的检测和唤醒功能。另外touch控制逻辑模块的低功耗控制逻辑还会接收来自于cpu内核模块的空闲模式信号idle、停止模式信号stop和睡眠模式信号sleep以及根据cpu内核模块的中断唤醒逻辑信号tkadc_intack进行touch控制逻辑模块的中断事件清除,具体的,中断控制器接收低功耗工作ip模块上的第一中断事件和touch ip及控制逻辑模块上的第二中断事件并进行处理,中断控制器将处理产生的信号传输至cpu内核模块,cpu内核模块响应中断从而清除中断事件。

53.另外,touch控制逻辑模块还会产生控制模拟touch电容及adc电路模块的采样时

钟信号tkadc_clk;touch控制逻辑模块还会产生控制模拟touch电容及adc电路模块运行的运行信号tkc_run、tkc_start以及通道信号channel。adc电路模块每次运行完会产生有效数据dat_in和一次有效信号dat_vld。另外,touch控制逻辑模块根据内部运行逻辑产生控制高频rc振荡器工作的信号tkc_hirc_en以及控制提供1.5v电源正常工作的信号tkc_bg_en。touch控制逻辑模块还会产生去中断控制器的信号tkadcif(第二中断事件)以及去唤醒控制逻辑模块的控制信号pd_tkcif_set,唤醒控制逻辑模块基于控制信号pd_tkcif_set(第二控制信号)产生唤醒逻辑信号。

54.如图8所示,工作在停止或睡眠模式下,选择时钟信号clk_hirc经过门控时钟电路后的产生的时钟信号clk_hirc_sig或者在非低功耗模式下选择第二时钟信号clk_per。当配置分频器不分频时,在低功耗模式下的用于adc电路模块的采样时钟信号tkadc_clk由信号tkc_hirc_en和退出低功耗同步信号及唤醒事件共同产生的作为门控时钟电路的使能信号tkc_clk_en结合门控时钟电路的输入信号clk_hirc产生。信号tkc_hirc_en由控制电源管理单元pmu的逻辑信号和低功耗信号sleep经低功耗模式下的时钟同步逻辑后的信号和低功耗模式下的时钟计数信号tkc_bg_en的相应个数后的信号共同控制产生,即当tkc_bg_en开启时,经计数信号tkc_bg_en开启后的相应个数后,开启信号tkc_hirc_en使其有效,当信号tkc_bg_en配置为0,不使能时,信号tkc_hirc_en也配置为不使能。即touch ip及控制逻辑模块工作在低功耗模式下,每次信号tkc_start和等待间隔逻辑信号共同有效时,开启信号tkc_bg_en和经过计数器对信号bgap_dly计数后控制信号tkc_hirc_en为有效。

55.如图9所示,管理系统的低功耗工作ip模块和touch ip及控制逻辑模块在空闲模式下,任何被使能的中断事件或复位都可以终止空闲模式。在发生中断事件的情况下,中断控制器请求cpu内核模块退出空闲模式之后,会使cpu内核模块立刻进入中断服务程序。

56.图9示出的是关于cpu内核模块和低功耗工作ip模块以及touch ip及控制逻辑模块的控制使能信号的产生,即使能信号clk_cpu_en以及使能信号clk_per_en的唤醒逻辑控制示意图,当进入空闲(idle)、停止(stop)、睡眠(sleep)模式时,没有唤醒事件及其他相应唤醒cpu内核模块的工作时钟产生时,使能信号clk_cpu_en为0,即cpu内核模块的时钟信号不工作,当唤醒事件信号pmuintreq产生时,使能信号clk_cpu_en为1,即会唤醒时钟信号clk_cpu。同理,时钟信号clk_per只有在停止(stop)和睡眠(sleep)模式的低功耗模式下被关断和唤醒开启。

57.前述对本发明的具体示例性实施方案的描述是为了说明和例证的目的。这些描述并非想将本发明限定为所公开的精确形式,并且很显然,根据上述教导,可以进行很多改变和变化。对示例性实施例进行选择和描述的目的在于解释本发明的特定原理及其实际应用,从而使得本领域的技术人员能够实现并利用本发明的各种不同的示例性实施方案以及各种不同的选择和改变。本发明的范围意在由权利要求书及其等同形式所限定。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。