技术特征:

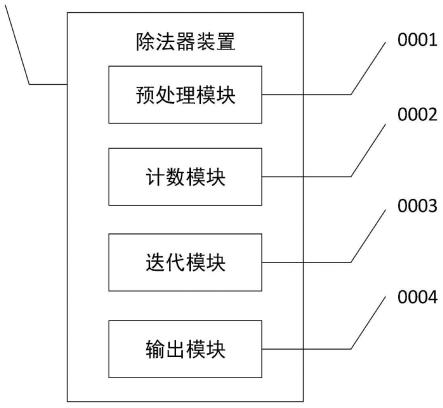

1.一种针对商位宽固定的情况的除法器装置,其特征在于,包括预处理模块、循环计数模块、迭代运算模块、输出模块。所述预处理模块,用于对输入的被除数和除数进行预处理,将被除数左移一个比特,低位补0,得到第一数据,除数左移数据位宽个比特,低位补0,得到第二数据;其中,所述数据位宽为所述商的位宽。所述计数模块,用于对运算周期进行计数,计数值可以表示商已经更新的位数。设置一个初始值为0的计数值,当除法使能信号拉高时,每个时钟周期,计数值在原来的基础上加1;当收到除法运算完成的标志信号时,计数值清零;其余情况下计数值保持不变。所述迭代运算模块,按照下面的步骤执行迭代的运算。s1:当计数值为0时,执行s1,比较所述第一数据和第二数据的大小:若所述第一数据大于或等于第二数据,则将第一数据左移一个比特,低位补0,再减去第二数据,两者的差再左移一个比特,低位补0,将运算结果存入预设寄存器,所述预设寄存器的值作为第三数据,同时将所述商寄存器的最高位赋值为1;若所述第一数据小于第二数据,则将第一数据左移一个比特再低位补0的运算结果存入所述预设寄存器,预测寄存器的值作为第三数据,同时将所述商寄存器的最高位赋值为0;s2:当计数值非0时,执行s2,比较所述第三数据和所述第二数据的大小:若所述第三数据大于所述第二数据,则将第三数据左移一个比特再减去第二数据,两者的差再左移一个比特,低位补0,将运算结果存入预设寄存器,预设寄存器的值作为更新的第三数据,同时将商寄存器的某一数据位赋值为1,所述数据位在商寄存器中的位数为:商的位宽与所述计数值的差,所述的位数按照从低位到高位的顺序进行计算,最低位对应的位数为第1位;若所述第三数据小于第二数据,则将第三数据左移一个比特再低位补0的运算结果存入所述预设寄存器,预测寄存器的值作为更新的第三数据,同时将所述商寄存器的所述数据位赋值为0;若所述第三数据等于第二数据,则将第三数据清零,同时将所述商寄存器的所述数据位赋值为1。所述输出模块,对除法运算结束的条件进行判断,当满足条件时,输出除法运算结束标志以及除法运算结果。2.如权利要求1所述商位宽固定的除法器装置,其特征在于:所述预处理模块采集到除法开始信号的上升沿时,则将被除数左移一个比特,低位补0,得到第一数据,除数左移数据位宽个比特,低位补0,得到第二数据。3.如权利要求1所述商位宽固定的除法器装置,其特征在于:所述预处理模块与所述计数模块连接,当采集到除法开始信号的上升沿时,将除法使能信号拉高,并送入所述计数模块;当采集到所述除法结束标志信号的上升沿,将除法使能信号拉低。4.如权利要求1所述商位宽固定的除法器装置,其特征在于:所述预处理模块为数据配置参数;其中,所述配置参数包括所述第一数据、第二数据的位宽以及所述计数值的位宽。5.如权利要求1所述商位宽固定的除法器装置,其特征在于:所述预处理模块与所述迭代运算模块连接,将所述的除法使能信号以及所述第一数据、所述第二数据输出至所述迭代运算模块。

6.如权利要求1所述商位宽固定的除法器装置,其特征在于:所述计数模块,用于在接收到所述除法使能信号后,从初始值0开始计数,每个时钟上升沿时自加1;在接收到表示运算结束的有效标志信号后,将计数值清零。7.如权利要求6所述商位宽固定的除法器装置,其特征在于:所述计数模块,用于记录s1和s2的执行次数。8.如权利要求1所述商位宽固定的除法器装置,其特征在于:所述计数模块与所述输出模块连接,将计数器的计数值输出至所述输出模块,作为判断除法结束的条件之一。9.如权利要求1所述商位宽固定的除法器装置,其特征在于:所述迭代运算模块,用于在接收到所述除法使能信号后,执行所述s1和s2;在接收到所述除法结束标志信号后,停止迭代运算。10.如权利要求1所述商位宽固定的除法器装置,其特征在于:所述输出模块,用于与所述迭代运算模块和所述计数模块连接,在接收到所述计数模块送入的计数值以及所述迭代运算模块送入的第三数据和第二数据后,判断除法是否结束,若计数值等于商的位宽减一或者所述第三数据等于所述第二数据,则产生表示除法运算结束的有效标志信号,并将该有效标志信号输出至所述计数模块,同时将所述除法运算结果赋值给除法器的输出。

技术总结

本发明属于数字集成电路设计领域,具体涉及一种用于商位宽固定的除法运算的除法器装置。本发明采用串行的思想实现除法,按照从最高位到最低位的顺序,串行地对商的每一位进行赋值。本发明设计的除法器装置,将除法运算转化为相对简单的比较、减法以及移位运算,方便硬件实现,也减小了除法运算电路消耗的面积;同时每个时钟周期对商的一位进行赋值,运算消耗的时钟周期数不超过商的位数,在被除数和除数位宽均大于商的位宽时,相比传统的基于减法的除法运算算法,可以节约运算时间;另外,每个时钟周期的运算最多仅包括一次比较、减法和移位,大大减小了电路中组合逻辑路径的延迟,更容易满足时序的要求。容易满足时序的要求。容易满足时序的要求。

技术研发人员:谢小东 张甜

受保护的技术使用者:电子科技大学

技术研发日:2022.11.17

技术公布日:2023/3/3

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。