1.本公开涉及固态成像装置和成像装置。

背景技术:

2.与成像装置等相关的常规技术已经使用同步固态成像装置,该同步固态成像装置与同步信号(诸如垂直同步信号)同步地捕获图像数据(帧)。这种典型的同步固态成像装置仅能够在每个同步信号周期(例如,1/60秒)获取图像数据,使得在与运输、机器人等相关的领域中需要时难以处理更快的处理。为了解决这个问题,已经提出了一种固态成像装置,该固态成像装置针对每个像素地址检测像素的亮度的变化量超过阈值的事件作为地址事件(例如,参考专利文献1)。以这种方式检测每个像素的地址事件的固态成像装置也称为基于事件的视觉传感器(evs)或动态视觉传感器(dvs)。

3.引用列表

4.专利文献

5.专利文献1:jp 5244587 b2

技术实现要素:

6.技术问题

7.然而,在传统的evs中,存在由于噪声的产生、切换操作模式时电位的波动等导致操作变得不稳定的情况。

8.鉴于此,本公开提出了能够抑制不稳定操作的发生的固态成像装置和成像装置。

9.问题的解决方案

10.为了解决上述问题,根据本公开的一个方面的固态成像装置包括:多个像素,每个像素输出入射光的亮度变化;以及检测电路,基于从每个像素输出的亮度变化输出事件信号,其中,每个像素包括:光电转换元件,根据入射光量产生电荷;对数转换电路,连接到光电转换元件,并将从光电转换元件流出的光电流转换为对应于光电流的对数值的电压信号;以及第一晶体管,其漏极连接到对数转换电路的感测节点。

附图说明

11.图1是示出根据第一实施方式的成像装置的配置示例的框图。

12.图2是示出根据第一实施方式的固态成像装置的堆叠结构的示例的示图。

13.图3是根据第一实施方式的光接收芯片的平面图的示例。

14.图4是根据第一实施方式的检测芯片的平面图的示例。

15.图5是根据第一实施方式的地址事件检测部的平面图的示例;

16.图6是示出根据第一实施方式的对数响应部的配置示例的电路图。

17.图7是示出了根据第一实施方式的对数响应部的另一配置示例的电路图。

18.图8是示出了根据第一实施方式的读出电路的示意性配置示例的电路图。

19.图9是示出了根据第一实施方式的响应电路的示意性配置示例的电路图。

20.图10是示出了根据第一实施方式的检测块的配置示例的框图。

21.图11是示出了根据第一实施方式的差分器的配置示例的电路图。

22.图12是示出根据第一实施方式的比较部的配置示例的电路图。

23.图13是示出根据第一实施方式的差分器、选择器和比较器的配置示例的电路图。

24.图14是示出了根据第一实施方式的在evs模式的行驱动电路的控制的示例的时序图。

25.图15是示出根据第一实施方式的在cis模式下的行驱动电路的控制的示例的时序图。

26.图16是示出根据第一实施方式的检测像素和检测电路的配置示例的框图。

27.图17是示出根据第一实施方式的固态成像装置的操作的示例的流程图。

28.图18是示出根据第一实施方式的变形例的检测像素和检测电路的配置示例的框图。

29.图19是示出根据第一实施方式的变形例的行驱动电路的控制的示例的时序图。

30.图20是示出了模式转变时的死区时间段的波形图。

31.图21是示出根据第一实施方式的响应电路的配置示例的电路图。

32.图22是示出根据第一实施方式的第一变形例的响应电路的配置示例的电路图。

33.图23是示出根据第一实施方式的第二变形例的响应电路的配置示例的电路图。

34.图24是示出根据第一实施方式的第三变形例的响应电路的配置示例的电路图。

35.图25是示出根据第一实施方式的第四变形例的响应电路的配置示例的电路图。

36.图26是示出根据第一实施方式的第五变形例的响应电路的配置示例的电路图。

37.图27是示出根据第一实施方式的第六变形例的响应电路的配置示例的电路图。

38.图28是示出根据第一实施方式的第七变形例的响应电路的配置示例的电路图。

39.图29是示出根据第一实施方式的第八变形例的响应电路的配置示例的电路图。

40.图30是示出根据第一实施方式的从cis模式转变到evs模式时的操作示例的时序图。

41.图31是示出根据第一实施方式的成像装置的操作示例的流程图。

42.图32是示出根据第一实施方式的第一共享示例的共享块的电路配置示例的电路图。

43.图33是示出根据第一实施方式的第二共享示例的共享块的电路配置示例的电路图。

44.图34是示出根据第一实施方式的第三共享示例的共享块的电路配置示例的电路图。

45.图35是示出根据第一实施方式的第四共享示例的共享块的电路配置示例的电路图。

46.图36是示出根据第一实施方式的第一布局示例的共享块的布局示例的平面图。

47.图37是示出根据第一实施方式的第二布局示例的共享块的布局示例的平面图。

48.图38是示出根据第二实施方式的第一控制示例的从cis模式转变到evs模式时的操作示例的时序图。

49.图39是示出根据第二实施方式的第二控制示例的从cis模式转变到evs模式时的操作示例的时序图。

50.图40是示出根据第二实施方式的第三控制示例的从cis模式转变到evs模式时的操作示例的时序图。

51.图41是示出根据第二实施方式的第四控制示例的从cis模式转变到evs模式时的操作示例的时序图。

52.图42是示出根据第二实施方式的第五控制示例的从cis模式转变到evs模式时的操作示例的时序图。

53.图43是示出根据第二实施方式的第六控制示例的从cis模式转变到evs模式时的操作示例的时序图。

54.图44是示出根据第二实施方式的第七控制示例的从cis模式转变到evs模式时的操作示例的时序图。

55.图45是示出根据第三实施方式的响应电路的配置示例的电路图。

56.图46是示出根据第三实施方式的响应电路的变形例的电路图。

57.图47是示出根据第三实施方式的从cis模式转变到evs模式时的操作示例的时序图。

58.图48是示出根据第三实施方式的成像装置的操作示例的流程图。

59.图49是示出根据第四实施方式的响应电路的配置示例的电路图。

60.图50是示出根据第四实施方式的响应电路的变形例的电路图。

61.图51是示出根据第四实施方式的从cis模式转变到evs模式时的操作示例的时序图。

62.图52是示出根据第四实施方式的成像装置的操作示例的流程图。

63.图53是根据第五实施方式的检测芯片的平面图的示例。

64.图54是示出根据第五实施方式的共享块的配置示例的电路图。

65.图55为示出根据第五实施方式的第一共享示例的共享块的电路配置示例的电路图。

66.图56为示出根据第五实施方式的第二共享示例的共享块的电路配置示例的电路图。

67.图57为示出根据第五实施方式的第三共享示例的共享块的电路配置示例的电路图。

68.图58是示出根据第六实施方式的响应电路的配置示例的电路图。

69.图59是示出根据第七实施方式的固态成像装置中的检测芯片的示意性配置示例的平面图。

70.图60是示出根据第八实施方式的第一布局变形例的共享块的布局示例的平面图。

71.图61是示出根据第八实施方式的第二布局变形例的共享块的布局示例的平面图。

72.图62是示出根据第八实施方式的第三布局变形例的共享块的布局示例的平面图。

73.图63是示出根据第八实施方式的第四布局变形例的共享块的布局示例的平面图。

74.图64是示出根据第八实施方式的第五布局变形例的共享块的布局示例的平面图。

75.图65是示出了根据第八实施方式的第六布局变形例的共享块的布局示例的平面

图。

76.图66是示出根据第八实施方式的第七布局变形例的共享块的布局示例的平面图。

77.图67是示出根据第九实施方式的第一示例的配线结构的截面图。

78.图68是示出根据第九实施方式的第二示例的配线结构的截面图。

79.图69是示出根据第九实施方式的第三示例的配线结构的截面图。

80.图70是示出根据第九实施方式的第四示例的配线结构的截面图。

81.图71是示出根据第九实施方式的第一配线层的配线布局示例的平面图。

82.图72是示出根据第九实施方式的第二配线层的配线布局示例的平面图。

83.图73是示出根据第九实施方式的第三配线层的配线布局示例的平面图。

84.图74是示出根据第九实施方式的第四配线层的配线布局示例的平面图。

85.图75是示出了沿着图71至图74中的线a-a’截取的截面结构示例的截面图。

86.图76是示出根据第九实施方式的变形例的第一配线层的配线布局示例的平面图。

87.图77是示出在第十实施方式中示出的共享块的电路配置示例的示图。

88.图78为示出在第十实施方式中示出的传输晶体管/开关晶体管与每个驱动线之间的连接的示例的示图。

89.图79是示出根据第十实施方式的配线结构的示例的截面图。

90.图80是示出根据第一实施方式的第一配线层的配线布局示例的平面图。

91.图81是示出根据第一实施方式的第二配线层的配线布局示例的平面图。

92.图82是示出根据第一实施方式的第三配线层的配线布局示例的平面图。

93.图83是示出根据第一实施方式的第四配线层的配线布局示例的平面图。

94.图84是描述车辆控制系统的示意性配置的示例的框图。

95.图85是帮助说明车外信息检测单元和成像部的安装位置的示例的示图。

具体实施方式

96.下面将参考附图详细描述本公开的实施方式。在下述实施方式的每一个中,相同的部件由相同的参考符号表示,并且将省略其重复描述。

97.将按照以下顺序描述本公开。

98.1.第一实施方式

99.1.1成像装置的配置示例

100.1.2固态成像装置的配置示例

101.1.3对数响应部的配置示例

102.1.3.1对数响应部的变形例

103.1.4像素电路的配置示例

104.1.5响应电路的基本配置示例

105.1.6检测块的配置示例

106.1.6.1差分器、选择器以及比较器的配置示例

107.1.7行驱动电路的控制示例

108.1.7.1evs模式

109.1.7.2cis模式

110.1.8检测像素和检测电路的配置示例

111.1.8.1evs模式下的固态成像装置的操作示例

112.1.9检测像素和检测电路的变形例

113.1.9.1根据变形例的行驱动电路的控制示例

114.1.10模式转变期间的死区时间段

115.1.11响应电路的配置示例

116.1.12响应电路的变形例

117.1.12.1第一变形例

118.1.12.2第二变形例

119.1.12.3第三变形例

120.1.12.4第四变形例

121.1.12.5第五变形例

122.1.12.6第六变形例

123.1.12.7第七变形例

124.1.12.8第八变形例

125.1.13从cis模式至evs模式的转变

126.1.14操作流程

127.1.15电路共享

128.1.15.1第一共享示例

129.1.15.2第二共享示例

130.1.15.3第三共享示例

131.1.15.4第四共享示例

132.1.16使用电路共享的合并模式和全像素模式1.17共享块的布局

133.1.17.1第一布局示例

134.1.17.2第二布局示例

135.1.18作用和效果

136.2.第二实施方式

137.2.1第一控制示例

138.2.2第二控制示例

139.2.3第三控制示例

140.2.4第四控制示例

141.2.5第五控制示例

142.2.6第六控制示例

143.2.7第七控制示例

144.2.8作用和效果

145.3.第三实施方式

146.3.1响应电路的配置示例

147.3.1.1响应电路的变形例

148.3.2从cis模式至evs模式的转变

149.3.3操作流程

150.3.4作用和效果

151.4.第四实施方式

152.4.1响应电路的配置示例

153.4.1.1响应电路的变形例

154.4.2从cis模式至evs模式的转变

155.4.3操作流程

156.4.4作用和效果

157.5.第五实施方式

158.5.1检测芯片的布局示例

159.5.2共享块的基本配置示例

160.5.3电路共享的合并模式

161.5.3.1第一共享示例

162.5.3.2第二共享示例

163.5.3.3第三共享示例

164.5.4作用和效果

165.6.第六实施方式

166.6.1响应电路的配置示例

167.6.2作用和效果

168.7.第七实施方式

169.8.第八实施方式

170.8.1第一布局变形例

171.8.2第二布局变形例

172.8.3第三布局变形例

173.8.4第四布局变形例

174.8.5第五布局变形例

175.8.6第六布局变形例

176.8.7第七布局变形例

177.9.第九实施方式

178.9.1配线结构示例

179.9.2效果

180.9.3配线布局的具体示例

181.10.第十实施方式

182.10.1截面结构和配线布局示例

183.11.应用于移动体的示例

184.1.第一实施方式

185.首先,将参考附图详细描述第一实施方式。在evs中,通过切换在检测一个地址事件时使用的光电转换元件的数量,可以实现关于地址事件改变灵敏度和分辨率的各种操作模式。此外,在evs中,通过并入用于从光电转换元件生成灰度数据的读出电路,除了检测地

址事件的操作模式之外,还可以实现生成灰度或彩色图像数据的操作模式。

186.然而,当在传统evs中切换操作模式时,用于检测地址事件的电路中的感测节点的电位有时偏离期望范围。感测节点的电位从正常范围的偏离导致地址事件的检测失败。因此,传统的evs具有出现死区时间段的的问题,在该死区时间段中,直到感测节点的电位稳定在正常范围内才能检测到地址事件。

187.鉴于此,本实施方式提出了能够抑制模式切换时的死区时间段的固态成像装置和成像装置。

188.1.1成像装置的配置示例

189.图1是示出根据本公开的第一实施方式的成像装置100的配置示例的框图。成像装置100包括光学部110、固态成像装置200、记录部120和控制部130。假设成像装置100的示例包括诸如安装在工业机器人上的照相机和车载照相机的装置。

190.光学部110会聚入射光并且将光引导至固态成像装置200。固态成像装置200光电转换入射光以产生图像数据。固态成像装置200对生成的图像数据执行预定信号处理(诸如,图像识别处理),并且通过信号线209将处理的数据输出至记录部120。

191.例如,记录部120包括诸如闪存的装置,并且记录从固态成像装置200输出的数据和从控制部130输出的数据。

192.例如,控制部130包括诸如应用处理器的信息处理装置,并且控制固态成像装置200输出图像数据。

193.1.2固态成像装置的配置示例

194.(堆叠结构的示例)

195.图2是示出根据本实施方式的固态成像装置200的堆叠结构的示例的示图。固态成像装置200包括检测芯片202和堆叠在检测芯片202上的光接收芯片201。这些芯片通过诸如通孔的连接部彼此电连接。除了通孔之外,cu-cu接合或凸块可用于连接。例如,光接收芯片201可以是权利要求中的第一芯片的示例,并且检测芯片202可以是权利要求中的第二芯片的示例。

196.(光接收芯片的布局示例)

197.图3是根据本实施方式的光接收芯片的平面图的示例。光接收芯片201包括光接收部220和通孔布置部211、212和213。

198.通孔布置部211、212和213是布置连接至检测芯片202的通孔的部分。光接收部220是其中多个共享块221以二维格状图案布置的地方。

199.在每个共享块221中,布置一个或多个响应电路301。例如,针对每个共享块221以2行

×

2列图案布置四个响应电路301。这四个响应电路301共享检测芯片202上的电路。以下将描述共享电路的细节。注意,共享块221中的响应电路301的数量不限于四个。此外,每个响应电路301中的光电转换元件311除外的电路配置的一部分或全部可以布置在检测芯片202侧。

200.如下所述,响应电路301包括:对数响应部310,根据对数值将从光电转换元件311流出的光电流转换为电压信号vpr;以及像素电路370,根据光电转换元件311中累积的电荷的电荷量生成电压值的像素信号(对应于灰度数据)。

201.包括行地址和列地址的像素地址被分配给每个响应电路301。应注意,本公开中的

像素可具有基于下面将描述的光电转换元件311的配置,并且在本实施方式中,例如,可具有被称为下面将描述的检测像素和/或灰度像素的配置。

202.(检测芯片的布局示例)

203.图4是根据本实施方式的检测芯片的平面图的示例。检测芯片202包括通孔布置部231、232和233、信号处理电路240、行驱动电路251、列驱动电路252、地址事件检测部260以及列模数转换器(列adc)270。通孔布置部231、232和233是布置连接至光接收芯片201的通孔的部分。

204.地址事件检测部260检测每个响应电路301(更具体地,每个对数响应部310)的地址事件的存在与否,并且生成指示检测结果的检测信号。

205.行驱动电路251选择行地址并且使地址事件检测部260输出与行地址对应的检测信号。

206.列驱动电路252选择列地址并且使地址事件检测部260输出与列地址对应的检测信号。

207.信号处理电路240对从地址事件检测部260输出的检测信号执行预定信号处理。信号处理电路240将检测信号作为像素信号布置为二维格状图案,并且为每个像素生成具有2位信息的图像数据。信号处理电路240然后对图像数据执行诸如图像识别处理等的信号处理。

208.此外,列adc 270包括例如与为每个响应电路301(更具体地,为每个像素电路370)设置的每个垂直信号线vsl一一对应的ad转换器,并且对通过垂直信号线vsl从每个像素电路370输入的模拟像素信号执行模数(ad)转换。随后,列adc 270将经历ad转换的数字信号提供至信号处理电路240。信号处理电路240对包括数字信号的图像数据执行预定图像处理。应注意,列adc 270可包括例如相关双采样(cds)电路并且可减少包括在数字像素信号中的ktc噪声。

209.(检测芯片的布局示例)

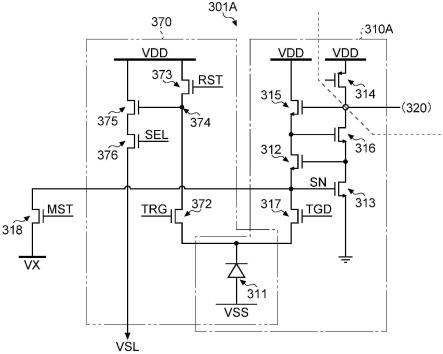

210.图5是根据本实施方式的地址事件检测部260的平面图的示例。地址事件检测部260是其中布置了多个检测块320的部分。在光接收芯片201上为每个共享块221布置检测块320。在共享块221的数量是n(n是整数)的情况下,布置n个检测块320。每个检测块320连接到对应的共享块221。

211.1.3对数响应部的配置示例

212.图6是示出根据本实施方式的对数响应部的基本配置示例的电路图。如图6所示,包括在响应电路301中的对数响应部310包括光电转换元件311、n沟道金属氧化物半导体(nmos)晶体管312和313以及p沟道mos(pmos)晶体管314。其中,两个nmos晶体管312和313例如构成将从光电转换元件311流出的光电流转换为与光电流的对数值对应的电压信号的对数转换电路。连接到nmos晶体管313的栅极的配线和来自光电转换元件311的光电流流过的配线用作检测地址事件时的感测节点sn。nmos晶体管313可例如对应于权利要求中的第二晶体管,且nmos晶体管312可例如对应于权利要求中的第三晶体管。

213.此外,pmos晶体管314作为用于包括两个nmos晶体管312和313的对数转换电路的负载mos晶体管来操作。注意,光电转换元件311和nmos晶体管312和313例如可以被布置在光接收芯片201上,并且pmos晶体管314可以被布置在检测芯片202上。

214.nmos晶体管312具有连接到光电转换元件311的阴极的源极,同时具有连接到电源端的漏极。pmos晶体管314和nmos晶体管313在电源端和接地端之间串联连接。此外,pmos晶体管314和nmos晶体管313的连接点连接到nmos晶体管312的栅极和检测块320的输入端,并且用作将电压信号vpr输出到检测块320的输出节点。此外,预定的偏置电压vbias1被施加到pmos晶体管314的栅极。

215.nmos晶体管312和313的漏极连接到电源侧,并且这样的电路被称为源极跟随器。以环形连接的两个源极跟随器将来自光电转换元件311的光电流转换为对应于对数值的电压信号vpr。此外,pmos晶体管314向nmos晶体管313提供恒定电流。

216.注意,光接收芯片201的接地和检测芯片202的接地可彼此隔离以对抗干扰。

217.1.3.1对数响应部的变形例

218.尽管图6是源极跟随器类型对数响应部310的配置的示例,但是该部的配置不限于这种示例。图7是示出根据本实施方式的变形例的对数响应部的基本配置示例的电路图。如图7所示,例如,对数响应部310a具有被称为增益升压型电路配置的配置,与图6所示的源极跟随器型电路配置相比,图7的对数响应部310a包括串联连接在nmos晶体管312和电源线之间的附加nmos晶体管315以及串联连接在nmos晶体管313和pmos晶体管314之间的附加nmos晶体管316。四个nmos晶体管312、313、315和316构成例如对数转换电路,该对数转换电路根据光电流的对数值将从光电转换元件311流出的光电流转换为电压信号vpr。

219.以这种方式,即使使用增益升压型对数响应部310a,也可以将来自光电转换元件311的光电流转换为与电荷量相对应的对数值的电压信号vpr。

220.1.4像素电路的配置示例

221.图8是示出根据本实施方式的像素电路的示意性配置示例的电路图。如图8所示,响应电路301中的像素电路370包括传输晶体管372、复位晶体管373、放大晶体管375以及选择晶体管376。与传输晶体管372的漏极、复位晶体管373的源极和放大晶体管375的栅极连接的节点用作具有电流-电压转换功能(即,将累积的电荷转换成与电荷量相对应的电压的功能)的浮置扩散区(fd)374。传输晶体管372可例如对应于权利要求中的第五晶体管。

222.像素电路370与相同响应电路301中的对数响应部310/310a共享光电转换元件311,并且操作为根据由光电转换元件311接收的光量生成像素信号的灰度像素。

223.例如,复位晶体管373的漏极和放大晶体管375的漏极连接至电源电压vdd。然而,复位晶体管373的漏极可连接到例如不同于电源电压vdd的重置电压。放大晶体管375的源极连接至选择晶体管376的漏极,并且选择晶体管376的源极连接至用于将模拟像素信号输入至下面描述的列adc 270的垂直信号线vsl。

224.当读取像素信号时,将高电平传输信号trg从行驱动电路251施加至传输晶体管372的栅极。这接通传输晶体管372,使得累积在光电转换元件311的阴极中的电荷通过传输晶体管372传输至浮置扩散区374。结果,具有与在浮置扩散区374中累积的电荷的电荷量相对应的电压值的像素信号出现在放大晶体管375的源极处。随后,通过将从行驱动电路251施加至选择晶体管376的栅极的选择信号sel设置为高电平,出现在放大晶体管375的源极中的像素信号出现在垂直信号线vsl中。

225.此外,当释放在浮置扩散区374中累积的电荷以重置浮置扩散区374时,从行驱动电路251向复位晶体管373的栅极施加高电平重置信号rst。这允许在浮置扩散区374中累积

的电荷通过复位晶体管373释放至电源侧(fd重置)。此时,通过在相同周期期间接通传输晶体管372,还可以将光电转换元件311的阴极中累积的电荷释放至电源侧(pd重置)。

226.在每个共享块221中,当读取灰度图像数据时同时连接至像素电路370的光电转换元件311的数量,即,在相同周期期间接通的传输晶体管372的数量不限于一个,并且可以是多个。例如,当在每个共享块221中读取高分辨率灰度图像数据时,传输晶体管372可以以时分方式顺次地连接到像素电路370,并且当在低亮度等下以扩展的动态范围执行读取时(在合并时),两个或更多个传输晶体管372可以在相同周期期间接通。

227.1.5响应电路的基本配置示例

228.接下来,将描述包括对数响应部310/310a和像素电路370的响应电路301的基本配置示例。图9是示出根据本实施方式的响应电路的基本配置示例的电路图。尽管以下描述是使用对数响应部310a的示例性情况,但是配置不限于此,并且可允许采用根据电荷量将来自光电转换元件311的光电流转换为对数值的电压信号vpr的各种电路,诸如,对数响应部310。

229.如图9所示,根据本实施方式的响应电路301具有其中图7中所示的对数响应部310a和图8中所示的像素电路370共享光电转换元件311的配置。然而,响应电路301还包括用于在evs模式和cis模式之间切换的开关晶体管317。开关晶体管317例如可以是nmos晶体管。开关晶体管317例如可以对应于权利要求中的第四晶体管。

230.在evs模式中,例如,行驱动电路251将高电平切换信号恒定地施加到开关晶体管317的栅极。另一方面,例如,行驱动电路251将低电平传输信号trg恒定地施加至传输晶体管372的栅极。这导致形成从光电转换元件311流出的光电流通过开关晶体管317流到感测节点sn侧的电流路径。

231.另一方面,在cis模式中,例如,低电平切换信号被恒定地从行驱动电路251施加到开关晶体管317的栅极。另一方面,例如,根据预定控制操作的指示高电平的传输信号trg从行驱动电路251施加至传输晶体管372的栅极。利用该操作,累积在光电转换元件311中的电荷在预定定时被传送到像素电路370的浮置扩散区374。

232.1.6检测块的配置示例

233.图10是示出了根据本实施方式的检测块320的配置示例的框图。检测块320包括多个缓冲器330、多个差分器340、选择部400、比较部500和传送电路360。缓冲器330和差分器340针对共享块221中的每个对数响应部310设置。例如,当在共享块221中存在四个对数响应部310时,布置四个缓冲器330和四个差分器340。

234.缓冲器330将电压信号从对应的对数响应部310输出至差分器340。缓冲器330可以改善用于驱动后续级的驱动力。此外,缓冲器330可确保与后续阶段中的切换操作相关联的噪声的隔离。

235.差分器340获得电压信号的变化量,即,入射在光电转换元件311上的光的亮度变化作为差分信号。差分器340通过缓冲器330从相应的对数响应部310接收电压信号,并且通过差分获得电压信号的变化量。随后,差分器340将差分信号供应至选择部400。检测块320中的第m(m是1至m的整数)个差分信号sin被定义为sinm。例如,差分器340可对应于权利要求中的第一电路。

236.选择部400根据来自行驱动电路251的选择信号来选择m个差分信号中的一个。选

择部400包括选择器410和420。

237.m个差分信号sin被输入到选择器410。选择器410根据选择信号选择这些差分信号sin中的一个,并且将所选择的差分信号sin作为sout 供应至比较部500。m个差分信号sin也被输入到选择器420。选择器420根据选择信号选择这些差分信号sin中的一个,并且将所选择的差分信号sin作为sout-提供给比较部500。

238.比较部500将由选择部400选择的差分信号(即,变化量)与预定阈值进行比较。比较部500将表示比较结果的信号作为检测信号提供至传送电路360。例如,比较部500可对应于权利要求中的第二电路。

239.传送电路360根据来自列驱动电路252的列驱动信号将检测信号传送到信号处理电路240。

240.(差分器的配置示例)

241.图11是示出了根据本实施方式的差分器340的配置示例的电路图。差分器340包括电容器341和343、反相器342和开关344。

242.电容器341的一端连接到缓冲器330的输出端,另一端连接到反相器342的输入端。电容器343并联连接到反相器342。开关344根据行驱动信号断开和闭合连接电容器343的两端的路径。

243.反相器342将通过电容器341输入的电压信号反相。反相器342将经反相的信号输出至选择部400。

244.当开关344接通时,电压信号v

init

被输入到电容器341的缓冲器330侧,使得相对侧成为虚拟接地端。为了方便起见,假设虚拟接地端的电位为零。此时,当电容器341的电容为cl时,电容器341中累积的电位q

init

由下面的公式(1)表示。另一方面,由于电容器343的两端短路,因此累积的电荷为0。

245.q

init

=c1

×vinit

ꢀꢀꢀꢀ

(1)

246.接着,假设开关344断开且电容器341的缓冲器330侧的电压变成电压v

after

,电容器341中累积的电荷q

after

用下式(2)表示。

247.q

after

=c1

×vafter

ꢀꢀꢀꢀꢀ

(2)

248.另一方面,当输出电压为v

after

时,电容器343中累积的电荷q2由以下公式(3)表示。

249.q2=-c2

×vout

ꢀꢀꢀ

(3)

250.此时,由于电容器341和343的总电荷量不改变,因此下面的公式(4)成立。

251.q

init

=q

after

q2

ꢀꢀꢀ

(4)

252.当式(1)至式(3)代入式(4)时,那么结果可以转换成以下式(5)。

[0253]vout

=-(c1/c2)

×

(v

after-v

init

)

ꢀꢀꢀꢀꢀ

(5)

[0254]

公式(5)表示电压信号的减法运算,其中,减法结果的增益为c1/c2。由于最大增益在通常情况下是期望的,因此优选地将c1设计为大并且将c2设计为小。另一方面,过小的c2将增加ktc噪声并且导致噪声特性的劣化。因此,c2的容量减小限于噪声容许范围。此外,因为为每个像素设置差分器340,所以电容c1和c2具有面积限制。考虑到这些,例如,c1被设置为20至200飞法(ff)的值,并且c2被设置为1至20飞法(ff)的值。

[0255]

(比较部的配置示例)

[0256]

图12是示出根据本实施方式的比较部500的配置示例的电路图。比较部500包括比

较器510和520。

[0257]

比较器510将来自选择器410的差分信号sout 与预定的上限阈值vrefp进行比较。比较器510将比较结果作为检测信号det 提供至传送电路360。检测信号det 表示存在与否开启事件。这里,开启事件表示亮度的变化量超过预定的上限阈值的事件。

[0258]

比较器520将来自选择器420的差分信号sout-与低于上限阈值vrefp的下限阈值vrefn进行比较。比较器520将比较的结果作为检测信号det-提供至传送电路360。检测信号det-指示关闭事件的存在与否。这里,关闭事件表示亮度的变化量小于预定的下限阈值的事件。应注意,尽管比较部500检测开启事件和关闭事件两者的存在与否,但是也可仅检测开启事件和关闭事件中的一个。

[0259]

应注意,例如,比较器510可以是权利要求中所描述的第一比较器的示例,并且比较器520可以是权利要求中所描述的第二比较器的示例。例如,上限阈值可以是在权利要求中描述的第一阈值的示例,并且下限阈值可以是在权利要求中描述的第二阈值的示例。

[0260]

1.6.1差分器、选择器以及比较器的配置示例

[0261]

图13是示出了根据本实施方式的检测块320中的差分器340、选择器410以及比较器510的配置示例的电路图。

[0262]

差分器340包括电容器341和343、pmos晶体管345和346以及nmos晶体管347。pmos晶体管345和nmos晶体管347以pmos晶体管345为电源侧串联连接在电源端和接地端之间。电容器341插入在pmos晶体管345/nmos晶体管347的栅极与缓冲器330之间。pmos晶体管345和nmos晶体管347的连接点连接到选择器410。通过该连接配置,pmos晶体管345和nmos晶体管347用作反相器342。

[0263]

此外,电容器341和pmos晶体管345并联连接在pmos晶体管346和nmos晶体管347的连接点与电容器343之间。pmos晶体管346用作开关344。

[0264]

此外,选择器410设置有多个pmos晶体管411。为每个差分器340布置pmos晶体管411。

[0265]

pmos晶体管411插入在相应的差分器340和比较器510之间。此外,选择信号sel被单独地输入到pmos晶体管411的每个栅极。第m pmos晶体管411的选择信号sel称为selm。通过这些选择信号sel,行驱动电路251可以控制接通m个pmos晶体管411中的一个并且断开其余的晶体管。此外,差分信号sout 通过接通状态下的pmos晶体管411输出到比较器510作为选择的信号。要注意的是,选择器420的电路配置与选择器410的电路配置相似。

[0266]

比较器510包括pmos晶体管511和nmos晶体管512。pmos晶体管511和nmos晶体管512串联连接在电源端和接地端之间。此外,差分信号sout 被输入到pmos晶体管511的栅极,而上限阈值vrefp的电压被输入到nmos晶体管512的栅极。检测信号det 从pmos晶体管511和nmos晶体管512的连接点输出。注意,比较器520的电路配置与比较器510的电路配置相似。

[0267]

应注意,差分器340、选择器410、以及比较器510的电路配置不限于在图13中示出的电路配置,只要它们具有参照图10描述的功能即可。例如,nmos晶体管和pmos晶体管是可互换的。

[0268]

1.7行驱动电路的控制示例

[0269]

接下来,将描述根据本实施方式的行驱动电路251的控制示例。在本实施方式中,

行驱动电路251在检测地址事件的操作模式(以下,称为evs模式)和获取灰度或彩色图像数据(以下,称为灰度图像数据)的操作模式(以下,称为cis模式)之间切换操作模式的执行。

[0270]

1.7.1evs模式

[0271]

图14是示出根据本实施方式的evs模式下的行驱动电路的控制的示例的时序图。在时刻t0,行驱动电路251通过行驱动信号l1选择第一行,并且驱动所选行的差分器340。行驱动信号l1对第一行的差分器340中的电容器343进行初始化。此外,行驱动电路251在某个时间段通过选择信号sel1选择共享块221中的2行

×

2列图案的左上方,并且驱动选择部400。通过该驱动,在第一行的奇数列中检测地址事件的存在与否。

[0272]

接下来,在时刻t1,行驱动电路251通过行驱动信号l1再次驱动第一行的差分器340。此外,行驱动电路251通过选择信号sel2在一定时间段内选择共享块221中的2行

×

2列图案的右上方。因而,在第一行的偶数列中检测地址事件的存在与否。

[0273]

在时刻t2,行驱动电路251通过行驱动信号l2驱动第二行中的差分器340。行驱动信号l2初始化第二行中的差分器340中的电容器343。此外,行驱动电路251在一定时间段内通过选择信号sel3选择共享块221中的2行

×

2列图案的左下方。通过该驱动,在第二行的奇数列中检测地址事件的存在与否。

[0274]

随后,在时刻t3,行驱动电路251通过行驱动信号l2再次驱动第二行中的差分器340。此外,行驱动电路251通过选择信号sel4在一定时间段内选择共享块221中的2行

×

2列图案的右下方。因而,在第二行的偶数列中检测地址事件的存在与否。

[0275]

此后,类似地,行驱动电路251依次选择其中布置响应电路301的行,并且通过行驱动信号驱动所选择的行。此外,每次选择了行时,行驱动电路251通过选择信号依次选择所选行的共享块221中的每个检测像素300。例如,在共享块221中布置2行

×

2列图案的检测像素300的情况下,每次选择行时,依次选择该行中的奇数列和偶数列。

[0276]

注意,行驱动电路251还可以顺次选择其中布置了共享块221的行(换言之,响应电路301的两行)。在这种情况下,每次选择行时,依次选择该行的共享块221中的四个检测像素。

[0277]

1.7.2cis模式

[0278]

图15是示出根据本实施方式的cis模式下的行驱动电路的控制的示例的时序图。如图15所示,行驱动电路251首先重置光电转换元件311中累积的电荷。具体地,行驱动电路251在时刻t11至t12的时间段期间将重置信号rst和传输信号trg设置为高电平,从而将累积在光电转换元件311中的电荷通过传输晶体管372和复位晶体管373释放至电源(vdd)侧(pd重置)。

[0279]

接下来,例如,行驱动电路251在时刻t13将选择信号sel设置成高电平,并且在时刻t13至t14之间的时间段期间将重置信号rst设置成高电平。这允许累积在浮置扩散区374中的电荷通过复位晶体管373释放至电源(vdd)侧,从而重置浮置扩散区374(fd重置)。

[0280]

在时刻t14至t15的后续时段中,在浮置扩散区374被重置的状态下出现在垂直信号线vsl中的电位由列adc 270读取为重置电平的像素信号(也称为重置信号)(重置电平读出)。例如,读取的重置信号用于列adc 270中的cds处理。

[0281]

接下来,行驱动电路251在时刻t15至t16的时段期间将传输信号trg设置为高电平。这允许累积在光电转换元件311中的电荷通过传输晶体管372传输到浮置扩散区374。应

注意,从在时刻t12处的重置信号rst的下降点至在时刻t15处的传输信号trg的上升点的时间段是累积时间段(也称为曝光时间段),在该累积时间段期间,由光电转换生成的电荷累积在光电转换元件311中。

[0282]

时刻t16至t17的后续时间段是在从光电转换元件311传送的电荷被累积在浮置扩散区374中的状态下,换言之,在基于电荷量(即,从光电转换元件311传送的电荷的量)的电压被施加到放大晶体管375的栅极的状态下,由列adc 270读取出现在垂直信号线vsl中的电位作为信号电平的像素信号的时间段。注意,列adc 270通过使用较早读取的重置信号对在时刻t16至时刻t17的时间段期间读取的像素信号进行cds处理,从而生成去除了ktc噪声等的像素信号。

[0283]

1.8检测像素和检测电路的配置示例

[0284]

图16是示出根据本实施方式的检测像素300和检测电路305的配置示例的框图。在由共享块221中的多个对数响应部310共享的检测块320中,包括选择部400、比较部500和传送电路360的电路被定义为检测电路305。此外,包括对数响应部310、缓冲器330、以及差分器340的电路被定义为检测像素300。如图所示,检测电路305由多个检测像素300共享。

[0285]

共享检测电路305的多个检测像素300的每个产生与光电流的对数值对应的电压信号。随后,检测像素300中的每一个根据行驱动信号将指示电压信号的变化量的差分信号sin输出至检测电路305。在每个检测像素300中,由对数响应部310生成对应于对数值的电压信号,而由差分器340生成差分信号。

[0286]

诸如选择信号sel1和sel2之类的选择信号被共同输入到检测电路305中的选择器410和420。检测电路305从多个检测像素300中选择选择信号所指示的检测像素的差分信号(即,变化量),并检测变化量是否超过预定阈值。检测电路305然后根据列驱动信号将检测信号传送到信号处理电路240。在检测电路305中,通过选择部400选择差分信号,并且通过比较部500执行与阈值的比较。此外,检测信号由传送电路360传输。

[0287]

这里,在典型的dvs中,比较部500和传送电路360与对数响应部310、缓冲器330和差分器340一起针对每个检测像素来布置。相反,在包括比较部500和传送电路360的检测电路305由多个检测像素300共享的上述配置中,与检测电路不被共享的情况相比,可以减小固态成像装置200的电路规模。这有助于像素的微制造。

[0288]

当特别地采用堆叠结构时,使用没有共用检测电路305的传统配置将导致与光接收芯片201相比,检测芯片202的电路规模更大。通过该配置,由于检测芯片202上的电路限制像素的密度,因此难以实现像素的微制造。然而,通过使用其中多个检测像素300共享检测电路305的配置,可以减小检测芯片202的电路规模,有利于像素的微制造。

[0289]

虽然对于每个检测像素300布置缓冲器330,但是配置不限于该配置,并且还可以省略缓冲器330。

[0290]

此外,尽管对数响应部310的光电转换元件311和nmos晶体管312和313被布置在光接收芯片201上,并且pmos晶体管314和随后的晶体管被布置在检测芯片202上,但是配置不限于该示例。例如,光电转换元件311可以单独布置在光接收芯片201上,并且其他器件可以布置在检测芯片202上。可替代地,对数响应部310可单独布置在光接收芯片201上,并且缓冲器330和后续器件可布置在检测芯片202上。仍然可替代地,对数响应部310和缓冲器330可以布置在光接收芯片201上,而差分器340和随后器件可以布置在检测芯片202上。此外,

对数响应部310、缓冲器330、以及差分器340可被布置在光接收芯片201上,并且检测电路305以及随后的电路可被布置在检测芯片202上。仍然可替代地,一直到选择部分400的部分可以布置在光接收芯片201上,而比较部500和随后的部分可以布置在检测芯片202上。

[0291]

1.8.1evs模式下的固态成像装置的操作示例

[0292]

图17是示出根据本实施方式的在evs模式下的固态成像装置的操作的示例的流程图。例如,在用于检测地址事件的存在与否的预定应用的执行的定时开始操作。

[0293]

如图17所示,在evs模式下,行驱动电路251选择行中之一(步骤s901)。行驱动电路251选择并驱动所选行中的每个共享块221中的检测像素300中的一个(步骤s902)。检测电路305检测所选择的检测像素300中地址事件存在与否(步骤s903)。在步骤s903之后,固态成像装置200重复地执行步骤s901和后续步骤。

[0294]

以这种方式,本实施方式具有这样的配置,其中检测地址事件的存在与否的检测电路305由多个检测像素300共享,使得与检测电路305不被共享的情况相比可以减小电路规模。这有助于检测像素300的微制造。

[0295]

1.9检测像素和检测电路的变形例

[0296]

在上述第一实施方式中,固态成像装置200逐一选择检测像素300,并且同时检测检测像素的开启事件和关闭事件。可替代地,固态成像装置200还可选择两个检测像素,检测其中一个检测像素的开启事件,并检测另一个检测像素的关闭事件。根据第一实施方式的变形例的固态成像装置200与第一实施方式的不同之处在于,对于两个检测像素中的一个检测像素检测开启事件并且对于另一个检测像素检测关闭事件。

[0297]

图18是示出根据本实施方式的变形例的检测像素300和检测电路305的配置示例的框图。根据第一实施方式的变形例的检测电路305与第一实施方式的检测电路的不同之处在于,诸如选择信号sel1p或sel2p的选择信号被输入到选择器410,而诸如选择信号sel1n或sel2n的选择信号被输入到选择器420。在第一实施方式的变形例中,选择两个检测像素300,并且选择器410根据选择信号sel1p、sel2p等选择一个差分信号。同时,选择器420根据选择信号sel1n、sel2n等选择另一差分信号。

[0298]

1.9.1根据变形例的行驱动电路的控制示例

[0299]

图19是示出本实施方式的变形例中的行驱动电路251的控制的示例的时序图。在时刻t0至t2处,假设选择了两个像素,即,输出差分信号sin1的检测像素300和输出差分信号sin2的检测像素300。在时刻t0至t1,行驱动电路251将选择信号sel1p和sel2n设定为高电平,将选择信号sel2p和sel1n设定为低电平。利用这种设置,针对与差分信号sin1相对应的像素检测开启事件,并且针对与差分信号sin2相对应的像素检测关闭事件。

[0300]

接着,在时刻t1至t2,行驱动电路251将选择信号sel1p和sel2n设定为低电平,将选择信号sel2p和sel1n设定为高电平。利用这种设置,针对与差分信号sin2相对应的像素检测开启事件,并且针对与差分信号sin1相对应的像素检测关闭事件。

[0301]

以这种方式,根据本实施方式的变形例,由于对于两个检测像素中的一个检测像素检测开启事件并且对于另一个检测像素检测关闭事件,所以可以在空间上同时并行地检测开启事件和关闭事件。

[0302]

1.10模式转变期间的死区时间段

[0303]

图20是示出了模式转变时的死区时间段的波形图。通过在cis模式下的上述配置,

与浮置扩散区374类似,光电转换元件311的阴极电位被重置为高于感测节点sn(pd重置)的电位(例如,0.5伏(v))的电位。在此,在光电转换元件311中产生的电荷量在低亮度下小。因此,即使在cis模式结束时,光电转换元件311的阴极电位也保持在高于感测节点sn的电位(在下文中,称为sn电位)的电位。在这种状态下,当模式转变至evs模式并且开关晶体管317接通时,高于sn电位的光电转换元件311的阴极电位与感测节点sn短路,导致sn电位的增加。如图20所示,这断开nmos晶体管312和315,使得电压信号vpr的电压电平保持卡在接地电位(gnd)上。这导致对流出光电转换元件311的光电流没有反应的死区时间段(换言之,地址事件检测失败的时间段)的发生。该死区时间段持续到sn电位稳定到预定电位为止,并且因此可以是例如大约100毫秒(ms)的长时间段。

[0304]

鉴于此,在本实施方式中,在从cis模式向evs模式的模式转变时,sn电位被固定为比正常操作时的sn电位低的电压vx。通过该配置,即使开关晶体管317转变为接通状态,也能够抑制sn电位的意外上升,能够避免nmos晶体管312、315的断开。结果,可以抑制由于电压信号vpr的电压电平卡到地电位(gnd)而引起的死区时间段。

[0305]

1.11响应电路的配置示例

[0306]

图21是示出了根据本实施方式的响应电路的配置示例的电路图。如图21所示,根据本实施方式的响应电路301a具有与上面参照图9描述的响应电路301类似的配置,其中,控制晶体管318连接至感测节点sn。例如,控制晶体管318可以是nmos晶体管。例如,控制晶体管318可以对应于权利要求中的第一晶体管。

[0307]

如上所述,控制晶体管318的漏极连接至感测节点sn,并且源极连接至电位,例如,等于或高于参考电位并且低于电源电压vdd的固定电位vx。参考电位可以是例如其上形成光电转换元件311的半导体基板的元件隔离区的阱电位vss或地电位(gnd)。此外,元件隔离区的阱电位vss可以是负电位。在这种情况下,固定电位vx的电压值是例如等于或者大于光电转换元件311的阳极电位(例如,vss或者gnd)并且等于或者小于正常操作时的感测节点sn的电位vsn的电压值。注意,正常操作时的感测节点sn的电位vsn可以是对数响应部310a正常操作时的感测节点sn的电位vsn,并且可以是例如由流过两个nmos晶体管313和316的偏置电流bias和nmos晶体管313的阈值电压确定的nmos晶体管313的栅极-源极电压vgs。

[0308]

此外,例如,将用于控制控制晶体管318的开/关的控制信号mst从行驱动电路251施加至控制晶体管318的栅极。

[0309]

在这种配置中,在从cis模式转变至evs模式时,高电平控制信号mst被施加至控制晶体管318的栅极。这接通控制晶体管318并且控制感测节点sn的sn电位被设置成固定电位vx。因此,即使开关晶体管317转变为接通状态,也可以抑制sn电位的意外增加。由此,能够避免nmos晶体管312、315断开,能够抑制因电压信号vpr的电压电平卡在接地电位(gnd)而引起的死区时间段。

[0310]

1.12响应电路的变形例

[0311]

接下来,将通过一些示例描述根据本实施方式的响应电路的变形例。

[0312]

1.12.1第一变形例

[0313]

图22是示出根据本实施方式的第一变形例的响应电路的配置示例的电路图。如图22中所示,根据第一变形例的响应电路301b具有与图21中所示的响应电路301a相似的配置,其中,在像素电路370中,控制晶体管318的漏极连接至传输晶体管372的漏极。

[0314]

在这种配置中,在从cis模式转变到evs模式时,在控制晶体管318和传输晶体管372接通的状态下,开关晶体管317接通。这允许通过控制晶体管318、传输晶体管372和开关晶体管317向感测节点sn施加固定电位vx,从而使得可以控制感测节点sn的sn电位被设置为固定电位vx。即,即使开关晶体管317转变为接通状态,也可以抑制sn电位的意外增加。

[0315]

1.12.2第二变形例

[0316]

图23是示出根据本实施方式的第二变形例的响应电路的配置示例的电路图。如图23中所示,根据第二变形例的响应电路301c具有与图22中所示的响应电路301b类似的配置,其中,控制晶体管319进一步连接在控制晶体管318的漏极与传输晶体管372与感测节点sn之间。例如,控制晶体管319可对应于权利要求中的第六晶体管。

[0317]

控制晶体管319的源极连接至控制晶体管318和传输晶体管372的漏极,并且控制晶体管319的漏极连接至感测节点sn。此外,例如,从行驱动电路251向控制晶体管319的栅极施加控制信号msm。

[0318]

在这种配置中,当从cis模式转变到evs模式时,控制晶体管318和319被接通。这允许通过控制晶体管318和319向感测节点sn施加固定电位vx,从而使得可以控制感测节点sn的sn电位被设置成固定电位vx。由此,即使在开关晶体管317转变为接通状态时,也能够抑制sn电位的意外上升。

[0319]

1.12.3第三变形例

[0320]

图24是示出根据本实施方式的第三变形例的响应电路的配置示例的电路图。如图24所示,根据第三变形例的响应电路301d具有与图21所示的响应电路301a类似的配置,其中,传输晶体管372的漏极和开关晶体管317的漏极通过控制晶体管319彼此连接。

[0321]

控制晶体管319的源极连接到传输晶体管372的漏极,并且控制晶体管319的漏极连接到开关晶体管317的漏极。此外,例如,从行驱动电路251向控制晶体管319的栅极施加控制信号msm。

[0322]

在这种配置中,当从cis模式转变到evs模式时,类似于第一变形例,控制晶体管318接通。这允许通过控制晶体管318向感测节点sn施加固定电位vx,从而使得可以控制感测节点sn的sn电位被设置成固定电位vx。由此,即使在开关晶体管317转变为接通状态时,也能够抑制sn电位的意外上升。

[0323]

1.12.4第四变形例

[0324]

图25是示出根据本实施方式的第四变形例的响应电路的配置示例的电路图。如图25所示,根据第四变形例的响应电路301e具有与图9所示的响应电路301类似的配置,其中,使用固定电位vx代替电源电压vdd作为像素电路370的重置电压(fd重置电压和pd重置电压)。

[0325]

在这种配置中,当从cis模式转变到evs模式时,复位晶体管373和传输晶体管372接通。这允许通过复位晶体管373和传输晶体管372将固定电位vx施加到感测节点sn,使得可以控制感测节点sn的sn电位被设置成固定电位vx。由此,即使在开关晶体管317转变为接通状态时,也能够抑制sn电位的意外上升。

[0326]

1.12.5第五变形例

[0327]

图26是示出根据本实施方式的第五变形例的响应电路的配置示例的电路图。如图26所示,根据第五变形例的响应电路301f具有与图25所示的响应电路301e类似的配置,其

中,传输晶体管372的漏极和开关晶体管317的漏极通过控制晶体管319彼此连接。

[0328]

在这种配置中,在从cis模式转变到evs模式时,复位晶体管373和控制晶体管319接通。这允许通过复位晶体管373和控制晶体管319向感测节点sn施加固定电位vx,使得可以将感测节点sn的sn电位控制为固定电位vx。由此,即使在开关晶体管317转变为接通状态时,也能够抑制sn电位的意外上升。

[0329]

1.12.6第六变形例

[0330]

图27是示出根据本实施方式的第六变形例的响应电路的配置示例的电路图。如图27所示,根据第六变形例的响应电路301g具有与图21所示的响应电路301a类似的配置,其中,控制晶体管318连接至光电转换元件311的阴极,而不是感测节点sn。

[0331]

在这种配置中,当从cis模式转变到evs模式时,开关晶体管317接通,以及控制晶体管318接通。这允许通过控制晶体管318和开关晶体管317向感测节点sn施加固定电位vx,使得可以将感测节点sn的sn电位控制为固定电位vx。由此,即使在开关晶体管317转变为接通状态时,也能够抑制sn电位的意外上升。

[0332]

1.12.7第七变形例

[0333]

图28是示出根据本实施方式的第七变形例的响应电路的配置示例的电路图。如图28所示,根据第七变形例的响应电路301h具有与图23所示的响应电路301c类似的配置,其中,传输晶体管372和开关晶体管317串联连接,并且感测节点sn通过控制晶体管319和开关晶体管317连接至光电转换元件311的阴极。

[0334]

在这种配置中,当从cis模式转变到evs模式时,控制晶体管318和319被接通。这允许通过控制晶体管318和319向感测节点sn施加固定电位vx,从而使得可以控制感测节点sn的sn电位被设置成固定电位vx。由此,即使在开关晶体管317转变为接通状态时,也能够抑制sn电位的意外上升。

[0335]

1.12.8第八变形例

[0336]

图29是示出根据本实施方式的第八变形例的响应电路的配置示例的电路图。如图29中所示,根据第八变形例的响应电路301i具有类似于图26中所示的响应电路301f的配置,其中,类似于第七变形例,传输晶体管372和开关晶体管317串联连接,并且感测节点sn通过控制晶体管319和开关晶体管317连接到光电转换元件311的阴极。

[0337]

在这种配置中,当从cis模式转变到evs模式时,复位晶体管373、传输晶体管372和控制晶体管319接通。这允许固定电位vx通过复位晶体管373、传输晶体管372和控制晶体管319被施加到感测节点sn,从而使得可以控制感测节点sn的sn电位被设置成固定电位vx。由此,即使在开关晶体管317转变为接通状态时,也能够抑制sn电位的意外上升。

[0338]

1.13从cis模式至evs模式的转变

[0339]

接下来,将描述从cis模式转变到evs模式时的操作。将参照图21中例示的响应电路301a给出本描述。然而,通过根据控制晶体管318的控制适当地控制控制晶体管319、传输晶体管372、复位晶体管373等,也可以通过变形例实现类似的操作。

[0340]

图30是示出根据本实施方式的从cis模式转变到evs模式时的操作示例的时序图。如图30所示,首先,在从cis模式至evs模式的转变中,在cis模式的结束时刻t0停止从行驱动电路251向构成像素电路370的传输晶体管372、选择晶体管376、以及复位晶体管373供应控制信号(trg、sel、以及rst)。

[0341]

接下来,在从cis模式到evs模式的转变时间段(t0至t4)中,行驱动电路251在时刻t1将控制信号mst设置为高电平,以接通控制晶体管318。这允许感测节点sn的sn电位被固定至固定电位vx。随后,行驱动电路251在时刻t2将切换信号tgd设置为高电平以接通开关晶体管317。此时,由于感测节点sn的sn电位被固定为固定电位vx,因此可以避免电压信号vpr的电压电平被卡到接地电位(gnd)。

[0342]

此后,行驱动电路251在时刻t3断开控制晶体管318。然后,行驱动电路251从时刻t4以后执行evs模式。

[0343]

1.14操作流程

[0344]

接下来,将描述根据本实施方式的成像装置100的操作示例。图31是示出根据本实施方式的成像装置的操作示例的流程图。以下描述是响应电路301a被结合在共享块221x中的示例性情况。然而,配置不限于此,并且根据变形例,响应电路301a可以替换为响应电路301b至301i等。此外,例如,图31中所示的操作可通过诸如关机的中断操作来终止。

[0345]

如图31所示,在本操作中,当激活成像装置100时,例如,首先在固态成像装置200中执行evs模式。如上所述,evs模式基于流出光电转换元件311的光电流的变化量来检测开启事件或关闭事件,由此检测进入成像装置100的视角的对象的运动(步骤s101)。要注意的是,该运动检测可由例如固态成像装置200中的信号处理电路240等执行,或者可由连接至固态成像装置200的控制部130、通过预定网络连接至成像装置100的服务器(包括云服务器等)等执行。

[0346]

接下来,在步骤s101中确定是否已经检测到对象的运动(步骤s102)。当未检测到对象的运动时(步骤s102中“否”),成像装置100继续evs模式。

[0347]

相反,当检测到对象的运动时(在步骤s102中为“是”),执行从evs模式向cis模式的转变。在该转变期间,行驱动电路251首先使响应电路301中的pmos晶体管314断开,使流过对数响应部310a的nmos晶体管313、316的偏置电流bias断开(步骤s103)。随后,行驱动电路251断开开关晶体管(也称为tgd栅极(gate))317(步骤s104)。由此,停止向对数响应部310a供给光电流,模式转变为cis模式。

[0348]

在cis模式下,行驱动电路251驱动像素电路370,以生成对象的拍摄图像的帧数据(步骤s105)。随后,对所生成的帧数据执行识别处理以识别所捕获的对象(步骤s106)。注意,可以不针对一个帧而是针对多个帧执行对象识别处理。应注意,对象识别处理可以由例如固态成像装置200中的信号处理电路240等执行,或者可以由连接至固态成像装置200的控制部130、经由预定网络连接至成像装置100的服务器(包括云服务器等)等执行。

[0349]

当以这种方式完成对象的识别时,固态成像装置200执行从cis模式到evs模式的转变。在该转变时间段期间,行驱动电路251首先接通控制晶体管(也称为mst栅极)318(步骤s107)。这允许将对数响应部310a的感测节点sn的sn电位控制为固定电位vx。接着,行驱动电路251使开关晶体管317接通(步骤s108),使控制晶体管318断开(步骤s109),之后,使响应电路301中的pmos晶体管314接通,以允许偏置电流bias在对数响应部310a的nmos晶体管313、316中流动(步骤s110)。这开始向对数响应部310a供应光电流,并且模式转变至evs模式。

[0350]

1.15电路共享

[0351]

以上描述是属于一个共享块221的多个响应电路301x(响应电路301x可以是上述

的响应电路301a至301i和下述的响应电路301j至301n中的任一个)中的每一个包括一个对数响应部310/310a和一个像素电路370的配置的示例。然而,构成响应电路301x的电路中的一些可以与其他响应电路301x共享。在下文中,将通过一些示例描述在多个响应电路301x之间共享部分电路配置的共享块的电路配置示例。

[0352]

1.15.1第一共享示例

[0353]

图32是示出根据第一共享示例的共享块的电路配置示例的电路图。应注意,第一共享示例示出了在包括图21中示出的四个响应电路301a的共享块221中共享像素电路370(具体地,不包括光电转换元件311和传输晶体管372的电路配置)的一部分的情况。在以下描述中,将像素电路370中的光电转换元件311和传输晶体管372除外的电路配置,即包括复位晶体管373、浮置扩散区374、放大晶体管375和选择晶体管376的电路配置称为读出电路370a。

[0354]

如图32所示,在根据第一共享示例的共享块221a中,每个响应电路301a1至301a4中的传输晶体管372的漏极连接至公共线3101。公共线3101与读出电路370a连接。读出电路370a通过公共线3101被多个响应电路301a1至301a4共享。即,每个共享块221a中的四个像素电路370中的每个包括每个响应电路301a1至301a4的光电转换元件311和传输晶体管372以及共享的读出电路370a。

[0355]

1.15.2第二共享示例

[0356]

图33是示出根据第二共享示例的共享块的电路配置示例的电路图。第二共享示例是在包括图23中所示的四个响应电路301c的共享块221中共享像素电路370的读出电路370a的情况。

[0357]

如图33所示,与根据第一共享示例的共享块221a相似,根据第二共享示例的共享块221c具有这样的配置,其中,每个响应电路301c1至301c4中的传输晶体管372的漏极连接至公共线3101,并且读出电路370a连接至公共线3101。利用该配置,每个共享块221c中的四个像素电路370中的每个包括每个响应电路301c1至301c4的光电转换元件311和传输晶体管372以及共享的读出电路370a。

[0358]

1.15.3第三共享示例

[0359]

图34是示出根据第三共享示例的共享块的电路配置示例的电路图。第三共享示例是在包括图24中所示的四个响应电路301d的共享块221中共享像素电路370的读出电路370a的情况。

[0360]

如图34所示,与根据第一共享示例的共享块221a相似,根据第三共享示例的共享块221d具有这样的配置,其中,每个响应电路301d1至301d4中的传输晶体管372的漏极连接至公共线3101,并且读出电路370a连接至公共线3101。利用该配置,每个共享块221d中的四个像素电路370中的每个包括每个响应电路301d1至301d4的光电转换元件311和传输晶体管372以及共享的读出电路370a。

[0361]

1.15.4第四共享示例

[0362]

图35是示出根据第四共享示例的共享块的电路配置示例的电路图。第四共享示例示出了在图33中示出的第二共享示例中进一步共享控制晶体管318的情况。

[0363]

如图35所示,根据第四共享示例的共享块221cc具有类似于根据第二共享示例的共享块221c的配置,其中,省略了响应电路301c1至301c4中的每一个中的控制晶体管318,

相反,一个控制晶体管318的源极连接至公共线3101。利用该配置,由响应电路301b1至301b4中的每一个的对数响应部310a共享控制晶体管318。

[0364]

如上所述,通过由多个响应电路301x共用一部分电路,可以减小光接收芯片201和/或检测芯片202中的占用面积,使得可以获得诸如固态成像装置200的小型化和通过光电转换元件311的面积扩大的灵敏度提高的效果。

[0365]

1.16使用电路共享的合并模式和全像素模式

[0366]

共享的读出电路370a和/或控制晶体管318可以在每个响应电路301x中的不同时段中使用,或者可以在相同的时段中使用。

[0367]

例如,在cis模式中的每个响应电路301x中在不同的时段使用读出电路370a的情况下,在其中每个共享块221x具有四个像素电路370的操作模式(在下文中,其被称为全像素模式)中,驱动每个共享块221x(共享块221x可以是上述共享块221a至221d中的任一个,或者通过将另一响应电路301x应用于共享块221a至221d而获得的共享块中的任一个)。

[0368]

另一方面,在cis模式下在相同时段内在各响应电路301x中使用读出电路370a的情况下,在各共享块221x具有一个像素电路370的操作模式(以下称为合并模式)下,驱动各共享块221x。合并模式使得可以在一个浮置扩散区374中收集在多个光电转换元件311中产生的电荷,导致灰度数据(像素信号)读出时的动态范围扩大,使得可以改善低亮度下的图像质量。

[0369]

此外,全像素模式和合并模式不仅能够应用于cis模式,还能够应用于evs模式。

[0370]

例如,在上述共享示例中的第一共享示例和第四共享示例中,通过使用配置,在evs模式中,其中响应电路301a1/301b1中的传输晶体管372和开关晶体管317接通,其他响应电路301a2/301b1至301a4/301b4中的传输晶体管372接通并且开关晶体管317断开,可以允许从每个响应电路301a1/301b1至301a4/301b4的光电转换元件311流出的光电流在响应电路301a1/301b1的对数响应部310a中聚集(合并模式)。

[0371]

此外,在上述共享示例中的第二共享示例和第三共享示例中,通过使用该配置,在evs模式中,其中响应电路301c1/301d1中的控制晶体管319和开关晶体管317接通,其他响应电路301c2/301d2至301c4/301d4中的传输晶体管372接通,并且控制晶体管319和开关晶体管317断开,可以允许从每个响应电路301c1/301d1至301c4/301d4的光电转换元件311流出的光电流聚集在响应电路301c1/301d1的对数响应部310a中。

[0372]

以这种方式,通过在一个对数响应部310/310a中聚集从每个光电转换元件311流出的光电流,可以增加一次流动的光电流的量,导致在地址事件的检测时动态范围的扩展。这使得可以提高例如在低亮度下对地址事件的灵敏度。

[0373]

另外,也可以在cis模式和evs模式的各模式下执行时,适当地切换全像素模式和合并模式。即使在此情况下,存在感测节点sn的sn电位在从全像素模式转变到合并模式或从合并模式转变到全像素模式时摆动的可能性。因此,与上述从cis模式向evs模式的转变类似,认为通过将sn电位固定为固定电位vx来缩短模式转变时的建立时间是有效的。

[0374]

1.17共享块的布局

[0375]

此外,下面将通过示例描述根据本实施方式的共享块221x的光接收部220中的布局。为了便于描述,以下将描述在其上形成光电转换元件311的半导体基板的元件形成表面侧上的示意性布局示例。此外,为了清楚起见,每个晶体管的布置由栅极的位置指示。

[0376]

1.17.1第一布局示例

[0377]

作为第一布局示例,将描述根据第一共享示例的共享块221a的布局示例。图36是示出根据第一布局示例的共享块的布局示例的平面图。如图36中所示,在光接收芯片201上,布置有一个响应电路301a的像素区域10由在行方向和列方向上延伸的像素隔离部12分割。响应电路301a1至301a4中的每一个包括光电转换元件311和沿着像素区域的外周部分布置的晶体管,换言之,被布置为从至少两个方向(图36中的三个方向)围绕光电转换元件311,晶体管是多个nmos晶体管312、313、315和316、开关晶体管317和控制晶体管318。此外,在四个像素区域10的每一个中,还布置构成读出电路370a的三个晶体管(373、375或376)中的任何一个或虚拟晶体管972。顺便提及,虚拟晶体管972是不包括在响应电路301a中的晶体管,并且例如可以是电浮置晶体管。

[0378]

在图36所示的布局示例中,每个对数响应部310a中的四个nmos晶体管312、313、315和316被布置在光电转换元件311的一侧上。以这种方式,通过将构成对数响应部310a的nmos晶体管312、313、315和316共同地布置在光电转换元件311的一侧上,可以减小由构成对数转换电路的配线形成的时间常数,导致对数转换电路的响应速度的提高。

[0379]

1.17.2第二布局示例

[0380]

作为第二布局示例,将描述根据第四共享示例的共享块221cc的布局示例。图37是示出根据第二布局示例的共享块的布局示例的平面图。如图37中所示,第二布局示例具有与第一布局示例相似的配置,其中,在第一布局示例中设置控制晶体管318的区域中设置控制晶体管319,并且共用控制晶体管318设置在设置虚拟晶体管972的区域中。

[0381]

1.18作用和效果

[0382]

如上所述,根据本实施方式,在从cis模式向evs模式的模式转变时,sn电位被固定为比正常操作时的sn电位低的电压vx。通过该配置,即使开关晶体管317转变为接通状态,也能够抑制sn电位的意外上升,能够避免nmos晶体管312、315的断开。结果,可以抑制由于电压信号vpr的电压电平卡到地电位(gnd)而引起的死区时间段。

[0383]

2.第二实施方式

[0384]

在上述第一实施方式中,在从cis模式向evs模式的模式转变时,sn电位被固定为比正常操作时的sn电位低的电压vx,因此能够抑制sn电位的意外增加,能够抑制死区时间段。相反,在第二实施方式中,光电转换元件311的阴极电位一旦降低到比正常操作时的sn电位低的电位,则光电转换元件311被电浮置,然后开关晶体管317接通。以这种方式,类似于第一实施方式,通过将光电转换元件311的阴极电位降低到比正常操作时的sn电位低的电位并且然后将光电转换元件311的阴极和感测节点sn彼此连接,可以抑制sn电位的意外增加。这使得可以抑制由于电压信号vpr的电压电平卡到地电位(gnd)而导致的死区时间段。在下文中,将通过一些示例描述从cis模式转变到evs模式时的响应电路301x的控制。

[0385]

因为根据本实施方式的成像装置、固态成像装置和构成固态成像装置的每个部分的配置可类似于第一实施方式的配置,所以将参照本实施方式进行描述。

[0386]

2.1第一控制示例

[0387]

第一控制示例是本实施方式应用于根据第一实施方式中参考图22描述的第一变形例的响应电路301b的示例性情况。图38是示出根据第一控制示例的从cis模式转变到evs模式时的操作示例的时序图。如图38所示,在图22所示的配置中,在从cis模式向evs模式转

变时的转变时段(t10至t14)中,行驱动电路251在时刻t11接通控制晶体管318和传输晶体管372。这允许通过控制晶体管318和传输晶体管372将固定电位vx施加到光电转换元件311的阴极,使得可以控制光电转换元件311的阴极电位被设置为固定电位vx。

[0388]

此后,行驱动电路251在时刻t12断开控制晶体管318和传输晶体管372以使光电转换元件311电浮置,并且然后在时刻t13接通开关晶体管317。在这种情况下,由于光电转换元件311的阴极电位被抑制到比正常操作时的sn电位低的固定电位vx,所以即使当开关晶体管317转变到接通状态时也可以抑制sn电位的意外增加。

[0389]

2.2第二控制示例

[0390]

第二控制示例是本实施方式应用于根据第一实施方式中参考图23描述的根据第二变形例的响应电路301c的示例性情况。图39是示出根据第二控制示例的从cis模式转变到evs模式时的操作示例的时序图。如图39所示,在图23所示的配置中,与第一控制示例类似,在从cis模式转变到evs模式时的转变时间段(t20至t25)中,行驱动电路251在时刻t21接通控制晶体管318和传输晶体管372。这允许通过控制晶体管318和传输晶体管372将固定电位vx施加到光电转换元件311的阴极,使得可以控制光电转换元件311的阴极电位被设置为固定电位vx。

[0391]

此后,类似于第一控制示例,行驱动电路251在时刻t22断开控制晶体管318和传输晶体管372以使光电转换元件311电浮置,并且然后在时刻t23接通开关晶体管317。在这种情况下,由于光电转换元件311的阴极电位被抑制到比正常操作时的sn电位低的固定电位vx,所以即使当开关晶体管317转变到接通状态时也可以抑制sn电位的意外增加。

[0392]

应注意,如图39所示,行驱动电路251可在时刻t21接通控制晶体管318和传输晶体管372,并且同时也可在时刻t21至t24的时段期间接通控制晶体管319。这也将感测节点sn的sn电位控制为固定电位vx,使得可以进一步抑制sn电位的意外增加。

[0393]

2.3第三控制示例

[0394]

第三控制示例是本实施方式应用于根据第一实施方式中参考图25描述的第四变形例的响应电路301e的示例性情况。图40是示出根据第三控制示例的从cis模式转变到evs模式时的操作示例的时序图。如图40所示,在图25所示的配置中,在从cis模式转变到evs模式时的转变时段(t30至t34)中,行驱动电路251在时刻t31接通复位晶体管373和传输晶体管372。这允许通过复位晶体管373和传输晶体管372将固定电位vx施加到光电转换元件311的阴极,使得可以控制光电转换元件311的阴极电位被设置为固定电位vx。

[0395]

此后,行驱动电路251在时刻t32断开复位晶体管373和传输晶体管372以使光电转换元件311电浮置,并且然后在时刻t33接通开关晶体管317。在这种情况下,由于光电转换元件311的阴极电位被抑制到比正常操作时的sn电位低的固定电位vx,所以即使当开关晶体管317转变到接通状态时也可以抑制sn电位的意外增加。

[0396]

2.4第四控制示例

[0397]

第四控制示例是本实施方式应用于根据第一实施方式中参考图26描述的第五变形例的响应电路301f的示例性情况。图41是示出根据第四控制示例的从cis模式转变到evs模式时的操作示例的时序图。如图41所示,在图26所示的配置中,在从cis模式向evs模式转变时的转变时段(t40至t45)中,与第三控制示例类似,行驱动电路251在时刻t41接通复位晶体管373和传输晶体管372。这允许通过复位晶体管373和传输晶体管372将固定电位vx施

加到光电转换元件311的阴极,使得可以控制光电转换元件311的阴极电位被设置为固定电位vx。

[0398]

此后,类似于第四控制示例,行驱动电路251在时刻t42断开复位晶体管373和传输晶体管372以使光电转换元件311电浮置,然后在时刻t23接通开关晶体管317。在这种情况下,由于光电转换元件311的阴极电位被抑制到比正常操作时的sn电位低的固定电位vx,所以即使当开关晶体管317转变到接通状态时也可以抑制sn电位的意外增加。

[0399]

应注意,如图41所示,行驱动电路251可在时刻t41接通复位晶体管373和传输晶体管372,并且同时也可在时刻t41至t44的时间段期间接通控制晶体管319。这也将感测节点sn的sn电位控制为固定电位vx,使得可以进一步抑制sn电位的意外增加。

[0400]

2.5第五控制示例

[0401]

第五控制示例是本实施方式应用于根据第一实施方式中参考图27描述的第六变形例的响应电路301g的示例性情况。图42是示出根据第五控制示例的从cis模式转变到evs模式时的操作示例的时序图。如图42中所示,在图27中所示的配置中,在从cis模式转变到evs模式时的转变时间段(t50至t54)中,行驱动电路251在时刻t51接通控制晶体管318。这允许通过控制晶体管318将固定电位vx施加到光电转换元件311的阴极,使得可以控制光电转换元件311的阴极电位被设置为固定电位vx。

[0402]

此后,行驱动电路251在时刻t52断开控制晶体管318以使光电转换元件311电浮置,并且然后在时刻t53接通开关晶体管317。在这种情况下,由于光电转换元件311的阴极电位被抑制到比正常操作时的sn电位低的固定电位vx,所以即使当开关晶体管317转变到接通状态时也可以抑制sn电位的意外增加。

[0403]

2.6第六控制示例

[0404]

第六控制示例是本实施方式应用于根据第一实施方式中参考图28描述的根据第七变形例的响应电路301h的示例性情况。图43是示出根据第六控制示例的从cis模式转变到evs模式时的操作示例的时序图。如图43中所示,在图28中所示的配置中,在从cis模式转变到evs模式时的转变时段(t60至t64)中,行驱动电路251在时刻t61接通控制晶体管318和开关晶体管317。这允许通过控制晶体管318和开关晶体管317将固定电位vx施加到光电转换元件311的阴极,使得可以控制光电转换元件311的阴极电位被设置为固定电位vx。

[0405]

此后,行驱动电路251在时刻t62断开控制晶体管318,以使光电转换元件311和开关晶体管317电浮置,然后在时刻t63接通控制晶体管319。在这种情况下,由于在正常操作期间光电转换元件311的阴极电位被抑制到低于sn电位的固定电位vx,所以即使当控制晶体管319转换到接通状态时,也可以抑制sn电位的意外增加。

[0406]

注意,行驱动电路251可以在时刻t61接通控制晶体管318和开关晶体管317,并且同时,可以接通控制晶体管319。这也将感测节点sn的sn电位控制为固定电位vx,使得可以进一步抑制sn电位的意外增加。

[0407]

2.7第七控制示例

[0408]

第七控制示例是本实施方式应用于根据第一实施方式中参考图29描述的第八变形例的响应电路3011的示例性情况。图44是示出根据第七控制示例的从cis模式转变到evs模式时的操作示例的时序图。如图44中所示,在图29中所示的配置中,在从cis模式转变到evs模式时的转变时段(t70至t74)中,行驱动电路251在时刻t71接通复位晶体管373、传输

晶体管372和开关晶体管317。这允许通过复位晶体管373、传输晶体管372和开关晶体管317将固定电位vx施加到光电转换元件311的阴极,使得可以控制光电转换元件311的阴极电位被设置为固定电位vx。

[0409]

此后,行驱动电路251在时刻t72断开复位晶体管373和传输晶体管372以使光电转换元件311和开关晶体管317电浮置,然后在时刻t73接通控制晶体管319。在这种情况下,由于光电转换元件311的阴极电位被抑制到低于在正常操作期间的sn电位的固定电位vx,所以即使当控制晶体管319转变到接通状态时,也可以抑制sn电位的意外增加。

[0410]

注意,行驱动电路251可以在时刻t71接通复位晶体管373、传输晶体管372和开关晶体管317,并且同时可以接通控制晶体管319。这也将感测节点sn的sn电位控制为固定电位vx,使得可以进一步抑制sn电位的意外增加。

[0411]

2.8作用和效果

[0412]

如上所述,根据本实施方式,类似于第一实施方式,光电转换元件311的阴极电位一旦降低到比正常操作时的sn电位低的电位,光电转换元件311电浮置,然后开关晶体管317接通。这使得可以抑制sn电位的意外增加,从而抑制由于电压信号vpr的电压电平卡到地电位(gnd)而导致的死区时间段。

[0413]

由于其他配置、操作和效果可类似于上述实施方式中的配置、操作和效果,因此这里将省略其详细描述。此外,根据本实施方式的配置可适当地与上述实施方式和/或下述实施方式组合。

[0414]

3.第三实施方式

[0415]

在第三实施方式中,控制流过对数响应部310/310a的对数变换电路中nmos晶体管313/nmos晶体管313、316的偏置电流bias,由此抑制sn电位的意外上升,从而抑制由于卡在接地电位(gnd)的电压信号vpr的电压电平而引起的死区时间段的情况为例进行说明。

[0416]

因为根据本实施方式的成像装置、固态成像装置和构成固态成像装置的每个部分的配置可类似于第一实施方式的配置,所以将参照本实施方式进行描述。然而,在本实施方式中,构成共享块221x的响应电路301x被替换成下面将要描述的响应电路。以下描述是使用第一实施方式中参照图7描述的对数响应部310a的响应电路的示例性情况。然而,配置不限于此,并且还可以使用诸如参考图6描述的对数响应部310的其他对数响应部。

[0417]

3.1响应电路的配置示例

[0418]

图45是示出了根据本实施方式的响应电路的配置示例的电路图。如图45所示,根据本实施方式的响应电路301j具有类似于在第一实施方式中参照图9描述的响应电路301的配置,例如,其中,对数响应部310a中的作为恒流电路的pmos晶体管314(也称为负载mos晶体管或负载电阻器)被偏置电路314a替代。

[0419]

偏置电路314a包括:构成电流镜电路的两个pmos晶体管,即pmos晶体管314a和314b;以及数模转换器(dac)314c,其根据从行驱动电路251输入的控制信号ctl,生成用于控制流过电流镜电路的偏置电流bias的电压。

[0420]

dac 314c将从行驱动电路251输入的数字控制信号ctl转换为模拟电压,并将获得的模拟电压施加到pmos晶体管314b的源极,由此控制流过与另一pmos晶体管314a的源极连接的对数转换电路的nmos晶体管313、316的偏置电流bias。

[0421]

具体地,例如,当从行驱动电路251输入表示“1”的控制信号ctl时,dac 314c将参

考电流提供至电流镜电路。这与参考电流对应的偏置电流bias流过对数转换电路的nmos晶体管313和316。

[0422]

另一方面,当从行驱动电路251输入表示“0”的控制信号ctl时,dac 314c切断向电流镜电路的参考电流的供应。这将切断流过对数转换电路的nmos晶体管313和316的偏置电流bias。

[0423]

偏置电路314a例如可设置在检测芯片202侧。此外,dac 314c可以通过使用使用r-2r阶梯的二进制系统、使用nmos晶体管的电流镜(在下文中,也称为nmos电流镜)等来形成。在使用nmos电流镜的情况下,可以通过带隙参考电路生成参考电流。

[0424]

3.1.1响应电路的变形例

[0425]

图46是示出根据本实施方式的响应电路的变形例的电路图。如图46中所示,根据变形例的响应电路301k具有与上面参照图45描述的响应电路301j的配置相似的配置,其中,例如,偏置电路314a由偏置电路314b取代。

[0426]

偏置电路314b具有与偏置电路314a的配置类似的配置,其中dac314c用恒定电流源314e替代,并且偏置控制晶体管314d被添加到构成电流镜电路的pmos晶体管314a的源极。

[0427]

当以这种配置将偏置电流提供至对数转换电路时,例如,行驱动电路251将高电平控制信号ctl施加至偏置控制晶体管314d的栅极。这形成从电流镜电路到对数转换电路的电流路径,能够将流过恒定电流源314e的电流作为参考电流的偏置电流bias供给到对数转换电路。相反,当偏置电流不被供应至对数转换电路时,例如,行驱动电路251将低电平控制信号ctl施加至偏置控制晶体管314d的栅极。由此,切断从电流镜电路到对数转换电路的电流路径,由此切断向对数转换电路的偏置电流bias的供给。

[0428]

偏置控制晶体管314d可布置在光接收芯片201上或者可布置在检测芯片202上。其他配置可类似于上述响应电路301j的配置。

[0429]

在上述配置中,在从cis模式向evs模式转变时,使用提供给dac314c或偏置控制晶体管314d的控制信号ctl来切断流过对数转换电路的nmos晶体管313和316的偏置电流bias。由此,与上述实施方式类似地,能够抑制开关晶体管317转变为接通状态时的sn电位的意外增加。由此,能够避免nmos晶体管312、315断开,从而能够抑制因电压信号vpr的电压电平卡于接地电位(gnd)而引起的死区时间段。

[0430]

另外,如本实施方式那样控制对数转换电路中的偏置电流bias的流动的情况下,也能够缓和对响应电路301j所需的电路设计的限制。这使得可以设计响应电路301j,更具体地,固态成像装置200的设计自由度变高。

[0431]

3.2从cis模式至evs模式的转变

[0432]

接下来,将描述从cis模式转变到evs模式时的操作。虽然本描述使用图45中所示的响应电路301j作为参考,但是也可以类似地将本描述应用于图46中所示的响应电路301k。

[0433]

图47是示出了根据本实施方式的从cis模式转变到evs模式时的操作示例的时序图。如图47所示,首先,在从cis模式至evs模式的转变中,在cis模式的结束时刻t80停止从行驱动电路251向构成像素电路370的传输晶体管372、选择晶体管376、以及复位晶体管373的控制信号(trg、sel、以及rst)的供应。

[0434]

接着,在从cis模式向evs模式的转变期间(t80至t82)中,行驱动电路251在时刻t81使开关晶体管317接通。控制信号ctl在转变时间段期间(t80至t82)指示“0”,因此,切断流过对数转换电路的偏置电流bias(低电平)。

[0435]

此后,行驱动电路251在时刻t82将控制信号ctl设置为“1”。这允许偏置电流bias经由偏置电路314a/314b供给到对数转换电路(高电平)。接着,行驱动电路251从时刻t82起执行evs模式。

[0436]

3.3操作流程

[0437]

接下来,将描述根据本实施方式的成像装置100的操作示例。图48是示出根据本实施方式的成像装置的操作示例的流程图。以下描述是响应电路301j被结合在共享块221x中的示例性情况。然而,配置不限于此,并且根据变形例,响应电路301j可以用响应电路301k等代替。此外,例如,图48中所示的操作可以通过诸如关机的中断操作来终止。

[0438]

如图48中所示,在本操作中,当成像装置100被激活时,例如,evs模式被激活并且执行运动检测处理(步骤s301),以便类似于第一实施方式中图31的步骤s101至s102确定是否检测到对象的运动(步骤s302)。

[0439]

当在步骤s302中检测到对象的运动时(步骤s302中的是),执行从evs模式向cis模式的转变。在该转变期间,首先,行驱动电路251使响应电路301j的偏置电路314a断开,使流过对数响应部310a的nmos晶体管313、316的偏置电流bias断开(步骤s303)。应注意,通过将指示“0”的控制信号ctl输入至dac 314c可实现断开偏置电路314a。

[0440]

随后,行驱动电路251断开开关晶体管(tgd栅极)317(步骤s304)。这停止向对数响应部310a供给光电流,模式转变为cis模式。

[0441]

在该cis模式下,与图31的步骤s105至步骤s106类似,行驱动电路251生成对象的捕获图像的帧数据(步骤s305),识别该捕获对象(步骤s306)。

[0442]

当以这种方式完成对象的识别时,固态成像装置200执行从cis模式到evs模式的转变。在该转变期间,行驱动电路251首先使开关晶体管317接通(步骤s307),然后使响应电路301中的偏置电路314a接通,以使偏置电流bias流向对数响应部310a的nmos晶体管313、316(步骤s308)。这开始向对数响应部310a供应光电流,并且模式转变至evs模式。要注意的是,通过将指示“1”的控制信号ctl输入到dac 314c中,可实现接通偏置电路314a。

[0443]

3.4作用和效果

[0444]

如上所述,根据本实施方式,在从cis模式向evs模式的转变期间,切断向对数转换电路的偏置电流bias的供给。由此,与上述实施方式类似,能够抑制开关晶体管317转变为接通状态时的sn电位的意外增加。由此,能够避免nmos晶体管312、315断开,从而能够抑制因电压信号vpr的电压电平卡于接地电位(gnd)而引起的死区时间段。

[0445]

另外,如本实施方式那样控制对数转换电路中的偏置电流bias的流动的情况下,也能够缓和响应电路301j所需的电路设计的限制。这使得可以以更高的设计自由度设计响应电路301j,更具体地,设计固态成像装置200。

[0446]

由于其他配置、操作和效果可类似于上述实施方式中的配置、操作和效果,因此这里将省略其详细描述。此外,根据本实施方式的配置可适当地与上述实施方式和/或下述实施方式组合。

[0447]

4.第四实施方式

[0448]

第四实施方式将描述根据上述第一和/或第二实施方式的配置和根据第三实施方式的配置彼此组合的示例性情况。

[0449]

因为根据本实施方式的成像装置、固态成像装置和构成固态成像装置的每个部分的配置可类似于第一至第三实施方式中的任一个的配置,所以将参照本实施方式进行描述。然而,在本实施方式中,构成共享块221x的响应电路301x被替换成下面将要描述的响应电路。以下描述是在第一实施方式中使用参照图7描述的对数响应部310a的响应电路的示例性情况。然而,配置不限于此,并且还可以使用诸如参考图6描述的对数响应部310的其他对数响应部。

[0450]

4.1响应电路的配置示例

[0451]

图49是示出了根据本实施方式的响应电路的配置示例的电路图。如图49所示,根据本实施方式的响应电路301l具有组合第一实施方式或第二实施方式中参考图21描述的响应电路301a与第三实施方式中参考图45描述的响应电路301j的配置。具体地,响应电路301l具有其中控制晶体管318连接到在第三实施方式中参考图45描述的响应电路301j中的感测节点sn的配置。

[0452]

4.1.1响应电路的变形例

[0453]

图50是示出了根据本实施方式的响应电路的变形例的电路图。如图50所示,根据变形例的响应电路301m具有例如将第一或第二实施方式中参考图21描述的响应电路301a与第三实施方式中参考图46描述的响应电路301k组合的配置。具体地,响应电路301m具有控制晶体管318连接至在第三实施方式中参考图46描述的响应电路301k中的感测节点sn的配置。

[0454]

根据这样的配置,在从cis模式转变到evs模式时,感测节点sn的sn电位和/或光电转换元件311的阴极电位可以被固定到比正常操作时的sn电位低的固定电位vx,并且可以切断向对数响应部310a中的对数响应电路的偏置电流的供应,使得可以进一步抑制sn电位的意外增加。这使得可以进一步抑制由卡到地电位(gnd)的电压信号vpr的电压电平引起的死区时间段。

[0455]

注意,与根据第三实施方式的响应电路301j/301k组合的配置不限于图21中示出的响应电路301a,并且可以是例如图22至图29中示出的响应电路301b至3011中的任一个。

[0456]

4.2从cis模式至evs模式的转变

[0457]

接下来,将描述从cis模式转变到evs模式时的操作。将参考图49中示例的响应电路301l给出本描述。然而,通过根据控制晶体管318的控制适当地控制控制晶体管319、传输晶体管372、复位晶体管373等,也可以通过变形例实现类似的操作。

[0458]

图51是示出根据本实施方式的从cis模式转变到evs模式时的操作示例的时序图。如图51所示,首先,在从cis模式转变至evs模式中,在cis模式的结束时刻t90停止从行驱动电路251向构成像素电路370的传输晶体管372、选择晶体管376、以及复位晶体管373的控制信号(trg、sel、以及rst)的供应。

[0459]

接下来,在从cis模式到evs模式的转变时段(t90到t94)中,行驱动电路251在时刻t91将控制信号mst设置为高电平,以接通控制晶体管318。这允许感测节点sn的sn电位被固定至固定电位vx。控制信号ctl在转变期间(t90至t92)指示“0”,因此,切断流过对数转换电路的偏置电流bias(低电平)。

[0460]

接着,行驱动电路251在时刻t92将切换信号tgd设定为高电平,以接通开关晶体管317。此时,由于感测节点sn的sn电位被固定为固定电位vx,因此可以避免电压信号vpr的电压电平卡到接地电位(gnd)。

[0461]

此后,行驱动电路251在时刻t93断开控制晶体管318,并且然后在时刻t94将控制信号ctl设置为“1”。由此,偏置电流bias经由偏置电路314a/314b供给到对数转换电路(高电平)。接着,行驱动电路251从时刻t94起执行evs模式。

[0462]

4.3操作流程

[0463]

接下来,将描述根据本实施方式的成像装置100的操作示例。图52是示出根据本实施方式的成像装置的操作示例的流程图。以下描述是响应电路301l包含在共享块221x中的示例性情况。然而,配置不限于此,并且根据变形例,响应电路301l可以由响应电路301m等代替。此外,例如,图52中所示的操作可通过诸如关机的中断操作来终止。

[0464]

如图52所示,在本操作中,当成像装置100被激活时,例如,evs模式被激活并且执行运动检测处理(步骤s401),以确定是否检测到对象的运动(步骤s402)。类似于第一实施方式中的图31的步骤s101至s102。

[0465]

当在步骤s402中检测到对象的运动时(步骤s402中“是”),执行从evs模式向cis模式的转变。在该转变期间中,例如与第三实施方式的图48的步骤s303至s304类似地,行驱动电路251使响应电路301l的偏置电路314a断开而切断偏置电流bias(步骤s403),之后使开关晶体管(tgd栅极)317断开(步骤s404)。由此,停止向对数响应部310a供给光电流,模式转变为cis模式。

[0466]

第一实施方式的图31的步骤s105-s106或第三实施方式的图48的步骤s305-s306类似地,在该cis模式下,行驱动电路251生成对象的捕获图像的帧数据(步骤s405),识别该拍摄的对象(步骤s406)。

[0467]

当以这种方式完成对象的识别时,固态成像装置200执行从cis模式到evs模式的转变。在这个转变时间段期间,行驱动电路251接通控制晶体管(也称为mst栅极)318和开关晶体管317(步骤s407至s408),并且断开控制晶体管318(步骤s409),类似于第一实施方式中图31中的步骤s107至s109。接着,与第三实施方式的图48的步骤s308类似,行驱动电路251使响应电路301l的偏置电路314a接通,以使偏置电流bias流向对数响应部310a的nmos晶体管313、316(步骤s410)。这开始向对数响应部310a供应光电流,并且模式转变至evs模式。

[0468]

4.4作用和效果

[0469]

如上所述,根据本实施方式,在从cis模式转变到evs模式时,感测节点sn的sn电位和/或光电转换元件311的阴极电位可以被固定到比正常操作时的sn电位低的固定电位vx,并且可以切断向对数响应部310a中的对数响应电路的偏置电流的供应,使得可以进一步抑制sn电位的意外增加。这使得可以进一步抑制由卡到地电位(gnd)的电压信号vpr的电压电平引起的死区时间段。

[0470]

由于其他配置、操作和效果可类似于上述实施方式中的配置、操作和效果,因此这里将省略其详细描述。此外,根据本实施方式的配置可适当地与上述实施方式和/或下述实施方式组合。

[0471]

5.第五实施方式

[0472]

在上述实施方式中,说明了对从cis模式向evs模式转变时产生的死区时间段进行抑制的情况。在本实施方式中,说明例如在evs操作(可以是evs模式)期间,抑制在从全像素模式向合并模式或从合并模式向全像素模式转变时可能发生的死区时间段的情况。

[0473]

如上所述,在固态成像装置200以evs操作时,感测节点sn的sn电位可在从全像素模式转变至像素合并模式或从像素合并模式转变至全像素模式时摆动。在那种情况下,可能出现死区时间段,其中在建立时间期间不能检测到地址事件,直到sn电位稳定到正常操作处的电压电平。因此,在本实施方式中,通过以下的示例说明能够抑制死区时间段的发生的配置。

[0474]

以下描述将描述固态成像装置200不包括cis模式(即,固态成像装置200不包括用于获取灰度数据的像素电路370)的情况。然而,本实施方式不限于此,与上述实施方式类似地,可以在包含像素电路370的固态成像装置200在evs模式下操作时,在从全像素模式向合并模式转变时或从合并模式向全像素模式转变时应用本实施方式。

[0475]

因为根据本实施方式的成像装置、固态成像装置和构成固态成像装置的每个部分的配置可类似于第一至第四实施方式中的任一个的配置,所以将参照本实施方式进行描述。然而,在本实施方式中,检测芯片202被替换成下面将要描述的检测芯片,并且共享块221x被替换成下面将要描述的共享块。以下描述是在第一实施方式中使用参照图7描述的对数响应部310a的示例性情况。然而,配置不限于此,并且还可以使用诸如参考图6描述的对数响应部310的其他对数响应部。

[0476]

5.1检测芯片的布局示例

[0477]

图53是根据本实施方式的检测芯片的平面图的示例。如图53所示,根据本实施方式的检测芯片202a具有这样的配置,其中,在类似于第一实施方式中参照图4所描述的检测芯片202的配置中,省略了用于读取低阶(lower order)工作数据的列adc 270。

[0478]

5.2共享块的基本配置示例

[0479]

图54是示出根据本实施方式的共享块的配置示例的电路图。如图54所示,根据本实施方式的共享块821包括多个响应电路801a1至801a4(下文中,当响应电路801a1至801a4彼此不区分时,称为801a)。注意,共享块821中的响应电路801a的总数不限于2行x2列图案中的四个,并且可以是2或更大的整数。

[0480]

每一个响应电路801a具有与第一实施方式中参考图21所描述的响应电路301a类似的配置,例如,其中省略了构成像素电路370的传输晶体管372、复位晶体管373、浮置扩散区374、放大晶体管375和选择晶体管376。

[0481]

在这种配置中,当抑制每个响应电路801中的感测节点sn的sn电位的摆动时,控制晶体管318接通,并且固定电位vx被施加至感测节点sn。这控制感测节点sn的sn电位被设置为固定电位vx,使得可以缩短由sn电位的摆动产生的建立时间。

[0482]

5.3通过电路共享的合并模式

[0483]

在图54所示的配置中,例如,通过使得能够形成连接各个响应电路801a的感测节点sn的电流路径,可以获得能够在全像素模式和合并模式之间切换的配置。因此,下面通过一些示例描述使得能够在全像素模式和合并模式之间进行切换的共享块821的电路配置示例。

[0484]

5.3.1第一共享示例

[0485]

图55为示出根据第一共享示例的共享块的电路配置示例的电路图。第一共享示例是示例性情况,其中,根据第一实施方式中参考图33描述的第二共享示例的共享块221c用作基础。

[0486]

如图55所示,根据第一共享示例的共享块821c具有这样的配置,其中从类似于参考图33所描述的共享块221c的配置中省略连接到公共线3101的读出电路370a。更具体地,共享块821c具有其中多个响应电路801c1~801c4的感测节点sn通过控制晶体管319和公共线3101彼此连接的配置。然而,共享块821c在每个响应电路801c1~801c4中保持传输晶体管372以控制光电转换元件311和公共线3101之间的连接。

[0487]

在这种配置中,当在全像素模式下驱动共享块821c时,行驱动电路251断开每个响应电路801c1~801c4的传输晶体管372和控制晶体管319。这允许每个响应电路801c1~801c4的光电转换元件311连接到每个感测节点sn,使得可以在全像素模式下检测地址事件。

[0488]

此外,当在全像素模式中抑制感测节点sn的sn电位的摆动时,响应电路801c1~801c4的控制晶体管318和319被接通。这允许将固定电位vx施加至响应电路801c1~801c4中的每一个的感测节点sn,使得可以缩短由sn电位的摆动产生的建立时间。此时,可以通过接通响应电路801c1~801c4中的每一个的传输晶体管372和/或开关晶体管317,将光电转换元件311的阴极电位控制为固定电位vx。

[0489]

此外,当在合并模式下驱动共享块821c时,行驱动电路251使响应电路801c1的开关晶体管317和控制晶体管319接通,使其他响应电路801c2至801c4中的开关晶体管317和控制晶体管319断开,并且使传输晶体管372接通。这导致形成从每个响应电路801c1~801c4的光电转换元件311到响应电路801c1的感测节点sn的电流路径,使得能够在合并模式下检测地址事件。

[0490]

此外,当在合并模式中抑制感测节点sn的sn电位的摆动时,响应电路801c1~801c4的控制晶体管318和319接通。这允许将固定电位vx施加至响应电路801c1~801c4中的每一个的感测节点sn,使得可以缩短由sn电位的摆动产生的建立时间。此时,可以通过接通响应电路801c1~801c4中的每一个的传输晶体管372和/或开关晶体管317将光电转换元件311的阴极电位控制为固定电位vx。

[0491]

5.3.2第二共享示例

[0492]

图56为示出根据第二共享示例的共享块的电路配置示例的电路图。第二共享示例是基于根据第一实施方式中参考图34描述的第三共享示例的共享块221d的示例性情况。

[0493]

如图56中所示,根据第二共享示例的共享块821d具有这样的配置:其中,从类似于参考图34所述的共享块221d的配置中省略连接至公共线3101的读出电路370a。更具体地,共享块821d具有其中多个响应电路801d1~801d4的感测节点sn通过控制晶体管319和公共线3101彼此连接的配置。然而,共享块821d在每个响应电路801d1~801d4中保持传输晶体管372以控制光电转换元件311和公共线3101之间的连接。

[0494]

在这样的配置中,当在全像素模式下驱动共享块821d时,行驱动电路251断开响应电路801d1~801d4中的每个的传输晶体管372和控制晶体管319。这允许每个响应电路801d1~801d4的光电转换元件311连接到每个感测节点sn,使得可以在全像素模式下检测地址事件。

[0495]

此外,当在全像素模式中抑制感测节点sn的sn电位的摆动时,响应电路801d1~801d4的控制晶体管318接通。这允许将固定电位vx施加至响应电路801d1~801d4中的每一个的感测节点sn,使得可以缩短由sn电位的摆动产生的建立时间。此时,可以通过接通响应电路801d1~801d4中的每一个的开关晶体管317来将光电转换元件311的阴极电位控制为固定电位vx。

[0496]

此外,当在合并模式下驱动共享块821d时,行驱动电路251使响应电路801d1的开关晶体管317和控制晶体管319接通,使其他响应电路801d2~801d4中的开关晶体管317和控制晶体管319断开,并且使传输晶体管372接通。这导致形成从每个响应电路801d1~801d4的光电转换元件311到响应电路801d1的感测节点sn的电流路径,使得能够在合并模式下检测地址事件。

[0497]

此外,当在合并模式中抑制感测节点sn的sn电位的摆动时,响应电路801d1~801d4的控制晶体管318接通。这允许将固定电位vx施加至响应电路801d1~801d4中的每一个的感测节点sn,使得可以缩短由sn电位的摆动产生的建立时间。此时,可以通过接通响应电路801d1~801d4中的每一个的开关晶体管317来将光电转换元件311的阴极电位控制为固定电位vx。

[0498]

5.3.3第三共享示例

[0499]

图57为示出根据第三共享示例的共享块的电路配置示例的电路图。第三共享示例是示例性情况,其中,根据第一实施方式中参考图35描述第四共享示例的共享块221cc用作基础。

[0500]

如图57所示,根据第三共享示例的共享块821cc具有这样的配置,其中从类似于参考图35所述的共享块221cc的配置中省略连接到公共线3101的读出电路370a。更具体地,共享块821cc具有其中多个响应电路801c1~801c4的感测节点sn通过控制晶体管319和公共线3101彼此连接的配置。然而,共享块821cc在每个响应电路801c1~801c4中保持传输晶体管372以控制光电转换元件311和公共线3101之间的连接。这可类似于其中根据参考图55描述的第一共享示例的共享块821c中连接至公共线3101的共用控制晶体管318替换响应电路801c1~801c4中的每个中的控制晶体管318的配置。

[0501]

在这种配置中,当在全像素模式下驱动共享块821d时,行驱动电路251断开每个响应电路801c1~801c4的传输晶体管372和控制晶体管319。这允许每个响应电路801c1~801c4的光电转换元件311连接到每个感测节点sn,使得可以在全像素模式下检测地址事件。

[0502]

此外,当在全像素模式中抑制感测节点sn的sn电位的摆动时,连接到公共线3101的控制晶体管318接通。这允许将固定电位vx施加至响应电路801c1~801c4中的每一个的感测节点sn,使得可以缩短由sn电位的摆动产生的建立时间。此时,可以通过接通响应电路801c1~801c4中的每一个的开关晶体管317来将光电转换元件311的阴极电位控制为固定电位vx。

[0503]

此外,当在合并模式下驱动共享块821d时,行驱动电路251使响应电路801d1的开关晶体管317和控制晶体管319接通,使其他响应电路801d2~801d4中的开关晶体管317和控制晶体管319断开,并且使传输晶体管372接通。这导致形成从每个响应电路801d1~801d4的光电转换元件311到响应电路801d1的感测节点sn的电流路径,使得能够在合并模

式下检测地址事件。

[0504]

此外,当在合并模式中抑制感测节点sn的sn电位的摆动时,连接到公共线3101的控制晶体管318接通。这允许将固定电位vx施加至响应电路801c1~801c4中的每一个的感测节点sn,使得可以缩短由sn电位的摆动产生的建立时间。此时,可以通过接通响应电路801c1~801c4中的每一个的开关晶体管317来将光电转换元件311的阴极电位控制为固定电位vx。

[0505]

5.4作用和效果

[0506]

如上所述,即使在固态成像装置以evs操作时,通过在从全像素模式转变至合并模式或从合并模式转变至全像素模式时将感测节点sn的sn电位固定为固定电位vx,可缩短由sn电位的摆动产生的建立时间并缩短模式转变所需的时间段。

[0507]

由于其他配置、操作和效果可类似于上述实施方式中的配置、操作和效果,因此这里将省略其详细描述。此外,根据本实施方式的配置可适当地与上述实施方式和/或下述实施方式组合。

[0508]

6.第六实施方式

[0509]

第六实施方式将描述模式转变时固定感测节点sn的sn电位的另一配置的示例。

[0510]

因为根据本实施方式的成像装置、固态成像装置和构成固态成像装置的每个部分的配置可类似于第一至第三实施方式中的任一个的配置,所以将参照本实施方式进行描述。然而,在本实施方式中,构成共享块221x的响应电路301x被替换成下面将要描述的响应电路。以下描述是使用在第一实施方式中参照图7描述的对数响应部310a的响应电路的示例性情况。然而,配置不限于此,并且还可以使用诸如参考图6描述的对数响应部310的其他对数响应部。

[0511]

6.1响应电路的配置示例

[0512]

图58是示出了根据本实施方式的响应电路的配置示例的电路图。如图58所示,根据本实施方式的响应电路301n具有与第一实施方式中参考图21描述的响应电路301a的配置类似的配置,例如,其中,控制晶体管318连接在nmos晶体管312的栅极与构成对数转换电路的nmos晶体管313的栅极(对应于感测节点sn)之间。

[0513]

6.2作用和效果

[0514]

在以上配置中,当控制晶体管318接通时,感测节点sn的sn电位可由流过nmos晶体管313的偏置电流bias来确定。因此,在本实施方式中,例如在从cis模式向evs模式转变时、或者在全像素模式与合并模式之间切换时,在使向nmos晶体管313的偏置电流bias的供给断开的状态下,使控制晶体管318接通,然后在使控制晶体管318接通的状态下,使开关晶体管317接通。这使得可以具有比正常操作时的sn电位低的sn电位,从而抑制由于电压信号vpr的电压电平卡在接地电位(gnd)上而导致的死区时间段。当开始evs模式时,开始向nmos晶体管313供给偏置电流bias。

[0515]

由于其他配置、操作和效果可类似于上述实施方式中的配置、操作和效果,因此这里将省略其详细描述。此外,根据本实施方式的配置可适当地与上述实施方式和/或下述实施方式组合。

[0516]

7.第七实施方式

[0517]

虽然上述实施方式是将同步evs应用于固态成像装置200的示例性情况,但是配置

不限于这种示例,其中同步evs不需要对用于请求读出从每个共享块221等输出的检测信号的请求进行仲裁。例如,如图59中的固态成像装置示出的,还可允许应用包括行仲裁器280的异步evs,行仲裁器280仲裁从地址事件检测部260的每一行输出的请求并确定检测信号的读出行的顺序。需注意,图59示出了根据本实施方式的固态成像装置中的检测芯片1202。

[0518]

以这种方式,即使在应用异步evs的情况下,也能够利用与上述实施方式的配置和操作类似的配置和操作来抑制模式转变时的死区时间段以实现快速模式转变。

[0519]

由于其他配置、操作和效果可类似于上述实施方式中的配置、操作和效果,因此这里将省略其详细描述。此外,根据本实施方式的配置可适当地与上述实施方式和/或下述实施方式组合。

[0520]

8.第八实施方式

[0521]

当如在上述实施方式中响应电路301/801等包括控制晶体管318和/或319时,将需要向现有的响应电路添加配线等。在这种情况下,配线电容在控制晶体管318和/或319的额外布置之前和之后改变,导致对关于入射光的量子效率、evs的操作特性等具有影响的可能性。鉴于此,第八实施方式将描述即使在额外的控制晶体管318和/或319的情况下也能够抑制对量子效率、操作特性等的影响的像素布局的示例。

[0522]

以下描述将是根据本实施方式的布局示例,作为对第一实施方式中例示的共享块221x的光接收部220中的基本布局示例(参照图36或图37)的变形例。此外,类似于第一实施方式中的图36或图37的描述,以下描述将示出在其上形成光电转换元件311的半导体基板的元件形成表面侧上的示意性布局示例。另外,为了清楚起见,每个晶体管的布置由栅极的位置指示。

[0523]

8.1第一布局变形例

[0524]

在第一布局变形例中,将描述根据第一实施方式的第一共享示例的共享块221a(参照图32)的布局示例。即,第一布局变形例示出响应电路301a1至301a4中的每个包括单独控制晶体管318的情况。图60是示出了根据第一布局变形例的共享块的布局示例的平面图。

[0525]

如图60所示,在第一布局变形例中,类似于上面参考图36所述的第一布局示例,响应电路301a1至301a4布置在以构成共享块221a的2

×

2像素图案形成的像素区域10中。布置在各个像素区域10中的响应电路301a1至301a4被布置为在垂直方向(例如,列方向)上对称。

[0526]

在每个像素区域10中,控制晶体管318被设置为靠近像素区域10的外围部分。换言之,在第一布局变形例中,控制晶体管318被设置在将相邻的光电转换元件311彼此电隔离的隔离区域中。这使得可以将光电转换元件311布置在像素区域10的中心,导致取决于光的入射角的量子效率的劣化的抑制。此外,该布置使得可以保持相邻光电转换元件311之间的距离,导致由于入射光泄漏到相邻像素而引起的颜色混合的减少。

[0527]

此外,在第一布局变形例中,构成像素电路370的复位晶体管373、放大晶体管375以及选择晶体管376被布置在构成共享块221a的2

×

2像素布局的中心。该配置可缩短将浮置扩散区374连接至放大晶体管375和复位晶体管373(以及虚拟晶体管972)的配线的长度,使得可以有利于浮置扩散区374的电容(fd电容)的优化。

[0528]

在第一布局变形例中,图7所示的对数响应部310a通过将nmos晶体管312和315与

在相邻像素区域10中靠近彼此面对的边布置的nmos晶体管313和316连接来配置。由此,能够缩短连接nmos晶体管312、315和nmos晶体管313、316的配线的长度,由此获得由于耦合电容的降低导致的操作性能的提高等效果。

[0529]

其他配置和效果可类似于上面参考图36或图37描述的布局示例的配置和效果,并且因此在此省略其详细描述。

[0530]

8.2第二布局变形例

[0531]

在第二布局变形例中,将描述根据第一实施方式的第四共享示例的共享块221cc(参照图35)的布局示例。即,第二布局变形例示出了响应电路301c1至301c4包括公共控制晶体管318,并且响应电路301c1至301c4中的每个包括单独控制晶体管319的情况。图61是示出了根据第二布局变形例的共享块的布局示例的平面图。

[0532]

如图61所示,第二布局变形例具有类似于上面参考图60描述的第一布局变形例的布局,其中每个控制晶体管319设置在每个控制晶体管318的位置处,并且公共控制晶体管318设置在虚拟晶体管972的位置处。

[0533]

通过采用这种布局,与第一布局变形例相似,可以实现诸如抑制量子效率劣化和减少颜色混合的效果。

[0534]

此外,第二布局变形例具有其中公共控制晶体管318被设置在2

×

2像素布局中的中心处的配置。因此,在能够在evs模式和cis模式之间切换的配置中,可以改善在evs模式和cis模式之间切换时的操作稳定性,同时抑制光电转换元件311中的光接收面积、孔径比、饱和电荷量等的减小。

[0535]

其他配置和效果可类似于上面参考图60描述的第一布局变形例的配置和效果,并且因此,这里将省略其详细描述。

[0536]

8.3第三布局变形例

[0537]

在第三布局变形例中,类似于第二布局变形例,将描述根据第一实施方式的第四共享示例的共享块221cc(参照图35)的布局示例。图62是示出了根据第三布局变形例的共享块的布局示例的平面图。

[0538]

如图62中所示,第三布局变形例使用与上面参照图61描述的第二布局变形例相似的布局,其中,单独控制晶体管319设置在构成共享块221cc的2

×

2像素布局的中心,并且像素电路370和控制晶体管318设置在与另一共享块221cc相邻的区域内。

[0539]

通过采用这种布局,与第二布局变形例类似,可以提高在evs模式和cis模式之间切换时的操作稳定性,并且可以实现诸如抑制量子效率劣化和减少颜色混合的效果。

[0540]

此外,因为在第三布局变形例中,单独控制晶体管319被布置在2

×

2像素布局的中心,所以可以缩短感测节点sn的配线长度。由此,能够抑制合并模式下的等待时间劣化。

[0541]

其他配置和效果可类似于上面参考图61描述的第二布局变形例的配置和效果,并且因此,这里将省略其详细描述。

[0542]

8.4第四布局变形例

[0543]

在第四布局变形例中,类似于第一布局变形例,将描述根据第一实施方式的第一共享示例的共享块221a(参考图32)的布局示例。图63是示出了根据第四布局变形例的共享块的布局示例的平面图。

[0544]

如图63中所示,在第四布局变形例中,布置在像素区域10中的响应电路301a1至

301a4全部被布置为面向相同的方向。即,在第四布局变形例中,相同布局的响应电路被周期性地布置在整个光接收部220中。

[0545]

通过采用这种布局,在第四布局变形例中,可以减小光电转换元件311相对于入射光的光轴的失准和配线布局中的像素之间的差异,使得可以减小相邻像素之间的灵敏度差和泄漏到相邻像素的光量的变化,从而提高整个光接收部220中的像素灵敏度的均匀性。

[0546]

其他配置和效果可类似于上面参考图60描述的第一布局变形例的配置和效果,并且因此,这里将省略其详细描述。

[0547]

8.5第五布局变形例

[0548]

在第五布局变形例中,将描述在像素电路370不包括在共享块中的情况下(即,在响应电路设计为evs的情况下)的布局示例。在这种情况下,响应电路301y(参照图64)可包括在第一实施方式中参照图7描述的对数响应部310/310a。图64是示出根据第五布局变形例的共享块的布局示例的平面图。

[0549]

如图64所示,在第五布局变形例中,光电转换元件311被布置在像素区域10的中心处,nmos晶体管312和315以及nmos晶体管313和316被布置为夹持光电转换元件311。nmos晶体管313的一个扩散区域与光电转换元件311连续。此外,通过将nmos晶体管312和315与布置在两个相邻像素区域10中的nmos晶体管313和316连接来配置一个响应电路301y。

[0550]

通过采用这种布局,可以相对于整个光接收部220周期性地布置具有相同布局的响应电路301y,因此,与第四布局变形例类似,可以减少光电转换元件311相对于入射光的光轴的失准以及在配线布局中的像素之间的差异。由此,能够减小相邻像素之间的灵敏度差和泄漏到相邻像素的光量的偏差,能够提高光接收部220整体的像素灵敏度的均匀性。

[0551]

其他配置和效果可类似于上面参考图36或图37描述的布局示例的配置和效果,并且因此在此省略其详细描述。

[0552]

8.6第六布局变形例

[0553]

在第六布局变形例中,将描述根据第五实施方式的第一共享示例的共享块821c(参考图55)的布局示例。即,第六布局变形例示出共享块821c被设计为用于evs的共享块,并且响应电路301c1至301c4中的每个包括单独控制晶体管318和单独控制晶体管319的情况。图65是示出了根据第六布局变形例的共享块的布局示例的平面图。

[0554]

如图65所示,第六布局变形例使用与上面参考图60描述的第一布局变形例类似的布局,其中布置单独控制晶体管319代替像素电路370和虚拟晶体管972。

[0555]

利用这种布局,可以将光电转换元件311布置在像素区域10的中心处,使得可以实现诸如抑制量子效率劣化和减少颜色混合的效果。此外,由于单独控制晶体管318被布置在2

×

2像素布局中的中心处,因此可以抑制由于感测节点sn的配线长度缩短而引起的合并模式下的等待时间的劣化。

[0556]

其他配置和效果可类似于上面参考图60描述的第一布局变形例的配置和效果,并且因此,这里将省略其详细描述。

[0557]

8.7第七布局变形例

[0558]

在第七布局变形例中,将描述根据第五实施方式的第三共享示例的共享块821cc(参考图57)的布局示例。即,第七布局变形例示出了共享块821c被设计为用于evs的共享块,并且响应电路301c1至301c4中的每个包括公共控制晶体管318和单独控制晶体管319的

n4电容和n3-n4电容大于在同一层内的配线之间由第一配线层m1形成的n1-n2电容、n1-n3电容、n1-n4电容和n3-n4电容。

[0573]

(第二条件)

[0574]

屏蔽层设置在由第二配线层或更高层形成的n1-n2电容、n1-n3电容、n1-n4电容和n3-n4电容与其上形成各种晶体管的半导体基板之间,以便减小n1配线/n3配线与半导体基板之间的电容。屏蔽层可以是包括另一配线层的配线(例如,电源线等),或者可以是通过从另一配线层去除配线图案而获得的剩余绝缘层。

[0575]

(第三条件)

[0576]

通过使用其中n1-n2电容、n1-n3电容、n1-n4电容和n3-n4电容由诸如梳齿结构的金属氧化物金属(mom)结构或使用配线层层间绝缘膜的金属绝缘体金属(mim)结构形成的配置,并且通过在基板侧上布置n4配线,节点n4与半导体基板之间的耦合电容(在下文中,称为n4-基板电容)增大,并且节点n1与半导体基板之间的耦合电容(在下文中,称为n1-基板电容)和节点n3与半导体基板之间的耦合电容(在下文中,称为n3-基板电容)减小。此时,例如,可以将第一配线层或各种晶体管的栅极用于n4配线。

[0577]

9.1配线结构示例

[0578]

接下来,将通过一些示例描述形成为满足上述条件中的至少一个的配线结构。以下,为了简单起见,对半导体基板(后述的半导体基板1001)和布置有节点n1-n4的配线层(后述的层间绝缘膜1010)进行说明。此外,在本说明书中,节点n1可表示上述感测节点sn。

[0579]

图67至图70是示出被设计为满足上述条件中的至少一个的配线结构的示例的示图。具体地,图67是示出了根据第一示例的配线结构的截面图;图68是示出了根据第二示例的配线结构的截面图;图69是示出根据第三示例的配线结构的截面图;以及图70是示出根据第四示例的配线结构的截面图。在第一示例至第四示例中,构成节点n1至n4的配线(在下文中,分别称为n1配线、n2配线、n3配线和n4配线)和电源线(vdd、gnd和vss)布置在三个配线层m1至m3上。然而,图67至图70是未暴露n2配线的截面图,并且因此,未示出n2配线。

[0580]

如图67至图70所示,在第一至第四示例中,构成像素电路370和/或对数响应部310/310a的各种晶体管1004形成在p型阱层1002中,p型阱层1002跨过栅极绝缘膜1003布置在半导体基板1001的元件形成表面侧上。在其上形成各种晶体管1004的元件形成表面上,存在包括n1配线、n2配线、n3配线、n4配线和电源线(vdd、gnd和vss)的层间绝缘膜1010。

[0581]

(第一配线层m1)

[0582]

在设置在层间绝缘膜1010中的三个配线层m1至m3中,最靠近半导体基板1001的第一配线层m1是主要布置n4配线的层。注意,其他配线(n1至n3配线、电源线等)的一部分或全部可以布置在第一配线层m1中以与设置在元件形成表面上的各种晶体管1004建立连接。

[0583]

布置在第一配线层m1中的n4配线可具有例如包括在平行于元件形成面的方向上延伸的两个或更多个梳齿的梳齿结构(在下文中,称为梳齿配线),如在图67中示出的第一示例中,或者可以是包括平行于元件形成面的主平面的实心图案,如在图68中示出的第二示例中。然而,配置不限于此,并且允许具有各种变形,诸如部分地具有梳齿结构、开口等的实心图案。

[0584]

以这种方式,通过将n4配线布置在最靠近半导体基板1001的第一配线层m1中,能够增大n4配线和半导体基板1001(包括阱层1002;这同样适用于下文)的耦合电容(n4-基板

电容)。此外,由于n4配线相对于形成在第二配线层m2或更高层的其他配线可用作屏蔽层,所以可抑制n1至n3配线与半导体基板1001之间的耦合电容(n1-基板电容、n2-基板电容和n3-基板电容)的增加。

[0585]

然而,该配置不限于此,并且如在图69所示的第三示例中,可允许采用其中n1至n4配线未布置在第一配线层m1中(参考区域r2-2)的配置。这使得可以保持形成在第二配线层m2或更高层的n1至n3配线与半导体基板1001之间的距离,导致抑制n1至n3配线与半导体基板1001之间的耦合电容的增加。

[0586]

此外,当如在图70中示出的第四示例中设置在半导体基板1001上的栅极1005用作节点n4时,其他配线(n1、n2和n3配线)可布置在第一配线层m1中的栅极1005上的区域中,并且n1-n4电容和n3-n4电容可由mim电容形成。

[0587]

(第二配线层m2)

[0588]

主要选自n1、n2和n3配线的一个或多个配线可布置在第一配线层m1上方的第二配线层m2中。然而,根据诸如调整配线之间的耦合电容的目的,一些或所有其他配线(n4配线、电源线等)可布置在第二配线层m2中。例如,如图67至图70所示,通过将形成n4配线的梳齿配线布置在各自构成n1配线、n2配线和n3配线的梳齿配线之间,梳齿电容形成在n1配线、n2配线和n3配线与n4配线之间,使得可以增加n1-n4电容、n2-n4电容和n3-n4电容。

[0589]

在图68示出的第二示例中,mim电容可形成在设置在第二配线层m2中的n1配线与设置在第一配线层m1中的n4配线之间。此外,在图70中示出的第四示例中,mim电容可形成在设置在第二配线层m2中的n3配线与设置在第一配线层m1中的栅极1005之间、以及在设置在第二配线层m2中的n1配线与设置在第一配线层m1中的栅极1005之间。

[0590]

(第三配线层m3及更高层)

[0591]

当第三配线层m3和更高配线层将设置在第二配线层m2上时,与第二配线层m2类似,可允许通过根据每个配线所需的耦合电容设置n1至n4配线和/或电源线来形成梳齿电容。

[0592]

此时,电源线(vdd、gnd和vss)优选设置在最上层(在该示例中,第三配线层m3)。这允许电源线用作防止来自外部(诸如检测芯片202)的电磁干扰的屏蔽层,从而提高操作稳定性。

[0593]

此外,n4配线可以进一步设置在最上层上,以在n4配线与电源线之间形成梳齿电容。

[0594]

另外,在上述构成的梳齿电容中,由n4配线和另一配线构成的梳齿电容优选构成为使得n4配线配置在最外周。此外,电源线可以设置为紧邻位于最外周的n4配线。

[0595]

9.2效果

[0596]

通过设计n1至n4配线和电源线(vdd、gnd和vss)以满足如上所述的第一至第三条件中的至少一个,能够实现以下效果。

[0597]

通过将n4配线设置在第一配线层m1中并且将具有n1至n3配线的梳齿电容设置为第二配线层m2或更高层中的一侧电极,第一配线层m1可用作屏蔽n1至n3配线与电源线(vdd、gnd和vss)之间的电场的屏蔽层。由此,能够降低n1至n3配线与半导体基板1001之间的耦合电容,从而能够降低bgr。

[0598]

通过将n4配线布置在第一配线层m1中并且形成具有大面积的n4-基板电容,导致

形成具有大电容的n4-基板电容,使得可以显著减小bgr。

[0599]

通过将作为梳齿电容的n3-n4电容、n2-n4电容、n1-n4电容、n1-n3电容、n1-n2电容和n4-电源线电容布置在第二配线层m2或更高层中,可以增加这些电容而不增加n1至n4配线与半导体基板1001之间的耦合电容,从而减小bgr。

[0600]

通过将n4配线布置在第一配线层m1中并且将n1至n3配线布置在第二配线层m2中,n1至n3配线与n4配线之间的耦合电容由构成层间绝缘膜1010的层间绝缘膜形成,从而减小bgr。

[0601]

利用由n4配线形成的梳齿电容的最外周,位于同一层中的n1配线至n3配线与电源线之间的耦合被位于同一层中的n4配线屏蔽。这使得可以在减小n1至n3配线与电源线之间的耦合电容的同时增加n4-电源线电容。这使得可以减小bgr。

[0602]

9.3配线布局的具体示例

[0603]

接下来,将描述根据本实施方式的n1至n4配线和电源线(vdd、gnd和vss)的具体布局示例。为了简单起见,下面的描述集中于为响应电路301布置的n1~n4配线以及电源线(vdd、gnd和vss)。此外,本示例将描述层间绝缘膜1010包括第一配线层m1至第四配线层m4的四层的示例性情况。

[0604]

图71是示出了第一配线层m1的配线布局示例的平面图;图72是示出了第二配线层m2的配线布局示例的平面图;图73是示出了第三配线层m3的配线布局示例的平面图;以及图74是示出了第四配线层m4的配线布局示例的平面图。此外,图75是示出了沿着图71至图74中的线a-a’截取的截面结构示例的截面图。此外,图76是示出了根据变形例的第一配线层m1的配线布局示例的平面图。

[0605]

如图71至图75所示,第一配线层m1具有这样的配置,其中,具有梳齿结构的n4配线层设置在像素区域10的大部分区域中,并且电源线(vdd、gnd和vss)被布置为包围n4配线的外周。在第一配线层m1中,布置了n1至n3配线的一部分以电连接至构成响应电路301的各种晶体管。

[0606]

在第二配线层m2中,相应的梳齿配线被布置成使得n4配线和n1或n3配线交替地布置。此时,n4配线布置在最外周。在第三配线层m3中,以围绕n4配线的方式布置电源线vdd。

[0607]

在作为最上层的第四配线层m4中,各个梳齿配线被布置成使得n4和n3配线交替地布置,并且其外周被电源线gnd包围。

[0608]

如图71和图72所示,设置在特定配线层(本示例中的第一配线层m1)中的梳齿配线的延伸方向和设置在另一配线层(本示例中的第二配线层m2)中的梳齿配线的延伸方向优选地彼此不平行(在此示例中垂直)。利用该配置,已经穿过光电转换元件311并且进入层间绝缘膜1010的光可以由n1至n4配线和电源线反射并且返回至光电转换元件311,由此导致量子效率的提高。

[0609]

如图76所示,设置在第一配线层m1中的n4配线可以是实心(solid,非中空)图案,而不是如上所述的梳齿结构。

[0610]

10.第十实施方式

[0611]

接下来,将描述本公开的第十实施方式。在上述实施方式中,当evs模式和cis模式被同时驱动时,存在感测节点sn的电位由于当像素电路370的传输晶体管372被驱动时的传输信号trg的电位变化而波动的可能性,并且该波动在evs操作中引起错误检测和死区时间

段。这将使用图77中所示的共享块的电路配置示例以及图78中所示的将传输晶体管372和开关晶体管317与驱动线tg11至tg42连接的示例进行描述。尽管图77中所示的共享块221z具有从上面参考图32所描述的共享块221a中省略控制晶体管318的配置,但是这仅仅是示例,并且共享块221z的配置不限于该示例。

[0612]

如图77所示,在同时驱动evs模式和cis模式的混合模式中,构成共享块221x的总共4个像素(例如,响应电路301a1至301a4)中的一个像素(例如,响应电路301a1)在evs模式中操作,以恒定地检测亮度变化,而其余三个像素(例如,响应电路301a2至301a4)在cis模式中操作,从而以预定帧率生成灰度图像。这使得可以针对在evs模式中检测到亮度变化的区域获取发生亮度变化时的灰度图像。

[0613]

然而,如图78所示,在混合模式中,用于将信号电荷从光电转换元件311传输到浮置扩散区374的传输信号以预定周期重复地施加到驱动线tg22、tg32和tg42,驱动线tg22、tg32和tg42连接到在cis模式中操作的三个像素(响应电路301a2至301a4;在下文中,在cis模式下操作的像素也被称为cis像素(对应于上述灰度像素)的传输晶体管372的栅极,而断开电压被恒定地施加到驱动线tg12,驱动线tg12连接到在evs模式下操作的像素(响应电路301a1;以下,在evs模式下操作的像素也被称为evs像素(对应于上述的检测像素)的传输晶体管372的栅极。

[0614]

因此,当在连接到cis像素(响应电路301a2至301a4)的驱动线tg22、tg32和tg42与evs像素中的感测节点sn(响应电路301a1)之间存在耦合电容时,感测节点sn的sn电位由于根据施加到驱动线tg22、tg32和tg42的传输信号的电位变化的静电感应而波动。这将对evs像素的对数响应部310/310a的操作具有影响,类似于当cis模式转变到evs模式时sn电位波动的情况,导致发生错误检测或死区时间段的可能性。顺便提及,例如,除了传输信号之外,感测节点sn的sn电位的这种波动同样可通过选择信号或重置信号发生。

[0615]

因此,本实施方式减小了各自连接至cis像素的传输晶体管372、选择晶体管376、以及复位晶体管373中的每一个的栅极的驱动线与evs像素的感测节点sn之间的耦合电容,从而避免由传输信号引起的感测节点sn的sn电位的波动导致的问题。

[0616]

10.1截面结构和配线布局示例

[0617]

图79是示出了根据本实施方式的配线结构示例的截面图。为了简化描述,图79示出了半导体基板1001和其上布置节点n1至n4的层间绝缘膜1010的摘录。图80是示出了第一配线层m1的配线布局示例的平面图;图81是示出了第二配线层m2的配线布局示例的平面图;图82是示出了第三配线层m3的配线布局示例的平面图;以及图83是示出了第四配线层m2的配线布局示例的平面图。

[0618]

如图79至图83所示,在本实施方式中,连接至构成像素电路370的传输晶体管372、复位晶体管373以及选择晶体管376的栅极的驱动线ld设置在与感测节点sn不同的配线层中。图79至图83中的示例示出了驱动线ld的驱动线tg11被布置在第四配线层m4(其是层间绝缘膜1010中的最上层)中,并且感测节点sn被布置在第一配线层m1和第二配线层m2中的情况。

[0619]

此外,在本实施方式中,在驱动线ld与感测节点sn之间设置有用作电磁屏蔽的配线(在下文中,也称为屏蔽配线)1012。图79中的示例示出了屏蔽配线1012布置在第一配线层m1与其中布置感测节点sn的第二配线层m2之间的第三配线层m3和其中布置驱动线ld的

第四配线层m4中的情况。屏蔽配线1012可以是例如n2至n4配线、电源线(vdd、gnd和vss)等。

[0620]

此外,驱动线ld通过形成在层间绝缘膜1010中的通孔配线1011连接到设置在半导体基板1001的元件形成表面上的像素电路370(图79至图83中所示的示例中的传输晶体管372)。因此,在驱动线ld设置在感测节点sn上方的配线层中的情况下,将驱动线ld和像素电路370彼此连接的配线(也是驱动线ld的一部分)穿过设置有感测节点sn的配线层。因此,在本实施方式中,在与设置有感测节点sn的配线层相同的层中,起到电磁屏蔽作用的屏蔽配线1012设置在穿透配线层的驱动线ld与感测节点sn之间。在图79至图83所示的示例中,屏蔽配线布置在驱动线ld与另一响应电路301a2(和301a3、301a4)中的感测节点sn之间的区域r12中,驱动线ld在区域r13中并将第四配线层m4的驱动线tg11和响应电路301a1中的传输晶体管372的栅极彼此连接。屏蔽配线可以是例如n2至n4配线、电源线(vdd、gnd和vss)等。

[0621]

通过以这种方式在感测节点sn与驱动线ld之间设置屏蔽配线1012,可以减小感测节点sn与驱动线ld之间的耦合电容。这抑制了由于施加至驱动线ld的驱动信号的电位变化而引起的sn电位的波动,使得可以抑制错误检测和死区时间段的发生。

[0622]

此外,在本实施方式中,连接驱动线ld与半导体基板1001上的各种晶体管的栅极的配线(例如,图79至图83中所示的示例中的区域r13中的驱动线ld)大致垂直于半导体基板1001的元件形成表面。这使得可以减小感测节点sn与驱动线ld之间的对向面积,从而导致感测节点sn与驱动线ld之间的耦合电容的减小。由此,能够抑制因施加于驱动线ld的驱动信号而引起的sn电位的变动,能够抑制错误检测和死区时间段的发生。

[0623]

11.应用于移动体的示例

[0624]

根据本公开的技术(本技术)可应用于各种产品。根据本公开的技术可应用于安装在任何移动体上的装置,移动体诸如,汽车、电动车辆、混合电动车辆、摩托车、自行车、个人移动性、飞机、无人机、船舶以及机器人。

[0625]

图84是描绘作为可应用根据本公开的实施方式的技术的移动体控制系统的示例的车辆控制系统的示意性配置的示例的框图。

[0626]

车辆控制系统12000包括经由通信网络12001彼此连接的多个电子控制单元。在图84所示的示例中,车辆控制系统12000包括驱动系统控制单元12010、车身系统控制单元12020、车外信息检测单元12030、车内信息检测单元12040以及综合控制单元12050。另外,作为综合控制单元12050的功能配置,例示了微型计算机12051、声音/图像输出部12052、车载网络接口(i/f)12053。

[0627]

驱动系统控制单元12010根据各种程序控制与车辆的驱动系统相关的装置的操作。例如,驱动系统控制单元12010用作用于产生车辆的驱动力的驱动力产生装置(诸如内燃机、驱动电机等)、用于将驱动力传递到车轮的驱动力传递机构、用于调节车辆的转向角的转向机构、用于产生车辆的制动力的制动装置等的控制装置。

[0628]

车身系统控制单元12020根据各种程序来控制设置在车身上的各种装置的操作。例如,车身系统控制单元12020用作用于无钥匙进入系统、智能钥匙系统、电动车窗装置或诸如前照灯、后备灯、制动灯、转向信号灯、雾灯等的各种灯的控制装置。在这种情况下,从作为钥匙的替代物的移动装置发送的无线电波或各种开关的信号可以被输入到车身系统控制单元12020。车身系统控制单元12020接收这些输入的无线电波或信号,并且控制车辆

的门锁装置、电动车窗装置、灯等。

[0629]

车外信息检测单元12030检测包含车辆控制系统12000的车辆外部的信息。例如,车外信息检测单元12030连接有成像部12031。车外信息检测单元12030使成像部12031拍摄车外的图像,并接收该拍摄图像。车外信息检测单元12030可以基于接收到的图像,进行检测诸如人、车辆、障碍物、标志、路面上的文字等对象的处理、或者检测其距离的处理等。

[0630]

成像部12031是接收光并且输出对应于接收到的光的光量的电信号的光学传感器。成像部12031可以输出电信号作为图像,或者可以输出电信号作为关于测量距离的信息。此外,成像部12031接收的光可以是可见光,或者可以是诸如红外线等不可见光。

[0631]

车内信息检测单元12040检测关于车辆内部的信息。车内信息检测单元12040例如与检测驾驶员的状态的驾驶员状态检测部12041连接。驾驶员状态检测部12041例如包括拍摄驾驶员的照相机。基于从驾驶员状态检测部12041输入的检测信息,车内信息检测单元12040可以计算驾驶员的疲劳度或驾驶员的集中度,或者可以确定驾驶员是否打瞌睡。

[0632]

微型计算机12051可以基于关于车辆内部或外部的信息来计算驱动力生成装置、转向机构或制动装置的控制目标值,其中,关于车辆内部或外部的信息是由车外信息检测单元12030或车内信息检测单元12040获得的信息,并且微型计算机12051向驱动系统控制单元12010输出控制命令。例如,微型计算机12051可以执行旨在实现高级驾驶员辅助系统(adas)的功能的协作控制,该功能包括用于车辆的防碰撞或减震、基于跟随距离的跟随驾驶、车辆速度保持驾驶、车辆碰撞的警告、车辆与车道的偏离的警告等。

[0633]

另外,微型计算机12051通过基于由车外信息检测单元12030或车内信息检测单元12040获得的关于车辆内部或外部的信息来控制驱动力产生装置、转向机构、制动装置等,可以执行用于自动驾驶的协作控制,这使得车辆不依赖于驾驶员的操作等而自动行驶。

[0634]

另外,微型计算机12051可以基于由车外信息检测单元12030获得的关于车辆外部的信息,将控制命令输出到车身系统控制单元12020。例如,微型计算机12051可以通过根据由车外信息检测单元12030检测的前方车辆或对面车辆的位置,控制前照灯以从远光改变到近光,来执行旨在防止眩光的协作控制。

[0635]

声音/图像输出部12052将声音和图像中的至少一个的输出信号发送到输出装置,该输出装置能够视觉地或听觉地将信息通知给车辆的乘员或车辆外部。在图85的示例中,音频扬声器12061、显示部12062和仪表板12063被示为输出设备。例如,显示部12062可包括板上显示器和平视显示器中的至少一个。

[0636]

图85是描述成像部12031的安装位置的示例的示意图。

[0637]

在图85中,成像部12031包括成像部12101、12102、12103、12104和12105。

[0638]

成像部12101、12102、12103、12104和12105例如设置在车辆12100的前鼻、侧视镜、后保险杠和后门上的位置以及车辆内部的挡风玻璃的上部的位置上。设置在前鼻的成像部12101和设置在车辆内部挡风玻璃的上部的成像部12105主要获得车辆12100的前方的图像。设置到侧视镜的成像部12102和12103主要获得车辆12100的侧面的图像。设置到后保险杠或后门的成像部12104主要获得车辆12100的后部的图像。设置在车辆内部挡风玻璃的上部的成像部12105主要用于检测前方车辆、行人、障碍物、信号、交通标志、车道等。

[0639]

顺便提及,图85描述了成像部12101至12104的拍摄范围的示例。拍摄范围12111表示设置到前鼻的成像部12101的拍摄范围。拍摄范围12112和12113分别表示设置到侧视镜

的成像部12102和12103的拍摄范围。拍摄范围12114表示设置到后保险杠或后门的成像部12104的拍摄范围。例如,通过叠加由成像部12101至12104成像的图像数据来获得从上方观看的车辆12100的鸟瞰图像。

[0640]

成像部12101至12104中的至少一个可具有获得距离信息的功能。例如,成像部12101至12104中的至少一个可以是由多个成像元件构成的立体相机,或者可以是具有用于相位差检测的像素的成像元件。

[0641]

例如,微型计算机12051可以基于从成像部12101至12104获得的距离信息确定到拍摄范围12111至12114内的每个三维物体的距离以及该距离的时间变化(相对于车辆12100的相对速度),并且由此提取最近的三维物体作为前方车辆,该最近的三维物体具体地存在于车辆12100的行驶路径上并且以预定速度(例如,等于或大于0km/小时)在与车辆12100基本相同的方向上行驶。另外,微型计算机12051可以预先设定与前方车辆的前方保持的跟随距离,并且执行自动制动控制(包括跟随停止控制)、自动加速控制(包括跟随起动控制)等。由此,能够进行不依赖于驾驶员的操作等而使车辆自动行驶的用于自动驾驶的协作控制。

[0642]

例如,微型计算机12051可以基于从成像部12101至12104获得的距离信息将与三维物体有关的三维物体数据分类为二轮车、标准车辆、大型车辆、行人、电线杆和其他三维物体的三维物体数据,提取分类的三维物体数据,并且将所提取的三维物体数据用于自动躲避障碍物。例如,微型计算机12051将车辆12100周围的障碍物识别为车辆12100的驾驶员可以视觉识别的障碍物和车辆12100的驾驶员难以视觉识别的障碍物。然后,微型计算机12051确定指示与每个障碍物碰撞的风险的碰撞风险。在碰撞风险等于或高于设定值并且因此存在碰撞可能性的情况下,微型计算机12051经由音频扬声器12061或显示部12062向驾驶员输出警告,并且经由驾驶系统控制单元12010执行强制减速或躲避转向。微型计算机12051可由此辅助驾驶以避免碰撞。

[0643]

成像部12101至12104中的至少一个可以是检测红外线的红外相机。微型计算机12051例如可以通过确定在成像部12101至12104的拍摄图像中是否存在行人来识别行人。行人的这种识别例如通过提取作为红外照相机的成像部12101至12104的拍摄图像中的特征点的过程以及通过对表示物体的轮廓的一系列特征点执行图案匹配处理来确定是否是行人的过程来执行。当微型计算机12051确定在成像部12101到12104的拍摄图像中存在行人并因此识别出行人时,声音/图像输出部12052控制显示部12062,使得用于强调的正方形轮廓线被显示为叠加在识别出的行人上。声音/图像输出部12052还可控制显示部12062,使得在期望位置处显示表示行人的图标等。

[0644]

在上文中,已经描述了根据本公开的技术可应用的车辆控制系统的示例。根据本公开的技术可适当地应用于上述配置之中的成像部12031。具体而言,图1中的成像装置100可应用于成像部12031。通过将根据本公开的技术应用于成像部12031,可以实现像素的微制造和在捕获图像中更高的可视性,从而缓解驾驶员的疲劳。

[0645]

应注意,上述实施方式示出了用于体现本技术的示例,并且实施方式中的事项和在权利要求中指定事项的本发明具有对应关系。类似地,权利要求中指定本发明的事项和本技术的实施方式中由与指定本发明的事项相同的名称表示的事项具有对应关系。然而,本技术不限于实施方式,并且在不背离本技术的范围和精神的情况下,可以通过对实施方

式做出各种修改来体现。

[0646]

本说明书中描述的效果仅是示例,并且因此,可存在不限于示例性效果的其他效果。

[0647]

应注意,本技术还可具有以下配置。

[0648]

(1)一种固态成像装置,包括:

[0649]

多个像素,各自输出入射光的亮度变化;以及

[0650]

检测电路,基于从每个所述像素输出的所述亮度变化输出事件信号,

[0651]

其中,每个像素包括:

[0652]

光电转换元件,根据入射光量产生电荷;

[0653]

对数转换电路,连接到所述光电转换元件,并将从所述光电转换元件流出的光电流转换为对应于所述光电流的对数值的电压信号;以及

[0654]

第一晶体管,所述第一晶体管的漏极连接至所述对数转换电路的感测节点。

[0655]

(2)根据(1)所述的固态成像装置,

[0656]

其中,第一晶体管的源极连接到等于或高于参考电位并且低于电源电压的第一电位。

[0657]

(3)根据(2)所述的固态成像装置,

[0658]

其中,每个所述像素进一步包括第一电路,所述第一电路基于从所述对数转换电路输出的所述电压信号输出已经进入所述光电转换元件的所述入射光的亮度变化,以及

[0659]

所述检测电路包括第二电路,所述第二电路基于从每个所述像素输出的所述亮度变化输出所述事件信号。

[0660]

(4)根据(2)所述的固态成像装置,其中所述参考电位是负电位或地电位。

[0661]

(5)根据(2)所述的固态成像装置,其中所述第一电位是比在所述对数转换电路的正常操作时所述感测节点的电位更低的电位。

[0662]

(6)根据(2)至(5)中任一项所述的固态成像装置,

[0663]

其中,所述对数转换电路包括:

[0664]

第二晶体管,具有连接至所述光电转换元件的栅极;以及

[0665]

第三晶体管,具有连接至所述光电转换元件的源极,

[0666]

所述第三晶体管的栅极连接至所述第二晶体管的漏极,以及

[0667]

所述感测节点是连接到所述第二晶体管的栅极的配线。

[0668]

(7)根据(6)所述的固态成像装置,其中每个像素进一步包括第四晶体管,第四晶体管的漏极连接至第二晶体管的栅极和第三晶体管的源极,并且所述第四晶体管的源极连接至光电转换元件。

[0669]

(8)根据(7)所述的固态成像装置,

[0670]

其中,每个所述像素还包括:

[0671]

第五晶体管,其源极连接到所述光电转换元件;以及

[0672]

读出电路,所述读出电路连接到所述第五晶体管的漏极,并且根据在所述光电转换元件中生成的电荷生成像素信号。

[0673]

(9)根据(8)所述的固态成像装置,其中所述第一晶体管通过所述第五晶体管和所述第四晶体管连接至所述感测节点。

[0674]

(10)根据(8)或(9)所述的固态成像装置,其中每个所述像素还包括第六晶体管,所述第六晶体管连接到所述第四晶体管的漏极和所述第五晶体管的漏极。

[0675]

(11)根据(10)所述的固态成像装置,其中,所述第一晶体管通过所述第六晶体管连接至所述感测节点。

[0676]

(12)根据(8)至(11)中任一项所述的固态成像装置,

[0677]

其中,所述读出电路包括所述第一晶体管,所述第一晶体管的源极连接到所述第五晶体管的漏极并且其漏极连接到所述第一电位。

[0678]

(13)根据(12)所述的固态成像装置,其中每个所述像素还包括第六晶体管,所述第六晶体管连接到所述第四晶体管的漏极和所述第五晶体管的漏极。

[0679]

(14)根据(8)至(13)中任一项所述的固态成像装置,其中所述第一晶体管通过所述第四晶体管连接至所述感测节点。

[0680]

(15)根据(7)所述的固态成像装置,

[0681]

其中,每个所述像素还包括:

[0682]

第五晶体管,所述第五晶体管的源极连接至所述第四晶体管的漏极;以及

[0683]

第六晶体管,所述第六晶体管的漏极连接至所述第四晶体管的漏极、所述第三晶体管的源极以及所述第二晶体管的栅极,并且所述第六晶体管的源极连接至所述第五晶体管的漏极,以及

[0684]

所述第一晶体管通过所述第六晶体管连接至所述感测节点。

[0685]

(16)根据(15)所述的固态成像装置,

[0686]

其中,每个所述像素还包括读出电路,所述读出电路连接到所述第五晶体管的漏极并且根据在所述光电转换元件中生成的电荷生成像素信号,以及

[0687]

所述读出电路包括其源极连接到所述第五晶体管的漏极并且其漏极连接到所述第一电位的所述第一晶体管。

[0688]

(17)根据(1)至(16)中任一项所述的固态成像装置,其中,所述对数转换电路包括控制流过对数转换电路的电流的偏置电路。

[0689]

(18)根据(1)至(17)中任一项所述的固态成像装置,

[0690]

其中,每个所述像素进一步包括第五晶体管,所述第五晶体管的源极连接至所述光电转换元件,以及

[0691]

所述固态成像装置还包括共同连接所述多个像素之中的所述第五晶体管的漏极的公共线。

[0692]

(19)根据(18)所述的固态成像装置,进一步包括读出电路,所述读出电路连接至公共线并且根据在每个像素的光电转换元件中生成的电荷生成像素信号。

[0693]

(20)根据(18)或(19)所述的固态成像装置,其中所述第一晶体管连接至所述公共线并且由所述多个像素共享。

[0694]

(21)根据(1)至(20)中任一项所述的固态成像装置,

[0695]

其中,包括在所述多个像素的每一个中的所述光电转换元件在半导体基板的元件形成表面上布置成矩阵,以及

[0696]

所述第一晶体管在所述元件形成表面上设置在布置为所述矩阵的所述光电转换元件之间。

[0697]

(22)根据(10)所述的固态成像装置,

[0698]

其中,包括在多个像素的每一个中的光电转换元件在半导体基板的元件形成表面上布置成矩阵,以及

[0699]

所述第六晶体管在所述元件形成表面上设置在布置为所述矩阵的所述光电转换元件之间。

[0700]

(23)根据(21)或(22)所述的固态成像装置,其中,光电转换元件和第一晶体管在元件形成表面上周期性地布置在矩阵中。

[0701]

(24)一种固态成像装置,包括:

[0702]

多个像素,各自输出入射光的亮度变化;以及

[0703]

检测电路,基于从每个所述像素输出的所述亮度变化输出事件信号,

[0704]

其中,每个像素包括:

[0705]

光电转换元件,根据入射光量产生电荷;以及

[0706]

对数转换电路,连接到所述光电转换元件并且将从所述光电转换元件流出的光电流转换为对应于所述光电流的对数值的电压信号,

[0707]

包括在所述多个像素的每一个中的所述光电转换元件在半导体基板的元件形成表面上布置成矩阵,

[0708]

所述对数转换电路包括:

[0709]

第一晶体管,其栅极连接至所述光电转换元件;

[0710]

第二晶体管,其源极连接到所述光电转换元件并且其栅极连接到所述第一晶体管的漏极;

[0711]

第三晶体管,其源极连接到所述第一晶体管的漏极和所述第二晶体管的栅极,其栅极连接到所述第二晶体管的漏极;以及

[0712]

第四晶体管,其源极连接到所述第二晶体管的漏极和所述第三晶体管的栅极,并且其栅极连接到所述第三晶体管的漏极,

[0713]

所述固态成像装置还包括:

[0714]

第一配线,连接到所述第一晶体管的栅极;

[0715]

第二配线,将第二晶体管的栅极和第一晶体管的漏极彼此连接;

[0716]

第三配线,将第三晶体管的栅极和第二晶体管的漏极彼此连接;以及

[0717]

第四配线,将所述第四晶体管的栅极和所述第三晶体管的漏极彼此连接,

[0718]

第一至第四配线在设置于半导体基板的元件形成表面侧的层间绝缘膜中分散地布置成多个配线层,以及

[0719]

所述第四配线的至少一部分设置在设置于所述层间绝缘膜中的所述多个配线层中最靠近所述半导体基板的一侧的配线层中。

[0720]

(25)一种固态成像装置,包括:

[0721]

多个像素,各自输出入射光的亮度变化;以及

[0722]

检测电路,基于从每个所述像素输出的所述亮度变化输出事件信号,

[0723]

其中,每个像素包括:

[0724]

光电转换元件,根据入射光量产生电荷;以及

[0725]

对数转换电路,连接到所述光电转换元件并且将从所述光电转换元件流出的光电

流转换为对应于所述光电流的对数值的电压信号,

[0726]

包括在所述多个像素的每一个中的所述光电转换元件在半导体基板的元件形成表面上布置成矩阵,

[0727]

所述对数转换电路包括:

[0728]

第一晶体管,其栅极连接至所述光电转换元件;

[0729]

第二晶体管,其源极连接到所述光电转换元件的源极并其栅极连接到所述第一晶体管的漏极;

[0730]

第三晶体管,其源极连接到所述第一晶体管的漏极和所述第二晶体管的栅极,其栅极连接到所述第二晶体管的漏极;以及

[0731]

第四晶体管,其源极连接到所述第二晶体管的漏极和所述第三晶体管的栅极,并且其栅极连接到所述第三晶体管的漏极,

[0732]

所述固态成像装置还包括:

[0733]

第一配线,连接到所述第一晶体管的栅极;

[0734]

第二配线,将第二晶体管的栅极和第一晶体管的漏极彼此连接;

[0735]

第三配线,将第三晶体管的栅极和第二晶体管的漏极彼此连接;以及

[0736]

第四配线,将所述第四晶体管的栅极和所述第三晶体管的漏极彼此连接,

[0737]

第一至第四配线在设置于半导体基板的元件形成表面侧的层间绝缘膜中分散地布置在多个配线层中,以及

[0738]

第一至第四配线中的至少一个具有梳齿结构。

[0739]

(26)一种固态成像装置,包括:

[0740]

多个像素,各自输出入射光的亮度变化;以及

[0741]

检测电路,基于从每个所述像素输出的所述亮度变化输出事件信号,

[0742]

其中,每个像素包括:

[0743]

光电转换元件,根据入射光量产生电荷;以及

[0744]

对数转换电路,连接到所述光电转换元件并且将流出所述光电转换元件的光电流转换为对应于所述光电流的对数值的电压信号,

[0745]

包括在所述多个像素的每一个中的所述光电转换元件在半导体基板的元件形成表面上布置成矩阵,

[0746]

所述对数转换电路包括:

[0747]

第一晶体管,其栅极连接至所述光电转换元件;

[0748]

第二晶体管,其源极连接到所述光电转换元件且其栅极连接到所述第一晶体管的漏极;

[0749]

第三晶体管,其源极连接到所述第一晶体管的漏极和所述第二晶体管的栅极,其栅极连接到所述第二晶体管的漏极;以及

[0750]

第四晶体管,其源极连接到所述第二晶体管的漏极和所述第三晶体管的栅极,并且其栅极连接到所述第三晶体管的漏极,

[0751]

所述固态成像装置还包括:

[0752]

第一配线,连接到所述第一晶体管的栅极;

[0753]

第二配线,将第二晶体管的栅极和第一晶体管的漏极彼此连接;

[0754]

第三配线,将第三晶体管的栅极和第二晶体管的漏极彼此连接;以及

[0755]

第四配线,将所述第四晶体管的栅极和所述第三晶体管的漏极彼此连接,

[0756]

所述第一至第四配线在设置于所述半导体基板的所述元件形成面侧的层间绝缘膜中分散地布置在多个配线层中,

[0757]

所述第四配线的至少一部分设置在设置在所述层间绝缘膜中的所述多个配线层中的最靠近所述半导体基板的一侧的配线层中,以及

[0758]

设置在最靠近所述半导体基板的一侧的所述配线层中的所述第四配线的至少一部分具有实心图案。

[0759]

(27)一种固态成像装置,包括:

[0760]

多个像素,各自输出入射光的亮度变化;以及

[0761]

检测电路,基于从每个所述像素输出的所述亮度变化输出事件信号,

[0762]

其中,每个像素包括:

[0763]

光电转换元件,根据入射光量产生电荷;以及

[0764]

对数转换电路,连接到所述光电转换元件并且将流出所述光电转换元件的光电流转换为对应于所述光电流的对数值的电压信号,

[0765]

包括在所述多个像素的每一个中的所述光电转换元件在半导体基板的元件形成表面上布置成矩阵,

[0766]

所述对数转换电路包括:

[0767]

第一晶体管,其栅极连接至所述光电转换元件;

[0768]

第二晶体管,其源极连接到所述光电转换元件并且其栅极连接到所述第一晶体管的漏极;

[0769]

第三晶体管,其源极连接到所述第一晶体管的漏极和所述第二晶体管的栅极,其栅极连接到所述第二晶体管的漏极;以及

[0770]

第四晶体管,其源极连接到所述第二晶体管的漏极和所述第三晶体管的栅极,并且其栅极连接到所述第三晶体管的漏极,

[0771]

所述固态成像装置还包括:

[0772]

第一配线,连接到所述第一晶体管的栅极;

[0773]

第二配线,将第二晶体管的栅极和第一晶体管的漏极彼此连的;

[0774]

第三配线,将第三晶体管的栅极和第二晶体管的漏极彼此连接;以及

[0775]

第四配线,将所述第四晶体管的栅极和所述第三晶体管的漏极彼此连接,

[0776]

所述第一至第四配线在设置于所述半导体基板的元件形成面侧的层间绝缘膜中分散地布置在多个配线层中,

[0777]

最靠近所述半导体基板的配线层包括形成在所述半导体基板的所述元件形成表面上的一个或多个晶体管的栅极,以及

[0778]

所述第四配线的所述至少一部分是所述一个或多个晶体管中的至少一个的栅极。

[0779]

(28)一种固态成像装置,包括:

[0780]

多个像素,各自输出入射光的亮度变化;以及

[0781]

检测电路,基于从每个所述像素输出的所述亮度变化输出事件信号,

[0782]

其中,每个像素包括:

[0783]

光电转换元件,根据入射光量产生电荷;以及

[0784]

对数转换电路,连接到所述光电转换元件并且将流出所述光电转换元件的光电流转换为对应于所述光电流的对数值的电压信号,

[0785]

包括在所述多个像素的每一个中的所述光电转换元件在半导体基板的元件形成表面上布置成矩阵,

[0786]

所述对数转换电路包括:

[0787]

第一晶体管,其栅极连接至所述光电转换元件;

[0788]

第二晶体管,其源极连接到所述光电转换元件并且其栅极连接到所述第一晶体管的漏极;

[0789]

第三晶体管,其源极连接到所述第一晶体管的漏极和所述第二晶体管的栅极,其栅极连接到所述第二晶体管的漏极;以及

[0790]

第四晶体管,其源极连接到所述第二晶体管的漏极和所述第三晶体管的栅极,并且其栅极连接到所述第三晶体管的漏极,

[0791]

所述固态成像装置还包括:

[0792]

第一配线,连接到所述第一晶体管的栅极;

[0793]

第二配线,将第二晶体管的栅极和第一晶体管的漏极彼此连接;

[0794]

第三配线,将第三晶体管的栅极和第二晶体管的漏极彼此连接;

[0795]

第四配线,将第四晶体管的栅极和第三晶体管的漏极彼此连接;以及

[0796]

电源线,设置在所述层间绝缘膜中并连接到电源电压、接地和预定电位中之一,

[0797]

第一至第四配线在设置于半导体基板的元件形成表面侧的层间绝缘膜中分散地布置在多个配线层中,以及

[0798]

第四配线的至少一部分设置在比其中布置电源线的层中最靠近半导体基板的层更靠近半导体基板的位置处。

[0799]

(29)根据(24)至(28)中任一项所述的固态成像装置,其中,在设置于第一至第四配线中的最靠近半导体基板侧的配线层中的配线之间形成的耦合电容小于设置在位于最靠近半导体基板侧的配线层上方的配线层中的配线之间形成的耦合电容。

[0800]

(30)一种固态成像装置,包括:

[0801]

多个像素,各自输出入射光的亮度变化;以及

[0802]

检测电路,基于从每个所述像素输出的所述亮度变化输出事件信号,

[0803]

其中,每个像素包括:

[0804]

光电转换元件,根据入射光量产生电荷;以及

[0805]

对数转换电路,连接到所述光电转换元件并且将流出所述光电转换元件的光电流转换为对应于所述光电流的对数值的电压信号,

[0806]

包括在所述多个像素的每一个中的所述光电转换元件在半导体基板的元件形成表面上布置成矩阵,

[0807]

所述对数转换电路包括:

[0808]

第一晶体管,其栅极连接至所述光电转换元件;

[0809]

第二晶体管,其源极连接到所述光电转换元件并且其栅极连接到所述第一晶体管的漏极;以及

[0810]

感测节点,所述感测节点连接至所述第一晶体管的所述栅极,

[0811]

每个所述像素还包括:

[0812]

第三晶体管,其漏极连接至所述第一晶体管的栅极和所述第二晶体管的源极,并且其源极连接至所述光电转换元件;

[0813]

第四晶体管,其源极连接到所述光电转换元件;以及

[0814]

读出电路,所述读出电路连接到所述第四晶体管的漏极并且根据在所述光电转换元件中生成的电荷生成像素信号,

[0815]

所述固态成像装置还包括:

[0816]

第一驱动线,连接到所述第三晶体管的栅极;

[0817]

第二驱动线,连接到所述第四晶体管的栅极;以及

[0818]

一个或多个第三驱动线,连接到构成所述读出电路的一个或多个晶体管的栅极,

[0819]

所述第一至第三驱动线和所述感测节点在布置在所述半导体基板的所述元件形成表面的一侧上的层间绝缘膜中分散地布置在多个配线层中,并且

[0820]

所述第一驱动线至所述第三驱动线和所述感测节点被设置在所述多个配线层中的彼此不同的层中。

[0821]

(31)根据(30)所述的固态成像装置,还包括布置在感测节点与第一至第三驱动线之间的屏蔽层。

[0822]

(32)根据(31)所述的固态成像装置,其中,所述屏蔽层包括以下中的至少一个:连接至电源电压、接地电压或预定电位的电源线;以及在构成所述对数转换电路的配线中除所述感测节点之外的配线。

[0823]

(33)根据(30)至(32)中任一项所述的固态成像装置,其中,第一驱动线至第三驱动线被布置在多个配线层的最上层中。

[0824]

(34)根据(30)至(32)中任一项所述的固态成像装置,其中,将第一驱动线至第三驱动线中的至少一个与栅极彼此连接的配线基本上垂直于元件形成表面延伸。

[0825]

(35)一种成像装置,包括:

[0826]

根据(2)所述的固态成像装置;以及

[0827]

控制部,控制所述固态成像装置,

[0828]

其中,所述固态成像装置包括多个操作模式,并且

[0829]

所述控制部控制所述感测节点在切换所述固态成像装置的操作模式时的电位。

[0830]

(36)根据(35)所述的成像装置,

[0831]

其中,所述控制部在切换所述固态成像装置的操作模式时经由第一晶体管将第一电位施加到感测节点和/或光电转换元件的阴极。

[0832]

(37)根据(35)或(36)所述的成像装置,其中,所述控制部在切换所述固态成像装置的操作模式时切断流过所述对数转换电路的电流。

[0833]

参考标号列表

[0834]

100 成像装置

[0835]

110 光学部

[0836]

120 记录部

[0837]

130 控制部

[0838]

200 固态成像装置

[0839]

201 光接收芯片

[0840]

202、202a、1202 检测芯片

[0841]

211~213、231~233 通孔布置部

[0842]

220 光接收部

[0843]

221、221a、221c、221cc、221d、821、821c、821cc、821d、共享块

[0844]

240 信号处理电路

[0845]

251 行驱动电路

[0846]

252 列驱动电路

[0847]

260 地址事件检测部

[0848]

270 行adc

[0849]

280 行仲裁器

[0850]

300 检测像素

[0851]

301、301a~301n、301y、801a、801c、801d 响应电路

[0852]

305 检测电路

[0853]

310、310a 对数响应部

[0854]

311 光电转换元件

[0855]

312、313、315、316、347、512 nmos晶体管

[0856]

314、314a、314b、345、346、411、511 pmos晶体管

[0857]

314a、314b 偏置电路

[0858]

314c dac

[0859]

314d 偏置控制晶体管

[0860]

314e 恒定电流源

[0861]

317 开关晶体管

[0862]

318、319 控制晶体管

[0863]

320 检测块

[0864]

370 像素电路

[0865]

370a 读出电路

[0866]

372 传输晶体管

[0867]

373 复位晶体管

[0868]

374 浮置扩散区

[0869]

375 放大晶体管

[0870]

376 选择晶体管

[0871]

330 缓冲器

[0872]

340 差分器

[0873]

341、343 电容器

[0874]

342 反相器

[0875]

344 开关

[0876]

360 传送电路

[0877]

400 选择部

[0878]

410、420 选择器

[0879]

500 比较部

[0880]

510、520 比较器

[0881]

972、973 虚拟晶体管

[0882]

1001 半导体基板

[0883]

1002 阱层

[0884]

1003 栅极绝缘膜

[0885]

1004 晶体管

[0886]

1010 层间绝缘膜

[0887]

1011 通孔配线

[0888]

1012 屏蔽配线

[0889]

3101 公共线

[0890]

ld、tg11~tg42 驱动线

[0891]

m1 第一配线层

[0892]

m2 第二配线层

[0893]

m3 第三配线层

[0894]

m4 第四配线层

[0895]

n1 节点(n1配线)

[0896]

n2 节点(n2配线)

[0897]

n3 节点(n3配线)

[0898]

n4 节点(n4配线)

[0899]

sn 感测节点

[0900]

vsl 垂直信号线

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。