1.本发明关于射频电路,特别是一种切换射频信号的开关装置。

背景技术:

2.射频(radio frequency,rf)开关装置能引导射频信号通过一或多条传送路径,且广泛应用于电视、移动电话、无线通信装置及卫星通讯装置。然而,由于寄生电容的效应,射频开关装置可能无法关闭不该传送射频信号的传送路径,使射频开关装置无法正常运作。

技术实现要素:

3.本发明实施例提供一种开关装置,包含信号输入端及开关电路。信号输入端用以接收射频信号。开关电路耦接于信号输入端,其包含有第一晶体管及第二晶体管。第一晶体管包含控制端,用以接收第一控制电压以截止第一晶体管;第一端;及第二端。第二晶体管包含控制端,用以接收第二控制电压以截止第二晶体管;第一端,耦接于第一晶体管的第二端;及第二端。第二控制电压不同于第一控制电压。

4.本发明实施例提供另一种开关装置,包含信号输入端及开关电路。信号输入端用以接收射频信号。开关电路耦接于信号输入端,其包含有第一晶体管及第二晶体管。第一晶体管包含第一控制端,用以接收第一控制电压以截止第一晶体管;第二控制端,用以接收第一辅助电压;第一端;及第二端。第二晶体管包含第一控制端,用以接收第二控制电压以截止第二晶体管;第二控制端,用以接收第二辅助电压;第一端,耦接于第一晶体管的第二端;及第二端。第一辅助电压不同于第二辅助电压。

附图说明

5.图1为本发明实施例中的一种开关装置的电路示意图。图2为图1的开关装置的一种第一截止路径的等效电路图。图3为本发明实施例中的另一种开关装置的电路示意图。图4为图1或图3的开关装置的另一种第一截止路径的等效电路图。图5a显示晶体管的控制电压/辅助电压及截止电容值的关系。图5b显示晶体管的辅助电压及截止电容值的关系。图6为本发明实施例中一种电压产生电路的电路示意图。图7为图1或图3的开关装置的另一种开关电路的截止路径的电路示意图。图8为图1或图3的开关装置的另一种开关电路的截止路径的电路示意图。图9显示晶体管的组件尺寸的示意图。图10显示晶体管的第一端及第二端之间的距离的示意图。符号说明1,3:开关装置101,102,121,122:开关电路

14:参考电压端6:电压产生电路60:振荡器62:电荷泵电路64:分压电路c(1)至c(3):截止电容值cds1至cdsn、cgd1至cgdn及cgs1至cgsn:电容cds:等效电容值cp:寄生电容值coff:截止电容值d1至d3,d:漏极g1至g5,g:栅极p1至p3:信号端s1至s3,s:源极sds:距离soc:振荡信号scp:第二电压t1至tn:晶体管v1至v3:射频信号vb(1)至vb(n):辅助电压vc(1)至vc(n),vc(n):控制电压wg:宽度

具体实施方式

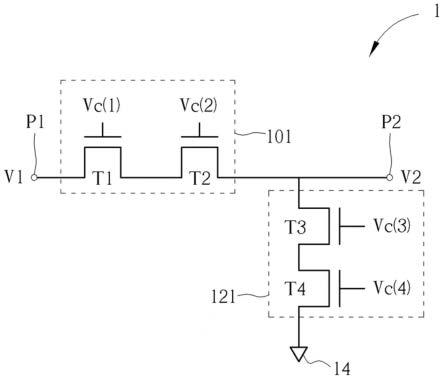

6.图1为本发明实施例中的一种开关装置1的电路示意图。开关装置1为单刀单掷(single-pole single throw,spst)开关,用以传送或接收射频信号。

7.开关装置1可包含信号端p1及p2、及开关电路101及121。在一些信号传送的实施例中,信号端p1可作为信号输入端,用以接收射频信号v1,且信号端p2可作为信号输出端,用以输出射频信号v2。在一些信号接收的实施例中,信号端p2可作为信号输入端,用以接收射频信号v2,且信号端p1可作为信号输出端,用以输出射频信号v1。

8.开关电路101耦接于信号端p1及p2,及可包含迭接的晶体管t1及t2。晶体管t1包含第一控制端、第一端及第二端。晶体管t2包含第一控制端、第一端,耦接于晶体管t1的第二端、及第二端。开关电路121耦接于信号端p2及开关电路101,及可包含迭接的晶体管t3及t4。晶体管t3包含第一控制端、第一端,耦接于晶体管t2的第二端、及第二端。晶体管t4包含第一控制端、第一端,耦接于晶体管t3的第二端、及第二端,耦接于参考电压端14,在一些实施例中,参考电压端14可为接地端。晶体管t1至t4可为相同种类的晶体管,且可为n型晶体管或p型晶体管。在图1中,晶体管t1至t4皆为nmos晶体管。

9.信号端p1及p2之间可被设置为导通状态或截止状态。于导通状态时,晶体管t1及t2可导通且晶体管t3及t4可截止,信号端p1及p2之间可形成第一导通路径,晶体管t1及t2

可视为串联的电阻。于截止状态时,晶体管t1及t2可截止且晶体管t3及t4可导通,信号端p1及p2之间可形成第一截止路径,晶体管t1及t2可视为串联的截止电容。于截止状态时,开关电路101中的每个迭接的晶体管的第一端及第二端之间的跨压实质上相同。例如,于截止状态时,开关电路101的晶体管t1的第一端及第二端之间的跨压实质上等于晶体管t2的第一端及第二端之间的跨压。因此在截止状态下,开关电路101中的每个迭接晶体管的第一端及第二端之间的跨压为平均分布(even voltage distribution),以减少迭接晶体管的数量同时防止晶体管导通或损坏。

10.虽然图1的开关电路101及开关电路121仅各自包含2晶体管,开关电路101及开关电路121亦可各自包含n晶体管及m晶体管,n及m为大于1的正整数,且n及m可相等或不相等。

11.在一些实施例中,图1中的开关电路121可包含其他数量的晶体管(例如包含1个晶体管),或对串联的晶体管(如t1、t2)施加以不同的控制电压/辅助电压,以使其于截止时具有不同的晶体管的截止电容值,以达到每个迭接晶体管的第一端及第二端之间的跨压为平均分布,以减少迭接晶体管的数量同时防止晶体管导通或损坏。其他组件的运作方式与原开关装置1相同,在此不再赘述。

12.图2开关装置1的一种第一截止路径的等效电路图。图2的开关装置1相似于图1,除了开关电路101包含3晶体管。图2显示第一晶体管的截止电容值c(1)、第二晶体管的截止电容值c(2)及寄生电容值cp、第三晶体管的截止电容值c(3)及寄生电容值cp及信号输入端20。截止电容值c(1)至c(3)可分别为截止状态时第一晶体管至第三晶体管的第一端及第二端之间的等效电容值。若第一晶体管至第三晶体管的晶体管大小相同、电容特性相同且具有相同偏压,则截止电容值c(1)至c(3)皆等于电容值cs。寄生电容值cp可为相应晶体管及芯片基底之间或相应晶体管及线路之间的等效电容值。寄生电容值cp的大小与制程相关,且寄生电容值cp对电容值cs的比值r可实质上为2%。图2的开关装置1可从信号输入端20接收射频信号而在截止的第一晶体管至第三晶体管产生跨压vx1至vx3。若截止电容值c(1)至c(3)的电容值皆相同,则寄生电容值cp的效应会导致截止电容值c(1)至c(3)的跨压vx1至vx3相异,如公式(1)所示:

13.vx1:vx2:vx3=(1 r)2:(1 r):1

ꢀꢀ

公式(1)

14.其中vx1至vx3分别为第一晶体管至第三晶体管的第一端及第二端之间的跨压;

15.r=cp/cs;

16.cp为寄生电容值;及

17.cs为第一晶体管至第三晶体管的任一晶体管的第一端及第二端之间的电容值。

18.公式(1)显示第一晶体管至第三晶体管的跨压vx1至vx3依序减小。第一晶体管t1可能会因为跨压vx1过大而崩溃,进而无法维持截止。因此需要对开关电路101的迭接晶体管的截止电容值进行补偿,以降低过大的跨压并减少迭接晶体管的数量。

19.为了补偿寄生电容值cp的效应,本发明实施例将截止电容值c(1)的电容值设为大于截止电容值c(2),且截止电容值c(2)设置为大于截止电容值c(3)。在一些实施中,开关电路101包含n晶体管,且第n晶体管的截止电容值c(n)可由第(n 1)晶体管的截止电容值c(n 1)及寄生电容值cp决定,如公式(2)所示:

20.c(n)=c(n 1) (n-n)*cp 公式(2)

21.其中c(n)及c(n 1)分别为第n晶体管及第(n 1)晶体管的截止电容值,n为小于n的

正整数;及

22.cp为寄生电容值;

23.例如在图2中,n=3,c(2)=c(3) cp,c(1)=c(2) 2cp。当截止电容值c(1)至c(n)符合公式(2)时,跨压vx1至vxn相同,即达成n晶体管的跨压平均分布的效果。

24.晶体管的截止电容值可由第一控制端的控制电压控制。参考图1,在一些实施中,于截止状态时,晶体管t1的第一控制端可接收控制电压vc(1)以截止晶体管t1,晶体管t2的第一控制端可接收控制电压vc(2)以截止晶体管t2,晶体管t3的第一控制端可接收控制电压vc(3)以导通晶体管t3,及晶体管t4的第一控制端可接收控制电压vc(4)以导通晶体管t4。控制电压vc(1)不同于控制电压vc(2)。在一些实施例中,控制电压vc(1)的绝对值小于控制电压vc(2)的绝对值。控制电压vc(3)可实质上等于或不同于控制电压vc(4)。例如,控制电压vc(3)可等于控制电压vc(1),控制电压vc(4)可等于控制电压vc(2)。在另一些实施例中,控制电压vc(1)及控制电压vc(2)之间的差值系正相关于射频信号的强度,且控制电压vc(3)实质上等于控制电压vc(4),藉以减少需提供负压的数量,并简化电路。

25.图3为本发明实施例中的另一种开关装置3的电路示意图。开关装置3系为单刀双掷(single-pole double throw,spdt)开关。开关装置3和开关装置1之间的差异在于开关装置3另包含信号端p3及开关电路102及122。以下针对开关装置3和开关装置1之间的差异进行解释。在一些信号传送的实施例中,信号端p1可作为信号输入端,用以接收射频信号v1,且信号端p2及p3中之一者可作为信号输出端,用以输出射频信号v2及v3中之一者。在一些信号接收的实施例中,信号端p2及p3中之一者可作为信号输入端,用以接收射频信号v2及v3中之一者,且信号端p1可作为信号输出端,用以输出射频信号v1。

26.信号端p1及p3之间可被设置为导通状态或截止状态。于导通状态时,晶体管t5及t6可导通且晶体管t7及t8可截止,信号端p1及p3之间可形成第二导通路径,晶体管t5及t6可视为串联的电阻。于截止状态时,晶体管t5及t6可截止且晶体管t7及t8可导通,信号端p1及p3之间可形成第二截止路径,晶体管t5及t6可视为串联的截止电容。在开关装置3运作时,信号端p1及p2与信号端p1及p3其中之一对之间可设置为导通状态,另一对之间可设置为截止状态。以下段落以信号端p1及p2之间形成第一截止路径及信号端p1及p3之间形成第二导通路径进行解释。

27.开关电路102耦接于信号端p1及p3,及可包含迭接的晶体管t5及t6。晶体管t5包含第一控制端、第一端及第二端。晶体管t6包含第一控制端、第一端,耦接于晶体管t5的第二端、及第二端。开关电路122耦接于信号端p3及开关电路102,及可包含迭接的晶体管t7及t8。晶体管t7包含第一控制端、第一端,耦接于晶体管t6的第二端、及第二端。晶体管t8包含第一控制端、第一端,耦接于晶体管t7的第二端、及第二端,耦接于参考电压端14。晶体管t1至t8可为相同种类的晶体管,且可为n型晶体管或p型晶体管。在图3中,晶体管t1至t8皆为nmos晶体管。

28.在一些实施例中,于形成第二导通路径时,晶体管t5的第一控制端可接收控制电压vc(5)以导通晶体管t5,晶体管t6的第一控制端可接收控制电压vc(6)以导通晶体管t6,晶体管t7的第一控制端可接收控制电压vc(7)以截止晶体管t7,及晶体管t8的第一控制端可接收控制电压vc(8)以截止晶体管t8。在一些实施例中,控制电压vc(1)实质上等于控制电压vc(7),控制电压vc(2)实质上等于控制电压vc(8),控制电压vc(3)系实质上等于控制

电压vc(5),及控制电压vc(4)实质上等于控制电压vc(6)。

29.在一些实施例中,图3中的开关电路121及122可包含其他数量的晶体管(例如各自包含1个晶体管),或对串联的晶体管(如t1、t2、t5、t6)施加以不同的控制电压/辅助电压,以使其于截止时具有不同的晶体管的截止电容值,以达到每个迭接晶体管的第一端及第二端之间的跨压为平均分布,以减少迭接晶体管的数量同时防止晶体管导通或损坏。其他组件的运作方式与原开关装置3相同,在此不再赘述。

30.图4为开关装置1或3的另一种第一截止路径是电路示意图。图4的开关装置相似于图1,除了开关电路101包含晶体管t1至tn。每个晶体管t1至tn皆包含第一控制端、第二控制端、第一端及第二端。晶体管t1至tn可为相同种类的晶体管,且可为n型晶体管或p型晶体管。在图4中,晶体管t1至tn皆为nmos晶体管。每个晶体管t1至tn的第一控制端可为栅极端,第二控制端可为基极(bulk)端,第一端可为漏极端及第二端可为源极端。每个晶体管t1至tn可通过各自的栅极电阻接收控制电压vc(1)至vc(n),通过各自的基极电阻接收辅助电压vb(1)至vb(n)。在一些实施例中,控制电压vc(1)至vc(n)及/或辅助电压vb(1)至vb(n)可用于控制晶体管t1至tn的截止电容值。

31.在一些实施例中,使用控制电压vc(1)至vc(n)及/或辅助电压vb(1)至vb(n)以用于控制晶体管t1至tn的截止电容值可适用于不同制程,例如:互补式金属氧化物半导体(cmos)制程、硅锗(sige)制程、绝缘层上覆硅(soi)制程,以及任何可以用于设计开关电路的制程。举例来说,使用不同控制电压以用于控制个别晶体管的截止电容值,使用不同辅助电压以用于控制个别晶体管的截止电容值,以及使用不同或相同控制电压及/或辅助电压以用于控制个别晶体管的截止电容值。以下以互补式金属氧化物半导体制程为例,说明使用不同辅助电压以用于控制个别晶体管的截止电容值的实施例。例如,在互补式金属氧化物半导体制程中使用辅助电压vb(1)至vb(n)以控制晶体管t1至tn的截止电容值。图5a所示,本发明控制不同变量,例如控制电压vc(1)至vc(n)及/或辅助电压vb(1)至vb(n)以得到晶体管t1至tn的适当截止电容coff,以此达到阻抗平均分布,使各个晶体管上有最合适的跨压。基本上这些电压参数与截止电容coff会成指数关系(exponential),藉由这些电压参数可以得到晶体管t1至tn各自的适当截止电容coff。

32.图5b显示晶体管tn的辅助电压vb(n)及截止电容值coff的关系,其中横轴表示辅助电压vb(n),纵轴表示截止电容值coff。当辅助电压vb(n)为非正值时,辅助电压vb(n)的绝对值与晶体管tn的截止电容值coff呈负相关。例如,以cmos 180nm制程为例,当辅助电压vb(n)等于0时,截止电容值coff的绝对值可约为0.4pf;当辅助电压vb(n)的绝对值等于4时,截止电容值coff可约为0.26pf。

33.在图4中,辅助电压vb(1)至vb(n)可设为0v或负值以截止晶体管t1至tn,且辅助电压vb(n)的绝对值可设为小于辅助电压vb(n 1)的绝对值,藉以使晶体管tn的截止电容值大于晶体管t(n 1)的截止电容值。在一些实施例中,辅助电压vb(1)至vb(n)至少其中之一者可为负值。例如,辅助电压vb(1)可设为-4v以使晶体管t1的截止电容值约等于0.26pf,辅助电压vb(2)可设-3.5v以使晶体管t2的截止电容值约等于0.27pf,辅助电压vb(1)的绝对值小于辅助电压vb(2)的绝对值,且晶体管t1的截止电容值大于晶体管t2。

34.在一些实施例中,辅助电压vb(n)实质上等于辅助电压vb(n 1)。例如,辅助电压vb(1)及辅助电压vb(2)可设为0v。在另一些实施例中,辅助电压vb(n)可设为实质上等于控制

电压vc(n),且辅助电压vb(n 1)可设为实质上等于控制电压vc(n 1)。例如,控制电压vc(1)及辅助电压vb(1)可设为-3.5v,且控制电压vc(2)及辅助电压vb(2)可设为-4v。在另一些实施例中,控制电压vc(n)及辅助电压vb(n)之间的压差不同于控制电压vc(n 1)及辅助电压vb(n 1)之间的压差。例如,控制电压vc(1)及辅助电压vb(1)之间的压差可设为4v,且控制电压vc(2)及辅助电压vb(2)之间的压差可设为3.5v。在另一些实施例中,辅助电压vb(n)及辅助电压vb(n 1)至少其中之一者为负值。例如,辅助电压vb(1)可设为0v,且辅助电压vb(2)可设为-0.5v。在另一些实施例中,控制电压vc(n)可与控制电压vc(n 1)相同,辅助电压vb(n)可不同于辅助电压vb(n 1)。例如,控制电压vc(n)及控制电压vc(n 1)可为0v,辅助电压vb(n)可为-3.5v,辅助电压vb(n 1)可为-4v。

35.图6为本发明实施例中一种电压产生电路6的电路示意图。电压产生电路6可产生控制电压vc(1)至vc(n),以供图1至图4的开关装置使用。电压产生电路6可包含振荡器60、电荷泵电路62及分压电路64。振荡器60可耦接于电荷泵电路62,电荷泵电路62可耦接于分压电路64。

36.振荡器60可产生振荡信号soc。振荡信号soc可为频率信号。电荷泵电路62可依据振荡信号soc将第一电压调整至第二电压scp。第一电压可为预定电压准位。第一电压及第二电压scp可同时为正压或负压,且第一电压的绝对值小于第二电压scp。分压电路64可依据第二电压scp产生控制电压vc(1)至控制电压vc(n)。在一些实施例中,电压产生电路6亦可产生辅助电压vb(1)至vb(n)。

37.在一些实施例中,晶体管的截止电容值可由晶体管的端点间电容值、组件尺寸(size)及长度控制,即晶体管t1至tn相异。

38.图7为开关装置1或3的另一种开关电路101的截止路径的电路示意图,藉由调整晶体管的端点间电容值而控制晶体管t1至tn的调整后截止电容值。图7的开关电路101包含晶体管t1至tn、电容cds1至cdsn、电容cgd1至cgdn及电容cgs1至cgsn。晶体管t1至tn可分别包含第一控制端、第一端及第二端。电容cgd1至cgdn可分别耦接于晶体管t1至tn的第一控制端及第一端之间,电容cgs1至cgsn可分别耦接于晶体管t1至tn的第一控制端及第二端之间,及电容cds1至cdsn可分别耦接于晶体管t1至tn的第一端及第二端之间。晶体管tn、电容cgd(n)、电容cgs(n)及电容cds(n)所产生的调整后截止电容值可大于晶体管t(n 1)、电容cgd(n 1)、电容cgs(n 1)及电容cds(n 1)所产生的调整后截止电容值。例如,电容cds1的电容值可等于cds2的电容值加上电容值(n-1)*cp,电容cgs(1)的电容值及电容cgs(2)的电容值可相等,电容cds(1)的电容值电容cds(2)的电容值可相等,使晶体管t1的调整后截止电容值等于晶体管t2的调整后截止电容值加上电容值(n-1)*cp。

39.在一些实施例中,开关电路101亦可包含电容cds1至cdsn、电容cgd1至cgdn及电容cgs1至cgsn的其中一种组合,用以控制晶体管t1至tn的调整后截止电容值。

40.图8为开关装置1或3的另一种开关电路101的截止路径的电路示意图。图8的开关电路101可藉由调整晶体管的组件尺寸而控制晶体管t1至tn的截止电容值。图8的开关电路101包含晶体管t1至tn,每个晶体管t1至tn的组件尺寸不同。在一些实施例中,晶体管tn的组件尺寸an可大于晶体管t(n 1)的组件尺寸a(n 1),如公式(3)所示:

41.an》a(n 1)

ꢀꢀ

公式(3)

42.组件尺寸可由栅极指节(finger)的宽度wg及数量m的乘积定义。图9显示晶体管的

组件尺寸的示意图,包含3漏极指节d1至d3,3源极指节s1至s3,5栅极指节g1至g5(m=5),每个栅极指节具有实质上相等的宽度wg。在一些实施例中,图8的晶体管t1至tn的栅极指节的数量m可依序减少。例如,晶体管t1可包含5栅极指节,晶体管t2可包含4栅极指节。

43.图8的开关电路101亦可藉由调整晶体管的长度而控制晶体管t1至tn的截止电容值。晶体管t1至tn的第一端及第二端之间之距离s1至sn可相异。在一些实施例中,晶体管tn的第一端及第二端之间的距离sn可小于晶体管t(n 1)的第一端及第二端之间的距离s(n 1),如公式(4)所示:

44.sn《s(n 1)公式(4)

45.图10显示晶体管的第一端及第二端之间的距离sds的示意图。当距离sds缩短时,晶体管的第一端及第二端之间的等效电容值cds会随之增加,藉以增加晶体管的截止电容值。在一些实施例中,图8的晶体管t1至tn的距离s1至sn可依序增加。例如,晶体管t1的距离s1可为1nm,晶体管t2的距离s2可为1.2nm。在一些实施例中,晶体管t(n)的距离s(n)可为晶体管t(n-1)的距离s(n-1)的1.5到1.6倍。例如晶体管t1的距离s1可为1nm,晶体管t2的距离s2可为1.5nm。

46.在一些实施例中,开关电路101亦可透过调整晶体管t1至tn的控制电压、辅助电压、端点间电容值、组件尺寸及长度中的一种组合而控制晶体管t1至tn的截止电容值,藉以达成晶体管t1至tn的跨压的平均分布。

47.图1-4、7-8中的实施例透过调整晶体管t1至tn的控制电压、辅助电压、端点间电容值、组件尺寸或长度而控制晶体管t1至tn的截止电容值,减少迭接晶体管的数量同时防止晶体管导通或损坏。以上所述仅为本发明的较佳实施例,凡依本发明权利要求范围所做的等同变化与修饰,皆应属本发明的涵盖范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。