1.一种基于时间同步的跟踪发信控制方法与装置,本发明属于信号传输技术领域,具体涉及基于时间同步的跟踪发信控制方法及装置技术领域。

背景技术:

2.随着现代通信技术水平的提高,通信技术的广泛应用已经为人类带来巨大的便利,逐渐地成为推动人类社会发展的重要力量之一,据北京研精毕智的统计数据分析,全球通信市场在2021年达到22473.78亿美元,通信设备的市场规模2020年达到约925亿美元。

3.另一方面,2021年全球网络犯罪造成损失超6万亿美元,这使人们不得不认真思考通信的安全问题,并不断通过提高技术手段来加强通信的安全性。通信安全涉及通信全过程中各环节的安全,其中传输过程的安全是重要的一环。通常在信号传输过程中为防止信息被非法获取,其防范手段之一就是采用数据加密的方式,让非法者即使获取了信息也不能从中得到有价值的内容;另一种手段就信道加密,让非法者难以捕获信道从而无法获取信息。

技术实现要素:

4.本发明的目的在于:提供一种基于时间同步的跟踪发信控制方法与装置,以解决上述现有的信息在传输的过程中不能进行同步跟踪,敌方容易捕获载波跳变的问题。

5.本发明采用的技术方案如下:

6.一种基于时间同步的跟踪发信控制方法与装置,包括基于时间同步的跟踪发信的控制方法和基于时间同步的跟踪发信的控制装置;

7.所述基于时间同步的跟踪发信的控制方法包括:基带数字载波信号产生的控制方法、待传输数据的编码成帧发送控制方法、信号的多路同步发送控制方法;

8.所述基于时间同步的跟踪发信的控制装置包括时钟驱动模块、时间获取模块、载频产生模块、载频控制模块、基带数据编码模块、高频调制与信道分割模块、显示控制模块、bd/gps授时接收模块、线路信号发送模块。

9.本技术的技术方案中,其特点是先在发信端产生一个本地时间数据,再从bd/gps授时接收模块获取一个标准北京时间数据,然后不断用标准北京时间数据刷新当前本地时间数据,从而获得本地时间完全同步于北京时间的标准控制时间。另一方面,产生m(m=1、2、3、

…

)个载波频率,将其组合为n(n=1、2、3、

…

)个频率组,每个频率组中包括j(j=1、2、3、

…

)个频率,并对每个频率进行编号,最后用标准控制时间的基本时间单元来选取j个频率,用这j个频率对待传输的数据进行按约定的帧格式编码,获得以h(h=1、2、3、

…

)位数据为一帧的基带传输信号。由于时间是在不断变化的,编码数据的传输码速也是不断变化的,这就使敌方难以通过固定的码速获取数据,从而达到信道加密的底层保护效果。更进一步地,在基带数据送往线路传输前,先将其调制到高频段去除直流分量,再将线路信道按时隙分割为k(k=1、2、3、

…

)个无线、fso或光纤载波频段信道上,使调制后的高频信号在不同时

隙由不同的传输信道进行传输。这样,即使敌方从某一信道中侦测到有信号传输,也只能获取部分不完整的数据片断,从而达到对传输信道的第二层保护作用;

10.其中基带数字载波信号产生的控制方法使通信双方每一时段所使用的数字载波频率是相同的,而不同时段所使用的数字载波频率是不相同的,同步时段的长度可以是时、分、秒、毫秒等单位,单位越小,数字载波频率变化越快,越难被敌方捕获;待传输数据的编码成帧发送控制方法使数据帧中各位的持续时间是数字载波周期的16倍,便于接收端进行采样。每个数据帧都有自己的独立起始位、数据位、奇偶校验位、停止位,便于独立传输和识别各帧;数字载波频率停留在一个载波频率的时间长度,大于一个数据帧传输所花时间的长度,避免1帧数据跨越两个数字载波频率;信号的多路同步发送控制方法将高频调制数据按时隙分配到k个不同的远程传输线路信道,即使某一远程信道被敌方捕获,只能截获部分片段信号,无法获取完整信号,加上基带载波的瞬时变化,从而进一步增加了信号传输的安全性。

11.进一步的,所述基带数字载波信号产生的控制方法,还包括如下步骤:

12.第一步:利用晶体振荡器输出的时钟信号在fpga芯片中产生本地基础时间,包括时、分、秒、毫秒等时间,以此作为系统发送数据的初始参照时间;

13.第二步:利用bd/gps授时接收模块获得标准北京时间包括时、分、秒、毫秒等时间,并将时间输出到fpag芯片,作为校准时间;

14.第三步:利用bd/gps授时的校准时间刷新本地参照时间,使本地电路产生的时间与标准北京时间一致,使通信发送端与接收端的时间刻度完全一致,以此作为通信双方同时控制数字载波频率选取的时间同步控制信号;

15.第四步:利用本地晶体振荡器输出的时钟信号,在fpga芯片中产生m个不同的数字载波信号,并将m(m=1、2、3、

…

)个载波信号组合成n(n=1、2、3、

…

)个载波频率组,每个载波编组中的载波数量为j(j=1、2、3、

…

)个,各载波按顺序进行编号,以便根据编号调用;每组中的各载波可以是不同的频率,也可以是相同的频率或部分相同的频率;

16.第五步:用外部输入的载波频率组选取控制信号,选取指定的载波编组,在fpga芯片中利用时间同步控制信号选取指定编组中的数字载波编号指定的频率;由于时间同步控制信号在不断变化,故数字载波也在不断变化,使通信双方的数字载波同步跟踪变化;。

17.进一步的,所述待传输数据的编码成帧发送控制方法,还包括如下步骤:

18.第一步:未传输数据时基带数据编码模块发送高电平直流信号,表示传输线路目前处于空闲状态,可以传输数据;

19.第二步:当欲传输数据时,先使高电平变为低电平,低电平的持续时间为数字载波信号持续16个周期的时间,称为一个传输比特位,表示一帧待传输数据的起始位;

20.第三步:开始传输数据,每一位待传输的1、0码数据的高电平或低电平持续时间占用1个传输比特位,每一帧数据的长度h由通信发送与接收双方约定;

21.第四步:设置一个奇偶校验位初始值,可以是0或1,由通信双方约定,每传输一位数据便与该初始值进行一次异或运算,以所有各位待传输数据运算后的结果作为本帧数据的奇偶位进行传输,h(h=1、2、3、

…

)位数据传输完后传输1比特的奇偶校验位;

22.第五步:发送至少1个传输比特位时长的高电平信号,表示1帧数据的结束,直到新的一帧数据开始传输;从数据开始到结束所传输的所有比特信号,称为1个基带数据帧,由

中包含h个待传输数据位。

23.进一步的,所述多路传输信号的同步发送控制方法还包括以下步骤:

24.第一步:用高频载波对编码后的基带数据帧进行调制,使其被搬移到高频载波信号频率上获得高频调制信号,以此去除掉基带数据帧中的直流成分;方法是将基带数据帧中的高电平信号,包括空闲信号、传输数据中的1信号、奇偶校验位的1信号、停止位的1信号,均用高频载波信号代替,传输的低电平位时信号保持不变;

25.第二步:利用k个信道分割控制信号将线路发送信道按时隙分割为k个传输信道,调制后的高频信号按时分方式轮流通过这k个传输信道;

26.第三步:将经过k个传输信道输出的信号调制到无线、fso或光纤载波频率的传输信道上进行远程传输。

27.进一步的,所述时钟驱动模块将输入的外部晶振时钟通过分频获得高频调制载波信号、k个线路信道时隙分割控制信号、显示驱动时钟信号;

28.所述时间获取模块将来自bd/gps授时接收模块接收的当前时间提取出来作为授时时间,同时由外部晶振时钟产生本地时间信号,然后不断用授时时间对本地时间刷新,使本地时间与授时时间一致,获得基带数据帧速率维持的标准控制时间。

29.更进一步的,所述bd/gps授时接收模块接收卫星下传的当前标准北京时间,并将该时间输出给fpga芯片;

30.所述载频产生模块产生进行基带数据帧编码时所需各种载波信号;

31.所述载频控制模块在当前标准时间控制下,从n个载波组中的m个数字载波频率中,按载波编号轮流选取一个作为基带数据帧编码在不同时段的载波;

32.所述基带数据编码模块将待传输的数据按空闲位、起始位、数据位、奇偶校验位、停止位的帧格式进行编码,产生以h位数据为一帧的基带数据。

33.更进一步的,所述高频调制与信道分割模块将基带数据帧调制到高频载波频率上,并将调制后的数据流按时隙轮流分配到k个无线、fso或光纤载波频段上;

34.所述线路信号发送模块将高频载波调制后的k路信号转换成无线、fso或光纤信号进行远程数据传输;

35.所述显示控制模块用于显示系统工作过程中的关键信号,方便随时掌握系统的工作状况,显示内容包括:时间同步控制信号的当前时间、当前时间选取的基带载波频率编号、当前正发送的数据。

36.综上所述,由于采用了上述技术方案,本发明的有益效果是:

37.可将bd/gps授时接收模块接收的北京时间与fpga芯片产生的本地时间修改为标准时间,并由该时间控制基带载波频率随着时间的变化而不断变化,导致基带数据码速不断变化,难以用固定的码速进行截获,从底层对信道进行保护;其次,按特殊格式设计的基带帧有独立的数据帧起止识别标志,可按约定帧长度独立进行各帧的传输;第三,将基带帧调制到高频传输,消除直流分量,使基带帧中空闲状态得以用数字载波进行传输,但却能让接收端可获得数据起始位和结束位的识别标志;第四,采用分时隙选择不同信道传输,使某个长途传输线路信道即使被侦测到,也只丢失片段数据,敌方难以获取完整数据,从而实现对传输信道的第二层保护。此外,本发明实施例的大部分硬件在fpga芯片内实现,使系统具有可靠性高、体积小和在系统可再编程能力。

附图说明

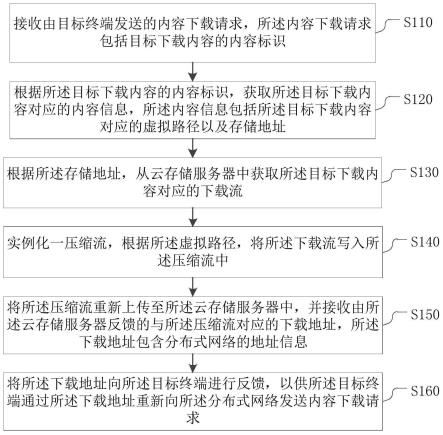

38.图1为本发明实施例中一种基于时间同步的跟踪发信控制方法的示意图。

39.图2为本发明实施例中一种基于时间同步的跟踪发信控制方法包括的基带数字载波信号产生的控制方法。

40.图3为本发明实施例中一种基于时间同步的跟踪发信控制方法包括的待传输数据的编码成帧发送控制方法。

41.图4为本发明实施例中一种基于时间同步的跟踪发信控制方法包括的信号的多路同步发送控制方法。

42.图5为本发明实施例中根据一种基于时间同步的跟踪发信控制方法所设计的一种基于时间同步的跟踪发信控制装置的示意图。

43.图6为本发明实施例中一种基于时间同步的跟踪发信控制装置集成在fpga芯片中的相关功能模块的一种电路连接关系的示意图。

44.图7为本发明实施例中一种基于时间同步的跟踪发信控制装置位于fpga芯片输出端的k个fso线路信号发送电路连接关系的示意图。

具体实施方式

45.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

46.请参阅图1-7,本实施例中提供了一种基于时间同步的跟踪发信控制方法与装置。

47.如图1所示为一种基于时间同步的跟踪发信控制方法涉及的整个控制过程,为详细描述该控制方法,可将该方法细化为:基带数字载波信号产生的控制方法、待传输数据的编码成帧发送控制方法、信号的多路同步发送控制方法;

48.图2所示为一种基于时间同步的跟踪发信控制方法包括的基带数字载波信号产生的控制方法,该方法包括如下步骤:

49.第一步:利用晶体振荡器输出的时钟信号在fpga芯片中产生本地基础时间,包括时、分、秒、毫秒等时间,这些时间在时钟驱动下按选取的最小时间单位不断计时当前本地时间,以此作为系统发送数据的初始参照时间;

50.第二步:利用bd/gps授时接收模块获得标准北京时间bdtimr,包括时、分、秒、毫秒等时间,这些时间可每秒进行几次更新,获得的时间被输出到fpag芯片中的时间获取模块,作为校准时间;

51.第三步:在fpga芯片中的时间获取模块利用bd/gps授时的校准时间刷新本地参照时间,使本地时间与标准北京时间一致,使通信接收端无论身处何地,只要用同样方法获得的标准北京时间,其时间刻度将会与通信发送端完全一致,以此时间作为通信双方同时控制选取相同数字载波频率的时间同步控制信号timctr[3:0],所选用作同步控制信号的时间可以是小时、分钟、秒钟、毫秒等。选用的时间单位越大,通信双方载波频率同步越容易,时间单位越小,每个载波持续时间越短,信道越安全。

[0052]

第四步:利用本地晶体振荡器输出的时钟驱动信号,在fpga芯片中的载频产生模块产生m个频率不同的数字载波信号,并将m个载波信号组合成n个载波频率组,每个载波编

组中的载波数量为j个,对各载波按顺序进行编号得到sfn[3:0],以便根据编号调用;每组中的各载波可以是不同的频率,也可以是相同的频率或部分相同的频率;

[0053]

第五步:用fpga芯片外部输入的载波频率组选取控制信号chsel[3:0],选取指定的载波编组,再用fpga芯片中的时间输出模块输出的同步控制信号timctr[3:0],选取指定载波编组中的数字载波编号所指定的频率clksp。由于时间同步控制信号在不断变化,故数字载波clksp也在不断变化,使通信双方的数字载波同步跟踪变化。例如若以秒钟为同步控制信号timctr[3:0],则第0秒选取编号为0的数字载波频率f0输出,第9秒选取编号为9的数字载波频率f9输出,这样随着秒钟从0到9的变化,载波频率编号指定的频率也变化了10个。

[0054]

图3所示为一种基于时间同步的跟踪发信控制方法包括的待传输数据的编码成帧发送控制方法,该方法包括如下步骤:

[0055]

第一步:在未传输数据的空闲时段fpga芯片中的基带数据编码模块的发送端tx输出高电平直流信号,表示传输线路目前处于空闲状态,可以传输数据;

[0056]

第二步:当欲传输数据时,基带数据编码模块的发送端tx由高电平变为低电平,低电平的持续时间为16个数字载波信号clksp周期,表示一帧待传输数据的起始位,这段时长也是每一个传输比特位的持续时间;

[0057]

第三步:开始传输数据,每一位待传输的1、0码数据的高电平或低电平持续时间占用1个传输比特位,每一帧所要传输的数据的长度h由通信发送与接收双方约定;

[0058]

第四步:设置一个奇偶校验位初始值,可以是0或1,由通信双方约定,每传输一位数据便与该初始值进行一次异或运算,以运算后的结果作为本帧数据的奇偶位进行传输,每一帧中的数据传输完后,发送端tx再传输1比特的奇偶校验位;

[0059]

第五步:发送至少1个传输比特位时长的高电平信号,表示一帧数据的结束,如果没有新的数据要传输,发送端tx就一直保持高电平;从数据开始到结束所传输的h位数据的总长度,称为1个基带数据帧;

[0060]

图4所示为一种基于时间同步的跟踪发信控制方法包括的多路同步发送控制方法,该方法包括如下步骤:

[0061]

第一步:用fpga芯片中的高频调制与信道分配模块中的高频载波clk_10khz对编码后的基带数据帧进行调制获得高频调制信号,使基带数据帧中的高电平被搬移到高频载波信号频率上,以此去除掉基带数据帧中的直流成分,便于在外部线路中传输;

[0062]

第二步:利用信道分配时钟clk_100hz设计一个k计数器,再对k计数器进行译码,使其输出轮流为高电平的k根信号线,用这k根信号线作为k个二输入与门电路的其中一个输入端口,k个二输入与门电路的另一个输入端口与高频调制信号相接,使高频调制信号按时隙轮流从k个二输入与门电路输出,获得k路高频调制信号laser8[7:0];

[0063]

第三步:将经过k个传输信道输出的信号laser8[7:0]调制到无线、fso或光纤载波频率的传输信道上进行远程传输。

[0064]

图5为本发明实施例中根据一种基于时间同步的跟踪发信控制方法所设计的一种基于时间同步的跟踪发信控制装置的示意图。该发信控制装置包括时钟驱动模块、时间获取模块、载频产生模块、载频控制模块、基带数据编码模块、高频调制与信道分割模块、显示控制模块、bd/gps授时接收模块、线路信号发送模块。

[0065]

图5中的时钟驱动模块将输入的外部晶振时钟通过分频获得高频调制载波信号、k

个线路信道时隙分割控制信号、显示驱动时钟信号;

[0066]

图5中的时间获取模块将来自bd/gps授时接收模块接收的当前时间提取出来作为授时时间,同时由外部晶振时钟产生本地时间信号,然后不断用授时时间对本地时间刷新,使本地时间与授时时间一致,获得基带数据帧速率维持的标准控制时间;

[0067]

图5中的bd/gps授时接收模块接收卫星下传的当前标准北京时间,并将该时间输出给fpga芯片;

[0068]

图5中的载频产生模块产生进行基带数据帧编码时所需各种载波信号;

[0069]

图5中的载频控制模块在当前标准时间控制下,从n个载波组的j个数字载波频率中,按载波编号轮流选取一个作为基带数据帧编码在不同时段的载波;

[0070]

图5中的基带数据编码模块将待传输的数据按空闲位、起始位、数据位、奇偶校验位、停止位的帧格式进行编码,产生以h位数据为一帧的基带数据传输信号;

[0071]

图5中的高频调制与信道分割模块将基带数据帧调制到高频载波频率上,并将调制后的数据流按时隙轮流分配到k个无线、fso或光纤载波频段上;

[0072]

图5中的线路信号发送模块将高频载波调制后的k路信号转换成无线、fso或光纤信号进行远程数据传输;

[0073]

图5中的显示控制模块用于显示系统工作过程中的关键信号,方便随时掌握系统的工作状况,显示内容包括:时间同步控制信号的当前时间、当前时间选取的基带载波频率编号、当前正发送的数据。

[0074]

图6为本发明实施例中一种基于时间同步的跟踪发信控制装置集成在fpga芯片中设计的相关功能模块的一种电路连接关系的示意图。

[0075]

图6中bd/gps授时接收模块输出的标准时间dtimrx串行输入到u2时间获取模块,与该模块中由clk产生的本地时间进行同步后,并行输出时间同步控制信号timctr[3:0];rst为系统复位信号;

[0076]

图6中u1载频产生模块对输入的clk时钟进行分频,获得10个载频信号fn[9:0];

[0077]

图6中u3载波控制模块在时钟clk、复位信号rst激励下,依据外部输入的频率组选取信号chsel[3:0]从n组载波中选取一个载波组,按照时间同步控制信号timctr[3:0]的时间变化速度,从输入的10个载频fn[9:0]中,选取1个载波轮流输出,作为对基带数据的载波调制信号clksp;同时还将当前载波调制信号clksp实际的频率编号输出到显示电路进行显示。

[0078]

图6中u4基带数据编码模块将外部输入的8位待发送数据datain[7:0],在基带数据的载波调制信号clksp、复位信号rst、外部发送使能信号txen激励下,将待发送数据datain[7:0]组成基带数据帧从tx输出。

[0079]

图6中u0时钟驱动模块产生显示模块所需要的时钟clk_1khz、高频调制所需要的高频载波信号clk_10khz、信道分割所需要的时隙控制信号clk_100hz。

[0080]

图6中u5高频调制与信道分割模块用信道分割控制信号clk_100hz产生8个轮流导通的外部线路传输信道,并用高频载波信号clk_10khz将基带数据帧调制到高频载波频段上,最后按时隙轮流从8个输出信道上输出信号laser8[7:0]。

[0081]

图6中u6四位七段显示模块将输入的当前时段基带编码载波频率编号sfn[3:0]、当前时间tim[3:0]、当前传输数据datain[3:0]编制成驱动4位数码管的七段进行显示的驱

动信号tub4[3:0]、sec7[6:0]。

[0082]

图7为本发明实施例中一种基于时间同步的跟踪发信控制装置位于fpga芯片输出端的8个fso线路信号发送电路连接关系的示意图。fpga输出的8个线路信号laser8[7:0],分别输入到激光调制电路的输入端laser0~laser7,经驱动管q0~q7驱动后,从led0~led7激光发射管输出承载高频调制信号的调制激光。图7中r为基极和集电极限流电阻,d为保护二极管。

[0083]

以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。