一种基于fpga的高效pcie dma数据传输方法

技术领域

1.本发明涉及数据传输技术领域,特别是一种基于fpga的高效pcie dma数据传输方法。

背景技术:

2.fpga普遍应用于通信、电力、导航、航空航天、交通等领域,随着科技地不断进步与发展,人们对高速信号传输的要求也越来越高。pcie是一种高速串行总线标准,采用高速串行点对点双通道高带宽传输,具有系统总线吞吐量高、i/o数量少和物理尺寸小等优势,因此广泛应用于高速信号传输。

3.pcie通常用于板卡间的高速、大带宽数据传输,涉及硬件、逻辑(fpga)、软件等方面。主机软件主要完成系统驱动file的操作(主要是open、read、write),这个依赖于驱动的开发。对于逻辑开发,fpga芯片提供方有支持pcie的物理层ip,一般提供两类ip:一类只有纯物理层、链路层和事务层,把复杂的pcie协议转换为各类传输包,工程师可以完全自主定义dma的设计,比如在dma上传时,可以定义dma读的源地址和物理地址以及传输长度等常规dma设计;另一类ip提供方直接把dma都定义好,主机驱动和软件也提供了参考设计,用户只需参考设计例程来完成自己的设计。pcie的常用高速传输的控制传输流程如图1所示,主要涉及dma传输的几个环节:1)用户数据为需要传输的数据;2)dma控制:控制dma,把用户数据上传到内核;3)pcie为pcie总线;4)内核:配置dma,并且能接收dma的数据;5)主机:即主控获取有效数据。通常一次dma操作流程为:主机对内核发起一次dma取数据;内核配置dma,并启动一次搬数据;fpga逻辑dma控制器收到配置且启动命令后,开始搬运数据,把用户数据搬运到主机的目的地址。这类dma操作是比较成熟的dma传输方法,对于逻辑设计来说,只需等待dma控制器的配置命令后,启动命令并开始搬运数据即可,相对来说比较简单。但这类传输方法的pcie传输链路比较长,传输控制环节过于冗余,相互制约,传输效率低。

技术实现要素:

4.鉴于此,本发明提供一种基于fpga的高效pcie dma数据传输方法,可大大提高传输带宽,实现高效率数据传输。

5.本发明公开了一种基于fpga的高效pcie dma数据传输方法,其包括创建dma阶段和主机读取数据阶段;

6.所述创建dma阶段包括以下步骤:

7.步骤1:主机向内核发出申请创建dma读文件句柄的指令,主机通过dma读文件句柄访问fpga相对应的内核;

8.步骤2:内核接收指令并创建dma读文件句柄,同时申请创建环形缓存空间以及dma描述符链表;

9.步骤3:fpga dma读链表控制器接收并处理内核创建的环形缓存对应的描述符链表信息,完成fpga dma读数据控制器初始化;

10.步骤4:fpga dma读数据控制器启动,根据描述符链表信息读取用户数据并将其上传到环形缓存空间;

11.所述主机读取数据阶段包括以下步骤:

12.步骤5:主机软件根据创建的读文件句柄,向内核发起一次读数据操作;

13.步骤6:内核收到主机软件读命令,获取主机软件的读取长度信息,然后判断环形缓存状态;若环形缓存数据满足主机读需求,则主机复制数据,完成用户数据到主机的数据传输。

14.进一步地,所述步骤2包括:

15.步骤21:内核创建dma描述符链表,底层fpga dma控制器主要根据dma描述符信息工作;

16.步骤22:内核配置dma描述符链表的基本参数并在内核中创建环形缓存;其中,所述基本参数包括dma传输完成状态、dma传输源地址、dma传输目的地址、dma传输长度;

17.步骤23:内核返回主机程序已创建的读文件句柄。

18.进一步地,所述步骤3包括:

19.步骤31:内核启动fpga dma读程序;

20.步骤32:fpga dma读链表控制器获取主机发起的读命令以及dma描述符链表参数;

21.步骤33:fpga dma读数据控制器接收并处理环形缓存对应的链表信息;

22.步骤34:待整个数据传输链路配置完成后,fpga dma控制器则一直根据dma链表信息将用户数据搬运到环形缓存空间。

23.进一步地,所述步骤4包括:

24.步骤41:fpga dma用户控制逻辑判断环形缓存是否已经存满,如果存满则停止读取用户数据;否则,重复执行步骤41;

25.步骤42:fpga dma读数据控制器根据当前dma链表信息,把用户数据搬运到内核目的地址,该目的地址为内核申请的环形缓存空间地址;

26.步骤43:fpga dma读数据控制器在搬运完一帧数据后,设置该dma描述符的dma传输完成状态,并提取下一包的dma描述符链表信息;其中,一帧数据对应一个dma描述符;

27.步骤44:若主机不发起停止读数据工作命令,则整个fpga逻辑程序重复执行步骤41至步骤43。

28.进一步地,在所述步骤5中,读取数据长度需要满足以下参数关系:

29.dma描述符链表的dma长度是内存页大小的整数倍时,传输效率最高;主机发起读操作长度必须是dma链表长度的整数倍。

30.进一步地,所述步骤6还包括:

31.若环形缓存数据不满足主机读需求,则主机软件开始等待。

32.进一步地,在所述步骤6之后,还包括:

33.内核每复制完一帧dma数据到主机目的地址时,需要把复制数据的长度信息传递至fpga dma用户控制逻辑,以便于fpga dma用户逻辑控制器获取环形缓存剩余空间大小。

34.进一步地,若主机需要再次读取数据,仅需重复步骤5至步骤6。

35.由于采用了上述技术方案,本发明具有如下的优点:本发明能够大大提高传输带宽,实现高效率数据传输。

附图说明

36.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明实施例中记载的一些实施例,对于本领域普通技术人员来讲,还可以根据这些附图获得其他的附图。

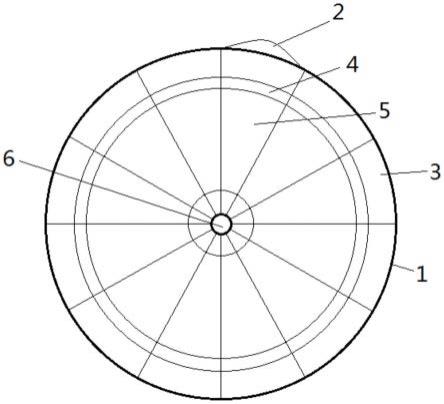

37.图1为现有技术的dma传输链路示意图;

38.图2为现有技术的dma传输时间示意图;

39.图3为本发明实施例的pcie传输结构图;

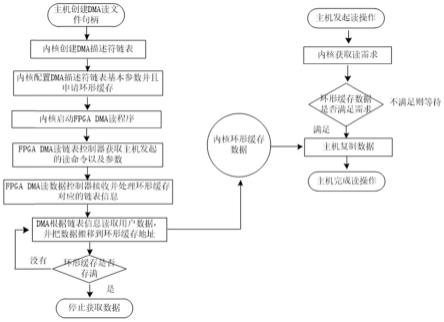

40.图4为现有技术的dma常规读流程示意图;

41.图5为本发明实施例的各环节完全前后承接独立传输流程示意图。

具体实施方式

42.结合附图和实施例对本发明作进一步说明,显然,所描述的实施例仅是本发明实施例一部分实施例,而不是全部的实施例。本领域普通技术人员所获得的所有其他实施例,都应当属于本发明实施例保护的范围。

43.现有技术中主机对内核发起一次dma取数据;内核收到读操作后配置dma,然后启动一次搬数据;fpga逻辑dma控制器收到配置且启动命令后,开始搬运数据,把用户数据搬运到主机的目的地址。设主机输出读操作到内核的时间为t1,内核完成dma配置的时间为t2,设fpga收到dma控制器搬运操作并访问用户数据的时间为t3,从内核搬移数据到主机目的地址的时间为t4。则要完成一次完整的用户数据搬移,所需时间t=t1 t2 t3 t4。如图2所示。

44.本发明所要解决的技术问题就是从传输链路上和控制流程上提高传输速率,即一种各环节完全前后承接独立的传输方案,让前一个环节完全只受后一个环节的影响。也就是在传数时,只要dma控制不处于忙状态,用户数据就一直上传;只要内核能收数据,dma控制环节就一直搬移数据;内核就等着主机来复制数据。整个流程所需时间受实际环境影响,假设搬移内核里的数据到主机目的地址的时间设置为ts1,用户数据到内核的时间为ts2,则搬移数据所需时间取决于这两个时间中最大的那个。很明显该解决办法大大减少了传输消耗的时间。

45.现有技术中dma长队读流程图如图3所示,dma描述符链表包含有dma传输的一些基本信息:

46.1)dma传输数据流结束符;

47.2)dma传输完成状态;

48.3)停止dma传输;

49.4)dma传输源地址;

50.5)dma传输目的地址;

51.6)dma传输长度。

52.根据上面的dma读流程和dma描述符基本说明信息,为了让传输时间最小,就必须让整个dma读控制不需要每次都受主机配置的dma描述符控制,独立自主往上搬移数据。

53.本发明针对数据传输路径的等待时间较长,传输效率受限问题提出了各环节完全前后承接独立的方案,采用环形缓存进行中转,前一个环节一直往环形缓存中传数据,主机

端直接复制数据,该方案无等待时间,各环节相互独立,主机读取用户数据所需时间只取决于用户数据到环形缓存传输时间与环形缓存到主机端传输时间中最大的那个时间。

54.本方案是基于fpga pc主机模式设计的,其中fpga可以是搭载在各类采集卡或者传输设备上的,fpga端用作pcie的ep端,主机作为rc,其结构图如图4所示。

55.参见图5,本发明提供了一种基于fpga的高效pcie dma数据传输方法的实施例,其包括创建dma阶段和主机读取数据阶段;

56.创建dma阶段包括以下步骤:

57.步骤1:主机向内核发出申请创建dma读文件句柄的指令,主机通过dma读文件句柄访问fpga相对应的内核;

58.步骤2:内核接收指令并创建dma读文件句柄,同时申请创建环形缓存空间以及dma描述符链表;

59.步骤3:fpga dma读链表控制器接收并处理内核创建的环形缓存对应的描述符链表信息,完成fpga dma读数据控制器初始化;

60.步骤4:fpga dma读数据控制器启动,根据描述符链表信息读取用户数据并将其上传到环形缓存空间;

61.主机读取数据阶段包括以下步骤:

62.步骤5:主机软件根据创建的读文件句柄,向内核发起一次读数据操作;

63.步骤6:内核收到主机软件读命令,获取主机软件的读取长度信息,然后判断环形缓存状态;若环形缓存数据满足主机读需求,则主机复制数据,完成用户数据到主机的数据传输。

64.本实施例中,步骤2包括:

65.步骤21:内核创建dma描述符链表,底层fpga dma控制器主要根据dma描述符信息工作;

66.步骤22:内核配置dma描述符链表的基本参数并在内核中创建环形缓存;其中,基本参数包括dma传输完成状态、dma传输源地址、dma传输目的地址、dma传输长度;

67.步骤23:内核返回主机程序已创建的读文件句柄。

68.本实施例中,步骤3包括:

69.步骤31:内核启动fpga dma读程序;

70.步骤32:fpga dma读链表控制器获取主机发起的读命令以及dma描述符链表参数;

71.步骤33:fpga dma读数据控制器接收并处理环形缓存对应的链表信息;

72.步骤34:待整个数据传输链路配置完成后,fpga dma控制器则一直根据dma链表信息将用户数据搬运到环形缓存空间。

73.本实施例中,步骤4包括:

74.步骤41:fpga dma用户控制逻辑判断环形缓存是否已经存满,如果存满则停止读取用户数据;否则,重复执行步骤41;

75.步骤42:fpga dma读数据控制器根据当前dma链表信息,把用户数据搬运到内核目的地址,该目的地址为内核申请的环形缓存空间地址;

76.步骤43:fpga dma读数据控制器在搬运完一帧数据后,设置该dma描述符的dma传输完成状态,并提取下一包的dma描述符链表信息;其中,一帧数据对应一个dma描述符;

77.步骤44:若主机不发起停止读数据工作命令,则整个fpga逻辑程序重复执行步骤41至步骤43。

78.本实施例中,在步骤5中,读取数据长度需要满足以下参数关系:

79.dma描述符链表的dma长度是内存页大小的整数倍时,传输效率最高;主机发起读操作长度必须是dma链表长度的整数倍。

80.本实施例中,步骤6还包括:

81.若环形缓存数据不满足主机读需求,则主机软件开始等待。

82.本实施例中,在步骤6之后,还包括:

83.内核每复制完一帧dma数据到主机目的地址时,需要把复制数据的长度信息传递至fpga dma用户控制逻辑,以便于fpga dma用户逻辑控制器获取环形缓存剩余空间大小。

84.本实施例中,若主机需要再次读取数据,仅需重复步骤5至步骤6。

85.本实施例中,主机发起一次读操作和每个环形缓存的大小,应该是整数倍关系。为使传输效率达到最高,在实际测试当中,一般在主机一次读数据大小是环形缓存大小的32倍左右,并且每个环形缓存大小在8kb时,带宽利用率基本达到最高。当然实际的传输带宽受主机性能和pcie的lane数以及gen协议的影响。

86.最后应当说明的是:以上实施例仅用以说明本发明的技术方案而非对其限制,尽管参照上述实施例对本发明进行了详细的说明,所属领域的普通技术人员应当理解:依然可以对本发明的具体实施方式进行修改或者等同替换,而未脱离本发明精神和范围的任何修改或者等同替换,其均应涵盖在本发明的权利要求保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。