1.本发明涉及半导体装置。

背景技术:

2.在专利文献1中公开了具有半导体衬底的半导体装置,该半导体衬底规定了相邻的igbt区域及二极管区域。在igbt表面配置有沟槽,半导体衬底的表面中的二极管表面相对于半导体衬底的表面中的igbt表面而凹陷。半导体衬底的表面的相反侧的背面与沟槽的下端之间的距离对应于半导体衬底的背面与二极管表面之间的距离。

3.专利文献1:日本特开2021-28922号公报

4.就专利文献1的半导体装置而言,衬底在整个二极管区域形成得薄。因此,特性调整有可能变得困难。

技术实现要素:

5.本发明就是为了解决上述课题而提出的,其目的在于得到容易进行特性调整的半导体装置。

6.本发明涉及的半导体装置具有:衬底,其具有igbt区域和二极管区域;表面电极,其设置于所述衬底的上表面;以及背面电极,其设置于所述衬底的与上表面相反侧的背面,所述二极管区域具有通过所述衬底的上表面凹陷而形成得比所述igbt区域薄的第1部分和设置于所述第1部分的一侧且比所述第1部分厚的第2部分。

7.发明的效果

8.就本发明涉及的半导体装置而言,二极管区域具有形成得比igbt区域薄的第1部分和比第1部分厚的第2部分。因此,容易进行特性调整。

附图说明

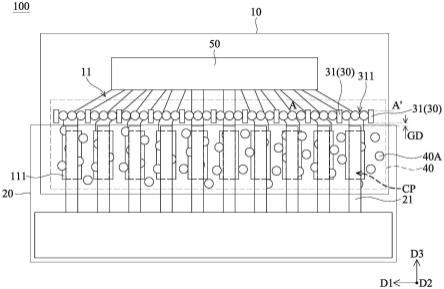

9.图1是实施方式1涉及的半导体装置的剖视图。

10.图2是实施方式1的变形例涉及的半导体装置的剖视图。

11.图3是实施方式2涉及的半导体装置的剖视图。

12.图4是实施方式3涉及的半导体装置的剖视图。

13.图5是实施方式4涉及的半导体装置的剖视图。

14.图6是实施方式5涉及的半导体装置的剖视图。

15.图7是实施方式6涉及的半导体装置的剖视图。

16.图8是实施方式7涉及的半导体装置的剖视图。

具体实施方式

17.参照附图,对各实施方式涉及的半导体装置进行说明。对相同或相应的结构要素标注相同的标号,有时省略重复说明。在以下的说明中,n及p表示半导体的导电型。在各实

施方式中说明的导电型也可以是相反的。另外,n-表示杂质浓度比n低,n 表示杂质浓度比n高。同样地,p-表示杂质浓度比p低,p 表示杂质浓度比p高。

18.实施方式1

19.图1是实施方式1涉及的半导体装置100的剖视图。半导体装置100具有衬底,该衬底具有igbt区域10和二极管区域20。半导体装置100是rc-igbt(reverse conducting igbt)。将igbt区域10及二极管区域20合称为单元区域。在单元区域的周围,为了半导体装置100的耐压保持而设置有未图示的末端区域。

20.在igbt区域10设置有源沟槽栅极11和哑沟槽栅极12。有源沟槽栅极11在形成于衬底的沟槽内隔着栅极沟槽绝缘膜11b而具有栅极沟槽电极11a。哑沟槽栅极12在形成于衬底的沟槽内隔着哑沟槽绝缘膜12b而具有哑沟槽电极12a。栅极沟槽电极11a与未图示的栅极焊盘电连接。哑沟槽电极12a与在衬底的上表面设置的表面电极6电连接。

21.表面电极6是发射极电极。

22.衬底具有n-型漂移层1。在igbt区域10,衬底为从n 型源极层13及p 型接触层14至p型集电极层16为止的范围。在igbt区域10,在n-型漂移层1的上表面侧设置有n型载流子积蓄层2。此外,也可以不设置n型载流子积蓄层2。也可以将n型载流子积蓄层2与n-型漂移层1合称为漂移层。

23.在n型载流子积蓄层2的上表面侧设置有p型基极层15。n 型源极层13及p 型接触层14构成衬底的上表面。n 型源极层13与栅极沟槽绝缘膜11b接触地设置。在相邻的2个哑沟槽栅极12之间设置p 型接触层14。此外,也可以将p 型接触层14与p型基极层15合称为p型基极层。

24.在n-型漂移层1的背面侧设置有n型缓冲层3。也可以不设置n型缓冲层3。也可以将n型缓冲层3与n-型漂移层1合称为漂移层。在n型缓冲层3的背面侧设置有p型集电极层16。p型集电极层16构成衬底的背面。p型集电极层16不仅设置于igbt区域10,也设置于末端区域。

25.在有源沟槽栅极11之上设置有层间绝缘膜4。在igbt区域10的上表面中的未设置层间绝缘膜4的区域之上及层间绝缘膜4之上形成有阻挡金属5。阻挡金属5与n 型源极层13、p 型接触层14及哑沟槽电极12a欧姆接触。在阻挡金属5之上设置表面电极6。在衬底的与上表面相反侧的背面设置背面电极7。背面电极7是集电极(collector)电极(electrode)。背面电极7与p型集电极层16欧姆接触。

26.半导体装置100在二极管区域20也具有n-型漂移层1。二极管区域20的n-型漂移层1与igbt区域10的n-型漂移层1是连续一体地构成的。在二极管区域20,衬底为从p 型接触层24至n 型阴极层26为止的范围。在n-型漂移层1的上表面侧设置有p型阳极层25及p 型接触层24。也可以将p 型接触层24与p型阳极层25合称为p型阳极层。

27.在二极管区域20,在n型缓冲层3的背面侧设置有n 型阴极层26。n 型阴极层26构成衬底的背面。在二极管区域20,表面电极6成为阳极电极,背面电极7成为阴极电极。

28.二极管区域20具有通过衬底的上表面凹陷而形成得比igbt区域10薄的第1部分20a。并且,二极管区域20具有设置于第1部分20a的一侧且比第1部分20a厚的第2部分20b和设置于第1部分20a的另一侧且比第1部分20a厚的第3部分20c。第2部分20b与igbt区域10相邻。

29.p型阳极层25具有沿第1部分20a的上表面而设置的部分25a。另外,p型阳极层25具有沿将第1部分20a与第2部分20b、第3部分20c连接起来的衬底的侧面而设置的部分25b、25c。

30.在本实施方式中,在二极管区域20,表面电极6与p型阳极层25接触的平面存在多个。第1部分20a的深度是任意的,能够进行选择。第1部分20a的深度能够通过掩模处理时的掩模图案和蚀刻处理条件进行变更。另外,也能够通过使掩模图案的宽度发生变化而对第1部分20a的深度进行调整。

31.在本实施方式中,二极管区域20具有薄的部分和厚的部分。此时,能够使p型阳极层25在深度方向上广阔地分布。由此,能够容易地对p型阳极层25的各部分的浓度进行调整。能够通过对p型阳极层25的深度及浓度进行调整而对来自p型阳极层25的空穴的注入量进行调整。由此,能够对正向动作时的接通电压和恢复特性进行调整。因此,在本实施方式中,能够容易地进行特性调整。

32.另外,当在二极管区域整面,硅厚度薄的情况下,有可能在igbt区域与二极管区域之间的边界区域或电流集中的区域容易产生破坏。电流集中的区域例如是二极管区域的中心或导线的正下方。另外,有可能产生芯片破裂。另外,有可能在igbt区域与二极管区域之间大范围地产生台阶,制造变得困难。

33.与此相对,在本实施方式中,能够对衬底薄的区域进行限定。由此,能够抑制晶片翘曲量。另外,能够抑制由电流的集中导致的破坏或芯片破裂,能够改善成品率。并且,通过对台阶部进行限定,从而能够避免照相制版掩模处理时的散焦,能够减少蚀刻后的残渣。因此,能够使半导体装置100的制造变得容易。综上所述,在本实施方式中,能够实现特性调整的容易化、破坏耐量的提高及制造工序的容易化。

34.另外,如图1所示,第2部分20b的上表面与igbt区域10的上表面也可以形成同一平面。如果在igbt区域10与二极管区域20之间的边界区域存在台阶,则有可能在台阶部电场局部地变高。此时,耐压下降,有可能在通断动作、恢复动作时容易产生破坏。由于在igbt区域10与二极管区域20之间的边界处没有台阶,因此能够抑制电场集中,提高反向偏置时的耐量。

35.在图1的例子中,在第2部分20b的上表面形成层间绝缘膜4。不限于此,第2部分20b也可以与表面电极6接触。另外,也可以形成有p型阳极层25而取代p 型接触层24。此时,也可以在与igbt区域10相邻的p型阳极层25设置有浓度梯度。优选p型阳极层25的浓度朝向igbt区域而下降。另外,也可以没有igbt区域10与二极管区域20之间的边界处的沟槽。

36.另外,在igbt区域10处在衬底的背面侧设置的p型集电极层16也可以伸出至二极管区域20。即,在二极管区域20,与igbt区域相邻的部分的背面侧也可以是p型集电极层16。

37.在与igbt区域10相邻的边界区域的背面构造是n 型阴极层26的情况下,有时在二极管的正向动作时载流子容易在边界区域滞留。因此,有可能在恢复动作时容易产生破坏。另外,有可能发生骤回现象,即,在igbt的接通时在n 型阴极层26流过电子,难以从p型集电极层16注入空穴,igbt不接通。通过使p型集电极层16向二极管区域扩展,从而能够抑制上述这样的igbt与二极管的载流子的干涉。

38.p型集电极层16的向二极管区域20的伸出量u1例如与晶片厚度相同。通常,电流在45

°

的角度范围内流动。因此,作为伸出量u1,只要确保与晶片厚度相同的距离,就能够抑制

电流的干涉。不限于此,伸出量u1能够任意地设定。p型集电极层16与p型阳极层25在俯视观察时可以重叠,也可以不重叠。

39.p型阳极层25的各部分25a、25b、25c也可以彼此浓度不同。p型阳极层25也可以与深度相应地具有浓度梯度。

40.图2是实施方式1的变形例涉及的半导体装置200的剖视图。p型阳极层25中的部分25a、25b、25c也可以是分离的。即,也可以在表面电极6与p型阳极层25接触的多个平面的每一者形成阳极。通过掩模处理时的掩模图案的设定或在蚀刻处理后进行注入,从而能够在每个平面形成阳极。

41.另外,在本实施方式中,二极管区域20的高度成为2个阶梯。不限于此,二极管区域20的高度也可以大于或等于3个阶梯。

42.在二极管区域20,第1部分20a可以仅设置于1个部位,也可以设置于多个部位。作为第1部分20a的俯视观察时的图案能够采用任意的形状。第1部分20a的俯视观察时的图案可以是条带型、岛型或圆形。第1部分20a的形状能够通过掩模处理时的掩模图案而适当变更。另外,二极管区域20只要具有第1部分20a和在第1部分20a的一侧设置的第2部分或第3部分即可。即,二极管区域20中的比第1部分20a厚的部分只要至少设置于第1部分20a的单侧即可。

43.另外,在图1的例子中,第1部分20a被挖至与有源沟槽栅极11相同的深度。第1部分20a的深度不限定于此。通过使第1部分20a被挖至比有源沟槽栅极11更靠下方处,从而能够进一步抑制损耗。另外,通过将第1部分20a的上表面设为与有源沟槽栅极11的底部相同,从而衬底变薄,能够抑制制造成本上升这一情况。

44.就半导体装置100而言,衬底也可以由宽带隙半导体形成。宽带隙半导体是碳化硅、氮化镓类材料或金刚石。根据本实施方式,通过适当的特性调整,从而能够在由宽带隙半导体形成的衬底稳定地流过高电流。

45.这些变形能够适当应用于以下的实施方式涉及的半导体装置。此外,关于以下的实施方式涉及的半导体装置,由于与实施方式1之间的共通点多,因而以与实施方式1之间的不同点为中心进行说明。

46.实施方式2

47.图3是实施方式2涉及的半导体装置300的剖视图。半导体装置300的第1部分20a的构造与半导体装置100不同。其它结构与半导体装置100的结构相同。半导体装置300的第1部分20a在最上层具有p型阳极层25和肖特基接触层40。也可以在肖特基接触层40注入有n型的p(磷)。

48.在第1部分20a处n-型漂移层1薄,因此电流容易集中。在第1部分20a,通过将p型阳极层25的一部分设为肖特基接触层40,从而能够抑制正向动作时的空穴的注入量。由此,能够降低恢复时的损耗。另外,通过改变p型阳极层25和肖特基接触层40的图案,从而能够对正向接通电压和恢复损耗的折衷关系(trade-off)进行调整。另外,也可以以反向偏置时的耗尽层从p型阳极层25延伸而将肖特基接触层40覆盖的方式对p型阳极层25的宽度、浓度或深度进行调整。由此,能够抑制泄漏电流。

49.p型阳极层25与肖特基接触层40的面积比率是任意的。俯视观察时的p型阳极层25及肖特基接触层40的图案可以是条带型、岛型、蜂窝构造或圆形。

50.实施方式3

51.图4是实施方式3涉及的半导体装置400的剖视图。半导体装置400的二极管区域20的构造与半导体装置100不同。其它结构与半导体装置100的结构相同。就半导体装置400而言,第1部分20a在最上层具有p型阳极层25,第3部分20c在最上层具有肖特基接触层40。

52.通常,肖特基接触层40的反向偏置时的泄漏电流大。因此,如实施方式2所示,为了通过从p型阳极层25延伸的耗尽层对泄漏电流进行阻挡,有可能会限制图案形状。在本实施方式中,通过将第1部分20a的上表面设为p型阳极层25,将第2部分20b或第3部分20c的上表面设为肖特基接触层40,从而在反向偏置时耗尽层容易将肖特基接触层40覆盖。因此,能够减少泄漏电流。

53.p型阳极层25与肖特基接触层40的面积比率是任意的。俯视观察时的p型阳极层25及肖特基接触层40的图案可以是条带型、岛型、蜂窝构造或圆形。另外,将第1部分20a与第2部分20b或第3部分20c连接起来的衬底的侧面可以是p型阳极层25,也可以是肖特基接触层40。

54.实施方式4

55.图5是实施方式4涉及的半导体装置500的剖视图。就半导体装置500而言,将第1部分20a与第2部分20b、第3部分20c连接起来的衬底的侧面被氧化膜42覆盖。其它构造与半导体装置400的构造相同。

56.氧化膜42的厚度是任意的。氧化膜42例如是通过热氧化或cvd(chemical vapor deposition)而形成的。另外,能够在cvd处理之后进行各向异性蚀刻,仅在衬底的侧面使氧化膜42残留。另外,氧化膜42也可以具有复合膜构造。在复合膜构造中,例如氧化膜、多晶硅、氧化膜进行层叠。

57.在本实施方式中,衬底的台阶部被氧化膜42覆盖。因此,在台阶部不流过电流。因此,能够提高恢复时的破坏耐量。

58.在图5所示的例子中,台阶部整体被氧化膜42覆盖。不限于此,只要将第1部分20a与第2部分20b、第3部分20c连接起来的衬底的侧面中的至少一部分被氧化膜42覆盖即可。例如,也可以仅衬底的侧面的上侧的角部或下侧的角部被氧化膜42覆盖。在这种情况下,也能够抑制电流在角部集中,能够提高恢复时的破坏耐量。

59.实施方式5

60.图6是实施方式5涉及的半导体装置600的剖视图。就半导体装置600而言,将第1部分20a与第2部分20b连接起来的衬底的侧面由向外侧凸出的曲面形成。其它结构与半导体装置100的结构相同。这样的台阶部的形状例如能够通过各向同性蚀刻形成。另外,能够使掩模图案的粗细根据位置进行变更,对蚀刻的深度进行调整。

61.在本实施方式中,与实施方式1相比,能够使p型阳极层25的厚度接近于均匀。特别地,能够在第1部分20a与第2部分20b、第3部分20c之间的台阶的下侧的角部处抑制p型阳极层25变薄。因此,能够抑制由于穿通而耐压下降的情况。另外,能够抑制在恢复时电流在角部集中,能够提高rrsoa(reverse recovery safe operation area)。

62.衬底的侧面的曲率是任意的。将衬底的侧面的曲率设定得越大,越能够在角部处抑制p型阳极层25变薄。只要衬底的侧面的曲率大于或等于p型阳极层25的曲率,就会得到足够的效果。

63.实施方式6

64.图7是实施方式6涉及的半导体装置700的剖视图。二极管区域20在衬底的背面侧具有n 型阴极层26。就半导体装置700而言,n 型阴极层26被间隔剔除。此外,在图7中采用了实施方式2的构造作为衬底的上表面侧的构造,但也可以采用其它实施方式的构造。

65.接下来,对这样的n 型阴极层26的形成方法进行说明。首先,对衬底的背面整体进行注入,形成p型集电极层16。接下来,通过使用掩模图案选择性地进行注入,从而形成n 型阴极层26。n 型阴极层26的注入量被设定得大于p型集电极层16的注入量。然后,通过激光退火进行再结晶化。由于浓度之差,在作为n 型阴极层26而进行了注入的区域,p型集电极层16被抵消。由此,能够形成p型集电极层16和n 型阴极层26的图案。俯视观察时的图案可以是条带型,可以是岛型,也可以是圆形。

66.通过对n 型阴极层26进行间隔剔除,从而抑制来自n 型阴极层26的电子的注入。因此,能够减小恢复时的尾电流。另外,通过改变p型集电极层16与n 型阴极层26的图案的比率,从而能够对正向接通电压和恢复损耗的折衷关系进行调整。

67.另外,也可以是越靠近igbt区域10侧,n 型阴极层26被越多地间隔剔除。此时,也可以朝向igbt区域10而使间隔剔除率倾斜。另外,也可以仅在与igbt区域10之间的边界区域处将n 型阴极层26大幅度地间隔剔除。由此,能够在igbt区域10侧使衬底背面的载流子浓度下降。因此,能够抑制恢复电流在二极管区域20的台阶的角部处集中。由此,能够提高rrsoa。

68.实施方式7

69.图8是实施方式7涉及的半导体装置800的剖视图。在本实施方式中,n 型阴极层26的构造与实施方式6不同。就半导体装置800而言,n 型阴极层26避开第1部分20a的p型阳极层25的正下方而设置。此外,在图8中采用了实施方式3的构造作为衬底的上表面侧的构造,但也可以采用其它实施方式的构造。

70.如果在靠近衬底背面的第1部分20a的p型阳极层25之下存在n 型阴极层26,则由从p型阳极层25注入的空穴和从n 型阴极层26注入的电子引起的电导率调制效应变大。因此,有可能恢复损耗变大。在本实施方式中,在p型阳极层25中的最背面侧的部分的正下方不形成n 型阴极层26。由此,能够减小恢复损耗。

71.另外,在本实施方式中,p型阳极层25中的最背面侧的部分、n-型漂移层1和p型集电极层16形成pnp构造。如果在恢复动作时电压上升,则该pnp晶体管进行动作,能够抑制浪涌电压。

72.此外,在各实施方式中说明过的技术特征也可以适当地组合使用。

73.标号的说明

74.1n-型漂移层,2n型载流子积蓄层,3n型缓冲层,4层间绝缘膜,5阻挡金属,6表面电极,7背面电极,10igbt区域,11有源沟槽栅极,11a栅极沟槽电极,11b栅极沟槽绝缘膜,12哑沟槽栅极,12a哑沟槽电极,12b哑沟槽绝缘膜,13n 型源极层,14p 型接触层,15p型基极层,16p型集电极层,20二极管区域,20a第1部分,20b第2部分,20c第3部分,24p 型接触层,25p型阳极层,25a部分,25b部分,26n 型阴极层,40肖特基接触层,42氧化膜,100、200、300、400、500、600、700、800半导体装置。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。