数据传输的方法、装置、设备、系统及可读存储介质

1.本技术要求于2021年8月11日提交的申请号为202110920833.x、发明名称为“级联结构、级联编码方法及设备”的中国专利申请的优先权,其全部内容通过引用结合在本技术中。

技术领域

2.本技术实施例涉及通信技术领域,尤其涉及一种数据传输的方法、装置、设备、系统及可读存储介质。

背景技术:

3.随着数据传输速率的提高,信道的损耗和噪声限制了数据传输的速率和距离。前向纠错码(forward error correction,fec)作为能够为被传递的数据提供校验位,提高信道中的数据传输速率以及传输距离的数据编码方法,得到了越来越广泛的应用。在数据传输过程中,发送端通过特定的fec码型将原始数据进行编码,将编码后的数据发送至接收端,接收端通过相同的fec码型将接收的数据进行解码,得到原始数据。

技术实现要素:

4.本技术提出一种数据传输的方法、装置、设备、系统及可读存储介质,用于提高数据传输的质量。

5.第一方面,提供了一种数据传输的方法,该方法包括:第一模块获取第一数据,第一数据为采用第一前向纠错码fec码型编码且经过第一处理的数据,第一处理包括交织处理;第一模块按照第二fec码型对第一数据进行编码,得到多个第二码字;第一模块对多个第二码字进行第二处理,得到第二数据;第一模块传输第二数据。

6.该方法通过级联编码能够使传输的数据具有更高的编码增益,在容易出现误码的通道中传输时,能够对出现误码的数据进行有效的纠错,且由于第一数据是经过交织处理得到的数据,能够将第二fec码纠后的码字内错误比特相关性消除,提高纠错性能,进一步提高数据传输的质量。

7.在一种可能的实施方式中,第二处理包括插入相干链路所需要的训练序列与导频符号中的至少一种。通过插入相干链路所需要的训练序列与导频符号中的至少一种,可使得该方法应用于相干链路。

8.在一种可能的实施方式中,所述第一处理和第二处理中的至少一个还包括插入用于调整频点的数据。通过插入用于调整频点的数据,使得处理后的数据的频点能够满足要求。

9.在一种可能的实施方式中,所述第一模块获取第一数据,包括:所述第一模块接收第二模块发送的多个第一子数据,所述多个第一子数据为采用第一fec码型编码且经过物理介质接入子层pma分发的数据;所述第一模块对所述多个第一子数据进行对齐,得到多个第一码字;所述第一模块对所述多个第一码字进行交织处理,得到所述第一数据。通过对多

个第一码字进行交织处理,能够消除后续采用第二fec码型编码后的码字内错误比特的相关性,从而提高纠错性能。

10.在一种可能的实施方式中,所述第一模块获取第一数据,包括:所述第一模块接收第二模块发送的多个第一子数据,所述多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据;所述第一模块对所述多个第一子数据进行对齐,得到多个第一码字;所述第一模块对所述多个第一码字进行交织处理,得到所述第一数据。在第一子数据进行了交织处理的情况下,后续对多个第一码字也进行交织处理,能够进一步消除后续采用第二fec码型编码后的码字内错误比特的相关性,从而提高纠错性能。

11.在一种可能的实施方式中,所述第一模块对所述多个第一子数据进行对齐,得到多个第一码字,包括:所述第一模块对所述多个第一子数据进行对齐,将对齐后的数据进行解交织,根据解交织的结果得到多个第一码字;或者,所述第一模块对所述多个第一子数据进行对齐,将对齐后的数据作为所述多个第一码字。在不解交织的情况下直接将对齐后的数据作为多个第一码字,可提高数据传输速度。

12.在一种可能的实施方式中,所述第一模块获取第一数据,包括:所述第一模块接收第二模块发送的多个第一子数据,所述多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据;所述第一模块对所述多个第一子数据进行对齐,得到所述第一数据。由于多个第一子数据为经过第一fec码型编码且经过交织处理及pma分发的数据,将多个第一子数据进行对齐得到第一数据,可进一步节省时延和功耗。

13.在一种可能的实施方式中,所述第一模块位于第一芯片,所述第二模块位于第二芯片,所述接收第二模块发送的多个第一子数据,包括:所述第一模块接收所述第二模块通过一个附件单元接口aui的多个通道发送的多个第一子数据。

14.在一种可能的实施方式中,所述第一模块位于第一芯片,所述第一模块获取第一数据,包括:所述第一模块接收第二模块通过一个附件单元接口aui的一个通道发送的多个第一子数据,所述第二模块位于第二芯片,所述多个第一子数据为采用第一fec码型编码且经过物理介质接入子层pma分发的数据,或者,所述多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据;所述第一模块对所述多个第一子数据进行对齐标志am锁定,得到多个第一码字;所述第一模块对所述多个第一码字进行交织处理,得到所述第一数据。

15.在一种可能的实施方式中,所述多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据,所述第一模块对所述多个第一子数据进行对齐标志am锁定,得到多个第一码字,包括:所述第一模块对所述多个第一子数据进行am锁定,将am锁定后的数据进行解交织,根据解交织的结果得到多个第一码字;或者,所述第一模块对所述多个第一子数据进行am锁定,将am锁定后的数据作为所述多个第一码字。

16.在一种可能的实施方式中,所述第一模块位于第一芯片,所述第一模块获取第一数据,包括:所述第一模块接收第二模块通过一个附件单元接口aui的一个通道发送的多个第一子数据,所述第二模块位于第二芯片,所述多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据;所述第一模块对所述多个第一子数据进行对齐标志am锁定,将am锁定后的数据作为所述第一数据。

17.在一种可能的实施方式中,所述第一模块对所述多个第二码字进行第二处理,得

到第二数据,包括:所述第一模块对所述多个第二码字进行交织处理,按照数据调制所需的符号或者至少一个比特对交织结果进行分组,将分组后的数据分发到对应的数据通道中;基于每个数据通道中的数据得到第二数据。

18.在一种可能的实施方式中,所述第一模块对所述多个第二码字进行第二处理,得到第二数据,包括:所述第一模块按照数据调制所需的符号或者至少一个比特对所述多个第二码字进行分组,将分组后的数据分发到对应的数据通道中;基于每个数据通道中的数据得到第二数据。

19.在一种可能的实施方式中,所述基于每个数据通道中的数据得到第二数据,包括:对每个数据通道中的数据插入相干链路所需要的训练序列与导频符号,得到处理后的数据,在所述处理后的数据中插入用于调整频点的数据,得到第二数据。

20.在一种可能的实施方式中,所述基于每个数据通道中的数据得到第二数据,包括:在每个数据通道中的数据中插入用于调整频点的数据,得到处理后的数据,在所述处理后的数据中插入相干链路所需要的训练序列与导频符号,得到第二数据。

21.在一种可能的实施方式中,所述对所述多个第一码字进行交织处理,包括:对所述多个第一码字进行直接交织,交织码字个数为参与交织的码字个数;或者,以参考间隔对所述多个第一码字进行错位交织,交织码字个数为参与交织的码字个数,所述参考间隔为两个码字之间错位的码块数量;或者,对所述多个第一码字进行卷积交织,交织码字个数为参与交织的码字个数。

22.在一种可能的实施方式中,所述对所述多个第二码字进行交织处理,包括:将所述多个第二码字中来自同一个编码器的第二码字进行交织;或者,将所述多个第二码字中来自多个编码器的多个第二码字进行交织;或者,将所述多个第二码字中来自同一个编码器的第二码字进行交织,将交织后获得的来自多个编码器的多个数据流进行再次交织。

23.在一种可能的实施方式中,所述第一模块按照第二fec码型对所述第一数据进行编码,得到多个第二码字,包括:所述第一模块分发所述第一数据得到多个第二子数据,所述第一模块按照所述第二fec码型分别对所述多个第二子数据进行编码,得到多个第二码字。

24.在一种可能的实施方式中,所述第一模块分发所述第一数据得到多个第二子数据,包括:所述第一模块通过物理编码子层pcs通道分发所述第一数据得到多个第二子数据;或者,所述第一模块通过物理介质接入子层pma分发所述第一数据得到多个第二子数据。

25.在一种可能的实施方式中,所述第一模块传输所述第二数据,包括:所述第一模块对所述第二数据进行分发,得到多个第三子数据,通过多条逻辑通道发送所述多个第三子数据。

26.第二方面,提供了一种数据传输的方法,该方法包括:第三模块获取第二数据,第二数据为采用第二前向纠错码fec码型对第一数据进行编码及进行第二处理得到的数据,第一数据为采用第一fec码型编码且经过第一处理的数据,第一处理包括交织处理;第三模块按照第二fec码型对所述第二数据进行解码,得到解码后的数据。

27.在一种可能的实施方式中,所述第三模块获取第二数据,包括:所述第三模块接收多个第三子数据,基于所述多个第三子数据恢复出第二数据。

28.第三方面,提供了一种数据传输的装置,该装置应用于第一模块,该装置包括:

29.获取单元,用于获取第一数据,所述第一数据为采用第一前向纠错码fec码型编码且经过第一处理的数据,所述第一处理包括交织处理;

30.编码单元,用于按照第二fec码型对所述第一数据进行编码,得到多个第二码字;

31.处理单元,用于对所述多个码字进行第二处理,得到第二数据;

32.传输单元,用于传输所述第二数据。

33.在一种可能的实施方式中,所述第二处理包括插入相干链路所需要的训练序列与导频符号中的至少一种。

34.在一种可能的实施方式中,所述第一处理和第二处理中的至少一个还包括插入用于调整频点的数据。

35.在一种可能的实施方式中,所述获取单元,用于接收第二模块发送的多个第一子数据,所述多个第一子数据为采用第一fec码型编码且经过物理介质接入子层pma分发的数据;对所述多个第一子数据进行对齐,得到多个第一码字;对所述多个第一码字进行交织处理,得到所述第一数据。

36.在一种可能的实施方式中,所述获取单元,用于接收第二模块发送的多个第一子数据,所述多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据;对所述多个第一子数据进行对齐,得到多个第一码字;对所述多个第一码字进行交织处理,得到所述第一数据。

37.在一种可能的实施方式中,所述获取单元,用于对所述多个第一子数据进行对齐,将对齐后的数据进行解交织,根据解交织的结果得到多个第一码字;或者,对所述多个第一子数据进行对齐,将对齐后的数据作为所述多个第一码字。

38.在一种可能的实施方式中,所述获取单元,用于接收第二模块发送的多个第一子数据,所述多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据;对所述多个第一子数据进行对齐,得到所述第一数据。

39.在一种可能的实施方式中,所述第一模块位于第一芯片,所述第二模块位于第二芯片,所述获取单元,用于接收所述第二模块通过一个附件单元接口aui的多个通道发送的多个第一子数据。

40.在一种可能的实施方式中,所述第一模块位于第一芯片,所述获取单元,用于接收所述第二模块通过一个附件单元接口aui的一个通道发送的多个第一子数据,所述第二模块位于第二芯片,所述多个第一子数据为采用第一fec码型编码且经过物理介质接入子层pma分发的数据,或者,所述多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据;对所述多个第一子数据进行对齐标志am锁定,得到多个第一码字;对所述多个第一码字进行交织处理,得到所述第一数据。

41.在一种可能的实施方式中,所述多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据,所述获取单元,用于对所述多个第一子数据进行am锁定,将am锁定后的数据进行解交织,根据解交织的结果得到多个第一码字;或者,对所述多个第一子数据进行am锁定,将am锁定后的数据作为所述多个第一码字。

42.在一种可能的实施方式中,所述第一模块位于第一芯片,所述获取单元,用于接收所述第二模块通过一个附件单元接口aui的一个通道发送的多个第一子数据,所述第二模

块位于第二芯片,所述多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据;对所述多个第一子数据进行对齐标志am锁定,将am锁定后的数据作为所述第一数据。

43.在一种可能的实施方式中,所述处理单元,用于对所述多个第二码字进行交织处理,按照数据调制所需的符号或者至少一个比特对交织结果进行分组,将分组后的数据分发到对应的数据通道中;基于每个数据通道中的数据得到第二数据。

44.在一种可能的实施方式中,所述处理单元,用于按照数据调制所需的符号或者至少一个比特对所述多个第二码字进行分组,将分组后的数据分发到对应的数据通道中;基于每个数据通道中的数据得到第二数据。

45.在一种可能的实施方式中,所述处理单元,用于对每个数据通道中的数据插入相干链路所需要的训练序列与导频符号,得到处理后的数据,在所述处理后的数据中插入用于调整频点的数据,得到第二数据。

46.在一种可能的实施方式中,所述处理单元,用于在每个数据通道中的数据中插入用于调整频点的数据,得到处理后的数据,在所述处理后的数据中插入相干链路所需要的训练序列与导频符号,得到第二数据。

47.在一种可能的实施方式中,所述获取单元,用于对所述多个第一码字进行直接交织,交织码字个数为参与交织的码字个数;或者,以参考间隔对所述多个第一码字进行错位交织,交织码字个数为参与交织的码字个数,所述参考间隔为两个码字之间错位的码块数量;或者,对所述多个第一码字进行卷积交织,交织码字个数为参与交织的码字个数。

48.在一种可能的实施方式中,所述处理单元,用于将所述多个第二码字中来自同一个编码器的第二码字进行交织;或者,将所述多个第二码字中来自多个编码器的多个第二码字进行交织;或者,将所述多个第二码字中来自同一个编码器的第二码字进行交织,将交织后获得的来自多个编码器的多个数据流进行再次交织。

49.在一种可能的实施方式中,所述编码单元,用于分发所述第一数据得到多个第二子数据,按照所述第二fec码型分别对所述多个第二子数据进行编码,得到多个第二码字。

50.在一种可能的实施方式中,所述编码单元,用于通过物理编码子层pcs通道分发所述第一数据得到多个第二子数据;或者,通过物理介质接入子层pma分发所述第一数据得到多个第二子数据。

51.在一种可能的实施方式中,所述传输单元,用于对所述第二数据进行分发,得到多个第三子数据,通过多条逻辑通道发送所述多个第三子数据。

52.第四方面,提供了一种数据传输的装置,该装置应用于第三模块,该装置包括:

53.获取单元,用于获取第二数据,所述第二数据为采用第二前向纠错码fec码型对第一数据进行编码及进行第二处理得到的数据,所述第一数据为采用第一fec码型编码且经过第一处理的数据,所述第一处理包括交织处理;

54.解码单元,用于按照所述第二fec码型对所述第二数据进行解码,得到解码后的数据。

55.在一种可能的实施方式中,所述获取单元,用于接收多个第三子数据,基于所述多个第三子数据恢复出第二数据。

56.第五方面,提供了一种数据传输的设备,该设备包括:处理器,处理器与存储器耦

合,存储器中存储有至少一条程序指令或代码,至少一条程序指令或代码由处理器加载并执行,以使设备实现如第一方面或第二方面中任一的数据传输的方法。

57.第六方面,提供了一种数据传输的系统,该系统包括:第一数据传输的设备,用于执行上述第一方面或第一方面任一所述的方法,第二数据传输的设备,用于执行上述第二方面或第二方面任一所述的方法。

58.第七方面,提供了一种计算机可读存储介质,该计算机可读存储介质中存储有至少一条程序指令或代码,程序指令或代码由处理器加载并执行时以使计算机实现如第一方面或第二方面中任一的数据传输的方法。

59.提供了另一种通信装置,该装置包括:通信接口、存储器和处理器。其中,该存储器和该处理器通过内部连接通路互相通信,该存储器用于存储指令,该处理器用于执行该存储器存储的指令,以控制通信接口接收数据,并控制通信接口发送数据,并且当该处理器执行该存储器存储的指令时,使得该处理器执行第一方面或第一方面的任一种可能的实施方式中的方法,或者执行第二方面或第二方面的任一种可能的实施方式中的方法。

60.作为一种示例性实施例,所述处理器为一个或多个,所述存储器为一个或多个。

61.作为一种示例性实施例,所述存储器可以与所述处理器集成在一起,或者所述存储器与处理器分离设置。

62.在具体实现过程中,存储器可以为非瞬时性(non-transitory)存储器,例如只读存储器(read only memory,rom),其可以与处理器集成在同一块芯片上,也可以分别设置在不同的芯片上,本技术实施例对存储器的类型以及存储器与处理器的设置方式不做限定。

63.提供了一种计算机程序(产品),所述计算机程序(产品)包括:计算机程序代码,当所述计算机程序代码被计算机运行时,使得所述计算机执行上述各方面中的方法。

64.提供了一种芯片,包括处理器,用于从存储器中调用并运行所述存储器中存储的指令,使得安装有所述芯片的设备执行上述各方面中的方法。

65.提供另一种芯片,包括:输入接口、输出接口、处理器和存储器,所述输入接口、输出接口、所述处理器以及所述存储器之间通过内部连接通路相连,所述处理器用于执行所述存储器中的代码,当所述代码被执行时,所述处理器用于执行上述各方面中的方法。

66.提供一种设备,包括上述方案中任一所述的芯片。

67.提供一种设备,包括上述方案中任一所述的第一芯片,和/或,上述方案中任一所述的第三芯片。

附图说明

68.图1是本技术实施例提供的一种数据传输的方法的实施场景示意图;

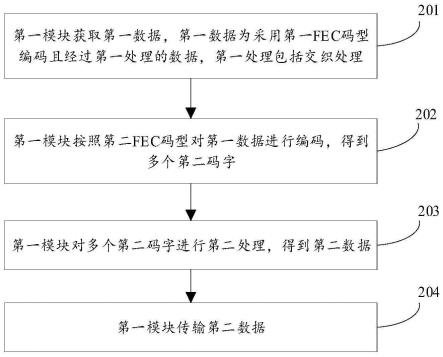

69.图2是本技术实施例提供的一种数据传输的方法流程图;

70.图3是本技术实施例提供的一种交织过程示意图;

71.图4是本技术实施例提供的另一种交织过程示意图;

72.图5是本技术实施例提供的一种数据发送的示意图;

73.图6是本技术实施例提供的另一种交织过程示意图;

74.图7是本技术实施例提供的另一种交织过程示意图;

75.图8是本技术实施例提供的另一种交织过程示意图;

76.图9是本技术实施例提供的一种数据处理系统的结构示意图;

77.图10是本技术实施例提供的另一种交织过程示意图;

78.图11是本技术实施例提供的另一种交织过程示意图;

79.图12是本技术实施例提供的一种数据处理过程示意图;

80.图13是本技术实施例提供的一种应用场景的实施环境示意图;

81.图14是本技术实施例提供的另一种应用场景的实施环境示意图;

82.图15是本技术实施例提供的另一种应用场景的实施环境示意图;

83.图16是本技术实施例提供的另一种应用场景的实施环境示意图;

84.图17是本技术实施例提供的另一种应用场景的实施环境示意图;

85.图18是本技术实施例提供的另一种应用场景的实施环境示意图;

86.图19是本技术实施例提供的另一种应用场景的实施环境示意图;

87.图20是本技术实施例提供的另一种数据传输的方法流程图;

88.图21是本技术实施例提供的一种数据传输的装置的结构示意图;

89.图22是本技术实施例提供的另一种数据传输的装置的结构示意图;

90.图23是本技术实施例提供的另一种数据传输的设备的结构示意图。

具体实施方式

91.本技术的实施方式部分使用的术语仅用于对本技术的实施例进行解释,而非旨在限定本技术。下面结合附图,对本发明的实施例进行描述。

92.在通信技术领域中,随着数据传输速率的提高,信道的损耗和噪声限制了数据传输的速率和距离。fec的出现,为传输中的数据提供了纠错保护,降低了数据传输过程中的误码率,从而能够提高信道中数据传输速率以及传输距离。但随着数据传输速率的不断提高,传输距离不断增加,对fec的要求也越来越高。与此同时,更强的fec往往需要更多校验位,从而使数据所需带宽更高。因此,对于链路速率提高、信道更为挑战的场景,可能需要更高编码增益的fec。例如,对于800吉比特以太网(gigabyte ethernet,ge)/1.6太比特以太网(trillion-byte ethernet,te)的以太接口,或者200g四阶脉冲幅度调制(4-level pulse amplitude modulation,pam4)光链路等。更高速率的传输往往面对更为严苛的信道和误码率要求,而更强的fec可以在纠前误码率升高之后,使纠后的误码率保持在一个好的水平。

93.当传输距离越短,路径时延所占的总体传输时延比例越低,fec带来的时延相应占比也越高,成为系统时延的制约因素。例如,如果在10km的距离上,光纤时延大约为50μs,1μs的fec时延仅为路径时延的2%,但如果是1km的距离,光纤时延为5μs,则1μs的fec时延将是路径时延的20%。随着距离进一步缩短,这一比例将持续提高,这显然是不可接受的。

94.对此,本技术实施例提供了一种数据传输的方法,该方法基于传输数据的第一模块将获取的采用第一fec码型编码的第一数据通过第二fec码型进行再一次编码,得到级联编码的第二数据,使该第二数据具有更高的编码增益,在容易出现误码的通道中传输时,能够对出现误码的数据进行有效的纠错,从而提高数据传输的质量。其次,由于第二数据为在第一数据的基础上直接编码获得的数据,该方法的实现过程较为简便,提高了数据传输的

效率。再有,由于第一数据是经过交织处理得到的数据,能够将第二fec码纠后的码字内错误比特相关性消除,提高纠错性能,进一步提高数据传输的质量。

95.本技术实施例的方法可适用于当前的以太接口或者其他需要传输数据的场景下,例如,相干光(coherent optics)往往具有较长的突发误码以及较高的误码率(biterror,ber),本技术实施例提供的方法可用于相干链路的、低时延的级联fec。以图1所示的实施场景为例,该实施场景包括多个模块,各个模块之间能够进行信息的交互,实现数据的传输。如图1所示,第一模块101与第二模块102之间,第一模块101与第三模块103之间均可以进行数据的传输。需要说明的是,如图1所示的实施场景可以包括n个模块,n为大于等于2的正整数,图1中仅以模块数量为3个为例进行说明。此外,各个模块可以位于同一芯片内,也可以位于不同芯片内。

96.结合图1所示的实施场景,本技术实施例提供的数据传输的方法如图2所示,包括但不限于步骤201至步骤203。

97.201,第一模块获取第一数据,第一数据为采用第一fec码型编码且经过第一处理的数据,第一处理包括交织处理。

98.本技术实施例提供的方法采用级联编码的方式,通过第一模块将获取的采用第一fec码型编码的第一数据通过第二fec码型进行再一次编码,得到级联编码的第二数据。由于通过交织处理能够消除后续采用第二fec码型编码后的码字内错误比特的相关性,从而提高纠错性能,因此,第一数据为采用第一fec码型编码且经过第一处理的数据,该第一处理包括交织处理。

99.本技术实施例不对第一模块获取第一数据的方式进行限定,在一种可能的实现方式中,第一模块与第二模块能够进行数据的传输,第一模块接收第二模块发送的多个第一子数据,基于第一子数据获取第一数据。其中,第一子数据为采用第一fec码型编码的数据,本技术实施例不对第一fec码型进行限定,示例性地,第一fec码型为里德-所罗门(reed-solomon,rs)码、博斯-乔赫里-霍克文黑姆(bose-chaudhuri-hocquenghem,bch)码、法尔(fire)码、涡轮(turbo)码、涡轮乘积码(turbo product code,tpc)、阶梯(staircase)码以及低密度奇偶校验(low-density parity-check,ldpc)码中的任一种。

100.第一子数据除了采用第一fec码型编码外,还经过其他处理。本技术实施例不对第一子数据除了第一fec码型编码之外的其他处理的处理方式进行限定。例如,该第一子数据为采用第一fec码型编码且经过物理介质接入子层(physical medium attachment sublayer,pma)分发的数据,或者,该第一子数据为采用第一fec码型编码且经过交织处理及pma分发的数据。根据第一子数据的不同情况,第一模块获取第一数据的方式,包括但不限于如下四种。

101.获取第一数据的方式一,第一模块获取第一数据,包括:第一模块接收第二模块发送的多个第一子数据,多个第一子数据为采用第一fec码型编码且经过pma分发的数据;第一模块对多个第一子数据进行对齐,得到多个第一码字;第一模块对多个第一码字进行交织处理,得到第一数据。

102.在获取第一数据的方式一中,第一模块位于第一芯片,第二模块位于第二芯片,第一模块接收第二模块发送的多个第一子数据,包括但不限于第一模块接收第二模块通过一个附件单元接口(attachment unit interface,aui)的多个通道发送的多个第一子数据。

示例性地,一个第一子数据通过一个aui通道发送。

103.其中,多个第一子数据为经过第一fec码型编码且pma分发的数据,但该第一子数据未进行过交织处理,因此,为了获取经过交织处理的第一数据,第一模块接收到多个第一子数据后,对多个第一子数据进行对齐,得到多个第一码字,之后再对多个第一码字进行交织处理,得到第一数据。在获取第一数据的方式一中,由于第一子数据未经过交织处理,但第一模块对多个第一码字进行了交织处理,在本技术实施例中,第一子数据采用第一fec码型编码可以称为外码编码,第一码字称为外码码字,该外码编码发生在第二模块。

104.关于对多个第一子数据进行对齐的方式,本技术实施例不进行限定。由于以对齐标志(alignment marker,am)字符为边界,也正因为如此,am字符能够为数据识别提供已有的标记,从而便于后续对插入的数据进行识别。因此,针对第一子数据包括am字符的情况,对多个第一子数据进行对齐包括但不限于am锁定和去偏斜(deskew)。其中,am锁定用于寻找码字的边界,寻找到码字边界后,便可以按照400gbe定义的方式进行去偏斜,进而获得第一码字。

105.在本技术实施例中,将第一模块对多个第一码字进行的交织处理称为外码交织,因此,该获取第一数据的方式一中,第二模块内未进行交织处理,第一模块内进行了外码交织。关于对多个第一码字进行交织处理也即外码交织的方式,包括但不限于如下三种。

106.外码交织方式一,对多个第一码字进行直接交织,交织码字个数为参与交织的码字个数。

107.直接交织是指将参与交织的码字无间隔的按照交织粒度依次进行交织,得到的交织码字个数为参与交织的码字个数。如图3所示,以多个第一码字为码字a、码字b、码字c和码字d这4个码字为例,对这4个码字进行直接交织得到的交织码字个数为参与交织的码字个数。例如,图3中参与交织的码字个数为4,则交织码字的个数以m表示,m=4。

108.如图4所示,码字a的内容包括a0、a1、a2、a3、a4、a5、a6和a7,码字b的内容包括b0、b1、b2、b3、b4、b5、b6和b7,码字c的内容包括c0、c1、c2、c3、c4、c5、c6和c7,码字d的内容包括d0、d1、d2、d3、d4、d5、d6和d7。对码字a、码字b、码字c和码字d进行直接交织后,按照图4中的箭头所示方向依次发送a0、b0、c0、d0、a1、b1、c1、d1

…

,依此类推,发送顺序如图5所示。图4和图5中,a0,b0等一个单元格代表交织粒度。本技术实施例不对交织粒度进行限定,包括但不限于1比特、1个正交幅度调制(quadrature amplitude modulation,qam)16符号,或者为多比特、多个符号。

109.外码交织方式二,以参考间隔对多个第一码字进行错位交织,交织码字个数为参与交织的码字个数,参考间隔为两个码字之间错位的码块数量。

110.错位交织是指将参与交织的码字以参考间隔按照交织粒度依次进行交织,得到的交织码字个数为参与交织的码字个数。如图6所示,以多个第一码字为码字a、码字b、码字c和码字d这4个码字为例,以参考间隔对这4个码字进行错位交织之后,得到的交织码字个数为参与交织的码字个数。例如,图6中参与交织的码字个数为4,则交织码字的个数以m表示,m=4。

111.其中,码字a的内容包括a0、a1、a2、a3、a4、a5、a6和a7,码字b的内容包括b0、b1、b2、b3、b4、b5、b6和b7,码字c的内容包括c0、c1、c2、c3、c4、c5、c6和c7,码字d的内容包括d0、d1、d2、d3、d4、d5、d6和d7。以参考间隔为k个码块,且k=1为例,也即是将码字a、码字b、码字c和

码字d以1个码块延迟按照交织粒度依次进行错位交织后,按照图7中的箭头所示方向发送a0、a1、b0、a2、b1、c0、a3、b2、c1、d0、a4、b3、c2、d1

…

,依此类推。图7中,a0,b0等一个单元格代表交织粒度。本技术实施例不对交织粒度进行限定,包括但不限于1比特、1个qam16符号,或者为多比特、多个符号。

112.可选地,图7仅以k=1,也即参考间隔为1个码块为例进行说明,但并不用于限制本技术。k还可以为其他值,也即参考间隔可以为其他值,本技术实施例不对参考间隔进行限定。

113.外码交织方式三,对多个第一码字进行卷积交织,交织码字个数为参与交织的码字个数。

114.该交织方式三中,码字不是并行进入不同时延的通道,而是串行进入。卷积交织是指将输入比特流也即参与交织的多个第一码字按照p比特为一个数据块单元进行轮询分发到多个具有不同长度延时的寄存器,这些寄存器对应的延时按照数据块分发到达的先后顺序通常为等量递增或者递减,然后来自各个寄存器经过不等量延时的数据块再汇聚到同一数据流中形成交织后的比特流。其中,本技术实施例不对p的大小进行限定,可基于应用场景或者经验设置。

115.如图8所示,来自第一模块的多个第一码字,按照最初第一模块中所发送的原始数据的排列顺序,被依次分发到n条通道,每条通道具有不同的时延。图8中,以寄存器对应的延时按照数据块分发到达的先后顺序通常为等量递增为例,通道1的时延为1个单位,通道2时延为2个单位,以此类推。可选地,时延累加的起点可以是0个单位。以寄存器对应的延时按照数据块分发到达的先后顺序通常为等量递减为例,通道1的时延可以是最大值,例如n个单位,通道2时延为n-1个单位,以此类推。可选地,时延递减的起点也可以是n-1,直至最小值为0。

116.无论是递增还是递减,上述时延单位,可以是n比特对应的时延,n为正整数。示例性地,选取的n的数值可以为内码的码长,也即第二fec码型的码长。

117.获取第一数据的方式二,第一模块获取第一数据,包括:第一模块接收第二模块发送的多个第一子数据,多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据;第一模块对多个第一子数据进行对齐,得到多个第一码字;第一模块对多个第一码字进行交织处理,得到第一数据。

118.在获取第一数据的方式二中,第一模块位于第一芯片,第二模块位于第二芯片,第一模块接收第二模块发送的多个第一子数据,包括但不限于第一模块接收第二模块通过一个aui的多个通道发送的多个第一子数据。示例性地,一个第一子数据通过一个aui通道发送。

119.由于多个第一子数据为经过第一fec码型编码且经过交织处理及pma分发的数据,第一模块接收到多个第一子数据后,可以对多个第一子数据进行对齐,得到多个第一码字。之后再对多个第一码字进行交织处理,得到第一数据。在获取第一数据的方式二中,由于第一子数据经过交织处理,且第一模块又对多个第一码字进行了交织处理,因而可进一步提高纠错性能。此外,在本技术实施例中,将第一模块对多个第一码字进行的交织处理称为外码交织,因此,该获取第一数据的方式二中,第二模块内进行了交织处理,第一模块内进行了外码交织。

120.关于对多个第一子数据进行对齐的方式,也仍然包括但不限于am锁定和去偏斜。此外,对多个第一码字进行交织处理的方式,可参考上述获取第一数据的方式一中有关外码交织方式一至三的描述,此处不再赘述。

121.需要说明的是,获取第一数据的方式二中,由于多个第一子数据为经过第一fec码型编码且经过交织处理及pma分发的数据,且得到多个第一码字后还需要进行交织处理,因此,第一模块对多个第一子数据进行对齐,得到多个第一码字时,可包括解交织的操作,也可不解交织,而直接对多个第一码字进行交织处理。

122.示例性地,第一模块对多个第一子数据进行对齐,得到多个第一码字,包括:第一模块对多个第一子数据进行对齐,将对齐后的数据进行解交织,根据解交织的结果得到多个第一码字。例如,如果第二模块中进行的交织是2个码字交织,那么第一模块获取多个第一子数据,并对多个第一子数据进行对齐后,得到2*n个码字长度的数据,解交织的情况下,将这2*n个码字长度的数据解交织,根据解交织结果得到多个第一码字,进行上述获取第一数据的方式一中有关外码交织方式一至三的描述。

123.或者,第一模块对多个第一子数据进行对齐,得到多个第一码字,包括:第一模块对多个第一子数据进行对齐,将对齐后的数据作为多个第一码字。例如,如果第二模块中进行的交织是2个码字交织,那么第一模块获取多个第一子数据,并对多个第一子数据进行对齐后,得到2*n个码字长度的数据,不解交织的情况下,将这2*n个码字长度的数据作为2*n个码字也即多个第一码字,进行上述获取第一数据的方式一中有关外码交织方式一至三的描述。在不解交织的情况下直接将对齐后的数据作为多个第一码字,可提高数据传输速度。

124.获取第一数据的方式三,第一模块获取第一数据,包括:第一模块接收第二模块发送的多个第一子数据,多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据;第一模块对多个第一子数据进行对齐,得到第一数据。

125.在获取第一数据的方式三中,第一模块位于第一芯片,第二模块位于第二芯片,第一模块接收第二模块发送的多个第一子数据,包括但不限于第一模块接收第二模块通过一个aui的多个通道发送的多个第一子数据。示例性地,一个第一子数据通过一个aui通道发送。

126.由于多个第一子数据为经过第一fec码型编码且经过交织处理及pma分发的数据,第一模块接收到多个第一子数据后,可以不再进行交织处理,仅将多个第一子数据进行对齐即可。由此,可节省获得第一码字的步骤,进一步节省时延和功耗。在获取第一数据的方式三中,由于第一子数据经过交织处理,但第一模块内未进行交织处理,因此,第二模块内进行了交织处理,第一模块内未进行外码交织。

127.关于对多个第一子数据进行对齐的方式,包括但不限于am锁定和去偏斜。

128.需要说明的是,以上获取第一数据的方式一至方式三中,第一模块获取第一数据时,均是从第二模块接收通过aui的多个通道发送的多个第一子数据。可选地,第一模块还可以接收第二模块通过aui的一个通道发送的多个第一子数据,详见如下获取第一数据的方式四。

129.获取第一数据的方式四,第一模块位于第一芯片,第一模块获取第一数据,包括:第一模块接收第二模块通过一个aui的一个通道发送的多个第一子数据,第二模块位于第二芯片,多个第一子数据为采用第一fec码型编码且经过pma分发的数据,或者,多个第一子

数据为采用第一fec码型编码且经过交织处理及pma分发的数据;第一模块对多个第一子数据进行am锁定,根据am锁定后的数据获取第一数据。

130.示例性地,第一模块对多个第一子数据进行am锁定,根据am锁定后的数据获取第一数据,包括:第一模块对多个第一子数据进行am锁定,得到多个第一码字;第一模块对多个第一码字进行交织处理,得到第一数据。

131.在获取第一数据的方式四中,由于多个第一子数据是由一个aui的一个通道发送的,且这多个第一子数据不仅采用了第一fec码型编码,还经过了pma分发,针对多个第一子数据未经过交织处理的情况,为了获取经过交织处理的第一数据,第一模块接收到多个第一子数据后,对多个第一子数据进行am锁定即可得到多个第一码字,之后再对多个第一码字进行交织处理,得到第一数据。在获取第一数据的方式四中,由于第一子数据未经过交织处理,但第一芯片对多个第一码字进行了交织处理,在本技术实施例中,将第一模块对多个第一码字进行的交织处理称为外码交织,因此,该获取第一数据的方式四中,第二模块内未进行交织处理,第一模块内进行了外码交织。

132.在一种可能的实现方式中,该获取第一数据的方式四中的多个第一子数据是由一个aui的一个通道发送的,且这多个第一子数据不仅采用了第一fec码型编码,还经过了交织处理及pma分发,针对多个第一子数据经过交织处理的情况,由于得到多个第一码字后还需要进行交织处理,因此,在该获取第一数据的方式四中,第一模块对多个第一子数据进行am锁定,得到多个第一码字时,可包括解交织的操作,也可不解交织,而直接对多个第一码字进行交织处理。

133.示例性地,第一模块对多个第一子数据进行am锁定,得到多个第一码字,包括:第一模块对多个第一子数据进行am锁定,将am锁定后的数据进行解交织,根据解交织的结果得到多个第一码字。例如,如果第二模块中进行的交织是2个码字交织,那么第一模块获取多个第一子数据,并对多个第一子数据进行am锁定后,得到2*n个码字长度的数据,解交织的情况下,将这2*n个码字长度的数据解交织,根据解交织结果得到多个第一码字,再进行对多个第一码字的交织处理。

134.或者,第一模块对多个第一子数据进行am锁定,得到多个第一码字,包括:第一模块对多个第一子数据进行am锁定,将am锁定后的数据作为多个第一码字。例如,如果第二模块中进行的交织是2个码字交织,那么第一模块获取多个第一子数据,并对多个第一子数据进行am锁定后,得到2*n个码字长度的数据,不解交织的情况下,将这2*n个码字长度的数据作为2*n个码字也即多个第一码字,再进行对多个第一码字的交织处理。

135.此外,对多个第一码字进行交织处理的方式,可参考上述获取第一数据的方式一中有关外码交织方式一至三的描述,此处不再赘述。

136.在一种可能的实现方式中,多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据,第一模块对多个第一子数据进行am锁定,根据am锁定后的数据获取第一数据,包括:第一模块对多个第一子数据进行am锁定,将am锁定后的数据作为第一数据。

137.例如,第一模块位于第一芯片,第二模块位于第二芯片,第一模块获取第一数据,包括:第一模块接收第二模块通过一个aui的一个通道发送的多个第一子数据,多个第一子数据为采用第一fec码型编码且经过交织处理及pma分发的数据;第一模块对多个第一子数

据进行对齐标志am锁定,将am锁定后的数据作为第一数据。

138.202,第一模块按照第二fec码型对第一数据进行编码,得到多个第二码字。

139.无论采用上述获取第一数据的方式一至方式四中的哪种方式获取到第一数据,为了进一步提高纠错性能,实现级联编码,第一模块获取到第一数据后,均按照第二fec码型对第一数据进行编码,得到多个第二码字。对第一数据进行编码可以称为内码编码,第二码字称为内码码字,该内码编码发生在第一模块。

140.其中,该第二fec码型包括但不限于为rs码、bch码、法尔码、涡轮码、涡轮乘积码、阶梯码以及ldpc码中的任一种,本技术实施例对第二fec码型的类型不做限定。示例性地,如果第二码字的码率(code rate)为r(r=k/n),编码前第一数据的速率为d,则编码后的速率为d/r。其中,k为码字信息位长度,n为码字长度,码字长度为信息位长度加校验位长度。例如,编码前第一数据的速率为d=425gb/s,如果选择r=17/18,则编码后的速率为d/r=450gb/s。如果r=239/256,则编码后的速率d/r约为455.23gb/s。

141.在一种可能的实现方式中,第一模块按照第二fec码型对第一数据进行编码,得到多个第二码字,包括:第一模块分发第一数据得到多个第二子数据,第一模块按照第二fec码型分别对多个第二子数据进行编码,得到多个第二码字。

142.示例性地,第一模块分发第一数据得到多个第二子数据,包括:第一模块通过物理编码子层(physical coding sublayer,pcs)通道分发第一数据得到多个第二子数据;或者,第一模块通过pma分发第一数据得到多个第二子数据。本技术实施例不对第一模块分发得到的第二子数据的数量进行限定,例如,可基于应用场景或者经验确定分发得到的第二子数据的数量。

143.203,第一模块对多个第二码字进行第二处理,得到第二数据。

144.在一种可能的实现方式中,第一模块对多个第二码字进行第二处理,获取第二数据的方式,包括但不限于如下两种。

145.获取第二数据的方式一,第一模块对多个第二码字进行第二处理,得到第二数据,包括:第一模块对多个第二码字进行交织处理,按照数据调制所需的符号或者至少一个比特对交织结果进行分组,将分组后的数据分发到对应的数据通道中;基于每个数据通道中的数据得到第二数据。

146.在获取第二数据的方式一中,通过对多个第二码字进行交织处理,能够应对链路上的突发误码,进一步提高了纠错性能。本技术实施例不对多个第二码字进行交织处理的方式进行限定,经过交织处理后的第二码字生成p路数据,p为大于或等于1的整数。每路数据对应一个内码编码器。例如,如图9所示,外码交织通过外码交织器实现,内码交织通过内码交织器实现,每路数据对应一个内码编码器。示例性地,对多个第二码字进行交织处理,包括但不限于如下三种交织处理方式。

147.内码交织方式一,将多个第二码字中来自同一个编码器的第二码字进行交织。

148.该内码交织方式一中,多个第二码字中来自同一个编码器的第二码字的数量为m’,对m’个第二码字可按照交织粒度k’进行交织。如图10所示,以来自同一个编码器的m’个码字分别为码字a、码字b、码字c和码字d为例,其中,码字a的内容包括a0、a1、a2、a3、a4、a5

…

,码字b的内容包括b0、b1、b2、b3、b4、b5

…

,码字c的内容包括c0、c1、c2、c3、c4、c5

…

,码字d的内容包括d0、d1、d2、d3、d4、d5

…

。将码字a、码字b、码字c和码字d以交织粒度k’进行交

织后,按照图10中的箭头所示方向发送a0、b0、c0、d0、a1、b1、c1、d1、a2、b2

…

,依此类推。图10中,a0,b0等一个单元格代表交织粒度。本技术实施例不对交织粒度k’进行限定,包括但不限于1比特、1个qam16符号,或者为多比特、多个符号。

149.内码交织方式二,将多个第二码字中来自多个编码器的多个第二码字进行交织。

150.该内码交织方式二中,由于是将多个第二码字中来自多个编码器的多个第二码字进行交织,因而参与交织的码字数量等于编码器的数量。如图11所示,以来自编码器a、编码器b、编码器c和编码器d的4个第二码字进行交织为例,这4个第二码字分别为码字a、码字b、码字c和码字d。其中,码字a的内容包括a0、a1、a2、a3、a4、a5

…

,码字b的内容包括b0、b1、b2、b3、b4、b5

…

,码字c的内容包括c0、c1、c2、c3、c4、c5

…

,码字d的内容包括d0、d1、d2、d3、d4、d5

…

。将码字a、码字b、码字c和码字d以交织粒度k’进行交织后,按照图11中的箭头所示方向发送a0、b0、c0、d0、a1、b1、c1、d1、a2、b2

…

,依此类推。

151.内码交织方式三,将多个第二码字中来自同一个编码器的第二码字进行交织,将交织后获得的来自多个编码器的多个数据流进行再次交织。

152.该内码交织方式三是上述内码交织方式一和内码交织方式二的综合,先将多个第二码字中来自同一个编码器的第二码字进行交织,来自不同编码器的第二码字分别交织之后得到多个数据流,一个编码器得到一个数据流。之后,再将交织后获得的来自多个编码器的多个数据流进行再次交织。由于该内码交织方式三采用了两个维度的交织,因而经过内码交织得到的第二数据的纠错性能更好。

153.无论采用上述内码交织的方式一还是方式二,该获取第二数据的方式一均能通过内码交织获得数据流,之后,可按照数据调制所需的符号进行分组,并分发到两个偏振方向对应的数据通道中。例如,连续的8比特数据,前4比特分到x偏振,后4比特分到y偏振。

154.此外,需要说明的是,上述内码交织的方式一至方式三中,无论是对来自同一个编码器的第二码字进行交织,还是对来自多个编码器的多个数据流进行交织,还是对来自多个编码器的多个第二码字进行交织,均可以采用上述外码交织方式一至三中所述的直接交织、错位交织和卷积交织中的任一种方式进行交织,具体采用哪种交织方式,本技术实施例不进行限定。

155.获取第二数据的方式二,第一模块对多个第二码字进行第二处理,得到第二数据,包括:第一模块按照数据调制所需的符号或者至少一个比特对多个第二码字进行分组,将分组后的数据分发到对应的数据通道中;基于每个数据通道中的数据得到第二数据。

156.在该获取第二数据的方式二中,第一模块未对第二码字进行交织处理,可直接按照数据调制所需的符号或者至少一个比特对多个第二码字进行分组,节省了内码交织的时延和功耗。例如,按照数据调制所需的符号进行分组,并分发到两个偏振方向对应的数据通道中时,可将连续的8比特数据中的前4比特分到x偏振,后4比特分到y偏振。

157.在一种可能的实现方式中,本技术实施例提供的方法可应用于相干链路。考虑到内码、外码开销后的数据流,在相干链路上插入训练序列(training sequence,ts)/导频符号(pilot symbol)时,可采用凑出频点的方法。因此,第二处理包括但不限于插入相干链路所需要的训练序列与导频符号中的至少一种。

158.可选地,第一处理和第二处理中的至少一个还包括插入用于调整频点的数据。本技术实施例不对用于调整频点的数据的类型及内容进行限定,该用于调整频点的数据可以

是按照固定长度周期性插入,关于固定长度以及周期,可基于应用场景或经验确定,本技术实施例对此不进行限定。如果频点不合适,或者说频点不符合要求,则第一处理和第二处理中均可包括插入用于调整频点的数据,或者,第一处理或第二处理中包括插入用于调整频点的数据。如果频点合适,第一处理和第二处理也可都不插入用于调整频点的数据。

159.此外,本技术实施例也不对插入相干链路所需要的训练序列与导频符号以及插入用于调整频点的数据的先后顺序进行限定。

160.例如,基于每个数据通道中的数据得到第二数据,包括:对每个数据通道中的数据插入相干链路所需要的训练序列与导频符号,得到处理后的数据,在处理后的数据中插入用于调整频点的数据,得到第二数据。

161.或者,基于每个数据通道中的数据得到第二数据,包括:在每个数据通道中的数据中插入用于调整频点的数据,得到处理后的数据,在处理后的数据中插入相干链路所需要的训练序列与导频符号,得到第二数据。

162.需要说明的是,本技术实施例不对插入的训练序列与导频符号进行限定,例如,该插入的训练序列与导频符号可以是预先配置好的,且基于应用场景或者经验进行配置。如果训练序列和导频符号插入后,频点已经合适,则不需要进行频点调整步骤,也即无需插入用于调整频点的数据。例如,图12中,ts对应训练序列,ps对应导频符号,oh则对应未调整频点而增加的额外数据。示例性地,ts的第一个符号为ps序列的一部分。

163.例如,当t=t1=0(即不存在ts和oh),则k=0。则编码后的速率为:d/r*(p 1)/p。如果p=72,则最终速率为456.25gb/s。在dp-qam16调制下,该码率对应波特率为57.03125gbd,为基频156.25mhz的365倍频。

164.又例如,当t≠0时,即存在ts时,需要考虑d_out对应波特率也为整数倍频。例如,t=10,t1=63,t=100,t1=1,则d_out=457.5gb/s,在dp-qam16调制下,波特率为366倍频。

165.需要说明的是,上述t1的值可以大于p,此时,oh内容可能会跨过1个或者多个ps。

166.204,第一模块传输第二数据。

167.在一种可能的实现方式中,第一模块传输第二数据,包括:第一模块对第二数据进行分发,得到多个第三子数据,通过多条逻辑通道发送多个第三子数据。

168.本技术实施例不对第一模块对第二数据进行分发得到的第三子数据的数量进行限定,例如,可基于应用场景或者经验确定分发得到的第三子数据的数量。

169.本技术实施例提供的方法,基于传输数据的第一模块将获取的采用第一fec码型编码的第一数据通过第二fec码型进行再一次编码,得到级联编码的第二数据,使该第二数据具有更高的编码增益,在容易出现误码的通道中传输时,能够对出现误码的数据进行有效的纠错,从而提高数据传输的质量。由于第二数据为在第一数据的基础上直接编码获得的数据,该方法的实现过程较为简便,提高了数据传输的效率。再有,由于第一数据是经过交织处理得到的数据,能够将第二fec码纠后的码字内错误比特相关性消除,提高纠错性能。此外,通过同时采用外码交织和内码交织,可进一步提高纠错性能。

170.接下来,结合上述图2所示的方法流程,以第一模块位于第一芯片,第二模块位于第二模块,针对如下几种场景为例,对本技术实施例提供的数据传输方法进行举例说明。

171.场景一:第二芯片未进行交织处理,第一芯片进行了外码交织和内码交织。

172.该场景一即为图2所示实施例中获取第一数据的方式一与获取第二数据的方式一

的组合,也即第二芯片未进行交织处理,第一芯片既对第一码字进行了交织处理,也对第二码字进行了交织处理。该场景的实施环境可如图13所示,数据传输的过程如下。

173.第二芯片对原始数据进行外码编码,也即采用fec1(第一fec码型)编码,并将编码后的数据进行pma分发,得到多个第一子数据,再通过aui将多个第一子数据发送到第一芯片,该多个第一子数据为采用第一fec码型编码且经过pma分发的数据。第一芯片接收到多个第一子数据后,对多个第一子数据进行am锁定和去偏斜,从而实现对齐操作,得到多个第一码字。之后,第一芯片对多个第一码字进行交织处理也即外码交织,得到第一数据。

174.进一步地,第一芯片按照第二fec码型对第一数据进行编码,得到多个第二码字后,对多个第二码字进行交织处理也即内码交织,再按照数据调制所需的符号对交织结果进行分组,将分组后的数据分发到对应的数据通道中;基于每个数据通道中的数据得到第二数据。最后,将第二数据调制发送。

175.场景二:第二芯片未进行交织处理,第一芯片进行了外码交织和内码交织,且第一芯片进行了频点调整及ts/pilot插入。

176.该场景二是在场景一基础上,加入了频点调整及ts/pilot插入的操作。因此,该场景二也可以为图2所示实施例中获取第一数据的方式一与获取第二数据的方式一的组合,也即第二芯片未进行交织处理,第一芯片既对第一码字进行了交织处理,也对第二码字进行了交织处理。该场景的实施环境可如图14所示,数据传输的过程如下。

177.第二芯片对原始数据进行了外码编码,也即采用fec1(第一fec码型)编码,并将编码后的数据进行pma分发,得到多个第一子数据,再通过aui将多个第一子数据发送到第一芯片,该多个第一子数据为采用第一fec码型编码且经过pma分发的数据。第一芯片接收到多个第一子数据后,对多个第一子数据进行am锁定和去偏斜,从而实现对齐操作,得到多个第一码字。之后,第一芯片对多个第一码字进行交织处理也即外码交织,得到第一数据。

178.进一步地,第一芯片按照第二fec码型对第一数据进行编码,得到多个第二码字后,对多个第二码字进行交织处理也即内码交织,再按照数据调制所需的符号对交织结果进行分组,将分组后的数据分发到对应的数据通道中;基于每个数据通道中的数据得到第二数据。最后,将第二数据调制发送。

179.其中,场景二中,基于每个数据通道中的数据得到第二数据,包括:对每个数据通道中的数据插入相干链路所需要的训练序列与导频符号,得到处理后的数据,在处理后的数据中插入用于调整频点的数据,得到第二数据。

180.或者,基于每个数据通道中的数据得到第二数据,包括:在每个数据通道中的数据中插入用于调整频点的数据,得到处理后的数据,在处理后的数据中插入相干链路所需要的训练序列与导频符号,得到第二数据。

181.场景三:第二芯片未进行交织处理,第一芯片进行了外码交织,未进行内码交织,且第一芯片进行了频点调整及ts/pilot插入。

182.该场景三与场景二相比,减少了第一芯片进行内码交织的操作。该场景三为图2所示实施例中获取第一数据的方式一与获取第二数据的方式二的组合,也即第二芯片未进行交织处理,第一芯片仅对第一码字进行了外码交织处理。该场景的实施环境可如图15所示,数据传输的过程如下。

183.第二芯片对原始数据进行外码编码,也即采用fec1(第一fec码型)编码,并将编码

后的数据进行pma分发,得到多个第一子数据,再通过aui将多个第一子数据发送到第一芯片,该多个第一子数据为采用第一fec码型编码且经过pma分发的数据。第一芯片接收到多个第一子数据后,对多个第一子数据进行am锁定和去偏斜,从而实现对齐操作,得到多个第一码字。之后,第一芯片对多个第一码字进行交织处理也即外码交织,得到第一数据。

184.进一步地,第一芯片按照第二fec码型对第一数据进行编码,得到多个第二码字后,第一芯片按照数据调制所需的符号对多个第二码字进行分组,将分组后的数据分发到对应的数据通道中;基于每个数据通道中的数据得到第二数据。最后,将第二数据调制发送。

185.其中,场景三中,基于每个数据通道中的数据得到第二数据,包括:对每个数据通道中的数据插入相干链路所需要的训练序列与导频符号,得到处理后的数据,在处理后的数据中插入用于调整频点的数据,得到第二数据。

186.或者,基于每个数据通道中的数据得到第二数据,包括:在每个数据通道中的数据中插入用于调整频点的数据,得到处理后的数据,在处理后的数据中插入相干链路所需要的训练序列与导频符号,得到第二数据。

187.场景四:第二芯片进行了交织处理,第一芯片进行了外码交织和内码交织,且第一芯片进行了频点调整及ts/pilot插入。

188.该场景四可以为图2所示实施例中获取第一数据的方式二与获取第二数据的方式一的组合,也即第二芯片进行了交织处理,第一芯片既对第一码字进行了交织处理,也对第二码字进行了交织处理。该场景的实施环境可如图16所示,数据传输的过程如下。

189.第二芯片对原始数据进行外码编码,也即采用fec1(第一fec码型)编码,并对编码后的数据进行外码交织,将交织后的数据流进行pma分发,得到多个第一子数据,再通过aui将多个第一子数据发送到第一芯片,该多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据。第一芯片接收到多个第一子数据后,对多个第一子数据进行am锁定和去偏斜,从而实现对齐操作,然后通过解交织得到多个第一码字。之后,第一芯片对多个第一码字进行交织处理也即外码交织,得到第一数据。

190.进一步地,第一芯片按照第二fec码型对第一数据进行编码,得到多个第二码字后,对多个第二码字进行交织处理也即内码交织,再按照数据调制所需的符号对交织结果进行分组,将分组后的数据分发到对应的数据通道中;基于每个数据通道中的数据得到第二数据。最后,将第二数据调制发送。

191.其中,场景四中,基于每个数据通道中的数据得到第二数据,包括:对每个数据通道中的数据插入相干链路所需要的训练序列与导频符号,得到处理后的数据,在处理后的数据中插入用于调整频点的数据,得到第二数据。

192.或者,基于每个数据通道中的数据得到第二数据,包括:在每个数据通道中的数据中插入用于调整频点的数据,得到处理后的数据,在处理后的数据中插入相干链路所需要的训练序列与导频符号,得到第二数据。

193.场景五:第二芯片进行了交织处理,第一芯片进行了外码交织,未进行内码交织,且第一芯片进行了频点调整及ts/pilot插入。

194.该场景五可以为图2所示实施例中获取第一数据的方式二与获取第二数据的方式二的组合,也即第二芯片进行了交织处理,第一芯片仅对第一码字进行了交织处理,未对第

二码字进行交织处理。该场景的实施环境可如图17所示,数据传输的过程如下。

195.第二芯片对原始数据进行外码编码,也即采用fec1(第一fec码型)编码,并对编码后的数据进行外码交织,将交织后的数据流进行pma分发,得到多个第一子数据,再通过aui将多个第一子数据发送到第一芯片,该多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据。第一芯片接收到多个第一子数据后,对多个第一子数据进行am锁定和去偏斜,从而实现对齐操作,然后通过解交织得到多个第一码字。之后,第一芯片对多个第一码字进行交织处理也即外码交织,得到第一数据。

196.进一步地,第一芯片按照第二fec码型对第一数据进行编码,得到多个第二码字后,第一芯片按照数据调制所需的符号对多个第二码字进行分组,将分组后的数据分发到对应的数据通道中;基于每个数据通道中的数据得到第二数据。

197.其中,场景五中,基于每个数据通道中的数据得到第二数据,包括:对每个数据通道中的数据插入相干链路所需要的训练序列与导频符号,得到处理后的数据,在处理后的数据中插入用于调整频点的数据,得到第二数据。

198.或者,基于每个数据通道中的数据得到第二数据,包括:在每个数据通道中的数据中插入用于调整频点的数据,得到处理后的数据,在处理后的数据中插入相干链路所需要的训练序列与导频符号,得到第二数据。

199.场景六:第二芯片进行了交织处理,第一芯片未进行外码交织,但进行了内码交织,且第一芯片进行了频点调整及ts/pilot插入。

200.该场景六可以为图2所示实施例中获取第一数据的方式二与获取第二数据的方式一的组合,也即第二芯片进行了交织处理,第一芯片未对第一码字进行了交织处理,但对第二码字进行交织处理。该场景的实施环境可如图18所示,数据传输的过程如下。

201.第二芯片对原始数据进行外码编码,也即采用fec1(第一fec码型)编码,并对编码后的数据进行外码交织,将交织后的数据流进行pma分发,得到多个第一子数据,再通过aui将多个第一子数据发送到第一芯片,该多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据。第一芯片接收到多个第一子数据后,对多个第一子数据进行am锁定和去偏斜,从而实现对齐操作,然后通过解交织得到多个第一码字。之后,第一芯片对多个第一码字进行交织处理也即外码交织,得到第一数据。

202.进一步地,第一芯片按照第二fec码型对第一数据进行编码,得到多个第二码字后,第一芯片对多个第二码字进行交织处理,按照数据调制所需的符号对交织结果进行分组,将分组后的数据分发到对应的数据通道中;基于每个数据通道中的数据得到第二数据。

203.其中,场景六中,基于每个数据通道中的数据得到第二数据,包括:对每个数据通道中的数据插入相干链路所需要的训练序列与导频符号,得到处理后的数据,在处理后的数据中插入用于调整频点的数据,得到第二数据。

204.或者,基于每个数据通道中的数据得到第二数据,包括:在每个数据通道中的数据中插入用于调整频点的数据,得到处理后的数据,在处理后的数据中插入相干链路所需要的训练序列与导频符号,得到第二数据。

205.场景七:第二芯片进行了交织处理,第一芯片未进行外码交织,也未进行内码交织,但第一芯片进行了频点调整及ts/pilot插入。

206.该场景七可以为图2所示实施例中获取第一数据的方式三与获取第二数据的方式

二的组合,也即第二芯片进行了交织处理,第一芯片未对第一码字进行了交织处理,但对第二码字进行交织处理。该场景的实施环境可如图18所示,数据传输的过程如下。

207.第二芯片对原始数据进行外码编码,也即采用fec1(第一fec码型)编码,并对编码后的数据进行外码交织,将交织后的数据流进行pma分发,得到多个第一子数据,再通过aui将多个第一子数据发送到第一芯片,该多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据。第一芯片接收到多个第一子数据后,对多个第一子数据进行am锁定,从而实现对齐操作,然后通过解交织得到第一数据。

208.进一步地,第一芯片按照第二fec码型对第一数据进行编码,得到多个第二码字后,第一芯片按照数据调制所需的符号对多个第二码字进行分组,将分组后的数据分发到对应的数据通道中;基于每个数据通道中的数据得到第二数据。

209.其中,场景七中,基于每个数据通道中的数据得到第二数据,包括:对每个数据通道中的数据插入相干链路所需要的训练序列与导频符号,得到处理后的数据,在处理后的数据中插入用于调整频点的数据,得到第二数据。

210.或者,基于每个数据通道中的数据得到第二数据,包括:在每个数据通道中的数据中插入用于调整频点的数据,得到处理后的数据,在处理后的数据中插入相干链路所需要的训练序列与导频符号,得到第二数据。

211.需要说明的一点是,上述场景一至场景七对应的图13-图19中,外码编码(fec1)可在pcs内部实现,也可独立在pcs外由单独的编码模块实现,本技术实施例对此不进行限定。

212.需要说明的另一点是,本技术实施例中的ts/pilot可以理解为ts和/或pilot。

213.以上以第一模块为例,对数据传输的方法进行了说明,接下来,以第一模块发送第二数据之后,对数据传输的过程进行说明。如图20所示,该数据传输的方法包括如下几个步骤。

214.2001,第三模块获取第二数据,第二数据为采用第二fec码型对第一数据进行编码及进行第二处理得到的数据,第一数据为采用第一fec码型编码且经过第一处理的数据,第一处理包括交织处理。

215.结合图1所示的实施环境,第三模块获取第一模块发送的第二数据。结合图2所示的实施例,第一模块得到第二数据的方式有多种,本技术实施例在此不再一一赘述,可参见上述图2所示实施例的内容。针对第一模块对第二数据进行分发,得到多个第三子数据,通过多条逻辑通道发送多个第三子数据的情况,第三模块获取第二数据包括:第三模块接收多个第三子数据,基于多个第三子数据恢复得到第二数据。

216.2002,第三模块按照第二fec码型对第二数据进行解码,得到解码后的数据。

217.由于第一模块获取第二数据的方式有多种,因而第二数据的情况也有多种,针对第二数据的不同情况,第三模块可采用不同的情况进行处理,包括但不限于按照第二fec码型对第二数据进行解码,得到解码后的数据。

218.之后,第三模块还可以对解码后的数据进行进一步的处理,本技术实施例不对第三模块对第二数据的处理方式进行限定。例如,将解码后的数据继续向其他模块发送。或者,第二数据是经过外码交织和内码交织之后得到的数据,则第三模块按照第二fec码型对第二数据进行解码之前,先对第二数据进行解交织,得到第二码字,再用第二fec码型对第二码字进行解码,得到解码后的数据之后,对解码后的数据再次进行解交织,得到第一码

字。

219.另外,第三模块可以位于第三芯片中,第一模块位于第一芯片中,第三模块接收第一模块通过aui发送的第二数据。

220.本技术实施例还提供了一种数据传输的装置。图21是本技术实施例提供的一种数据传输的装置的结构示意图。基于图21所示的如下多个单元,该图21所示的数据传输的装置能够执行第一模块所执行的全部或部分操作。应理解到,该装置可以包括比所示单元更多的附加单元或者省略其中所示的一部分单元,本技术实施例对此并不进行限制。如图21所示,该装置包括:

221.获取单元2101,用于获取第一数据,第一数据为采用第一前向纠错码fec码型编码且经过第一处理的数据,第一处理包括交织处理;

222.编码单元2102,用于按照第二fec码型对第一数据进行编码,得到多个第二码字;

223.处理单元2103,用于对多个码字进行第二处理,得到第二数据;

224.传输单元2104,用于传输第二数据。

225.在一种可能的实施方式中,第二处理包括插入相干链路所需要的训练序列与导频符号中的至少一种。

226.在一种可能的实施方式中,第一处理和第二处理中的至少一个还包括插入用于调整频点的数据。

227.在一种可能的实施方式中,获取单元2101,用于接收第二模块发送的多个第一子数据,多个第一子数据为采用第一fec码型编码且经过物理介质接入子层pma分发的数据;对多个第一子数据进行对齐,得到多个第一码字;对多个第一码字进行交织处理,得到第一数据。

228.在一种可能的实施方式中,获取单元2101,用于接收第二模块发送的多个第一子数据,多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据;对多个第一子数据进行对齐,得到多个第一码字;对多个第一码字进行交织处理,得到第一数据。

229.在一种可能的实施方式中,获取单元2101,用于对多个第一子数据进行对齐,将对齐后的数据进行解交织,根据解交织的结果得到多个第一码字;或者,对多个第一子数据进行对齐,将对齐后的数据作为多个第一码字。

230.在一种可能的实施方式中,获取单元2101,用于接收第二模块发送的多个第一子数据,多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据;对多个第一子数据进行对齐,得到第一数据。

231.在一种可能的实施方式中,第一模块位于第一芯片,第二模块位于第二芯片,获取单元2101,用于接收第二模块通过一个附件单元接口aui的多个通道发送的多个第一子数据。

232.在一种可能的实施方式中,第一模块位于第一芯片,获取单元2101,用于接收第二模块通过一个附件单元接口aui的一个通道发送的多个第一子数据,第二模块位于第二芯片,多个第一子数据为采用第一fec码型编码且经过物理介质接入子层pma分发的数据,或者,多个第一子数据为采用第一fec码型编码且经过交织处理及pma分发的数据;对多个第一子数据进行对齐标志am锁定,得到多个第一码字;对多个第一码字进行交织处理,得到第

一数据。

233.在一种可能的实施方式中,多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据,获取单元2101,用于对多个第一子数据进行am锁定,将am锁定后的数据进行解交织,根据解交织的结果得到多个第一码字;或者,对多个第一子数据进行am锁定,将am锁定后的数据作为多个第一码字。

234.在一种可能的实施方式中,第一模块位于第一芯片,获取单元2101,用于接收第二模块通过一个附件单元接口aui的一个通道发送的多个第一子数据,第二模块位于第二芯片,多个第一子数据为采用第一fec码型编码且经过交织处理及物理介质接入子层pma分发的数据;对多个第一子数据进行对齐标志am锁定,将am锁定后的数据作为第一数据。

235.在一种可能的实施方式中,处理单元2103,用于对多个第二码字进行交织处理,按照数据调制所需的符号或者至少一个比特对交织结果进行分组,将分组后的数据分发到对应的数据通道中;基于每个数据通道中的数据得到第二数据。

236.在一种可能的实施方式中,处理单元2103,用于按照数据调制所需的符号或者至少一个比特对多个第二码字进行分组,将分组后的数据分发到对应的数据通道中;基于每个数据通道中的数据得到第二数据。

237.在一种可能的实施方式中,处理单元2103,用于对每个数据通道中的数据插入相干链路所需要的训练序列与导频符号,得到处理后的数据,在处理后的数据中插入用于调整频点的数据,得到第二数据。

238.在一种可能的实施方式中,处理单元2103,用于在每个数据通道中的数据中插入用于调整频点的数据,得到处理后的数据,在处理后的数据中插入相干链路所需要的训练序列与导频符号,得到第二数据。

239.在一种可能的实施方式中,获取单元2101,用于对多个第一码字进行直接交织,交织码字个数为参与交织的码字个数;或者,以参考间隔对多个第一码字进行错位交织,交织码字个数为参与交织的码字个数,参考间隔为两个码字之间错位的码块数量;或者,对多个第一码字进行卷积交织,交织码字个数为参与交织的码字个数。

240.在一种可能的实施方式中,处理单元2103,用于将多个第二码字中来自同一个编码器的第二码字进行交织;或者,将多个第二码字中来自多个编码器的多个第二码字进行交织;或者,将多个第二码字中来自同一个编码器的第二码字进行交织,将交织后获得的来自多个编码器的多个数据流进行再次交织。

241.在一种可能的实施方式中,编码单元2102,用于分发第一数据得到多个第二子数据,按照第二fec码型分别对多个第二子数据进行编码,得到多个第二码字。

242.在一种可能的实施方式中,编码单元2102,用于通过物理编码子层pcs通道分发第一数据得到多个第二子数据;或者,通过物理介质接入子层pma分发第一数据得到多个第二子数据。

243.在一种可能的实施方式中,传输单元2104,用于对第二数据进行分发,得到多个第三子数据,通过多条逻辑通道发送多个第三子数据。

244.图22是本技术实施例提供的一种数据传输的装置的结构示意图。基于图22所示的如下多个单元,该图22所示的数据传输的装置能够执行第三模块所执行的全部或部分操作。应理解到,该装置可以包括比所示单元更多的附加单元或者省略其中所示的一部分单

元,本技术实施例对此并不进行限制。如图22所示,该装置包括:

245.获取单元2201,用于获取第二数据,第二数据为采用第二前向纠错码fec码型对第一数据进行编码及进行第二处理得到的数据,第一数据为采用第一fec码型编码且经过第一处理的数据,第一处理包括交织处理;

246.解码单元2202,用于按照第二fec码型对第二数据进行解码,得到解码后的数据。

247.在一种可能的实施方式中,获取单元2201,用于接收多个第三子数据,基于多个第三子数据恢复出第二数据。

248.应理解的是,上述图21、图22提供的装置在实现其功能时,仅以上述各功能模块的划分进行举例说明,实际应用中,可以根据需要而将上述功能分配由不同的功能单元完成,即将设备的内部结构划分成不同的功能单元,以完成以上描述的全部或者部分功能。另外,上述实施例提供的装置与方法实施例属于同一构思,其具体实现过程详见方法实施例,这里不再赘述。

249.本技术实施例提供了一种数据传输的设备,该设备包括:处理器,该处理器与存储器耦合,该存储器中存储有至少一条程序指令或代码,该至少一条程序指令或代码由该处理器加载并执行,以使该数据传输的设备实现如上述方法实施例中的方法。

250.参见图23,图23示出了本技术一个示例性实施例提供的数据传输的设备1100的结构示意图,该数据传输的设备1100为发送侧/接收侧设备。图23所示的数据传输的设备1100用于执行上述图2所示的数据传输的方法所涉及的操作。该数据传输的设备1100例如是交换机、路由器等网络设备以及其他包含这种芯片级联模式的设备(例如服务器、pc等)。该数据传输的设备1100的硬件结构包括通信接口1101和处理器1102。可选地,通信接口1101和处理器1102之间通过总线1104连接。其中,通信接口1101用于获取第一数据和传输第二数据,处理器可存储有指令或程序代码,通过调用该指令或程序代码来执行上述第一模块所执行的功能,或者第三模块所执行的功能。可选地,该网络设备还包括存储器1103,由存储器1103存放指令或程序代码,处理器1102用于调用存储器1103中的指令或程序代码使得网络设备执行上述方法实施例中第一模块的相关处理步骤。在具体实施例中,本技术实施例的数据传输的设备1100可包括上述各个方法实施例中的第一模块,数据传输的设备1100中的处理器1102读取存储器1103中的指令或程序代码,使图23所示的数据传输的设备1100能够执行第一模块所执行的全部或部分操作。

251.在具体实施例中,本技术实施例的数据传输的设备1100包括上述各个方法实施例中的第三模块,数据传输的设备1100中的处理器1102读取存储器1103中的指令或程序代码,使图23所示的数据传输的设备1100能够执行第三模块所执行的全部或部分操作。

252.示例性地,处理器1102例如是通用中央处理器(central processing unit,cpu)、数字信号处理器(digital signal processor,dsp)、网络处理器(network processer,np)、图形处理器(graphics processing unit,gpu)、神经网络处理器(neural-network processing units,npu)、数据处理单元(data processing unit,dpu)、微处理器或者一个或多个用于实现本技术方案的集成电路。例如,处理器1102包括专用集成电路(application-specific integrated circuit,asic),可编程逻辑器件(programmable logic device,pld)或者其他可编程逻辑器件、晶体管逻辑器件、硬件部件或者其任意组合。pld例如是复杂可编程逻辑器件(complex programmable logic device,cpld)、现场可

编程逻辑门阵列(field-programmable gate array,fpga)、通用阵列逻辑(generic array logic,gal)或其任意组合。其可以实现或执行结合本发明实施例公开内容所描述的各种逻辑方框、模块和电路。处理器也可以是实现计算功能的组合,例如包括一个或多个微处理器组合,dsp和微处理器的组合等等。

253.可选的,数据传输的设备1100还包括总线。总线用于在数据传输的设备1100的各组件之间传送信息。总线可以是外设部件互连标准(peripheral component interconnect,简称pci)总线或扩展工业标准结构(extended industry standard architecture,简称eisa)总线等。总线可以分为地址总线、数据总线、控制总线等。为便于表示,图23中仅用一条粗线表示,但并不表示仅有一根总线或一种类型的总线。图23中数据传输的设备1100的各组件之间除了采用总线连接,还可采用其他方式连接,本发明实施例不对各组件的连接方式进行限定。

254.存储器1103例如是只读存储器(read-only memory,rom)或可存储静态信息和指令的其它类型的静态存储设备,又如是随机存取存储器(random access memory,ram)或者可存储信息和指令的其它类型的动态存储设备,又如是电可擦可编程只读存储器(electrically erasable programmable read-only memory,eeprom)、只读光盘(compact disc read-only memory,cd-rom)或其它光盘存储、光碟存储(包括压缩光碟、激光碟、光碟、数字通用光碟、蓝光光碟等)、磁盘存储介质或者其它磁存储设备,或者是能够用于携带或存储具有指令或数据结构形式的期望的程序代码并能够由计算机存取的任何其它介质,但不限于此。存储器1103例如是独立存在,并通过总线与处理器1102相连接。存储器1103也可以和处理器1102集成在一起。

255.通信接口1101使用任何收发器一类的装置,用于与其它设备或通信网络通信,通信网络可以为以太网、无线接入网(ran)或无线局域网(wireless local area networks,wlan)等。通信接口1101可以包括有线通信接口,还可以包括无线通信接口。具体的,通信接口1101可以为以太(ethernet)接口、快速以太(fast ethernet,fe)接口、千兆以太(gigabit ethernet,ge)接口,异步传输模式(asynchronous transfer mode,atm)接口,无线局域网(wireless local area networks,wlan)接口,蜂窝网络通信接口或其组合。以太网接口可以是光接口,电接口或其组合。在本技术实施例中,通信接口1101可以用于数据传输的设备1100与其他设备进行通信。

256.在具体实现中,作为一种实施例,处理器1102可以包括一个或多个cpu。这些处理器中的每一个可以是一个单核(single-cpu)处理器,也可以是一个多核(multi-cpu)处理器。这里的处理器可以指一个或多个设备、电路、和/或用于处理数据(例如计算机程序指令)的处理核。

257.在具体实现中,作为一种实施例,数据传输的设备1100可以包括多个处理器。这些处理器中的每一个可以是一个单核处理器(single-cpu),也可以是一个多核处理器(multi-cpu)。这里的处理器可以指一个或多个设备、电路、和/或用于处理数据(如计算机程序指令)的处理核。

258.在具体实现中,作为一种实施例,数据传输的设备1100还可以包括输出设备和输入设备。输出设备和处理器1102通信,可以以多种方式来显示信息。例如,输出设备可以是液晶显示器(liquid crystal display,lcd)、发光二级管(light emitting diode,led)显

示设备、阴极射线管(cathode ray tube,crt)显示设备或投影仪(projector)等。输入设备和处理器1102通信,可以以多种方式接收用户的输入。例如,输入设备可以是鼠标、键盘、触摸屏设备或传感设备等。

259.在一些实施例中,存储器1103用于存储执行本技术方案的程序代码,处理器1102可以执行存储器1103中存储的程序代码。也即是,数据传输的设备1100可以通过处理器1102以及存储器1103中的程序代码,来实现方法实施例提供的数据传输的方法。程序代码中可以包括一个或多个软件模块。可选地,处理器1102自身也可以存储执行本技术方案的程序代码或指令。

260.在具体实施例中,本技术实施例的数据传输的设备1100可包括上述各个方法实施例中的第一芯片,数据传输的设备1100中的处理器1102读取存储器1103中的程序代码或处理器1102自身存储的程序代码或指令,使图23所示的数据传输的设备1100能够执行第一网络设备所执行的全部或部分操作。

261.在具体实施例中,本技术实施例的数据传输的设备1100可包括上述各个方法实施例中的第三模块,数据传输的设备1100中的处理器1102读取存储器1103中的程序代码或处理器1102自身存储的程序代码或指令,使图23所示的数据传输的设备1100能够执行第三模块所执行的全部或部分操作。

262.数据传输的设备1100还可以对应于上述图21、22所示的装置,图21、22所示的装置中的每个功能单元采用数据传输的设备1100的软件实现。换句话说,图21、22所示的装置包括的功能单元为数据传输的设备1100的处理器1102读取存储器1103中存储的程序代码后生成的。

263.其中,图2所示的数据传输的方法的各步骤通过数据传输的设备1100的处理器中的硬件的集成逻辑电路或者软件形式的指令完成。结合本技术实施例所公开的方法的步骤可以直接体现为硬件处理器执行完成,或者用处理器中的硬件及软件模块组合执行完成。软件模块可以位于随机存储器,闪存、只读存储器,可编程只读存储器或者电可擦写可编程存储器、寄存器等本领域成熟的存储介质中。该存储介质位于存储器,处理器读取存储器中的信息,结合其硬件完成上述方法的步骤,为避免重复,这里不再详细描述。

264.本技术实施例还提供了一种数据传输的系统,该系统包括:第一数据传输的设备和第二数据传输的设备;第一数据传输的设备用于执行图2所示的第一模块所执行的方法,第二数据传输的设备用于执行图2所示的第三模块所执行的方法。

265.该系统的第一数据传输的设备和第二数据传输的设备各自的功能可参考上述图2所示的相关描述,此处不再一一赘述。

266.应理解的是,上述处理器可以是中央处理器(central processing unit,cpu),还可以是其他通用处理器、数字信号处理器(digital signal processing,dsp)、专用集成电路(application specific integrated circuit,asic)、现场可编程门阵列(field-programmable gate array,fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件等。通用处理器可以是微处理器或者是任何常规的处理器等。值得说明的是,处理器可以是支持进阶精简指令集机器(advanced risc machines,arm)架构的处理器。

267.进一步地,在一种可选的实施例中,上述存储器可以包括只读存储器和随机存取存储器,并向处理器提供指令和数据。存储器还可以包括非易失性随机存取存储器。例如,

存储器还可以存储设备类型的信息。

268.该存储器可以是易失性存储器或非易失性存储器,或可包括易失性和非易失性存储器两者。其中,非易失性存储器可以是只读存储器(read-only memory,rom)、可编程只读存储器(programmable rom,prom)、可擦除可编程只读存储器(erasable prom,eprom)、电可擦除可编程只读存储器(electrically eprom,eeprom)或闪存。易失性存储器可以是随机存取存储器(random access memory,ram),其用作外部高速缓存。通过示例性但不是限制性说明,许多形式的ram可用。例如,静态随机存取存储器(static ram,sram)、动态随机存取存储器(dynamic random access memory,dram)、同步动态随机存取存储器(synchronous dram,sdram)、双倍数据速率同步动态随机存取存储器(double data date sdram,ddr sdram)、增强型同步动态随机存取存储器(enhanced sdram,esdram)、同步连接动态随机存取存储器(synchlink dram,sldram)和直接内存总线随机存取存储器(direct rambus ram,dr ram)。

269.还提供了一种计算机可读存储介质,存储介质中存储有至少一条程序指令或代码,程序指令或代码由处理器加载并执行时以使计算机实现如上图2所示的数据传输的方法。

270.本技术提供了一种计算机程序,当计算机程序被计算机执行时,可以使得处理器或计算机执行上述方法实施例中对应的各个步骤和/或流程。

271.提供了一种芯片,包括处理器,用于从存储器中调用并运行所述存储器中存储的指令,使得安装有所述芯片的设备执行上述各方面中的方法。

272.提供另一种芯片,包括:输入接口、输出接口、处理器和存储器,所述输入接口、输出接口、所述处理器以及所述存储器之间通过内部连接通路相连,所述处理器用于执行所述存储器中的代码,当所述代码被执行时,所述处理器用于执行上述各方面中的方法。

273.提供一种设备,包括上述方案中任一所述的芯片。

274.提供一种设备,包括上述方案中任一所述的第一芯片,和/或,上述方案中任一所述的第三芯片。

275.在一些实施例中,图13-19中,第二芯片可以是发送侧设备,比如路由器、交换机、服务器中的物理层(phy)芯片,第一芯片可以是接收侧设备的接口,比如光模块中的芯片或者cdr/retimer芯片。第三芯片可以是接收侧设备的接口,比如光模块中的芯片或者cdr/retimer芯片。所述phy芯片可以是位于计算设备的单板上的芯片,该芯片可以是cpu、网络处理器(network processor,np)、神经网络处理单元(neural network processing unit,npu)、现场可编程逻辑门阵列(field programmable gate array,fpga)、可编程逻辑控制器(programmable logic controller,plc)等中的一个或其任意组合。

276.在一些实施例中,第一芯片和第二芯片之间通过aui通信;在一些实施例中,第三芯片和第一芯片之间通过aui通信。

277.在上述实施例中,可以全部或部分地通过软件、硬件、固件或者其任意组合来实现。当使用软件实现时,可以全部或部分地以计算机程序产品的形式实现。所述计算机程序产品包括一个或多个计算机指令。在计算机上加载和执行所述计算机程序指令时,全部或部分地产生按照本技术所述的流程或功能。所述计算机可以是通用计算机、专用计算机、计算机网络、或者其他可编程装置。所述计算机指令可以存储在计算机可读存储介质中,或者

从一个计算机可读存储介质向另一个计算机可读存储介质传输,例如,所述计算机指令可以从一个网站站点、计算机、服务器或数据中心通过有线(例如同轴电缆、光纤、数字用户线)或无线(例如红外、无线、微波等)方式向另一个网站站点、计算机、服务器或数据中心进行传输。所述计算机可读存储介质可以是计算机能够存取的任何可用介质或者是包含一个或多个可用介质集成的服务器、数据中心等数据存储设备。所述可用介质可以是磁性介质,(例如,软盘、硬盘、磁带)、光介质(例如,dvd)、或者半导体介质(例如固态硬盘,solid state disk)等。

278.以上所述的具体实施方式,对本技术的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本技术的具体实施方式而已,并不用于限定本技术的保护范围,凡在本技术的技术方案的基础之上,所做的任何修改、等同替换、改进等,均应包括在本技术的保护范围之内。

279.本领域普通技术人员可以意识到,结合本文中所公开的实施例中描述的各方法步骤和模块,能够以软件、硬件、固件或者其任意组合来实现,为了清楚地说明硬件和软件的可互换性,在上述说明中已经按照功能一般性地描述了各实施例的步骤及组成。这些功能究竟以硬件还是软件方式来执行,取决于技术方案的特定应用和设计约束条件。本领域普通技术人员可以对每个特定的应用来使用不同方法来实现所描述的功能,但是这种实现不应认为超出本技术的范围。

280.本领域普通技术人员可以理解实现上述实施例的全部或部分步骤可以通过硬件来完成,也可以通过程序来指令相关的硬件完成,该程序可以存储于一种计算机可读存储介质中,上述提到的存储介质可以是只读存储器,磁盘或光盘等。

281.当使用软件实现时,可以全部或部分地以计算机程序产品的形式实现。该计算机程序产品包括一个或多个计算机程序指令。作为示例,本技术实施例的方法可以在机器可执行指令的上下文中被描述,机器可执行指令诸如包括在目标的真实或者虚拟处理器上的器件中执行的程序模块中。一般而言,程序模块包括例程、程序、库、对象、类、组件、数据结构等,其执行特定的任务或者实现特定的抽象数据结构。在各实施例中,程序模块的功能可以在所描述的程序模块之间合并或者分割。用于程序模块的机器可执行指令可以在本地或者分布式设备内执行。在分布式设备中,程序模块可以位于本地和远程存储介质二者中。

282.用于实现本技术实施例的方法的计算机程序代码可以用一种或多种编程语言编写。这些计算机程序代码可以提供给通用计算机、专用计算机或其他可编程的数据处理装置的处理器,使得程序代码在被计算机或其他可编程的数据处理装置执行的时候,引起在流程图和/或框图中规定的功能/操作被实施。程序代码可以完全在计算机上、部分在计算机上、作为独立的软件包、部分在计算机上且部分在远程计算机上或完全在远程计算机或服务器上执行。

283.在本技术实施例的上下文中,计算机程序代码或者相关数据可以由任意适当载体承载,以使得设备、装置或者处理器能够执行上文描述的各种处理和操作。载体的示例包括信号、计算机可读介质等等。

284.信号的示例可以包括电、光、无线电、声音或其它形式的传播信号,诸如载波、红外信号等。

285.机器可读介质可以是包含或存储用于或有关于指令执行系统、装置或设备的程序

的任何有形介质。机器可读介质可以是机器可读信号介质或机器可读存储介质。机器可读介质可以包括但不限于电子的、磁的、光学的、电磁的、红外的或半导体系统、装置或设备,或其任意合适的组合。机器可读存储介质的更详细示例包括带有一根或多根导线的电气连接、便携式计算机磁盘、硬盘、随机存储存取器(ram)、只读存储器(rom)、可擦除可编程只读存储器(eprom或闪存)、光存储设备、磁存储设备,或其任意合适的组合。

286.所属领域的技术人员可以清楚地了解到,为了描述的方便和简洁,上述描述的系统、设备和模块的具体工作过程,可以参见前述方法实施例中的对应过程,在此不再赘述。

287.在本技术所提供的几个实施例中,应该理解到,所揭露的系统、设备和方法,可以通过其它的方式实现。例如,以上所描述的设备实施例仅仅是示意性的,例如,该模块的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个模块或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另外,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口、设备或模块的间接耦合或通信连接,也可以是电的,机械的或其它的形式连接。

288.该作为分离部件说明的模块可以是或者也可以不是物理上分开的,作为模块显示的部件可以是或者也可以不是物理模块,即可以位于一个地方,或者也可以分布到多个网络模块上。可以根据实际的需要选择其中的部分或者全部模块来实现本技术实施例方案的目的。

289.另外,在本技术各个实施例中的各功能模块可以集成在一个处理模块中,也可以是各个模块单独物理存在,也可以是两个或两个以上模块集成在一个模块中。上述集成的模块既可以采用硬件的形式实现,也可以采用软件功能模块的形式实现。

290.该集成的模块如果以软件功能模块的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读存储介质中。基于这样的理解,本技术的技术方案本质上或者说对现有技术做出贡献的部分,或者该技术方案的全部或部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本技术各个实施例中方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、只读存储器(read-only memory,rom)、随机存取存储器(random access memory,ram)、磁碟或者光盘等各种可以存储程序代码的介质。

291.本技术中术语“第一”“第二”等字样用于对作用和功能基本相同的相同项或相似项进行区分,应理解,“第一”、“第二”、“第n”之间不具有逻辑或时序上的依赖关系,也不对数量和执行顺序进行限定。还应理解,尽管以下描述使用术语第一、第二等来描述各种元素,但这些元素不应受术语的限制。这些术语只是用于将一元素与另一元素区别分开。例如,在不脱离各种所述示例的范围的情况下,第一网络设备可以被称为第二网络设备,并且类似地,第二网络设备可以被称为第一网络设备。第一网络和设备和第二网络设备都可以是网络设备,并且在某些情况下,可以是单独且不同的网络设备。

292.还应理解,在本技术的各个实施例中,各个过程的序号的大小并不意味着执行顺序的先后,各过程的执行顺序应以其功能和内在逻辑确定,而不应对本技术实施例的实施过程构成任何限定。

293.本技术中术语“至少一个”的含义是指一个或多个,本技术中术语“多个”的含义是

指两个或两个以上,例如,多个第二报文是指两个或两个以上的第二报文。本文中术语“系统”和“网络”经常可互换使用。

294.应理解,在本文中对各种所述示例的描述中所使用的术语只是为了描述特定示例,而并非旨在进行限制。如在对各种所述示例的描述和所附权利要求书中所使用的那样,单数形式“一个(“a”,“an”)”和“该”旨在也包括复数形式,除非上下文另外明确地指示。

295.还应理解,术语“包括”(也称“includes”、“including”、“comprises”和/或“comprising”)当在本说明书中使用时指定存在所陈述的特征、整数、步骤、操作、元素、和/或部件,但是并不排除存在或添加一个或多个其他特征、整数、步骤、操作、元素、部件、和/或其分组。

296.还应理解,术语“若”和“如果”可被解释为意指“当...时”(“when”或“upon”)或“响应于确定”或“响应于检测到”。类似地,根据上下文,短语“若确定...”或“若检测到[所陈述的条件或事件]”可被解释为意指“在确定...时”或“响应于确定...”或“在检测到[所陈述的条件或事件]时”或“响应于检测到[所陈述的条件或事件]”。

[0297]

应理解,根据a确定b并不意味着仅仅根据a确定b,还可以根据a和/或其它信息确定b。

[0298]

还应理解,说明书通篇中提到的“一个实施例”、“一实施例”、“一种可能的实现方式”意味着与实施例或实现方式有关的特定特征、结构或特性包括在本技术的至少一个实施例中。因此,在整个说明书各处出现的“在一个实施例中”或“在一实施例中”、“一种可能的实现方式”未必一定指相同的实施例。此外,这些特定的特征、结构或特性可以任意适合的方式结合在一个或多个实施例中。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。