1.本公开涉及一种半导体封装件。更具体地说,本公开涉及利用应力松弛焊盘(边缘焊盘)减小钝化膜的热应力。

背景技术:

2.由于对高规格套件的需求和高带宽存储器(hbm)的采用,插入件市场正在增长。例如,在使用硅基插入件的半导体封装件的情况下,可以通过在硅基插入件上表面安装半导体芯片,并通过使用模制材料将安装的半导体芯片模制来制造半导体封装件。

3.另一方面,由于近年来套件的高规格,高带宽存储器的数量增加了,半导体封装件的尺寸也扩大了。这导致热膨胀系数(cte)差异导致的应力增加、增加半导体封装件的工艺难度、以及降低成品率的问题。

技术实现要素:

4.本公开的各方面提供了一种能够提高性能和可靠性的半导体封装件。

5.然而,本公开的各方面不限于本文阐述的这些。通过参照下面提供的本公开的具体实施方式,本公开的上面和其它方面将对于本公开所属领域的普通技术人员之一变得更清楚。

6.根据本公开的一方面,提供了一种半导体封装件,该半导体封装件包括:彼此电连接的第一装置和第二装置,其中第一装置包括衬底、形成在衬底的上侧的第一焊盘以及形成在衬底的上侧并且形成为包围第一焊盘的钝化膜,第二装置包括布置为面对第一焊盘的第二焊盘,并且第一焊盘包括具有第一弹性模量的中心焊盘和具有小于第一弹性模量的第二弹性模量的边缘焊盘,边缘焊盘形成为包围中心焊盘和接触钝化膜。

7.根据本公开的另一方面,提供了一种半导体封装件,该半导体封装件包括:插入件衬底;以及半导体芯片,其安装在插入件衬底上,并且电连接至插入件衬底,其中,插入件衬底包括:插入件;钝化膜,其接触插入件的上侧;插入件焊盘,其穿过钝化膜并且电连接至插入件内部的再分布层;以及应力松弛焊盘,其穿过钝化膜并且包围插入件焊盘,并且其中,插入件焊盘的上侧与应力松弛焊盘的上侧位于相同平面上。

8.根据本公开的另一方面,提供了一种半导体封装件,该半导体封装件包括:电路板;电路板上的插入件衬底;以及安装在插入件衬底上并且电连接至插入件衬底的逻辑半导体芯片和存储器半导体芯片,其中,插入件衬底包括:插入件,插入件焊盘,其置于插入件的上侧并且包括导电材料,应力松弛焊盘,其置于插入件的上侧、包围插入件焊盘的周边、并且包括绝缘材料,以及钝化膜,其在插入件的上侧上包围应力松弛焊盘的周边,其中,应力松弛焊盘的宽度为1μm或更大且10μm或更小。

附图说明

9.本公开的以上和其它方面和特征将通过参照附图详细描述其示例性实施例而变

得更清楚,在附图中:

10.图1是用于解释根据一些实施例的半导体封装件的示例性示图。

11.图2是示出图1的边缘焊盘的宽度与钝化膜的热应力之间的关系的图表。

12.图3至图6是用于解释根据一些实施例的半导体封装件的示例性示图。

13.图7至图10是用于解释根据一些实施例的边缘焊盘的示例性平面图。

14.图11是用于解释根据一些实施例的半导体封装件的示意性布局图。

15.图12是沿着图11的a-a截取的截面图。

16.图13是用于解释图12的区p的放大图。

17.图14是用于解释根据一些实施例的半导体封装件的示图。

18.图15是用于解释图14的区域q的放大图。

19.图16是用于解释根据一些实施例的半导体封装件的示图。

20.图17是用于解释图16的区域r的放大图。

21.图18是用于解释根据一些实施例的半导体封装件的示图。

22.图19是用于解释图18的区域s的放大图。

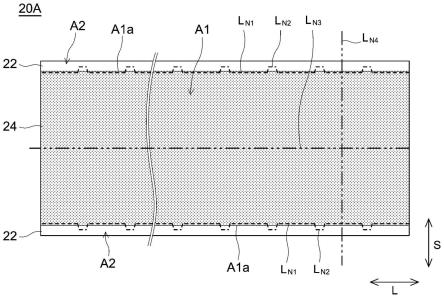

23.图20是根据一些实施例的半导体封装件的示例性布局图。

24.图21是根据一些实施例的半导体封装件的示例性布局图。

25.图22是根据一些实施例的半导体封装件的示例性布局图。

26.图23是沿着图22的线b-b截取的截面图。

具体实施方式

27.下文中,将参照图1至图23描述根据一些实施例的半导体封装件。

28.图1是用于解释根据一些实施例的半导体封装件的示例性示图。图2是示出图1的边缘焊盘的宽度与钝化膜的热应力之间的关系的图表。

29.参照图1和图2,根据一些实施例的半导体封装件可包括第一装置10和第二装置20。

30.第一装置10和第二装置20可彼此电连接。例如,第一装置10和第二装置20可通过第一焊盘13、第二焊盘23和焊料凸块35彼此电连接。例如,第一装置10和第二装置20中的每一个可为电路板、插入件、逻辑半导体芯片或者存储器半导体芯片。

31.如本文所用,被描述为“电连接”的组件被配置为使得电信号可从一个组件传递至另一组件(但是该电信号可在传递时强度衰减,且可选择性传递)。

32.第一装置10可包括衬底11、钝化膜12、第一焊盘13和再分布层/图案14。虽然未示出,但是第一装置10可包括绝缘层,并且还可包括穿通电极。

33.例如,衬底11可包括或者可为硅基插入件、电路板、逻辑半导体芯片和存储器半导体芯片中的至少一种。在本说明书中,衬底11将被描述为包括硅基插入件。

34.第一焊盘13可形成在衬底11上。第一焊盘13可置于衬底11的上侧(顶/上表面)11_us上。第一焊盘13可接触衬底11的上侧11_us。

35.将理解,当元件被称作“连接”或“耦接”至另一元件上,或者“在”另一元件“上”时,其可直接连接至或耦接至另一元件,或在另一元件上,或者可存在中间元件。相反,当元件被称作“直接连接”或“直接耦接”至另一元件,或者“接触”另一元件时,在接触点不存在中

间元件。

36.第二焊盘23可布置为面对第一焊盘13。第一装置10和第二装置20可利用第一焊盘13和第二焊盘23彼此电连接。第二焊盘23可例如包括(但不限于)诸如铜(cu)或铝(al)的金属材料或者由该金属材料形成。第一焊盘13的含量将在稍后描述。

37.在一些实施例中,第一焊盘13可包括中心焊盘13c和边缘焊盘13e。边缘焊盘13e可形成为包围中心焊盘13c。中心焊盘13c可包括导电材料或由导电材料形成。例如,中心焊盘13c可包括(但不限于)诸如铜(cu)或铝(al)的金属材料或由该金属材料形成。

38.边缘焊盘13e可包括绝缘材料或由绝缘材料形成。边缘焊盘13e可包括基于氧化物的绝缘材料或由基于氧化物的绝缘材料形成。例如,边缘焊盘13e可由(但不限于)正硅酸乙酯(teos)或光敏聚酰亚胺(pspi)形成。边缘焊盘13e可由能够减轻稍后将描述的钝化膜12的热应力的材料形成。

39.边缘焊盘13e可在第一方向x上具有宽度w1。边缘焊盘13e的宽度w1可为1μm或更大且20μm或更小。例如,边缘焊盘13e的宽度w1可为1μm或更大且10μm或更小。例如,边缘焊盘13e的宽度w1可为5μm或更大且10μm或更小。

40.边缘焊盘13e可与焊料凸块35竖直地重叠。例如,边缘焊盘13e可在第二方向z上与焊料凸块35完全重叠。如本文所用,第一方向x可为水平方向。第二方向z可为竖直方向。第一方向x和第二方向z可彼此垂直。然而,本公开的技术思想不限于此。

41.在图2中,x轴意指/表示边缘焊盘13e在第一方向x上的宽度。y轴意指/表示钝化膜12的热应力。例如,边缘焊盘13e的宽度可为从边缘焊盘13e的接触中心焊盘13c的表面至边缘焊盘13e的位于在从中心焊盘13c的中心远离的方向上并接触钝化膜12的表面的距离。

42.当未形成边缘焊盘13e时,例如,当边缘焊盘13e的宽度为0μm时,将钝化膜12的热应力定义为1。

43.当边缘焊盘13e的宽度w1为1μm时,钝化膜12的热应力为0.92。与不形成边缘焊盘13e的情况(当边缘焊盘13e的宽度为0μm时)相比,当边缘焊盘13e的宽度w1为1μm时,钝化膜12的热应力可减小约8%。

44.当边缘焊盘13e的宽度w1为5μm时,钝化膜12的热应力为0.82。与不形成边缘焊盘13e的情况(当边缘焊盘13e的宽度为0μm时)相比,当边缘焊盘13e的宽度w1为5μm时,钝化膜12的热应力可减小约18%。

45.当边缘焊盘13e的宽度w1为10μm时,钝化膜12的热应力为0.64。与不形成边缘焊盘13e的情况(当边缘焊盘13e的宽度为0μm时)相比,当边缘焊盘13e的宽度w1为10μm时,钝化膜12的热应力可减小约36%。

46.当边缘焊盘13e的宽度w1为15μm时,钝化膜12的热应力为0.6。与不形成边缘焊盘13e的情况(当边缘焊盘13e的宽度为0μm时)相比,当边缘焊盘13e的宽度w1为15μm时,钝化膜12的热应力可减小约40%。

47.当边缘焊盘13e的宽度w1为20μm时,钝化膜12的热应力为0.58。与不形成边缘焊盘13e的情况(当边缘焊盘13e的宽度为0μm时)相比,当边缘焊盘13e的宽度w1为20μm时,钝化膜12的热应力可减小约42%。

48.中心焊盘13c可具有第一模量。边缘焊盘13e可具有第二模量。术语“模量”是测量固体材料的硬度的机械特性。模量是定义线性弹性材料在单轴变形区域中的应力与应变之

间的关系的弹性模量。通常,具有高模量的材料可为具有高刚度的材料。例如,第一模量和第二模量可为中心焊盘13c和边缘焊盘13e的弹性模量或杨氏模量。

49.在一些实施例中,中心焊盘13c的第一模量可大于边缘焊盘13e的第二模量。例如,中心焊盘13c的刚度可大于边缘焊盘13e的刚度。利用中心焊盘13c的刚度与边缘焊盘13e的刚度之间的差,钝化膜12的热应力可松弛。

50.例如,边缘焊盘13e的第二模量可为(但不限于)大于15gpa且小于117gpa。

51.边缘焊盘13e可使钝化膜12的热应力松弛。边缘焊盘13e的热膨胀系数可为1ppm/k或更大且17ppm/k或更小。例如,边缘焊盘13e可为能够减小钝化膜12的热应力同时热膨胀系数为1ppm/k或更大且17ppm/k或更小的材料。

52.钝化膜12可形成在衬底11上。钝化膜12可置于衬底11的上侧11_us上。钝化膜12可接触衬底11的上侧11_us。钝化膜12可形成为包围第一焊盘13。钝化膜12可接触边缘焊盘13e。钝化膜12可不接触中心焊盘13c。

53.例如,钝化膜12可为(但不限于)氮化硅膜/层。例如,钝化膜12可包括基于氮化物的绝缘材料或由基于氮化物的绝缘材料形成。钝化膜12可由钝化材料、bcb(苯并环丁烯)、聚苯恶唑、聚酰亚胺、环氧树脂、氧化硅、氮化硅或它们的组合制成。

54.在一些实施例中,中心焊盘13c在第二方向z上的高度可与边缘焊盘13e在第二方向z上的高度相同。中心焊盘13c的上侧(顶/上表面)13c_us可与边缘焊盘13e的上侧(顶/上表面)13e_us位于相同平面上。钝化膜12在第二方向z上的高度可与中心焊盘13c和边缘焊盘13e在第二方向z上的高度相同。钝化膜12的上侧(顶/上表面)12_us可与中心焊盘13c的上侧13c_us和边缘焊盘13e的上侧13e_us位于相同平面上。

55.再分布层/图案14可形成在衬底11的内部。再分布层14可电连接至第一焊盘13。再分布层14可电连接至中心焊盘13c。再分布层14可包括导电材料或由导电材料形成。例如,再分布层14可包括(但不限于)铜(cu)、铝(al)、银(ag)、锡(sn)、金(au)、镍(ni)、铅(pb)、钛(ti)和它们的合金中的至少一种或由铜(cu)、铝(al)、银(ag)、锡(sn)、金(au)、镍(ni)、铅(pb)、钛(ti)和它们的合金中的至少一种形成。

56.根据一些实施例的半导体封装件还可包括焊料凸块35和底部填料30。

57.第一装置10和第二装置20可通过焊料凸块35彼此电连接。第一焊盘13和第二焊盘23可通过焊料凸块35彼此电连接。

58.焊料凸块35可将第一装置10和第二装置20电连接。焊料凸块35可包括焊料或由焊料形成。例如,焊料凸块35可包括(但不限于)铅(pb)、锡(sn)、铟(in)、铋(bi)、锑(sb)、银(ag)和它们的合金中的至少一种或由铅(pb)、锡(sn)、铟(in)、铋(bi)、锑(sb)、银(ag)和它们的合金中的至少一种形成。

59.底部填料30可形成在第一装置10和第二装置20之间。底部填料30可填充第一装置10和第二装置20之间的空间。另外,底部填料30可覆盖焊料凸块35。例如,底部填料30可包围和接触焊料凸块35的侧表面。例如,底部填料30可包括(但不限于)诸如emc(环氧模塑料)的绝缘聚合材料或由该绝缘聚合材料形成。

60.图3至图6是用于解释根据一些实施例的半导体封装件的示例性示图。为了便于解释,将主要描述与利用图1和图2描述的那些不同的点/方面。

61.参照图3所示的实施例,如截面所示,边缘焊盘13e的外侧之间在第一方向x上的宽

度/距离可与焊料凸块35在第一方向x上的宽度相同。边缘焊盘13e的外侧可为与钝化膜12接触的部分。在这种情况下,边缘焊盘13e在第二方向z上与焊料凸块35完全重叠。

62.参照图4所示的实施例,如截面所示,边缘焊盘13e的外侧之间在第一方向x上的宽度可大于焊料凸块35在第一方向x上的宽度。

63.例如,边缘焊盘13e可包括在第二方向z上不与焊料凸块35重叠的部分。

64.参照图5所示的实施例,从截面看,边缘焊盘13e可不对称。

65.边缘焊盘13e可包括第一边缘焊盘13e1和第二边缘焊盘13e2。第一边缘焊盘13e1和第二边缘焊盘13e2可分别置于中心焊盘13c的一侧和另一侧上。

66.第一边缘焊盘13e1在第一方向x上的宽度w2可与第二边缘焊盘13e2在第一方向x上的宽度w3不同。虽然第一边缘焊盘13e1在第一方向x上的宽度w2示为大于第二边缘焊盘13e2在第一方向x上的宽度w3,但是实施例不限于此。在一些实施例中,第二边缘焊盘13e2在第一方向x上的宽度w3可大于第一边缘焊盘13e1在第一方向x上的宽度w2。

67.第一边缘焊盘13e1的一部分在第二方向z上可不与焊料凸块35重叠。第二边缘焊盘13e2在第二方向z上可与焊料凸块35完全重叠。然而,本公开的技术思想不限于此。在一些实施例中,对于第一边缘焊盘13e1和第二边缘焊盘13e2,虽然第一边缘焊盘13e1在第一方向x上的宽度w2与第二边缘焊盘13e2在第一方向x上的宽度w3不同,但是第一边缘焊盘13e1和第二边缘焊盘13e2二者在第二方向z上可与焊料凸块35完全重叠。

68.在一些实施例中,第一边缘焊盘13e1和第二边缘焊盘13e2可具有在第二方向z上不与焊料凸块35重叠的一些部分,同时第一边缘焊盘13e1在第一方向x上的宽度w2与第二边缘焊盘13e2在第一方向x上的宽度w3不同。

69.参照图6,第二焊盘23和第一焊盘13可彼此接触。例如,第二焊盘23和中心焊盘13c可彼此接合。在这种情况下,可不包括焊料凸块35。虽然第二焊盘23和中心焊盘13c在第一方向x上的宽度示为彼此相同,但是实施例不限于此。

70.图7至图10是用于解释根据一些实施例的边缘焊盘的示例性平面图。将利用图7至图10更详细地描述根据一些实施例的边缘焊盘。

71.参照图7至图10,例如,在平面图中,中心焊盘13c可具有圆形。虽然中心焊盘13c在附图中示为按照z字形布置,但是实施例不限于此。

72.边缘焊盘13e可形成在中心焊盘13c周围。边缘焊盘13e可接触中心焊盘13c。边缘焊盘13e可包括内侧13e_a和外侧13e_b。边缘焊盘13e的内侧13e_a可为与中心焊盘13c接触的一侧。边缘焊盘13e的外侧13e_b可与边缘焊盘13e的内侧13e_a相对。边缘焊盘13e的外侧13e_b可接触钝化膜12。边缘焊盘13e可置于中心焊盘13c与钝化膜12之间。再分布层14可与中心焊盘13c重叠。

73.在图7中,例如,在平面图中,边缘焊盘13e的外侧13e_b可具有圆形。在这种情况下,在截面中,边缘焊盘13e的宽度可相同。

74.在图8中,例如,在平面图中,边缘焊盘13e的外侧13e_b可具有方形。在这种情况下,例如,在平面图中,边缘焊盘13e的宽度可根据位置和/或方向而不同。

75.在图9中,例如,在平面图中,边缘焊盘13e的外侧13e_b可具有六边形。在这种情况下,例如,在平面图中,边缘焊盘13e的宽度可根据位置和/或方向而不同。

76.在图10中,例如,在平面图中,边缘焊盘13e的外侧13e_b可具有三角形。在这种情

况下,例如,在平面图中,边缘焊盘13e的宽度可根据位置和/或方向而不同。

77.在本说明书中,虽然边缘焊盘13e的外侧13e_b示为包括圆形、方形、六边形和三角形之一,但是实施例不限于此。例如,在平面图中,边缘焊盘13e的外侧13e_b可具有各种形状。例如,在平面图中,边缘焊盘13e的外侧13e_b可为圆形、四边形、三角形或六边形。

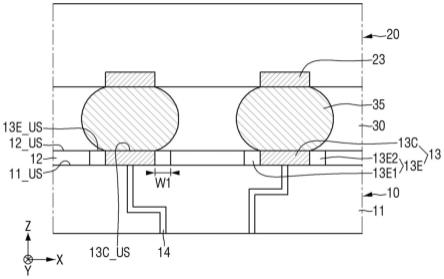

78.图11是用于解释根据一些实施例的半导体封装件的示意性布局图。图12是沿着图11的a-a截取的截面图。图13是用于解释图12的区域p的放大图。下文中,将描述包括利用图1至图10描述的边缘焊盘的半导体封装件。

79.在图11至图13中,根据一些实施例的半导体封装件可为包括硅插入件的2.5d封装件。然而,这仅是示例,并且本公开的技术思想不限于此。

80.参照图11至图13,根据一些实施例的半导体封装件可包括电路板100、插入件结构200、第一半导体芯片310、第二半导体芯片320和模制构件400。

81.插入件结构200可安装在电路板100上。第一半导体芯片310和第二半导体芯片320可安装在插入件结构200上。第一半导体芯片310和第二半导体芯片320可布置为在第一方向x上彼此间隔开。第二半导体芯片320可置于第一半导体芯片310的一侧和另一侧。两个或更多个第二半导体芯片320可在第三方向y上布置。第二半导体芯片320可布置为在第三方向y上彼此间隔开。第三方向y可垂直于第一方向x和第二方向z。

82.电路板100可为封装板。电路板100可为印刷电路板(pcb)。电路板100可包括彼此相对的上侧(例如,顶/上表面)和下侧(例如,底/下表面)。

83.电路板100可包括绝缘核心101、第一板焊盘102和第二板焊盘104。例如,电路板100可包括多个第一板焊盘102和多个第二板焊盘104。第一板焊盘102和第二板焊盘104可用于将电路板100电连接至其它组件。例如,第一板焊盘102可从绝缘核心101的下表面/侧暴露出来,第二板焊盘104可从绝缘核心101的上表面/侧暴露出来。第一板焊盘102和第二板焊盘104可包括(但不限于)诸如铜(cu)或铝(al)的金属材料或由该金属材料形成。

84.用于电连接第一板焊盘102和第二板焊盘104的布线图案可形成在绝缘核心101的内部。虽然绝缘核心101示为单层,但这仅是为了便于解释。例如,在一些实施例中,理所当然的是,绝缘核心101由多层构成,并且多层布线图案可形成在绝缘核心101的内部。

85.电路板100可安装在电子装置的母板等上。例如,可形成电连接至第一板焊盘102的第一连接构件150。电路板100可通过第一连接构件150安装在电子装置的母板等上。电路板100可为(但不限于)bga(球栅阵列板)。

86.例如,第一连接构件150可为(但不限于)焊料凸块。第一连接构件150可具有诸如块、球、引脚和柱的各种形状。第一连接构件150的数量、间隙、布置形式等当然不限于示出的那些,并且可根据设计而不同。

87.在一些实施例中,绝缘核心101可包括有机物质或由有机物质形成。例如,绝缘核心101可包括预浸料或由预浸料形成。预浸料是一种复合纤维,其中诸如碳纤维、玻璃纤维和芳纶纤维的增强纤维预先浸渍有热固性聚合物粘合剂(例如环氧树脂)或热塑性树脂。

88.在一些实施例中,电路板100可以包括或可以是覆铜板(ccl)。例如,电路板100可以具有这样一种结构,其中在热固性预浸料(例如,c级预浸料)的一侧或两侧堆叠铜板。

89.插入件结构200可置于电路板100的上表面/侧上。例如,插入件结构200可为(但不限于)硅插入件。插入件结构200可包括彼此相对的下侧(例如,底/下表面)和上侧(例如,

顶/上表面)。插入件结构200有利于电路板100与稍后将描述的第一半导体芯片310和第二半导体芯片320之间的电连接,并且可防止半导体封装件的翘曲。

90.插入件结构200可包括第一插入件焊盘202和第二插入件焊盘204。第一插入件焊盘202和第二插入件焊盘204可用于将插入件结构200分别电连接至其它组件。例如,第一插入件焊盘202可从插入件结构200的下侧/表面暴露出来,第二插入件焊盘204可从插入件结构200的上侧/表面暴露出来。例如,第一插入件焊盘202和第二插入件焊盘204可包括(但不限于)诸如铜(cu)或铝(al)的金属材料或由该金属材料形成。用于电连接第一插入件焊盘202和第二插入件焊盘204的布线图案可形成在插入件结构200的内部。

91.插入件结构200可安装在电路板100的上侧/表面上。例如,第二连接构件250可形成/设置在电路板100与插入件结构200之间。第二连接构件250可以电连接第二板焊盘104和第一插入件焊盘202。因此,电路板100和插入件结构200可通过第二连接构件250电连接。

92.第二连接构件250可为(但不限于)包括例如锡(sn)、锡(sn)合金等的低熔点金属的焊料凸块。第二连接构件250可具有诸如块、球、引脚和柱的各种形状。第二连接构件250可由单层或多层形成。当第二连接构件250由单层形成时,例如,第二连接构件250可包括锡-银(sn-ag)焊料或铜(cu)或由锡-银(sn-ag)焊料或铜(cu)形成。当第二连接构件250由多层形成时,例如,第二连接构件250可包括铜(cu)填料和焊料。第二连接构件250的数量、间隙、布置形式等当然不限于示出的那些,并且可根据设计而不同。

93.在一些实施例中,插入件结构200可为插入件衬底并且可包括插入件210、穿通件240和再分布层230。

94.例如,插入件210可为(但不限于)硅膜。穿通件240可置于插入件210内。例如,穿通件240可置于插入件210内,并且电连接至第一插入件焊盘202。

95.在一些实施例中,第一底部填料260可形成在电路板100与插入件结构200之间。第一底部填料260可填充电路板100与插入件结构200之间的空间。此外,第一底部填料260可覆盖第二连接构件250。例如,第一底部填料260可包围和接触第二连接构件250的侧壁。通过将插入件结构200固定于电路板100上,第一底部填料260可防止插入件结构200破裂等。例如,第一底部填料260可包括(但不限于)诸如emc(环氧模塑料)的绝缘聚合材料或由该绝缘聚合材料形成。

96.在一些实施例中,插入件结构200可包括钝化膜220和应力松弛焊盘205。应力松弛焊盘205可为例如图1的边缘焊盘13e。例如,应力松弛焊盘205可松弛钝化膜220的热应力。

97.应力松弛焊盘205可形成在插入件210的上侧/表面210_us上。应力松弛焊盘205可置于第二插入件焊盘204周围。应力松弛焊盘205可包围第二插入件焊盘204。应力松弛焊盘205可接触第二插入件焊盘204。应力松弛焊盘205的内侧可接触第二插入件焊盘204。例如,多个应力松弛焊盘205可分别包围和接触第二插入件焊盘204的侧表面。

98.钝化膜220可在插入件210的上侧/表面210_us上延伸。钝化膜220可接触应力松弛焊盘205。应力松弛焊盘205的外侧可接触钝化膜220。例如,钝化膜220可包围和接触应力松弛焊盘205的侧表面。应力松弛焊盘205和第二插入件焊盘204可例如在第二方向z上各自穿过钝化膜220,并且接触插入件210的上侧/表面210_us。

99.当根据一些实施例的半导体封装件暴露于高温时,热应力可集中于钝化膜220上。第二连接构件250可比钝化膜220具有更高的热膨胀系数(cte)。热应力可由于第二连接构

件250与钝化膜220之间的热膨胀系数的差异集中于钝化膜220。

100.根据本公开的一些实施例的半导体封装件的应力松弛焊盘205可置于第二插入件焊盘204与钝化膜220之间,以松弛钝化膜220的热应力。

101.应力松弛焊盘205可为在图1中描述的边缘焊盘13e。应力松弛焊盘205可包括绝缘材料或由绝缘材料形成。例如,应力松弛焊盘205可包括teos或pspi或由teos或pspi形成。

102.在截面中,应力松弛焊盘205在第一方向x上的宽度w1可为1μm或更大且20μm或更小。例如,应力松弛焊盘205在第一方向x上的宽度w1可为1μm或更大且10μm或更小。例如,应力松弛焊盘205在第一方向x上的宽度w1可为5μm或更大且10μm或更小。应力松弛焊盘205的热膨胀系数可为1ppm/k或更大且17ppm/k或更小。应力松弛焊盘205的模量可小于第二插入件焊盘204的模量。例如,应力松弛焊盘205的模量可大于15gpa且小于117gpa。然而,本公开的技术思想不限于此。

103.在平面图中,应力松弛焊盘205可包括与第二插入件焊盘204接触的内侧和与钝化膜220接触的外侧。应力松弛焊盘205的外侧可具有圆形、方形、三角形或六边形。然而,本公开的技术思想不限于此。

104.例如,钝化膜220可为(但不限于)氮化硅膜。在一些实施例中,钝化膜220也可由钝化材料、bcb(苯并环丁烯)、聚苯恶唑、聚酰亚胺、环氧树脂、氧化硅、氮化硅或它们的组合形成。

105.应力松弛焊盘205的上侧/表面205_us可与第二插入件焊盘204的上侧/表面204_us位于相同平面上。应力松弛焊盘205的上侧/表面205_us可与钝化膜220的上侧/表面220_us位于相同平面上。应力松弛焊盘205的上侧/表面205_us、第二插入件焊盘204的上侧/表面204_us和钝化膜220的上侧/表面220_us可为/构成插入件结构200的上侧/表面。

106.第一半导体芯片310和第二半导体芯片320可布置为在第一方向x上彼此间隔开,并且置于插入件结构200的上侧/表面上。第一半导体芯片310和第二半导体芯片320各自可为几百至几百万或更多个半导体元件集成在单个芯片中的集成电路(ic)。

107.在一些实施例中,第一半导体芯片310可为逻辑半导体芯片。例如,第一半导体芯片310可为例如(但不限于)应用处理器(ap),诸如cpu(中央处理单元)、gpu(图形处理单元)、fpga(现场可编程门阵列)、数字信号处理器、加密处理器,微处理器、微控制器和asic(专用ic)。

108.在一些实施例中,第二半导体芯片320可为存储器半导体芯片。例如,第二半导体芯片320可为易失性存储器(诸如,dram(动态随机存取存储器)或sram(静态随机存取存储器))或者可为非易失性存储器(诸如,闪速存储器、pram(相变随机存取存储器)、mram(磁阻随机存取存储器)、feram(铁电随机存取存储器)或rram(电阻随机存取存储器))。

109.作为示例,第一半导体芯片310可为诸如gpu的asic,第二半导体芯片320可为诸如高带宽存储器(hbm)的堆叠存储器。这种堆叠存储器可具有堆叠有多个集成电路的形式。堆叠的集成电路可通过tsv(硅穿通件)等彼此电连接。

110.在一些实施例中,第二半导体芯片320的数量可设为大于第一半导体芯片310的数量。例如,多个第二半导体芯片320可置于第一半导体芯片310周围。作为示例,如图11所示,可在第一半导体芯片310的两侧各自布置两个第二半导体芯片320。

111.第一半导体芯片310可包括第一芯片焊盘312。第一芯片焊盘312可用于将第一半

导体芯片310电连接至其它组件。例如,第一芯片焊盘312可从第一半导体芯片310的下侧/表面暴露出来。

112.第二半导体芯片320可包括第二芯片焊盘314。第二芯片焊盘314可用于将第二半导体芯片320电连接至其它组件。例如,第二芯片焊盘314可从第二半导体芯片320的下侧/表面暴露出来。

113.例如,第一芯片焊盘312和第二芯片焊盘314各自可包括(但不限于)诸如铜(cu)或铝(al)的金属材料或由该金属材料形成。

114.第一半导体芯片310和第二半导体芯片320可安装在插入件结构200的上侧/表面上。例如,第三连接构件352可形成/设置在插入件结构200和第一半导体芯片310之间。第三连接构件352可将多个第二插入件焊盘204中的一些电连接至第一芯片焊盘312。例如,第三连接构件352可接触多个第二插入件焊盘204中的一些和第一芯片焊盘312。因此,插入件结构200和第一半导体芯片310可彼此电连接。

115.此外,例如,第四连接构件354可形成/设置在插入件结构200与第二半导体芯片320之间。第四连接构件354可将多个第二插入件焊盘204中的另一些电连接至第二芯片焊盘314。例如,第四连接构件354可接触多个第二插入件焊盘204中的另一些和第二芯片焊盘314。因此,插入件结构200和第二半导体芯片320可电连接。

116.在一些实施例中,再分布层230的一部分可电连接第三连接构件352和第四连接构件354。例如,再分布层230的一部分可将连接至第三连接构件352的第二插入件焊盘204与电连接至第四连接构件354的第二插入件焊盘204电连接。因此,第一半导体芯片310和第二半导体芯片320可电连接。

117.第三连接构件352和第四连接构件354各自可为(但不限于)包括例如锡(sn)和锡(sn)合金的低熔点金属的焊料凸块。第三连接构件352和第四连接构件354可具有诸如块、球、引脚和柱的各种形状。第三连接构件352和第四连接构件354可包括或可为(但不限于)ubm(凸块下金属层)。

118.在一些实施例中,第二底部填料362可形成在插入件结构200和第一半导体芯片310之间,第三底部填料364可形成在插入件结构200和第二半导体芯片320之间。第二底部填料362可填充插入件结构200和第一半导体芯片310之间的空间,第三底部填料364可填充插入件结构200和第二半导体芯片320之间的空间。此外,第二底部填料362可覆盖第三连接构件352,第三底部填料364可覆盖第四连接构件354。例如,第二底部填料362可包围并接触第三连接构件352的侧表面,第三底部填料364可包围并接触第四连接构件354的侧表面。通过将第一半导体芯片310和第二半导体芯片320固定于插入件结构200上,第二底部填料362和第三底部填料364可防止第一半导体芯片310和第二半导体芯片320破裂。例如,第二底部填料362和第三底部填料364各自可包括(但不限于)诸如emc的绝缘聚合材料或由该绝缘聚合材料形成。

119.模制构件400可形成在插入件结构200的上侧(顶/上表面)上。模制构件400可形成为覆盖第一半导体芯片310和第二半导体芯片320的至少一部分。例如,模制构件400可覆盖/接触第一半导体芯片310的侧面、第二半导体芯片320的侧面、第二底部填料362和第三底部填料364。虽然模制构件400仅示为暴露出第一半导体芯片310的上侧(顶/上表面)和第二半导体芯片320的上侧(顶/上表面),但这仅是示例,并且模制构件400当然可覆盖第一半

导体芯片310的上侧(顶/上表面)和第二半导体芯片320的上侧(顶/上表面)。

120.模制构件400可包括(但不限于)诸如emc的绝缘聚合材料或由该绝缘聚合材料形成。在一些实施例中,第一底部填料260、第二底部填料362和第三底部填料364可包括与模制构件400的材料不同的材料或由该材料形成。例如,第一底部填料260、第二底部填料362和第三底部填料364各自可包括相比于模制构件400具有更好的流动性的绝缘材料或由该绝缘材料形成。因此,第一底部填料260、第二底部填料362和第三底部填料364可以有效地填充电路板100与插入件结构200之间或者插入件结构200与第一半导体芯片310和第二半导体芯片320之间的窄空间。

121.图14是用于解释根据一些实施例的半导体封装件的图。图15是用于解释图14的区域q的放大图。为了便于解释,将主要描述与利用图11至图13描述的那些不同的特征/点。

122.参照图14和图15,应力松弛焊盘205可不置于电连接至第一半导体芯片310的第二插入件焊盘204周围。

123.在一些实施例中,第二插入件焊盘204可包括第二_1插入件焊盘204_1和第二_2插入件焊盘204_2。

124.第二_1插入件焊盘204_1可为电连接至第一半导体芯片310的第二插入件焊盘204。第二_2插入件焊盘204_2可为电连接至第二半导体芯片320的第二插入件焊盘204。第二_1插入件焊盘204_1可电连接至和/或接触第三连接构件352。例如,第二_1插入件焊盘204_1可通过第三连接构件352电连接至第一芯片焊盘312。第二_2插入件焊盘204_2可电连接至和/或接触第四连接构件354。第二_2插入件焊盘204_2可例如通过第四连接构件354电连接至第二芯片焊盘314。

125.应力松弛焊盘205可不置于第二_1插入件焊盘204_1周围。应力松弛焊盘205可不置于作为电连接至第一半导体芯片310的第二插入件焊盘204的第二_1插入件焊盘204_1周围。例如,应力松弛焊盘205可不形成在电连接至逻辑半导体芯片的第二插入件焊盘204周围。

126.应力松弛焊盘205可置于第二_2插入件焊盘204_2周围。应力松弛焊盘205可置于作为电连接至第二半导体芯片320的第二插入件焊盘204的第二_2插入件焊盘204_2周围。例如,应力松弛焊盘205可形成在电连接至存储器半导体芯片的第二插入件焊盘204周围。

127.图16是用于解释根据一些实施例的半导体封装件的示图。图17是用于解释图16的区域r的放大图。为了便于解释,将主要描述与利用图11至图15描述的那些不同的特征/点。

128.参照图16和图17,应力松弛焊盘205可不置于第二_2插入件焊盘204_2周围。

129.应力松弛焊盘205可不置于第二_2插入件焊盘204_2周围。应力松弛焊盘205可不置于作为电连接至第二半导体芯片320的第二插入件焊盘204的第二_2插入件焊盘204_2周围。例如,应力松弛焊盘205可不形成在电连接至逻辑半导体芯片的第二插入件焊盘204周围。

130.应力松弛焊盘205可置于第二_1插入件焊盘204_1周围。应力松弛焊盘205可置于作为电连接至第一半导体芯片310的第二插入件焊盘204的第二_1插入件焊盘204_1周围。例如,应力松弛焊盘205可形成在电连接至存储器半导体芯片的第二插入件焊盘204周围。

131.图18是用于解释根据一些实施例的半导体封装件的图。图19是用于解释图18的区域s的放大图。为了便于解释,将主要描述与利用图11至图13描述的那些不同的特征/点。

132.参照图18和图19,插入件210可为多层。例如,插入件210可包括半导体膜211和层间绝缘膜213。

133.例如,半导体膜211可为(但不限于)硅膜。穿通件240可穿过半导体膜211。例如,穿通件240可从半导体膜211的顶/上表面/侧延伸,并且电连接至和/或接触第一插入件焊盘202。

134.层间绝缘膜213可覆盖半导体膜211的顶部/上侧/表面。例如,层间绝缘膜213可包括(但不限于)氧化硅、氮化硅、氧氮化硅和具有比氧化硅的介电常数更低的介电常数的低k材料中的至少一种或由它们中的至少一种形成。再分布层230可形成在层间绝缘膜213的内部。再分布层230可将穿通件240电连接至第二插入件焊盘204。

135.图20是根据一些实施例的半导体封装件的示例性布局图。为了便于解释,将主要描述与利用图11至图13描述的那些不同的特征/点。

136.参照图20,在根据一些实施例的半导体封装件中,可将六个第二半导体芯片320置于第一半导体芯片310周围。

137.例如,第二半导体芯片320可在第一半导体芯片310的一侧在第三方向y上并排放置。第二半导体芯片320可在第一半导体芯片310的另一侧在第三方向y上并排放置。例如,可将六个存储器半导体芯片置于单个逻辑半导体芯片周围。

138.图21是根据一些实施例的半导体封装件的示例性布局图。为了便于解释,将主要描述与利用图11至图13描述的那些不同的特征/点。

139.参照图21,根据一些实施例的半导体封装件可包括虚设芯片330。

140.虚设芯片330可不用作半导体芯片。例如,虚设芯片330可不用作集成电路芯片。例如,虚设芯片330可沿着第一方向x与第一半导体芯片310一起布置。作为示例,如图21所示,可在虚设芯片330的两侧上各自布置两个第一半导体芯片310。例如,虚设芯片330可设置在第一半导体芯片310的两侧上。例如,虚设芯片330中的每一个可在第三方向y上设置在两个第二半导体芯片320之间。

141.图22是根据一些实施例的半导体封装件的示例性布局图。图23是沿着图22的线b-b截取的截面图。为了便于解释,将主要描述与利用图11至图13描述的那些不同的特征/点。

142.在图22和图23中,根据一些实施例的半导体封装件可为包括硅插入件的3d封装件。然而,这仅是示例,本公开的技术思想不限于此。

143.参照图22和图23,根据一些实施例的半导体封装件可包括电路板100、插入件结构200、第一半导体芯片310和第二半导体芯片320。

144.在一些实施例中,第一半导体芯片310和第二半导体芯片320可按次序堆叠。第一半导体芯片310可在第二方向z上与第二半导体芯片320间隔开。例如,第二半导体芯片320可形成/设置在第一半导体芯片310上。可设置至少一个或多个第二半导体芯片320。在图23中,第二_1半导体芯片321和第二_2半导体芯片323可按次序堆叠在第一半导体芯片310上。尽管示出了两个第二半导体芯片320,但这仅是为了便于解释,并且实施例不限于此。

145.电路板100可为封装板。电路板100可为印刷电路板(pcb)。电路板100可包括绝缘核心101、第一板焊盘102和第二板焊盘104。

146.电路板100可安装在电子装置的母板等上。例如,电连接至和/或接触第一板焊盘102的第一连接构件150可形成/设置在电路板100的底表面上。电路板100可通过第一连接

构件150安装在电子装置的母板等上。

147.插入件结构200可置于电路板100的上(顶)侧(表面)上。例如,插入件结构200可为(但不限于)硅插入件。

148.插入件结构200可安装在电路板100的上(顶)侧(表面)上。例如,第二连接构件250可形成/设置在电路板100与插入件结构200之间。第二连接构件250可电连接第二板焊盘104和第一插入件焊盘202。因此,电路板100和插入件结构200可例如通过第二连接构件250电连接。

149.在一些实施例中,第一底部填料260可形成在电路板100与插入件结构200之间。第一底部填料260可填充电路板100与插入件结构200之间的空间。

150.插入件结构200可包括插入件210以及置于插入件210的上(顶)侧(表面)上的钝化膜220、第二插入件焊盘204和应力松弛焊盘205。应力松弛焊盘205可置于第二插入件焊盘204与钝化膜220之间。应力松弛焊盘205可松弛钝化膜220的热应力。

151.第一半导体芯片310可置于插入件结构200的上(顶)侧(表面)上。第一半导体芯片310可为逻辑半导体芯片。例如,第一半导体芯片310可为(但不限于)应用处理器(ap),诸如cpu(中央处理单元)、gpu(图形处理单元)、fpga(现场可编程门阵列)、数字信号处理器、加密处理器、微处理器、微控制器和asic(专用ic)。

152.第一半导体芯片310可包括第三芯片焊盘302和第四芯片焊盘304。第三芯片焊盘302和第四芯片焊盘304各自可用于将第一半导体芯片310电连接至其它组件。例如,第三芯片焊盘302可从第一半导体芯片310的下(底)侧(表面)暴露出来。第四芯片焊盘304可从第一半导体芯片310的上(顶)侧(表面)暴露出来。

153.例如,第三芯片焊盘302和第四芯片焊盘304各自可包括(但不限于)诸如铜(cu)或铝(al)的金属材料或由该金属材料形成。

154.在一些实施例中,第五连接构件351可形成/设置在插入件结构200与第一半导体芯片310之间。第五连接构件351可电连接第二插入件焊盘204和第三芯片焊盘302。因此,插入件结构200和第一半导体芯片310可例如通过第五连接构件351彼此电连接。

155.第五连接构件351可为(但不限于)包括例如锡(sn)和锡(sn)合金的低熔点金属或由该低熔点金属形成的焊料凸块。第五连接构件351可具有诸如块、球、引脚和柱的各种形状。第五连接构件351可包括(但不限于)ubm(凸块下金属层)。

156.在一些实施例中,第四底部填料361可形成在插入件结构200和第一半导体芯片310之间。第四底部填料361可填充插入件结构200和第一半导体芯片310之间的空间。第四底部填料361可覆盖第五连接构件351。例如,第四底部填料361可包围并接触第五连接构件351的侧表面。通过将第一半导体芯片310固定于插入件结构200上,第四底部填料361可防止第一半导体芯片310破裂等。第四底部填料361可包括(但不限于)一种或多种的诸如emc的绝缘聚合材料或由该绝缘聚合材料形成。

157.第二半导体芯片320可置于第一半导体芯片310的上(顶)侧(表面)上。第二半导体芯片320可包括第二_1半导体芯片321和第二_2半导体芯片323。第二_1半导体芯片321可安装在第一半导体芯片310的上(顶)侧(表面)上。第二_2半导体芯片323可安装在第二_1半导体芯片321的上(顶)侧(表面)上。

158.第二_1半导体芯片321和第二_2半导体芯片323中的每一个可为存储器半导体芯

片。例如,第二_1半导体芯片321和第二_2半导体芯片323各自可为诸如dram(动态随机存取存储器)或sram(静态随机存取存储器)的易失性存储器或者可为诸如闪速存储器、pram(相变随机存取存储器)、mram(磁阻随机存取存储器)、feram(铁电随机存取存储器)或rram(电阻随机存取存储器)的非易失性存储器。

159.第二_1半导体芯片321可包括第五芯片焊盘306和第六芯片焊盘308。第五芯片焊盘306和第六芯片焊盘308中的每一个可用于将第二_1半导体芯片321电连接至其它组件。例如,第五芯片焊盘306可从第二_1半导体芯片321的下(底)侧(表面)暴露出来。第六芯片焊盘308可从第二_1半导体芯片321的上(顶)侧(表面)暴露出来。

160.例如,第五芯片焊盘306和第六芯片焊盘308各自可包括(但不限于)一种或多种诸如铜(cu)或铝(al)的金属材料或由该金属材料形成。

161.在一些实施例中,第六连接构件353可形成/设置在第一半导体芯片310和第二_1半导体芯片321之间。第六连接构件353可电连接第四芯片焊盘304和第五芯片焊盘306。因此,第一半导体芯片310和第二_1半导体芯片321可例如通过第六连接构件353电连接。

162.第六连接构件353可为(但不限于)包括例如锡(sn)和锡(sn)合金的低熔点金属的焊料凸块。第六连接构件353可具有诸如块、球、引脚和柱的各种形状。第六连接构件353可包括(但不限于)ubm(凸块下金属层)。

163.在一些实施例中,第五底部填料363可形成在第一半导体芯片310和第二_1半导体芯片321之间。第五底部填料363可填充第一半导体芯片310和第二_1半导体芯片321之间的空间。第五底部填料363可覆盖第六连接构件353。例如,第五底部填料363可包围并接触第六连接构件353的侧表面。通过将第二_1半导体芯片321固定于第一半导体芯片310上,第五底部填料363可防止第二_1半导体芯片321破裂等。第五底部填料363可包括(但不限于)诸如emc的绝缘聚合材料或由该绝缘聚合材料形成。

164.第二_2半导体芯片323可包括第七芯片焊盘309。第七芯片焊盘309可用于将第二_2半导体芯片323电连接至其它组件。例如,第七芯片焊盘309可从第二_2半导体芯片323的下(底)侧(表面)暴露出来。第七芯片焊盘309可包括(但不限于)一种或多种诸如铜(cu)或铝(al)的金属材料或由该金属材料形成。

165.在一些实施例中,第七连接构件355可形成/设置在第二_1半导体芯片321和第二_2半导体芯片323之间。第七连接构件355可电连接第六芯片焊盘308和第七芯片焊盘309。因此,第二_1半导体芯片321和第二_2半导体芯片323可例如通过第七连接构件355彼此电连接。

166.第七连接构件355可为(但不限于)包括例如锡(sn)和锡(sn)合金的低熔点金属或由该低熔点金属形成的焊料凸块。第七连接构件355可具有诸如块、球、引脚和柱的各种形状。第七连接构件355可包括(但不限于)ubm(凸块下金属层)。

167.在一些实施例中,第六底部填料365可形成在第二_1半导体芯片321和第二_2半导体芯片323之间。第六底部填料365可填充第二_1半导体芯片321和第二_2半导体芯片323之间的空间。第六底部填料365可覆盖第七连接构件355。例如,第六底部填料35可包围并接触第七连接构件355的侧表面。通过将第二_2半导体芯片323固定至第二_1半导体芯片321上,第六底部填料365可防止第二_2半导体芯片323破裂等。例如,第六底部填料365可包括(但不限于)诸如emc的绝缘聚合材料或由该绝缘聚合材料形成。

168.作为具体实施方式的总结,本领域技术人员将理解,在不实质上偏离本公开的原理的情况下,可以对可选实施例进行许多变化和修改。因此,本公开所公开的可选实施例仅在一般和描述性意义上使用,而非出于限制的目的。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。