1.本发明是关于一种芯片传送速度(baud rate)检测方法及电子装置,特别是关于一种无须时脉引脚进行同步,且可自动进行调整以配合各种产品数据传输的芯片传送速度检测方法,以及执行芯片传送速度检测方法的电子装置。

背景技术:

2.在各种电子装置内部,常会设置多种感测装置,例如温度、湿度、距离、方位等感测器,这些感测器可通过通用非同步收发传输(universal asynchronous receiver transmitter,uart)接口将感测讯息传送给电子装置的处理器。通用非同步收发传输接口分别通过tx引脚进行传输、rx引脚进行接收,不须通过时脉信号的引脚进行同步的动作。此时,数据的传送或接收通过传送速度的方式进行同步,也就是确认每一个位传输或接收的时间,使得传送方与接收方同步,进而得到正确的信息。

3.现有的通用非同步收发传输接口的电子装置当中,虽然能通过型号确认数据传送速度,但由于时序不同或制作上的误差使得传送方与接收方的传送速度不同,将会造成数据传输间的通讯错误。为了自动调整传送速度,必须在传送数据时设定起始位,设定起始位到预设位为高准位,再检测达到第一个位或者是到达预设位的经过时间,依此来计算每个位的传送时间。然而,现有的感测器往往一连接上电源后即开始传送感测数据,并未设定相关的讯息表头格式以供上述初始位的检测,难以达到自动调整传送速度的目标。

4.综观前所述,本发明的发明人思索并设计一种芯片传送速度检测方法及电子装置,以期针对已知技术的问题加以改善,进而增进产业上的实施利用。

技术实现要素:

5.有鉴于背景技术所述的问题,本发明的目的在于提供一种芯片传送速度检测方法及电子装置,避免感测器与处理器的芯片传送速度有所差异而影响数据传送的正确性,造成数据读取错误的问题。

6.基于上述目的,本发明提供一种芯片传送速度检测方法,是由处理单元通过通用非同步收发传输接口传送或接收作动装置的操作信号,芯片传送速度检测方法包含:启动处理单元的通用非同步收发传输接口,获取预设时间内操作信号的信号波形;检测信号波形当中具有连续三个位转换波形的多个位传送时间;选择多个位传送时间当中最小的多个选择时间,计算多个选择时间的平均时间;以及设定处理单元,以平均时间作为读取操作信号的芯片传送速度。

7.较佳地,多个位传送时间可包含信号波形由高准位转为低准位再转回高准位的过程中所检测到的低准位时间。

8.较佳地,多个位传送时间可包含信号波形由低准位转为高准位再转回低准位的过程中所检测到的高准位时间。

9.较佳地,该芯片传送速度检测方法可于处理单元上电时执行以设定芯片传送速

度。

10.较佳地,芯片传送速度检测方法可进一步包含:于处理单元运作固定时间后,重新进行芯片传送速度检测方法以定期更新芯片传送速度。

11.较佳地,芯片传送速度检测方法可进一步包含当检测处理单元运作达预设温度后,重新进行芯片传送速度检测方法以定期更新芯片传送速度。

12.较佳地,作动装置可包含温度感测器、湿度感测器、距离感测器、方向感测器。

13.本发明提供一种电子装置,其包含处理单元及通用非同步收发传输接口。通用非同步收发传输接口耦接于处理单元,通用非同步收发传输接口传送或接收作动装置的操作信号,由处理单元执行如上所述的芯片传送速度检测方法。作动装置可包含温度感测器、湿度感测器、距离感测器、方向感测器。

14.承上所述,依本发明的芯片传送速度检测方法及电子装置,其可具有一或多个下述优点:

15.(1)此芯片传送速度检测方法及电子装置能运用于各种连接通用非同步收发传输接口的作动装置,在不改变操作信号内容的情况下,自动检测芯片传送速度,使得处理单元能正确地读取操作信号,避免信号读取产生异常,提升芯片操作的正确率。

16.(2)此芯片传送速度检测方法及电子装置能自动更新芯片传送速度,避免芯片在操作过程中因为芯片传送速度差异造成信号读取错误,提升作动装置操作上的稳定性及可靠度。

17.(3)此芯片传送速度检测方法及电子装置可依据装置类型或处理单元类型调整获取时间及选择芯片处理时间的数量,适用于不同作动装置及芯片的操作上,增加芯片传送速度检测方法的适用范围。

附图说明

18.为使本发明的技术特征、内容与优点及其所能达成的功效更为显而易见,兹将本发明配合以下附图进行说明:

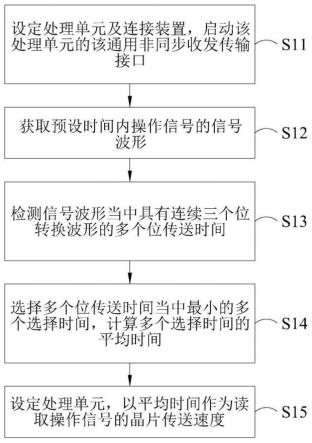

19.图1为本发明实施例的芯片传送速度检测方法的流程图。

20.图2为本发明实施例的芯片传送速度设定的流程图。

21.图3为本发明实施例的连续位转换的示意图。

22.图4为本发明实施例的获取时间的波形示意图。

23.图5为本发明实施例的电子装置的示意图。

24.附图标记

25.s11~s15,s21~s27:步骤

26.h:高准位

27.l:低准位

28.t:预设时间

29.t1~t15:位传送时间

30.t

high

:高准位时间

31.t

low

:低准位时间

32.w:信号波形

33.10:电子装置

34.11:处理单元

35.12:通用非同步收发传输接口

36.21:温度感测器

37.22:湿度感测器

38.23:距离感测器

39.24:方向感测器

具体实施方式

40.为利于了解本发明的技术特征、内容与优点及其所能达成的功效,兹将本发明配合附图,并以实施例的表达形式详细说明如下,而其中所使用的图式,其主旨仅为示意及辅助说明书之用,未必为本发明实施后的真实比例与精准配置,故不应就所附的图式的比例与配置关系解读、局限本发明于实际实施上的权利范围。

41.请参阅图1,图1为本发明实施例的芯片传送速度检测方法的流程图。如图1所示,芯片传送速度检测方法包含以下步骤(s11~s15):

42.步骤s11:设定处理单元及连接装置,启动该处理单元的该通用非同步收发传输接口。在电子装置当中,设有运算处理的处理单元,例如中央处理器、微处理器的芯片,这些芯片通过通用非同步收发传输接口与电子装置连接的各种作动装置进行信号的传输,例如接收感测装置所检测到的感测信号或是传送操作信号至各个作动装置。例如当电子装置连接的温度感测器、湿度感测器、距离感测器、方向感测器等接上电源启动后,感测信号的传输即通过通用非同步收发传输接口传送到电子装置的处理单元,当这些感测信号通过通用非同步收发传输接口传送时,芯片处理速度的设定,将是各种操作信号是否能正确读取的重要依据。

43.步骤s12:获取预设时间内操作信号的信号波形。如背景技术所述,操作信号在装置上电后即开始传送,而传送的信号并未设置检测数据起始位的表头,无法由此判断信号的芯片处理速度。因此,为进行自动芯片处理速度的判断,首先获取预设时间内操作信号的信号波形,利用此预设时间内的信号波形来决定操作信号的芯片处理时间。

44.步骤s13:检测信号波形当中具有连续三个位转换波形的多个位传送时间。当获取一段时间的的信号波形后,通过处理单元判断此信号波形当中,具有连续三个位转换波形的状态,将具有连续三个位转换波形的信号判定为一个位传送时间。在本实施例中,连续三个位转换波形可为信号波形由高准位转为低准位再转回高准位,将两个高准位之间的低准位时间作为位传送时间。类似地,连续三个位转换波形也可为信号波形由低准位转为高准位再转回低准位,以两个低准位之间的高准位时间作为位传送时间。由于获取预设时间内具有多个高低准位切换,因此可取得多个位传送时间。

45.步骤s14:选择多个位传送时间当中最小的多个选择时间,计算多个选择时间的平均时间。当获取到多个位传送时间后,将多个位传送时间进行排序,依排序选择最小的几个位传送时间作为选择时间,以这些选择时间为基准,进行加总后平均来取得一个平均时间。选择最小的几个位传送时间来平均而非将所有位传送时间平均的原因,主要是因为操作信号的信号波形并非每个位即会产生高低准位的变化,若采用整体平均可能会将非单一位的

时间计入而使得判断过程产生误差,因此本实施例中,选择取得的位传送时间中最小的多个位传送时间来进行平均,选择的数量可为最小的10个位传送时间,但本发明不以此为限,选择的数量可依据前述获取时间的长短来加以调整。

46.步骤s15:设定处理单元,以平均时间作为读取操作信号的芯片传送速度。在经过前述的波形获取、位转换时间判断以及选择时间平均后,取得一个平均时间,在处理单元取得此平均时间后,设定此平均时间作为操作信号的芯片传送速度,当处理单元通过通用非同步收发传输接口传送或接收操作信号时,以此芯片传送速度来读取操作信号。

47.在本实施例中,芯片传送速度检测方法仅需于作动装置上电后获取一段传送信号的波形进行分析即可取得操作信号的芯片传送速度,并不需要对作动装置传送的操作信号设定不同的起始信号或设定信号,使得芯片经由通用非同步收发传输接口连接的电子装置能适用于各种连接的作动装置,例如温度感测器、湿度感测器、距离感测器、方向感测器等感测装置,增加装置的相容性。同时,芯片传送速度能自动设定,减少设定芯片传送速度的设定流程,同时维持信号读取的正确性,避免信号读取速度错误而使得电子装置操作产生异常,提升装置操作的稳定性。

48.请参阅图2,图2本发明实施例的芯片传送速度设定的流程图。如图2所示,芯片传送速度设定包含以下步骤(s21~s27):

49.步骤s21:启动通用非同步收发传输接口。当电子装置接收到电源供应后,系统对处理单元供电,启动通用非同步收发传输接口。通用非同步收发传输接口通过传输及接收的引脚连接至感测装置感测装置所检测的信号传输至处理单元。

50.步骤s22:确认是否收到传输信号。若是,则进入步骤s23。若否,则重新检测是否接受到感测装置的传输信号。

51.步骤s23:获取一段时间的信号波形。当接收到感测装置的传输信号后,处理单元获取传输信号当中一段预设时间的信号波形,分析预设时间的信号波形来决定芯片传送速度。芯片传送速度的检测方法可依据前述实施例所述,检测信号波形当中具有连续三个位转换波形的多个位传送时间,再选择其中最小的多个位传送时间,将所选的时间进行平均来作为芯片传送速度。

52.步骤s24:设定芯片传送速度。当芯片传送速度确定后,以计算所取得的平均时间设定为处理单元的芯片传送速度,让处理单元在读取传输信号时,依据设定的芯片传送速度来处理信号。

53.步骤s25:接收传输信号。当设定完芯片传送速度后,处理单元持续通过通用非同步收发传输接口来传送或接收连接装置的传输信号,例如接收感测装置的感测信号,通过正确的芯片处理速度来解析感测信号内容。

54.步骤s26:确认是否自动更新芯片传送速度。若是,则进入步骤s27,若否,则重新回到步骤s25,持续接收传输信号。

55.步骤s27:设定自动更新的时间。当电子装置运转过程中,芯片传送速度可能会因为各种因素而有所变化,例如不同温度会使得芯片传送速度有所差异,因此在电子装置运转过程中,可设定自动更新芯片传送速度的机制。在本实施例中,设定处理单元在运转一段固定时间后自动进行更新,即每设定芯片传送速度后经过一段固定时间,则重新回到步骤s22,再次进行检测与设定的流程,自动更新最新的芯片传送速度。在另一实施例中,处理单

元也可依据温度变化来进行更新,例如感测处理单元的运作温度,当温度上升或下降到达预设温度后,重新回到步骤s22,再次进行检测与设定的流程,更新最新的芯片传送速度。

56.请参阅图3,图3为本发明实施例的连续位转换的示意图。如图3中(a)部分所示,当信号波形由高准位h转为低准位l再转回高准位h的过程中,两个高准位h波形之间所检测到的低准位时间t

low

可作为一个位传送时间。相对地,在图3中(b)部分所示,当信号波形由低准位l转为高准位h再转回低准位l的过程中,两个低准位l波形之间所检测到的高准位时间t

high

可作为一个位传送时间。依据上述判断方式,当获取到一段时间的信号波形时,可依据信号波形的高低准位变化方式,判断位传送时间,以此作为计算芯片传送速度的计算基础,实际波形及获取内容如以下实施例所示。

57.请参阅图4,图4为本发明实施例的获取时间的波形示意图。如图4所示,当处理单元上电启动后,通用非同步收发传输接口开始传输连接装置的操作信号,首先获取预设时间t的信号波形w,此预设时间t可依据连接装置类型或处理单元类型加以调整。在预设时间t当中,判断信号波形w具有连续三个位转换波形的15个位传送时间(t1~t15)。

58.在取得的15个位传送时间当中,其包含高准位时间及低准位时间,为了取得精确的位传输处理的时间,选择最小的前11个位传送时间(t2,t3,t5,t6,t7,t9,t10,t11,t12,t14,t15),并将其加总平均,以平均时间8.61μs作为芯片传送速度。在本实施例中,选择前11小的位传送时间,排除4个位传送时间(t1,t4,t8,t13),可将信号波形w中超过单一位处理时间的波形剔除,避免获取到错误的位处理时间而使得计算出来的芯片传送速度产生误差。在其他实施例中,获取预设时间t以及选择位传送时间的数量,都可依据装置类型或处理单元类型对应改变。

59.请参阅图5,图5为本发明实施例的电子装置的示意图。如图5所示,电子装置10包含处理单元11及通用非同步收发传输接口12。电子装置10可为电脑装置或机台设备,其中的处理单元11为电子装置10当中的中央处理器或微处理器芯片,通用非同步收发传输接口12耦接于处理单元11。通用非同步收发传输接口12可连接至作动装置,传送或接收作动装置的操作信号,例如连接至温度感测器21、湿度感测器22、距离感测器23、方向感测器24来接收各个感测装置的感测信号。当接收到感测装置的感测信号,可由处理单元11执行如上所述实施例所述的芯片传送速度检测方法,让电子装置10能正确的读取作动装置的操作信号。电子装置10执行芯片传送速度检测方法以及设定芯片传送速度的方法请参阅前述实施例,相同内容不再重复描述。

60.以上所述仅为举例性,而非为限制性者。任何未脱离本发明的精神与范畴,而对其进行的等效修改或变更,均应包含于所附的权利要求的范围中。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。