1.本技术涉及智能驾驶技术领域,具体涉及一种时间同步方法、装置、设备及存储介质。

背景技术:

2.随着智能驾驶技术的发展,车辆驾驶舱中对传感器的需求也是越来越多,为了获得更加精准的融合数据,采用各传感器基于同一时间域采集数据的方式。目前大多采用精密时间协议(precision time protocol简称ptp)做车内的时钟同步,传感器在需在启动后做时间同步,经历了启动时间和同步时间之后进行数据采集。传统的ptp在两个单一链路延迟(pdelay)后才能计算时钟的相邻关系(neighboratio)值,故链路延迟也只能在两个周期之后计算得出,从而导致整个时间同步的收敛时间较长。

3.为了有效提升ptp时间同步精度,通常通过补偿软件计算和硬件配置的延后和频率偏移引入的时间偏移误差,或采用时间戳抖动补偿方法,通过接收端根据本次报文与上次报文的发送时间间隔、以及本次报文与上次报文的接收时间间隔,对本次报文的时间戳进行补偿。然而,现目前阶段ptp本身精度以达到微秒级,已难以突破,而时间同步的收敛时间却相对较长,且尚无解决方案。

技术实现要素:

4.鉴于以上所述现有技术的缺点,本发明提供一种时间同步方法、装置、设备及存储介质,以解决上述技术问题。

5.本发明提供的一种时间同步方法,所述方法包括:获取时间同步指令、当前时刻以及历史存储链路延迟值,所述时间同步指令包括原始时间戳信息、发送校验值、发送频率比值;基于所述原始时间戳信息、所述发送校验值、所述发送频率比值和所述历史存储链路延迟值确定指令发送时刻;将所述当前时刻确定为指令接收时刻,基于所述指令接收时刻和所述指令发送时刻确定本地时钟偏差,以对时间进行第一次同步。

6.于本发明的一实施例中,基于原始时间戳信息、发送校验值、发送频率比值和历史存储链路延迟值确定指令发送时刻的公式如下:

7.t

i-1

=preciseorigintimestamp correctionfield

i-1

rateratio

i-1

*meanlinkdelay

i-1

8.其中,t

i-1

是指令发送时刻,preciseorigintimestamp是原始时间戳,correctionfield

i-1

是发送校验值,rateratio

i-1

是发送频率比值,meanlinkdelay

i-1

是历史存储链路延迟值。

9.于本发明的一实施例中,基于所述指令发送时刻和所述指令接收时刻确定时钟偏差的公式如下:

10.offset=t

i-t

i-1

11.其中,offset是本地时钟偏差,ti是指令接收时刻,t

i-1

是指令发送时刻。

12.于本发明的一实施例中,对时间进行第一次同步之后还包括:获取所述发送频率比值和预设的相邻频率比值比率,将所述发送频率比值和所述相邻频率比值比率的乘积确定为当前频率比值,并将所述接收频率比值作为下一次时间同步周期的发送频率比值,以完成下一次时间同步。

13.于本发明的一实施例中,获取历史存储链路延迟值还包括:获取预设固定周期数的多个独立链路延迟值,基于所述多个独立链路延迟值确定所述预设固定周期的周期平均链路延迟值,并在接收到下电指令时保存所述周期平均链路延迟值,以作为历史存储链路延迟值。

14.于本发明的一实施例中,获取历史存储链路延迟值还包括:获取当前周期的当前链路延迟值,和上一周期的上一链路延迟值;若所述当前链路延迟值和所述上一链路延迟值的差值大于预设的标准差值,则记录当前链路延迟值,并在接收到下电指令时存储所述当前链路延迟值,以作为历史存储链路延迟值;若所述当前链路延迟值和所述上一链路延迟值的差值小于或等于预设的标准差值,则记录所述上一链路延迟值,并在接收到下电指令时存储所述上一链路延迟值,以作为历史存储链路延迟值。

15.本发明提供的一种时间同步装置,所述装置包括:信息获取模块,用于获取时间同步指令、当前时刻以及历史存储链路延迟值,所述时间同步指令包括原始时间戳信息、发送校验值、发送频率比值;数据确定模块,用于基于所述原始时间戳信息、所述发送校验值、所述发送频率比值和所述历史存储链路延迟值确定指令发送时刻;同步执行模块,用于将所述当前时刻确定为指令接收时刻,基于所述指令接收时刻和所述指令发送时刻确定本地时钟偏差,以对时间进行第一次同步。

16.本发明提供的一种电子设备,所述电子设备包括:一个或多个处理器;存储装置,用于存储一个或多个程序,当所述一个或多个程序被所述一个或多个处理器执行时,使得所述电子设备实现如上所述的时间同步法。

17.本发明提供的一种计算机可读存储介质,其特征在于,其上存储有计算机程序,当所述计算机程序被计算机的处理器执行时,使计算机执行如上所述的时间同步方法。

18.本发明的有益效果:本发明提供一种时间同步方法、装置、设备及存储介质,通过获取时间同步指令、当前时刻以及历史存储链路延迟值,时间同步指令包括原始时间戳信息、发送校验值、发送频率比值;基于原始时间戳信息、发送校验值、发送频率比值和历史存储链路延迟值确定指令发送时刻;将当前时刻确定为指令接收时刻,基于指令发送时刻和指令接收时刻确定时钟偏差,以对时间进行第一次同步;将在上一次下电时存储的时间同步周期的链路延迟值确定为历史存储链路延迟值,作为本次上电后的第一个时间同步链路延迟值,以达到在上电的第一个同步命令周期就能同步的目的,从而降低时间同步周期的收敛时间,以提升精密时间协议数据采集的准确性。

19.应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本技术。

附图说明

20.此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本技术的实施例,并与说明书一起用于解释本技术的原理。显而易见地,下面描述中的附图仅仅是本技术

的一些实施例,对于本领域普通技术者来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。在附图中:

21.图1是本技术的一示例性实施例示出的在车辆驾驶域中进行时间同步的实施环境示意图;

22.图2是本技术的一示例性实施例示出的时间同步流程图;

23.图3是本技术的一示例性实施例示出的时间同步上下电流程图;

24.图4是本技术的一示例性实施例示出的时间同步全过程;

25.图5是本技术的一示例性实施例示出的时间同步装置的框图;

26.图6示出了适于用来实现本技术实施例的电子设备的计算机系统的结构示意图。

具体实施方式

27.以下将参照附图和优选实施例来说明本发明的实施方式,本领域技术人员可由本说明书中所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。应当理解,优选实施例仅为了说明本发明,而不是为了限制本发明的保护范围。

28.需要说明的是,以下实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

29.在下文描述中,探讨了大量细节,以提供对本发明实施例的更透彻的解释,然而,对本领域技术人员来说,可以在没有这些具体细节的情况下实施本发明的实施例是显而易见的,在其他实施例中,以方框图的形式而不是以细节的形式来示出公知的结构和设备,以避免使本发明的实施例难以理解。

30.首先需要说明的是,在目前阶段,但对于车辆座舱域中各传感器之间的时间同步一般采用精密时间协议(precision time protocol,简称ptp)的方式实现,该协议是一个通过网络同步时钟的一个协议。当硬件支持时,ptp精度能达到亚微秒。

31.图1是本技术的一示例性实施例示出的在车辆驾驶域中进行时间同步的实施环境示意图。如图1所示,系统架构可以包括当前车辆101和计算机设备102。其中,计算机设备102可以是台式图形处理器(graphic processing unit,gpu)计算机、gpu计算集群、神经网络计算机等中的至少一种。相关技术人员可以使用该计算机设备102基于车辆驾驶域中的多个传感器在进行时间同步过程指令的发出与接收时间,确定该时间同步的本地时钟偏差,同时基于计算机设备102存储该车辆驾驶域在上一次下电前的历史链路延迟值,并将其作为本次上电后的第一次时间同步周期的链路延迟值,从而达到降低时间同步过程中的收敛时间的目的。

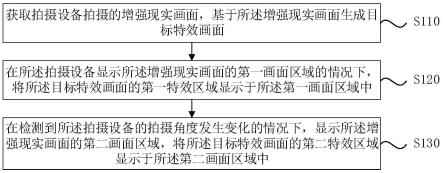

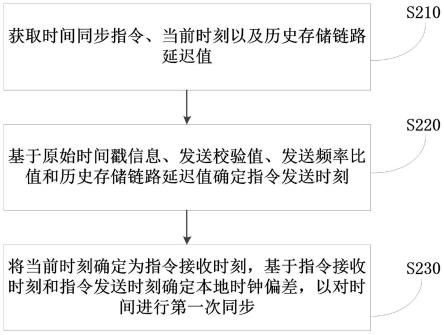

32.图2是本技术的一示例性实施例示出的时间同步流程图,如图2所示,在一示例性的实施例中,时间同步方法至少包括步骤s210至步骤s230,详细介绍如下:

33.步骤s210,获取时间同步指令、当前时刻以及历史存储链路延迟值,时间同步指令包括原始时间戳信息、发送校验值、发送频率比值;

34.在本发明的一个实施例中,同步指令(sync)信息的交互涉及两个ptp实例,在sync消息从ptp示例主盘(master)传输到从盘slave过程中,master在t1时刻发送sync消息,随后发送时间戳消息(即follw_up消息),该follw_up消息中携带了2个重要信息,该重要消息即为sync消息的发送时间以及发送频率比值,其中发送时间包括原始时间戳preciseorigintimestamp和校验值correctionfield

i-1

,而发送频率比值即为rateratio

i-1

。

35.步骤s220,基于原始时间戳信息、发送校验值、发送频率比值和历史存储链路延迟值确定指令发送时刻;

36.在本发明的一个实施例中,基于原始时间戳、发送校验值、发送频率比值以及历史存储链路延迟值确定时间同步指令的发送时刻,其公式如下:

37.t

i-1

=preciseorigintimestamp correctionfield

i-1

rateratio

i-1

*meanlinkdelay

i-1

公式(1),

38.其中,t

i-1

是指令发送时刻,preciseorigintimestamp是原始时间戳,correctionfield

i-1

是发送校验值,rateratio

i-1

是发送频率比值,meanlinkdelay

i-1

是历史存储链路延迟值。

39.步骤s230,将当前时刻确定为指令接收时刻,基于指令接收时刻和指令发送时刻确定本地时钟偏差,以对时间进行第一次同步。

40.在本发明的一个实施例中,将当前时刻确定为接收到该时间同步指令的时刻,然后根据接收到该时间同步指令的当前时刻和该时间同步指令的发送时刻之间的差值,计算得到本地时钟偏差,从而完成时间同步,其本地时钟偏差的计算公式如下:

41.offset=t

i-t

i-1

ꢀꢀꢀꢀ

公式(2),

42.其中,offset是本地时钟偏差,ti是指令接收时刻,t

i-1

是指令发送时刻。

43.在本发明的一个实施例中,由于每个节点的硬件的时钟精度不一样,每次的时间同步都只是在当前时刻的时间同步,并不是完全时间同步,经过一段时间之后,不同传感器之间的时间又会跑偏,故时间同步的动作不是只做一次,而是需要周期性的进行,故在基于当前时间同步周期的发送频率比值和相邻频率比值比率得到当前时间同步周期的接收频率比值之后,需要将该接收频率比值记录,并作为下一次时间同步周期的发送时间比值。

44.图3是本技术的一示例性实施例示出的时间同步上下电流程图,如图3所示,在上电之后,需持续记录每一个时间同步周期的链路延迟值,以及该上电时间段内时间同步的周期数量,并基于每个时间同步周期的链路延迟值和时间同步周期的数量,得到一个平均链路延迟值,并将该平均链路延迟值记录下来,并识别是否收到下电的指令,若并未收到下电指令,则持续重复时间同步指令并反复记录每个时间同步周期的链路延迟值、时间同步周期数量以及平均链路延迟值,当收到下电指令时,则将得到的最后一个平均链路延迟值作为这个上电期间的平均链路延迟值,并记录。

45.获取历史存储链路延迟值包括:获取每个时间同步周期的链路延迟值,以及时间同步周期的次数;基于多个链路延迟值和时间同步周期的次数,确定平均链路延迟值;监测指令状态,若接收到下电指令,则保存平均链路延迟值,以使下次上电可读取平均链路延迟值,并将平均链路延迟值作为历史存储链路延迟值。

46.在本发明的一个实施例中,从上电之后开始记录每个时间同步周期的链路延迟值

(meanlinkdelay),并记录每个meanlinkdelay的值到的总和,其计算公式如下:

47.sum(meanlinkdelay)i=sum(meanlinkdelay)

i-1

meanlinkdelayi,counter=i 公式(3),

48.其中,sum(meanlinkdelay)i为截至当前时间同步周期的所有链路延迟值的总和,sum(meanlinkdelay)

i-1

为截止到上一时间同步周期的全部链路延迟值的总和,meanlinkdelayi为当前时间同步周期的链路延迟值,counter=i为截至当前时间同步周期的周期数量。

49.在计算得到截至当前时间同步周期的链路延迟值总和之后,基于时间同步周期的周期数量,计算得到个时间同步周期的平均链路延迟值,其计算公式如下:

50.avg(meanlinkdealy)=sum(meanlinkdelay)/counter 公式(4),

51.其中avg(meanlinkdealy)为平均链路延迟值,sum(meanlinkdelay)为链路延迟值的总和,counter时间同步周期数量。

52.然后将得到的平均链路延迟值作为标准的链路延迟值,即历史存储链路延迟值。获取历史存储链路延迟值还包括:获取预设固定周期数的多个独立链路延迟值,基于多个独立链路延迟值确定预设固定周期的周期平均链路延迟值,并在接收到下电指令时保存周期平均链路延迟值,以作为历史存储链路延迟值。

53.在本发明的一个实施例中,以预设固定周期n=100为例,则以当前周期为0计数,取当前周期之前99个时间同步周期的链路延迟值的总和,与当前周期的链路延迟值相加,得到固定周期内链路延迟值的总和,将该链路延迟值总和除以周期数量即100,得到该固定周期内的平均链路延迟值,将平均链路延迟值作为历史存储链路延迟值。

54.获取历史存储链路延迟值还包括:获取当前周期的当前链路延迟值,和上一周期的上一链路延迟值;若当前链路延迟值和上一链路延迟值的差值大于预设的标准差值,则记录当前链路延迟值,并在接收到下电指令时存储当前链路延迟值,以作为历史存储链路延迟值;若当前链路延迟值和上一链路延迟值的差值小于或等于预设的标准差值,则记录上一链路延迟值,并在接收到下电指令时存储上一链路延迟值,以作为历史存储链路延迟值。

55.在本发明的一个实施例中,以链路延迟值的标准差值100ns为例,获取当前时间同步周期的链路延迟值x以及上一时间同步周期的链路延迟值y,比较当前时间同步周期的链路延迟值x和上一时间同步周期的链路延迟值y,当得到|x-y|>100,则记录当前链路延迟值x,并以x为历史存储链路延迟值;当得到|x-y|≤100,则保持记录上一时间同步周期的链路延迟值y,并以y为历史存储链路延迟值。

56.对时间进行第一次同步之后还包括:获取发送频率比值和预设的相邻频率比值比率,将发送频率比值和相邻频率比值比率的乘积确定为当前频率比值,并将接收频率比值作为下一次时间同步周期的发送频率比值,以完成下一次时间同步。根据发送频率比值和相邻频率比值比率的关系,确定得到该时间同步指令接收时刻的接收频率比值的公式如下:

57.rateratio=rateratio

i-1

*neighborrateratio

ꢀꢀꢀ

公式(5),

58.其中,rateratio是接收频率比值,rateratio

i-1

是发送频率比值,neighborrateratio是相邻频率比值比率。

59.图4是本技术的一示例性实施例示出的时间同步全过程,如图4所示,时间同步指令涉及master和slave两个ptp实例,slave通过发送链路延迟测量请求(pdelay_req)消息向master请求计算传播延时,并获取pdelay_req消息的发送时间的时间戳t1;当master接收到pdelay_req消息,并获取接收到该消息的时间戳t2;然后master则会发送测量响应(pdelay_resp)消息,该消息携带有时间戳t2,同时获取pdelay_resp消息发送时间的时间戳t3,随后master则会发送测量相应跟随(pdelay_resp_followup)消息,该pdelay_resp_followup消息携带有时间戳t3;当slave接收到pdelay_resp消息后,获取接收到该消息的时间戳t4,同时提取出消息中的时间戳t2;当slave接收到pdelay_resp_followup消息,则提取消息中的时间戳t3;至此,slave在所有的消息完成交互之后,则获取到时间戳t1、t2、t3和t4,并以相同的方式得到下一次时间同步周期的时间戳t1’、t2’、t3’和t4’。

60.在本发明的一个实施例中,通过如图4所示的方法slave在两次时间同步周期之后获取得到t1、t2、t3、t4以及t1’、t2’、t3’、t4’,则可以计算得到master相对于slave的频率比率neighborrateratio,其计算公式如下:

[0061][0062]

其中,neighborrateratio为master相对于slave的频率比率,t3'为第二个时间同步周期中pdelay_resp消息发送时间的时间戳,t3为第一个时间同步周期中pdelay_resp消息发送时间的时间戳,t4'为第二个时间同步周期中slave接收到pdelay_resp消息的时间戳,t4为第一个时间同步周期中slave接收到pdelay_resp消息的时间戳。

[0063]

又根据得到的neighborrateratio和第一次时间同步周期的各时间戳得到master相对于slave的路径传播延时,其计算公式如下:

[0064][0065]

其中,meanlinkdelay为master相对于slave的路径传播延时,neighborrateratio为master相对于slave的频率比率,t4为第一个时间同步周期中slave接收到pdelay_resp消息的时间戳,t1为第一个时间同步周期中pdelay_req消息的发送时间戳,t3为第一个时间同步周期中pdelay_resp消息发送时间的时间戳,t2为第一个时间周期中maste接收到pdelay_req消息的时间戳。

[0066]

图5是本技术的一示例性实施例示出的时间同步装置的框图。该装置可以应用于图1所示的实施环境,并具体配置在智能终端102中。该装置也可以适用于其它的示例性实施环境,并具体配置在其它设备中,本实施例不对该装置所适用的实施环境进行限制。

[0067]

如图5所示,该示例性的时间同步装置包括:信息获取模块510,数据确定模块520,同步执行模块530。

[0068]

其中,信息获取模块510,用于获取时间同步指令、当前时刻以及历史存储链路延迟值,时间同步指令包括原始时间戳信息、发送校验值、发送频率比值;数据确定模块520,用于基于原始时间戳信息、发送校验值、发送频率比值和历史存储链路延迟值确定指令发送时刻;同步执行模块530,用于将当前时刻确定为指令接收时刻,基于指令接收时刻和指令发送时刻确定本地时钟偏差,以对时间进行第一次同步。

[0069]

需要说明的是,上述实施例所提供的时间同步装置与上述实施例所提供的时间同

步方法属于同一构思,其中各个模块和单元执行操作的具体方式已经在方法实施例中进行了详细描述,此处不再赘述。上述实施例所提供的时间同步装置在实际应用中,可以根据需要而将上述功能分配由不同的功能模块完成,即将装置的内部结构划分成不同的功能模块,以完成以上描述的全部或者部分功能,本处也不对此进行限制。

[0070]

本技术的实施例还提供了一种电子设备,包括:一个或多个处理器;存储装置,用于存储一个或多个程序,当一个或多个程序被一个或多个处理器执行时,使得电子设备实现上述各个实施例中提供的时间同步方法。

[0071]

图6示出了适于用来实现本技术实施例的电子设备的计算机系统的结构示意图。需要说明的是,图6示出的电子设备的计算机系统600仅是一个示例,不应对本技术实施例的功能和使用范围带来任何限制。

[0072]

如图6所示,计算机系统600包括中央处理单元(central processing unit,cpu)601,其可以根据存储在只读存储器(read-only memory,rom)602中的程序或者从储存部分608加载到随机访问存储器(random access memory,ram)603中的程序而执行各种适当的动作和处理,例如执行上述实施例中所述的方法。在ram 603中,还存储有系统操作所需的各种程序和数据。cpu 601、rom 602以及ram 603通过总线604彼此相连。输入/输出(input/output,i/o)接口605也连接至总线604。

[0073]

以下部件连接至i/o接口605:包括键盘、鼠标等的输入部分606;包括诸如阴极射线管(cathode ray tube,crt)、液晶显示器(liquid crystal display,lcd)等以及扬声器等的输出部分607;包括硬盘等的储存部分608;以及包括诸如lan(local area network,局域网)卡、调制解调器等的网络接口卡的通信部分609。通信部分609经由诸如因特网的网络执行通信处理。驱动器610也根据需要连接至i/o接口605。可拆卸介质611,诸如磁盘、光盘、磁光盘、半导体存储器等等,根据需要安装在驱动器610上,以便于从其上读出的计算机程序根据需要被安装入储存部分608。

[0074]

特别地,根据本技术的实施例,上文参考流程图描述的过程可以被实现为计算机软件程序。例如,本技术的实施例包括一种计算机程序产品,其包括承载在计算机可读介质上的计算机程序,该计算机程序包含用于执行流程图所示的方法的计算机程序。在这样的实施例中,该计算机程序可以通过通信部分609从网络上被下载和安装,和/或从可拆卸介质611被安装。在该计算机程序被中央处理单元(cpu)601执行时,执行本技术的系统中限定的各种功能。

[0075]

需要说明的是,本技术实施例所示的计算机可读介质可以是计算机可读信号介质或者计算机可读存储介质或者是上述两者的任意组合。计算机可读存储介质例如可以是电、磁、光、电磁、红外线、或半导体的系统、装置或器件,或者任意以上的组合。计算机可读存储介质的更具体的例子可以包括但不限于:具有一个或多个导线的电连接、便携式计算机磁盘、硬盘、随机访问存储器(ram)、只读存储器(rom)、可擦式可编程只读存储器(erasable programmable read only memory,eprom)、闪存、光纤、便携式紧凑磁盘只读存储器(compact disc read-only memory,cd-rom)、光存储器件、磁存储器件、或者上述的任意合适的组合。在本技术中,计算机可读的信号介质可以包括在基带中或者作为载波一部分传播的数据信号,其中承载了计算机可读的计算机程序。这种传播的数据信号可以采用多种形式,包括但不限于电磁信号、光信号或上述的任意合适的组合。计算机可读的信号介

质还可以是计算机可读存储介质以外的任何计算机可读介质,该计算机可读介质可以发送、传播或者传输用于由指令执行系统、装置或者器件使用或者与其结合使用的程序。计算机可读介质上包含的计算机程序可以用任何适当的介质传输,包括但不限于:无线、有线等等,或者上述的任意合适的组合。

[0076]

附图中的流程图和框图,图示了按照本技术各种实施例的系统、方法和计算机程序产品的可能实现的体系架构、功能和操作。其中,流程图或框图中的每个方框可以代表一个模块、程序段、或代码的一部分,上述模块、程序段、或代码的一部分包含一个或多个用于实现规定的逻辑功能的可执行指令。也应当注意,在有些作为替换的实现中,方框中所标注的功能也可以以不同于附图中所标注的顺序发生。例如,两个接连地表示的方框实际上可以基本并行地执行,它们有时也可以按相反的顺序执行,这依所涉及的功能而定。也要注意的是,框图或流程图中的每个方框、以及框图或流程图中的方框的组合,可以用执行规定的功能或操作的专用的基于硬件的系统来实现,或者可以用专用硬件与计算机指令的组合来实现。

[0077]

描述于本技术实施例中所涉及到的单元可以通过软件的方式实现,也可以通过硬件的方式来实现,所描述的单元也可以设置在处理器中。其中,这些单元的名称在某种情况下并不构成对该单元本身的限定。

[0078]

本技术的另一方面还提供了一种计算机可读存储介质,其上存储有计算机程序,该计算机程序被计算机的处理器执行时,使计算机执行如前所述的时间同步方法。该计算机可读存储介质可以是上述实施例中描述的电子设备中所包含的,也可以是单独存在,而未装配入该电子设备中。

[0079]

本技术的另一方面还提供了一种计算机程序产品或计算机程序,该计算机程序产品或计算机程序包括计算机指令,该计算机指令存储在计算机可读存储介质中。计算机设备的处理器从计算机可读存储介质读取该计算机指令,处理器执行该计算机指令,使得该计算机设备执行上述各个实施例中提供的时间同步方法。

[0080]

上述实施例仅示例性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,但凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。