1.本发明涉及技术串行收发机领域,用于对串行收发机的信号进行前馈均衡,降低信号的误码率,具体为一种发送端及接收端的前馈均衡器抽头系数联合优化系统。

背景技术:

2.串行收发机面临的主要问题是发送端的高速信号经过信道的影响后,会存在各种各样的码间串扰,这将使信号的0/1之间的区分变得很困难,如果不对信号做均衡处理,那接收端接收的信号将会出现非常多的误码,为了降低传输信号的误码率,必须使用多种均衡器来消除带宽有限的信道脉冲响应中的各种类型的码间串扰;串行收发机的信号均衡手段可以分别从发送端和接收端来看,发送端主要的均衡手段是前馈均衡器,接收端主要的均衡手段有三种,分别是连续时间线性均衡放大器、前馈均衡器和判决反馈均衡器,接收端中的前馈均衡器和判决反馈均衡器根据接收端是基于slicer形式的,还是基于模数转换器形式的,可以分别通过模拟以及数字的方式实现,接收端中的前馈均衡器和判决反馈均衡器抽头系数通过最小均方算法自适应进行收敛,以应对不同信号损害的情况;然而发送端的前馈均衡器,由于不知道传输信道的损害情况,其抽头系数往往只能是预先设定,提前对发射的脉冲进行一定的预失真,以抵消信道带来的失真,但是这个预先设定的抽头系数并不一定是适合当前信道的传输特性,所以不能实现最佳的均衡效果。

技术实现要素:

3.本发明的目的在于提供一种发送端及接收端的前馈均衡器抽头系数联合优化系统,由于在高速通信链路中,均衡是必需的,尤其是铜质信道中,信号传输线表现出来的是低通滤波特性,传输过程中信道对信号的高频成分衰减大,低频成分衰减少,造成信号质量下降,如果不对信号进行均衡补偿,系统的误码率就会大大上升;前馈均衡器是高速串口系统中最常用的均衡技术,为了缓解接收端均衡的压力,通常高速串口系统的发送端会使用前馈均衡器技术对信号进行预均衡,发送端前馈均衡的两种基本类型是预加重和去加重,预加重技术在传输线的发送端增强信号的高频成分,以补偿高频分量在传输过程中的过大衰减;信号频率的高低主要是由信号电平变化的速度决定的,所以信号的高频分量主要出现在信号的上升沿和下降沿处,预加重技术就是增强信号上升沿和下降沿处的幅度;去加重技术的思想与预加重技术类似,只是实现方法有点不同,预加重是增加信号上升沿和下降沿处的幅度,其它地方幅度不变;而去加重是保持信号上升沿和下降沿处的幅度不变,其他地方信号减弱,去加重补偿后的信号摆幅比预加重补偿后的信号摆幅小,眼图高度低,功耗小,电磁辐射小。

4.为实现上述目的,本发明提供如下技术方案:发送端的前馈均衡方法,不管是使用预加重和去加重,都是通过有限冲激响应(finite impulse response,fir)滤波器实现的,

即将延时的信号按不同的权重(c0, c1, c2,

ꢀ…

, cn)相加,控制权重的大小即可调整均衡强度,前馈均衡器的实质是使用高通滤波器提高信号的高频分量,实现信道的补偿,滤波器系数表达式如下:相比于接收端前馈均衡器可以根据信道损耗和串扰特性自动收敛前馈均衡器抽头的系数,发送端的前馈均衡器由于缺少后续信道的信息,而无法设定最合适的系数大小,通常做法是预设一个系数大小组合,但是此方法可能并不能对信号做到一个最合适的均衡;在本发明中,发送端的前馈均衡器采用3阶抽头,分别为前抽头(pre-cursor),主抽头(main-cursor)和后抽头(post-cursor);接收端的前馈均衡器采用8个抽头,除了一个主抽头之外,还有多个前抽头和后抽头。在收发机全集成的系统中,接收端的前馈均衡器系数会根据信号的质量自动进行收敛,系数的大小可以反映信道对信号造成的损耗情况;能够通过一个系数反馈系统,将接收端前馈均衡器中的主抽头、主抽头的前一抽头和后一抽头的系数大小反馈给发送端的前馈均衡器的3阶抽头,从而发送端前馈均衡器3阶抽头的系数的设定就是依据当前信道下的情况来设定最优的情况,在发送端前馈均衡器系数设定完成后,再重新进行接收端前馈均衡器系数的收敛,因为此时发送端前馈均衡器已经达到最优设定,接收端的前馈均衡所需要提供的均衡能力就降低了,将大大降低系统整体的功耗。

5.本发明提出的一种发送端及接收端的前馈均衡器抽头系数联合优化系统,有益效果在于:1、本发明利用串行收发机中接收端的前馈均衡器自动收敛的抽头系数大小来帮助设定发送端的前馈均衡器抽头系数的大小,从而实现功耗更小、均衡效果更好的前馈均衡方案;2、本发明因为联合了发送端和接收端前馈均衡器的抽头系数,从而使发送端前馈均衡器抽头系数的设定更为适合当前应用中的信道损害情况,大大降低了均衡电路的功耗,提升了信号的均衡效果,降低信号的误码率。

附图说明

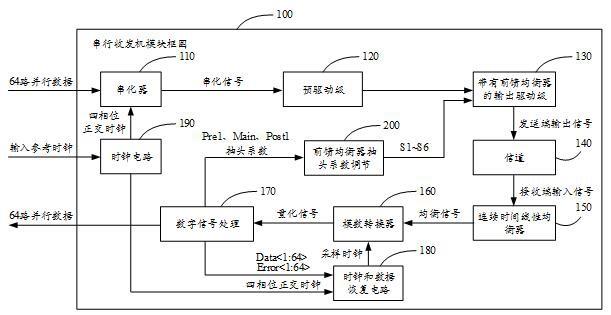

6.图1是本发明实施提供的串行收发机模块框图;图2是本发明实施提供的串化器的电路图;图3是本发明实施提供的预驱动级的电路图;图4是本发明实施提供的带有前馈均衡器的输出驱动级的电路图;图5是本发明实施提供的连续时间线性均衡器的电路图;图6是本发明实施提供的模数转换器的电路图;图7是本发明实施提供的数字信号处理模块的电路图;图8是本发明实施提供的时钟与数据恢复电路的电路图;

图9是本发明实施提供的时钟电路的电路图;图10是本发明实施提供的前馈均衡器抽头系数调节模块的电路图。

具体实施方式

7.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

8.请参阅图1,本发明提供一种技术方案:一种发送端及接收端的前馈均衡器抽头系数联合优化系统,该系统应用在芯片100上,该实施方式中输入的64路并行数据串化到1路串行信号以及发送端采用3抽头的前馈均衡器,不同速率分配方案下的其他数量的并行数据以及发送端不同抽头数量的前馈均衡器都可以采用本发明的发送端和接收端前馈均衡器的抽头系数联合优化系统;具体地,芯片中的对串行接收机中发送端和接收端前馈均衡器的抽头系数联合优化系统包括:串化器110、预驱动级120、带有前馈均衡器的输出驱动级130、信道140、连续时间线性均衡器150、模数转换器160、数字信号处理模块170、时钟和数据恢复电路180、时钟电路190和前馈均衡器抽头系数调节模块200。

9.在这一具体的实施例中,请参阅图2;串化器110包括64到4串化电路111,4到1串化电路112,3阶fir生成器113以及提供给串化电路相对应时钟的分频电路114,64到4串化电路111会接收数字系统传输过来的64路并行数据,并根据时钟信号对其依次进行串化,串化完成后的4路并行信号再送给4到1串化电路112,4到1串化电路112会将64到4串化电路111传输过来的4路并行信号继续串化,串化为1路串行信号,为了给最后含有3阶抽头的前馈均衡器提供输入信号,所以还需要通过3阶fir生成器生成pre串化信号、main串化信号和post串化信号,分频电路114接收时钟电路190送来的四相位正交时钟,并对其进行分频送给64到4串化电路111。

10.在这一具体的实施例中,请参阅图3;由于最后输出级的晶体管尺寸很大,而串化电路晶体管尺寸很小,可能无法驱动最后输出级的晶体管,所以需要预驱动级120对pre串化信号、main串化信号和post串化信号进行预驱动,预驱动级120采用尺寸逐级放大的反相器进行预驱动,每级反相器由一个pmos (p-metal-oxide

ꢀ‑

semiconductor,p型金属氧化物半导体)管和一个nmos (n-metal-oxide

‑ꢀ

semiconductor,n型金属氧化物半导体) 管构成;p1、p2、p3和p4的pmos管尺寸是逐级放大,n1、n2、n3和n4的nmos管尺寸是逐级放大,最后一级由p4和n4构成的反相器的尺寸就可以驱动最后的输出级了;反相器链中还加入了反馈电阻rf形成一个sub-ui (sub unit interval,亚单位间隔) 的均衡,提升反相器输出信号的上升速度。

11.在这一具体的实施例中,请参阅图4;带有前馈均衡器的输出驱动级130包括共模反馈电路131、电阻阵列132和电流模逻辑驱动级133;共模反馈电路131由共模提取电路1311和运算放大器1312组成;共模提取电路1311使用两个阻值很大的电阻r放置在电流模逻辑驱动级133的差分输出端voutp和voutn之间,提取出电流模逻辑驱动级133差分输出的共模电平vcm,并将这个共模电平vcm与基准电压产生电路设定的参考电压vref一起送给运

算放大器1312,运算放大器1312将输出一个偏置电压vb送给电流模逻辑驱动级133的共源共栅管,调节共源共栅管的偏置电压以调节电流模逻辑驱动级133的电流,使电流模逻辑驱动级133差分输出的共模电平vcm等于基准电压产生电路所设定的参考电压vref;因此,只需要调节vref的大小,就可以输出我们想要的电流模逻辑驱动级133的输出摆幅大小;而避免传统结构中,电流模逻辑驱动级133的输出摆幅大小是由电流和电阻的乘积决定;实际工艺的电阻如果没有进行校准,会有很大的偏差,如果任由电阻偏差产生,那电流模逻辑驱动级133的输出摆幅的准确度和输出阻抗匹配的性能就会大大折扣,电阻阵列132由电阻1321和开关1322组成,开关1322接收由电阻校准模块送来的电阻校准控制码,根据控制码来切换开关,开关1322的栅极信号为高电平1时,该pmos管关断,下方的电阻不产生作用;开关1322的栅极信号为低电平0时,该pmos管打开,下方的电阻被并联入总的电阻阵列中,最终的电阻值r由所有pmos开关打开的电阻共同并联获得,精确的电阻可以实现良好的阻抗匹配的效果;电流模逻辑驱动级133由预驱动后pre串化信号的电流模逻辑驱动级1331、预驱动后main串化信号的电流模逻辑驱动级1332和预驱动后post串化信号的电流模逻辑驱动级1333组成,形成一个3阶前馈均衡器的效果;基于共模反馈输出驱动级130的信号输入端会连接预驱动级120驱动后的高速串行信号,这个串行信号有三路信号,分别是预驱动后pre串化信号、预驱动后main串化信号和预驱动后post串化信号;这三路信号之间会有一个单位间隔的延迟,这三路信号都会接入到电流模逻辑驱动级133相对应的驱动级,但是每个信号所接的电流模逻辑驱动级的权重大小不一致,对于预驱动后main串化信号的电流模逻辑驱动级1332,其权重大小为16,对于预驱动后pre串化信号的电流模逻辑驱动级1331和预驱动后post串化信号的电流模逻辑驱动级1333,其权重大小有1,2,4三档;均衡选通开关接收外部输入的选通开关设置,通过s1到s6开关的打开或关断,就能够加入不同均衡档位的pre信号和post信号的电流模逻辑驱动级;如果将这三档全关,则没有均衡效果,仅仅是主路信号输出,如果将这三档全开,则达到最大的均衡效果;预驱动后pre串化信号,预驱动后main串化信号和预驱动后post串化信号电流模逻辑驱动级由输入差分对管、预充电对管和共源共栅管偏置对管构成,输入差分对管的栅极就是基于共模反馈输出驱动级130的信号输入端,连接着预驱动级120驱动后的高速串行信号,pre串化信号通路的输入为vin1和vin2, main串化信号通路的输入为vin3和vin4,post串化信号通路的输入为vin5和vin6;共源共栅管偏置对管的栅极接运算放大器1312的输出偏置电压vb,以调节电流模逻辑驱动级133的电流使电流模逻辑驱动级133差分输出的共模电平vcm等于基准电压产生电路所设定的参考电压vref;预驱动后main串化信号和预驱动后post串化信号。

12.在这一具体的实施例中,请参阅图5;连续时间线性均衡器150包括衰减器151、跨导级152和跨阻放大器153;信道140的传输特性是低通的,因此接收机收到的低频信号通常会有比较大的幅值,衰减器151通过交流源极退化的原理对不同频率的交流信号进行不同程度的衰减或者放大;传统的连续时间线性均衡器150通常在负载上通过电感与电阻进行串联的方式获得更高的高频增益,抵消掉后级输入寄生电容的影响;然而在集成电路中,使用电感通常都要牺牲非常大的版图面积;在本方案中,通过跨导级152和跨阻放大器153的设计等效出一个有源电感,拓展我们的带宽的同时带来了更多的灵活性;跨导级152的作用主要是通过pn互补形式的晶体管将输入电压转换成电流,这里我们通过调节电路并联个数

的方式进行输出电流调节;通过共模反馈调节电流管的偏置电压保证最后跨阻放大器153的输出共模处于模数转换器的量化电压的中间,保证系统处于最佳性能。

13.在这一具体的实施例中,请参阅图6;模数转换器160包括四个通道的逐次逼近型模数转换器161和8分频电路162;四个通道的逐次逼近型模数转换器161接收连续时间线性均衡器150送出的均衡信号;四个8分频电路162接收时钟和数据恢复电路180送来的采样时钟,并对采样时钟进行分频操作,并将分频后的时钟送给相对应的逐次逼近型模数转换器161,逐次逼近型模数转换器161按照分频时钟依次对均衡信号进行量化,并将量化完成的32路数字信号送给数字信号处理模块170。

14.在这一具体的实施例中,请参阅图7;数字信号处理模块170包括解串化器171、前馈均衡器172和判决反馈均衡器173;解串化器171接收模数转换器160送出的32路量化信号,并将其解串成64路量化信号;具有8个抽头系数的前馈均衡器172对64路量化信号进行均衡,将均衡后的64路量化信号送给判决反馈均衡器173,同时将主抽头以及主抽头的前一个抽头和后一个抽头的系数送给前馈均衡器抽头系数调节模块200;判决反馈均衡器173对接收的前馈均衡器172送来的均衡后的64路量化信号再进行判决反馈均衡,同时对信号进行判别,并将判决的结果输出,同时将时钟与数据恢复电路180所需的data《1:64》和error《1:64》传输过去。

15.在这一具体的实施例中,请参阅图8;时钟与数据恢复电路180包括mueller-muller相位探测器181、抽取模块182和比例路径增益模块183、积分路径增益模块184、频率积分器185、相位积分器186和相位插值器187;mueller-muller相位探测器181接收数字信号处理模块170传输过来的data《1:64》和error《1:64》信号,并进行判断,产生64路up或者down的信号,抽取模块182对64路up或者down的信号进行抽取,抽取为1路up或者down的信号。比例路径增益模块183、积分路径增益模块184和频率积分器185结合起来对1路up或者down的信号进行滤波;相位积分器186再将滤波结果进行积分得到相位插值器187的所需的相位选择;相位插值器187采用八边形相位插值的形式对时钟进行插值产生128个可选相位,并根据相位选择的结果选定相位,产生相应的采样时钟送给模数转换器160。

16.在这一具体的实施例中,请参阅图9;时钟电路190包括正交时钟产生电路191、占空比校准电路192、正交误差校准电路193、占空比/正交误差检测电路194和占空比/正交误差校准逻辑195;正交时钟产生电路191接收输入参考时钟,并产生四相位正交时钟,四相位正交时钟经过占空比校准电路192和正交误差校准电路193的校准后,会输出一个校准后的高质量的四相位正交时钟。同时这个四相位正交时钟会送回给占空比/正交误差检测电路194,对四相位时钟的占空比和正交误差情况进行检测,并将检测的结果送给占空比/正交误校准逻辑195,占空比/正交误校准逻辑195根据检测结果进行判断,进而调节占空比校准电路192和正交误差校准电路193的切换开关的数量,使输出的四相位正交时钟具有优秀的占空比和正交性能。

17.在这一具体的实施例中,请参阅图10;前馈均衡器抽头系数调节模块200包括系数译码器201;系数译码器201接收数字信号处理模块170中前馈均衡器172送出的pre1抽头系数、main抽头系数和post1抽头系数,并将其系数转换成发送端带有前馈均衡器的输出驱动级130中的s1-s6的开关信号;s1-s3的开关信号用来调节预驱动后pre串化信号的电流模逻辑驱动级1331的均衡大小,s4-s6的开关信号用来调节预驱动后post串化信号的电流模逻

辑驱动级1333的均衡大小;使发送端的3阶前馈均衡器的抽头系数设置成与接收端前馈均衡器相对应阶数的抽头系数一致,这样发送端的前馈均衡能力就更适合于当前的信道140的损耗情况,接收端数字实现的前馈均衡抽头系数就不需要提供那么大的均衡能力,进而减小了系统整体的功耗。

18.尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。