1.本公开涉及量子计算、自动化控制技术领域,尤其涉及一种基于射频开关的量子计算低延时反馈控制装置及方法。

背景技术:

2.在近二十年来,超导量子计算发展迅速,已进入含噪声中等规模量子计算阶段,处理器可集成量子比特数目达100左右,当量子比特可集成数目上升到上千个时,就进入了容错量子计算阶段,这也是实现通用量子计算的关键阶段。

3.容错量子计算要求能够实现基于量子比特测量结果的反馈控制,根据实时测量结果,动态调整后续量子线路。由于量子比特具有有限的寿命,要在有限的时间内完成尽可能多的量子门操作,这就需要尽可能降低反馈控制环路的电子学系统延时,该指标约为量子比特寿命的1/100。目前比特寿命约为几十微秒,因此电子学反馈延时需控制在百纳秒量级。此外,目前量子比特均采用自然弛豫的方式来达到实验前的初始态,该方法效率较低,基于反馈控制的量子比特主动重置可大大提升量子初态制备效率。

4.目前量子计算反馈控制方法的技术方案中,基本采用低延时daq模块(fpga adc)和低延时awg模块(fpga lvds协议类型dac)实现。lvds协议类型dac延时较低,可以较快响应量子比特测量结果,该方案可实现约100纳秒的反馈延时。但是lvds类型的dac芯片会占用较多的fpga接口,使得单片fpga能够挂载的dac芯片数量有限,无法做到高集成度。而jesd 204协议类型的dac芯片仅通过约1-8个fpga高速接口即可实现数据高速通信,单片fpga可挂载更多数量的dac芯片,与lvds协议类型相比,该数量可提高2-3倍。但是仅jesd 204协议的时间开销就高达200纳秒,大大增加了电子学反馈延时。

技术实现要素:

5.(一)要解决的技术问题

6.基于上述问题,本公开提供了一种基于射频开关的量子计算低延时反馈控制装置及方法,以缓解现有技术中量子计算反馈控制方法的技术方案中fpga接口资源占用较多或反馈延时较长等技术问题。

7.(二)技术方案

8.本公开的一个方面,提供一种基于射频开关的量子计算低延时反馈控制装置,包括:读取awg(arbitrary waveform generator,任意波形发生器),通过传输线与量子芯片相连,并被配置成用于发出读取激励波形;daq模块,通过传输线与量子芯片相连,并被配置成采集所述读取激励波形与量子比特读取腔耦合后生成的读取反馈波形并解模出量子态信息,同时所述daq(data acquisition,数据采集系统)模块被配置成根据实时的量子态信息生成不同时序的高低电平控制信号;控制awg,被配置成用于按设定时序发出初始反馈控制波形;以及射频开关,通过传输线分别与所述daq模块、控制awg、以及量子芯片相连,所述射频开关被配置成在所述高低电平控制信号的作用下通断,从而使得所述初始反馈控制波

形响应于射频开关的通断得到最终反馈控制波形作用于量子芯片。

9.根据本公开实施例,初始反馈控制波形包括多种适用于不同量子态信息的反馈波形。

10.根据本公开实施例,控制awg被配置成还用于按设定时序发出多种实验线路波形。

11.根据本公开实施例,daq模块中包括用于实现高低电平控制信号的时序管理器。

12.根据本公开实施例,时序管理器包括:空闲状态、开始状态、运行状态和结束状态四种不同的状态。

13.根据本公开实施例,在开始状态中进行初始化操作;在运行状态中根据不同的量子态信息,通过不同的反馈波形执行反馈控制;在结束状态中,进行反馈结果校验并关断射频开关。

14.根据本公开实施例,daq模块对读取反馈波形进行一定时间的积分解模得到量子态信息。

15.根据本公开实施例,初始反馈控制波形到达射频开关的时间和射频开关响应不同量子态信息的高低电平控制信号的时间是对齐的。

16.本公开的另一方面,提供一种基于射频开关的量子计算低延时反馈控制方法,包括:操作s1:通过读取awg发出读取激励波形;操作s2:通过daq模块采集所述读取激励波形与量子比特读取腔耦合后生成的读取反馈波形并解模出量子态信息,同时根据实时的量子态信息生成不同时序的高低电平控制信号;操作s3:使控制awg按设定时序发出初始反馈控制波形;以及操作s4:使射频开关在所述高低电平控制信号的作用下通断,从而使得所述初始反馈控制波形响应于射频开关的通断得到最终反馈控制波形作用于量子芯片。

17.(三)有益效果

18.从上述技术方案可以看出,本公开基于射频开关的量子计算低延时反馈控制装置及方法至少具有以下有益效果其中之一或其中一部分:

19.(1)能够在低于100纳秒的时间里完成量子态信息反馈控制;

20.(2)在不同量子态信息情况下,射频开关的通断状态不同,从而允许不同的反馈波形最终作用到量子比特上。

附图说明

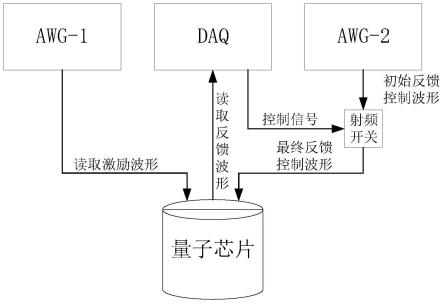

21.图1是本公开实施例的基于射频开关的量子计算低延时反馈控制装置的示意图;

22.图2是本公开实施例的时序管理器的状态示意图;

23.图3是本公开实施例的射频开关控制逻辑示意图;

24.图4是本公开实施例的基于单次反馈的量子比特主动重置波形示意图;

25.图5是本公开实施例的基于射频开关的量子计算低延时反馈控制方法流程示意图。

具体实施方式

26.本公开提供了一种基于射频开关的量子计算低延时反馈控制装置及方法,提出利用低延时射频开关响应量子比特测量结果,在不同测量结果反馈情况下,射频开关处于不同通断状态,从而实现反馈控制波形有选择性地输出给量子比特,因此使jesd 204协议类

型的dac芯片在低于100纳秒的时间里完成量子态信息反馈控制,并提出其具体的实现方法。

27.为使本公开的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本公开进一步详细说明。

28.在本公开实施例中,提供一种基于射频开关的量子计算低延时反馈控制装置,如图1所示,所述反馈控制装置,包括:读取awg(awg-1),daq模块,控制awg(awg-2),射频开关。

29.读取awg通过传输线与量子芯片相连,并被配置成用于发出读取激励波形;

30.daq模块通过传输线与量子芯片相连,并被配置成采集所述读取激励波形与量子比特读取腔耦合后生成的读取反馈波形并解模出量子态信息,同时所述daq模块被配置成根据实时的量子态信息生成不同时序的高低电平控制信号;

31.控制awg被配置成用于按设定时序发出初始反馈控制波形;

32.射频开关通过传输线分别与所述daq模块、控制awg、以及量子芯片相连,所述射频开关被配置成在所述高低电平控制信号的作用下通断,从而使得所述初始反馈控制波形响应于射频开关的通断得到最终反馈控制波形作用于量子芯片。

33.根据本公开实施例,所述量子芯片包括量子比特和量子比特读取腔。

34.根据本公开实施例,结合图4所示,所述初始反馈控制波形包括多种适用于不同量子态信息的反馈波形(图中示出两种反馈波形)。所述控制awg同时按设定时序发出多种实验线路波形(图中示出三种实验线路波形),需要指出的是,上述反馈波形或实验线路波形的种类仅是示例性说明,可以根据实际应用进行调整。

35.综上,awg-1和daq组成了量子比特的测量系统,由awg-1产生读取激励波形,该波形与量子比特读取腔耦合作用后作为读取反馈波形被daq采集,并解模出量子态信息。daq模块根据不同的量子态信息,产生不同时序的高低电平控制信号,该控制信号能够直接用于控制射频开关。控制awg模块产生的波形序列与量子态信息完全解耦,无论量子比特测量结果如何,控制awg都会在指定的时序下提前准备生成各种反馈控制波形,使初始反馈控制波形到达射频开关的时间和射频开关响应量子态信息的时间是对齐的。在不同量子态信息情况下,射频开关的通断状态不同,从而允许不同的反馈波形最终作用到量子芯片的量子比特上。在该结构下,负责产生反馈控制波形的awg-2只需要按照一定时序静态产生波形序列。

36.根据本公开实施例,时序管理器分为四种状态包括:分别是空闲状态st_idle、开始状态st_start、运行状态st_run和结束状态st_end四种不同的状态。在st_start状态,主要进行各寄存器值、开关控制信号的初始化;在st_run状态,等待响应有效的测试结果,执行反馈控制;在st_end状态,进行反馈结果校验并拉低开关控制信号。时序管理器的状态及跳转详细情况如图2及表1所示。

37.表1

[0038][0039]

本公开的技术方案中的关键是确保射频开关能够有效、准确地响应测量结果,这既包含了开关状态的准确性,又包含了开关时序的准确性。本公开在daq模块中实现射频开关控制信号的时序管理器,在awg模块中生成初始反馈控制波形和其余实验线路波形,具体实现可描述为以下步骤:

[0040]

(1)配置相关逻辑控制参数和各种波形数据,参数包括测量结果响应次数m、开关延时复位时间t、不同反馈控制波形的长度len1/len2/len3...,波形数据包括初始反馈控制波形数据和正常实验线路波形数据;

[0041]

(2)在量子线路开始时,开关控制信号导通开关模块,并等待响应测量结果;

[0042]

(3)根据有效测量结果和awg预生成的反馈控制波形的时序关系,产生相应时序的高低电平开关控制信号,从而使awg产生的多种反馈控制波形有选择地通过开关模块;

[0043]

(4)成功响应一次测量结果后,响应次数m-1;

[0044]

(5)当m=0时,已完成全部反馈控制,为了确保反馈线路后的实验线路波形能正常通过开关模块,延时t时间后,开关控制信号再次导通开关模块;

[0045]

(6)在该条量子线路结束后,开关控制信号关断开关模块,执行完一个完整的量子线路。

[0046]

根据本公开实施例,结合图3所示,测量结果响应次数m=3,表示会执行3次反馈控制。当一条线路开始时,时序管理器由st_idle状态跳转至st_start状态,并加载测量结果响应次数m等寄存器值。随后时序管理器直接跳转至st_run状态,在该阶段,时序管理器会等待有效测量结果,每当收到一次有效测量结果,时序管理器会根据测量结果和各寄存器值生成特定时序的开关控制信号。当m=0时,时序管理器延时t时间后拉高开关控制信号。当这条线路执行完毕后,时序管理器跳转至st_end状态,进行反馈结果校验并关断开关模块。在多条量子线路之间,时序管理器一直处于st_idle状态,并保持关断开关模块。图4以基于单次反馈的量子比特主动重置为例演示了反馈控制的整个流程。awg-1生成读取激励波形,daq经过一定时间的积分解模后得到量子态信息,不同的量子态信息会产生不同的控制信号。如图所示,根据测量结果是状态1、2、3三种状态,射频开关会收到三种不同的控制信号。而awg-2无论测量结果是哪个状态,都只会按照一定时序产生一个静态的波形序列,包含所有的反馈波形和实验波形。具体哪个反馈波形能够最终作用到量子比特上,就完全由射频开关控制。假设在基于反馈的量子比特主动重置实验中,当测量到量子态信息为状态1时,表明不需要对量子比特进行任何复位操作,那么当awg-2产生的反馈波形到达射频开关时,开关会处于关闭状态,反馈波形无法通过开关,最终作用到量子比特上的只有后续

(and)或“且”(and)特征乙,是指甲与乙同时存在;所谓的“包括”、“包含”、“具有”、“含有”,是指包括但不限于此。

[0060]

此外,在本文中,所谓的“上”、“下”、“左”、“右”、“前”、“后”、或“之间”等用语,只是用于描述多个元件之间的相对位置,并在解释上可推广成包括平移、旋转、或镜像的情形。此外,在本文中,除了特别指明的之外,“一元件在另一元件上”或类似叙述不必然表示该元件接触该另一元件。

[0061]

此外,除非特别描述或必须依序发生的步骤,上述步骤的顺序并无限制于以上所列,且可根据所需设计而变化或重新安排。并且上述实施例可基于设计及可靠度的考虑,彼此混合搭配使用或与其他实施例混合搭配使用,即不同实施例中的技术特征可以自由组合形成更多的实施例。

[0062]

以上所述的具体实施例,对本公开的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本公开的具体实施例而已,并不用于限制本公开,凡在本公开的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。