1.本发明总体来说涉及一种用于优化晶片中的电子装置芯片的保护电路的方法。更确切地说,本发明涉及一种用于晶片中的基于氮化物的电子装置芯片的保护电路的晶片级优化方法。

背景技术:

2.诸如氮化镓(gan)的宽带隙材料已广泛用于大功率和高频装置,这是因为其与硅(si)金属氧化物半导体(mos)材料相比具有更低电力损耗和快速切换过渡速度。举例来说,gan场效应晶体管(fet)已广泛用于制造移动装置的快速充电器中的电力装置。因为基于氮化物的晶体管具有较低阈值电压,所以其容易受到例如静电放电(esd)等高电压损害的影响。常规地,可用如图1中所示的保护电路保护基于氮化物的晶体管qm。保护电路可包含放电控制晶体管qdis和串联连接在主晶体管的栅极与放电控制晶体管的栅极之间的数个整流器d1、d2、

…

。放电控制晶体管qdis的阈值电压应被控制在所要范围内以确保保护电路的有效性。如果放电控制晶体管的阈值电压过高,那么保护电路无法及时被激活以保护主晶体管免受过电压损坏。如果放电控制晶体管的阈值电压过低,那么放电控制晶体管将容易被突破。此外,所需整流器的数目取决于主晶体管qm的阈值电压。通常,主晶体管qm的阈值电压越高,则需要更大数目的整流器。随着晶片大小增大,难以维持整个晶片的处理条件和参数一致,从而产生阈值电压非一致性。举例来说,在同一设计值下,形成于晶片的中心区域中的晶体管的阈值电压可低于形成于晶片的外围区域中的那些晶体管。

技术实现要素:

3.本发明的一个目标是提供一种用以解决上述晶片内的非均匀阈值电压分布问题以便提高制造良率的低本高效的方法。

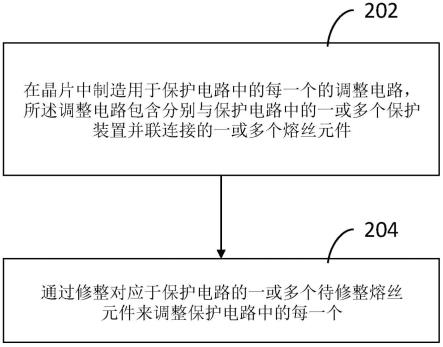

4.根据本公开的一个方面,提供一种用于晶片中的基于氮化物的电子装置芯片的保护电路的晶片级优化方法。所述方法包括:在晶片中制造用于保护电路中的每一个的调整电路,所述调整电路包含分别与保护电路中的一或多个保护装置并联连接的一或多个熔丝元件;以及通过修整对应于保护电路的一或多个待修整熔丝元件来调整保护电路中的每一个。通过在晶片上施加光致抗蚀剂层;用一比一(1:1)光掩模对光致抗蚀剂层进行图案化以暴露待修整熔丝元件;以及蚀刻掉待修整熔丝元件来执行待修整熔丝元件的修整。

5.通过使用1:1光掩模,可实现完整晶片覆盖度而无需在光柱下反复将晶片从一个位置移到另一个位置。因此,可极大地减小光掩模对准的复杂性,且可最小化曝光误差。

附图说明

6.通过参考附图从以下详细描述可以容易地理解本公开的各方面。图解可能未必按比例绘制。也就是说,为了论述清楚起见,各种特征的尺寸可以任意增大或减小。由于制造工艺和公差,本公开中的工艺再现与实际设备之间可能存在区别。为简单起见,可在整个图

式和具体实施方式中使用共同参考标号来指示相同或类似组件。

7.图1展示晶片中的电子装置芯片的典型保护电路的电路图;

8.图2展示根据本发明的一些实施例的用于晶片中的基于氮化物的电子装置芯片的保护电路的晶片级优化方法的流程图;

9.图3展示根据本发明的一些实施例的在执行用于保护电路的晶片级优化方法之前的晶片中的基于氮化物的电子装置芯片的示范性电路;以及

10.图4展示根据本发明的一些实施例的在执行用于保护电路的晶片级优化方法之后的晶片中的基于氮化物的电子装置芯片的示范性电路。

具体实施方式

11.在以下描述中,将阐述本公开的优选实例作为应被视为说明性而非限制性的实施例。可以省略特定细节以免使本公开模糊不清;然而,编写本公开是为了使所属领域的技术人员能够在不进行不当实验的情况下实践本文中的教示。

12.图2展示根据本发明的一些实施例的用于晶片中的基于氮化物的电子装置芯片的保护电路的晶片级优化方法的流程图。每一基于氮化物的电子装置芯片可包含基于氮化物的主晶体管和经配置以用于保护基于氮化物的主晶体管免于高电压损坏的保护电路。举例来说,保护电路可为经配置以用于保护晶体管免受esd损坏的esd保护电路。保护电路可包含放电控制晶体管和串联连接在主晶体管的栅极与放电控制晶体管的栅极之间的多个保护装置。

13.如图2中所展示,所述方法可包括以下步骤:

14.s202:在晶片中制造用于保护电路中的每一个的调整电路,所述调整电路包含分别与保护电路中的一或多个保护装置并联连接的一或多个熔丝元件;

15.s204:通过修整对应于保护电路的一或多个待修整熔丝元件来调整保护电路中的每一个。

16.在一些实施例中,可通过以下操作来执行待修整熔丝元件的修整:在晶片上施加光致抗蚀剂层;用一比一(1:1)光掩模(即,具有1x光掩模放大倍数)对光致抗蚀剂层进行图案化以暴露待修整熔丝元件;以及蚀刻掉待修整熔丝元件。

17.基于晶片的阈值电压分布形成1:1光掩模以暴露待修整熔丝元件。确切地说,可基于阈值电压分布将晶片分成一或多个区域。因此,可形成光掩模,使得包含较低阈值电压的晶体管的区域中用于保护电路的待修整熔丝元件的数量大于包含较高阈值电压的晶体管的区域中用于保护电路的待修整熔丝元件的数量。

18.在一些实施例中,可仅在形成熔丝元件之后执行待修整熔丝元件的修整。在一些实施例中,在将钝化层沉积在熔丝元件的顶部上之后,可执行待修整熔丝元件的修整。因而,除了那些待修整熔丝元件外的结构可在修整过程期间由钝化层保护。

19.在一些实施例中,熔丝元件可由多晶硅制成。在一些实施例中,熔丝元件可由包含但不限于以下各者制成:钛(ti)、钽(ta)、钨(w)、铝(al)、钴(co)、铜(cu)、镍(ni)、铂(pt)、铅(pb)、钼(mo)和其化合物(例如但不限于氮化钛(tin)、氮化钽(tan)、其它导电氮化物或导电氧化物)、金属合金(例如铝铜合金(ai-cu)),或其它适当材料。

20.图3展示根据本发明的一些实施例的在执行用于保护电路的晶片级优化方法之前

的晶片3中的基于氮化物的电子装置芯片的示范性电路。如图3所示,可基于阈值电压分布将晶片3分成一或多个区域30_1、

…

、30_n,其中n为区域的数目。举例来说,区域30_1可包含多个电子装置芯片300_1,每一电子装置芯片包括基于氮化物的主晶体管qm_1,区域30_2可包含多个电子装置芯片300_2,每一电子装置芯片包括基于氮化物的主晶体管qm_2、

…

且区域30_n可包含多个电子装置芯片300_n,每一电子装置芯片包括基于氮化物的主晶体管qm_n。

21.晶片的阈值电压分布可随距晶片的中心的距离而变。举例来说,位于晶片的中心区域内的区域30_1中的基于氮化物的主晶体管qm_1可具有相对低的阈值电压vth1。位于晶片的最外外围区域中的区域30_n中的基于氮化物的主晶体管qm_n可具有相对较高的阈值电压vthn。

22.在一些实施例中,阈值电压值vth_i(i=1、2、

…

、n)之间的关系可由vth

i 1

=vthi δv给出,其中δv为位于任何两个邻近区域中的晶体管的阈值电压值之间的差。

23.可用保护电路320_1保护基于氮化物的主晶体管qm_1中的每一个。保护电路320_1可包含放电控制晶体管q

dis_1

和串联连接在主晶体管qm_1的栅极与放电控制晶体管q

dis_1

的栅极之间的多个整流器d

1_1

、d

1_2

、

…

、d

1_m

。多个整流器d

1_1

、d

1_2

、

…

、d

1_m

可包含第一整流器d

1_1

和最后一个整流器d

1_m

,所述第一整流器的阳极连接到主晶体管qm_1的栅极,所述最后一个整流器的阴极连接到放电控制晶体管q

dis_1

的栅极。

24.电子装置芯片300_1中的每一个可进一步具有调整电路,所述调整电路包含分别与保护电路中的一或多个整流器并联连接的一或多个熔丝元件f

1_1

、f

1_2

、

…

、f

1_k

,其中k为熔丝元件的数目。在一些实施例中,k可等于m,也就是说,所有整流器d

1_1

、d

1_2

、

…

、d

1_m

分别与熔丝元件并联连接以用于电路优化。在其它实施例中,k可小于m,也就是说,整流器d

1_1

、d

1_2

、

…

、d

1_m

中只有一部分分别与熔丝元件并联连接以用于电路优化。

25.类似地,可用保护电路320_n保护基于氮化物的主晶体管qm_n中的每一个。保护电路320_n可包含放电控制晶体管q

dis_n

和串联连接在主晶体管qm_n的栅极与放电控制晶体管q

dis_n

的栅极之间的一或多个整流器d

n_1

、d

n_2

、

…

、d

n_m

。多个整流器d

n_1

、d

n_2

、

…

、d

n_m

可包含第一整流器d

n_1

和最后一个整流器d

n_m

,所述第一整流器的阳极连接到主晶体管qm_n的栅极,所述最后一个整流器的阴极连接到放电控制晶体管q

dis_n

的栅极。

26.电子装置芯片300_n中的每一个可进一步具有调整电路,所述调整电路包含分别与保护电路中的一或多个整流器并联连接的一或多个熔丝元件f

n_1

、f

n_2

、

…

、f

n_k

,其中k为熔丝元件的数目。在一些实施例中,k可等于m,也就是说,所有整流器d

n_1

、d

n_2

、

…

、d

n_m

分别与熔丝元件并联连接以用于电路优化。在其它实施例中,k可小于m,也就是说,整流器d

n_1

、d

n_2

、

…

、d

n_m

中只有一部分分别与熔丝元件并联连接以用于电路优化。

27.在一些实施例中,主晶体管中的每一个可为algan/gan增强型(e型)高电子迁移率晶体管(hemt)。

28.在一些实施例中,放电控制晶体管中的每一个可为algan/gan增强型(e型)高电子迁移率晶体管(hemt)。

29.在一些实施例中,整流器中的每一个可包括具有与源极短接以充当整流器的阳极的栅极和充当整流器的阴极的漏极的晶体管。晶体管中的每一个可为algan/gan增强型(e型)高电子迁移率晶体管(hemt)。

30.图4展示在执行用于保护电路的晶片级优化方法之后的晶片3中的基于氮化物的电子装置芯片的示范性电路。如图所示,保护电路302_n中没有熔丝元件已经修整以用于保护晶体管qm_n,同时已从保护电路302_1去除或蚀刻掉用于保护晶体管qm_1的两个熔丝元件f

1_1

和f

1_2

,所述晶体管qm_1的阈值电压低于晶体管qm_n。

31.如从图3和4中的实例可以看出,通过执行用于保护电路的晶片级优化方法,调整保护电路中的每一个经调整以使得包含较低阈值电压的晶体管的区域中用于保护电路的已修整熔丝元件的数量大于包含较高阈值电压的晶体管的区域中用于保护电路的已修整熔丝元件的数量。应理解,图3和4中所示的示例性电路仅出于说明性目的。用于每一保护电路的待修整熔丝元件的数目可为任何合适的数目。

32.选择和描述实施例是为了最好地解释本发明的原理及其实际应用,由此使得所属领域的其他技术人员能够理解本发明的各种实施例以及适合于所预期的特定用途的各种修改。虽然本文中所公开的方法已参考按特定次序执行的特定操作加以描述,但应理解,可在不脱离本公开的教示的情况下对这些操作进行组合、细分或重新排序以形成等效方法。因此,除非在本文中具体指示,否则操作的次序及分组并非限制性的。虽然本文中公开的设备已参考特定结构、形状、材料、物质组成和关系等等加以描述,但这些描述和说明并非限制性的。可作出修改以使特定情形适用于本公开的目标、精神和范围。所有此类修改旨在处于所附权利要求的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。