1.本发明总体上涉及分组通信,并且具体涉及用于网络设备中的出站分组的准确加时间戳的方法和系统。

背景技术:

2.在各种应用中,网络设备对其接收、发送或转发的分组加时间戳。例如,在将网络节点同步到公共时基的时间同步协议中使用加时间戳。这种协议的常见示例是ieee标准1588-2002和1588-2008中定义的精确时间协议(ptp)及其后续版本。

技术实现要素:

3.本文描述的本发明的实施例提供一种网络设备,包括端口、传输管线和加时间戳电路。所述端口被配置用于连接到网络。所述传输管线包括多个管线级,并且被配置为处理分组以及经由所述端口将所述分组发送至所述网络。加时间戳电路被配置为:暂时中止传输管线中的至少给定分组的至少一些处理;验证位于加时间戳电路下游的具有可变处理延迟的管线级是否满足空置条件;以及仅当管线级满足空置条件时,对给定分组加时间戳并恢复对给定分组的处理。

4.在一些实施例中,具有可变处理延迟的管线级是具有可变占用级别的缓冲区。

5.在一些实施例中,加时间戳电路被配置为支持:(i)正常模式,在所述正常模式中,不管所述管线级是否满足所述空置条件而对分组加时间戳;和(ii)高准确度模式,在所述高准确度模式中,仅当所述管线级满足所述空置条件时,对分组加时间戳。在示例实施例中,加时间戳电路被配置为仅将所述高准确度模式应用于选定的分组。在另一实施例中,加时间戳电路被配置为仅将所述高准确度模式应用于时间同步分组。在又一实施例中,加时间戳电路被配置为仅在所述端口不受到来自所述网络的背压时应用所述高准确度模式。

6.在实施例中,加时间戳电路被配置为自适应地修改所述空置条件的严格性。在所公开的实施例中,加时间戳电路被配置为通过自适应地修改空置条件来调整加时间戳电路的加时间戳准确度直至达到目标准确度。在示例实施例中,加时间戳电路被配置为:当给定分组与第一应用相关联时,应用具有第一严格性的第一空置条件;以及当给定分组与第二应用相关联时,应用具有第二严格性的第二空置条件。

7.在另一实施例中,加时间戳电路被配置为将具有不同的第一和第二严格程度的第一和第二空置条件应用于同一应用的不同的第一和第二给定分组。在又一实施例中,加时间戳电路被配置为响应于检测到端口受到来自网络的背压而应用经修改的空置条件。在又一实施例中,加时间戳电路被配置为根据连接到端口的网络链路的链路速度来设置空置条件。

8.在实施例中,加时间戳电路被配置为通过从管线级接收状态指示来验证管线级是否满足空置条件。在示例实施例中,加时间戳电路被配置为通过在所述传输管线中的处理被中止时等待一持续时间来验证所述管线级是否满足所述空置条件。

9.在公开的实施例中,加时间戳电路被配置为将所述管线级的空置程度报告给所述网络设备的处理器。在实施例中,加时间戳电路被配置为应用故障保护机制,该故障保护机制限制中止传输管线中的处理的最大程度。

10.在一些实施例中,所述传输管线和所述加时间戳电路被配置为处理用于多个主机的分组。在示例实施例中,加时间戳电路被配置为将空置条件的第一设置应用于主机中的第一主机,并且将空置条件的不同于第一设置的第二设置应用于主机中的第二主机。在另一实施例中,加时间戳电路被配置为针对所述主机中的第一主机执行所述空置条件的第一类型验证,并且针对所述主机中的第二主机执行所述空置条件的不同于所述第一类型的第二类型验证。

11.在又一实施例中,给定分组源自主机之中的给定主机,并且加时间戳电路被配置为暂时停顿源自除了给定主机之外的主机的分组的处理,以便使管线级能够满足用于对给定分组加时间戳的空置条件。在又一实施例中,加时间戳电路被配置为禁止中止源自主机之中的给定主机的至少一些分组。

12.在实施例中,加时间戳电路被配置为将时间戳插入到给定分组中,并且具有可变处理延迟的管线级是被配置为对包括所插入的时间戳的给定分组进行加密的加密引擎。

13.根据本发明的实施例,还另外提供了一种网络设备中的方法。所述方法包括:使用所述网络设备中的传输管线,处理分组并且将所述分组发送至网络,所述传输管线包括多个处理级。使用所述网络设备中的加时间戳电路,(i)暂时中止所述传输管线中的至少给定分组的至少一些处理,验证位于所述加时间戳电路下游的具有可变处理延迟的管线级是否满足空置条件,以及(iii)仅当所述管线级满足所述空置条件时,对所述给定分组加时间戳并且恢复对所述给定分组的处理。

附图说明

14.从下面结合附图对本发明实施例的详细描述,将更充分地理解本发明,其中:

15.图1是示意性地示出了根据本发明的实施例的以高精度对出口分组加时间戳的网络设备的框图;

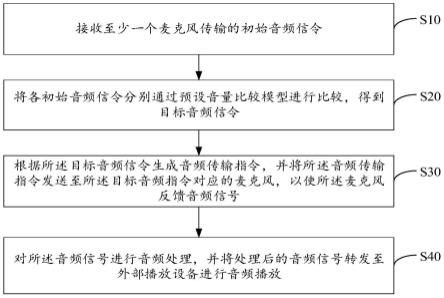

16.图2是示意性地示出了根据本发明的实施例的用于出口分组的准确加时间戳的方法的流程图;以及

17.图3是示出了根据本发明的实施例的在加时间戳准确度与空置条件严格性之间的示例关系的曲线图。

具体实施方式

18.概述

19.本文描述的本发明的实施例提供了用于网络设备中的出站(出口)分组的精确加时间戳的方法和装置。本文描述的实施例主要涉及网络适配器中的实施,但所公开的技术也适用于网络交换机和需要准确加时间戳的其他类型的网络设备。

20.通常,网络设备包括处理分组并且经由出口端口将它们传输到网络的传输(tx)管线。为了利用出口时间准确地对分组加时间戳,期望在管线的尽可能靠近出口端口的点处对分组加时间戳。然而,在许多实际实现方式中,一个或更多个处理级仍然保持在加时间戳

点的下游,即在加时间戳点与出口端口之间。

21.如果这些中间处理级的延时是固定的,则这些中间处理级不太成问题,因为这个延时可以在时间戳中被校准和补偿。另一方面,具有可变延时的中间处理级是有问题的,因为它们向时间戳添加可变抖动并且降低它们的准确度。例如,2021年5月10日提交的美国专利申请17/315,396中解决了涉及时间戳中的时间抖动的估计的方面,其公开内容以引用方式并入本文。

22.例如,位于加时间戳点和出口端口之间的任何缓冲区或队列将向时间戳添加可变延时,因为缓冲区或队列的延时根据其占用级别而改变。为了清楚和简洁起见,以下描述指的是“缓冲区”。然而,在本公开的上下文中并且在权利要求中,术语“缓冲区”广泛地指暂时地存储分组、分组的部分、或与分组相关联的描述符、指针或元数据的各种类型的存储器、寄存器或数据结构。例如,各个队列在本文中也被视为缓冲区。缓冲区的使用可具有任何合适的生产者/消费者语义(例如,写入到缓冲区中的实体可以是从缓冲区读取的相同实体,或不同实体;缓冲区可具有多个生产者和/或多个消费者;将项目写入到缓冲区中的顺序可与从缓冲区读出的顺序相同,或不同顺序;等等)。

23.管线中的其他类型的处理级也可具有可变的处理延迟,且因此可影响加时间戳准确度。这样的处理级的示例包括但不限于诸如ipsec引擎和macsec引擎之类的加密引擎。下面的描述通过示例的方式主要指的是缓冲区,但所公开的技术可应用于各种其他类型的处理级。术语“管线级”和“处理级”在此可互换地使用。

24.在本发明的一些实施例中,网络设备包括加时间戳电路,即使tx管线包括位于加时间戳点下游的缓冲区,加时间戳电路也以高准确度对出口分组加时间戳。(术语“在加时间戳点的下游”和“在加时间戳电路的下游”在本文中可互换地使用。)

25.在一些实施例中,为了准确地对给定分组加时间戳,加时间戳电路确保在加时间戳的时间,位于加时间戳点下游的缓冲区足够空。以此方式,加时间戳电路为给定分组基本上清除了管线中的低抖动路径。加时间戳电路可以验证关于缓冲区的各个空置条件,例如,缓冲区是完全空的、缓冲区的占用级别低于阈值等。空置条件通常为使得当满足时,缓冲区的延时抖动足够小从而实现所要求的加时间戳准确度。

26.在一些实施例中,加时间戳电路通过暂时中止管线中的处理的至少一部分(例如,中止缓冲区上游的处理,至少给定分组和可能的所有分组)来主动地使缓冲区排空和变空。然后,加时间戳电路验证缓冲区是否满足空置条件。仅当缓冲区满足空置条件时,加时间戳电路才对给定分组加时间戳并恢复管线处理。

27.加时间戳电路可以使用各种技术(直接或间接地)来评估缓冲区是否满足空置条件。在一些实施例中,加时间戳电路从缓冲区接收明确的填充状态指示。在其他实施例中,在管线处理被时,加时间戳电路等待定义的持续时间。也可以使用这两种技术的组合。

28.如可了解的,管线中的处理的中止可导致性能的一些下降,例如平均传输延时和吞吐量。因此,在一些实施例中,加时间戳电路选择性地应用所公开的技术,即,仅应用于选定的分组。例如,高准确度的加时间戳可仅应用于时间同步分组,例如,ptp分组。

29.减少可能由所公开的技术引起的性能的可能下降的另一方式是自适应地修改空置条件的严格性以匹配特定需要。例如,一些分组类型或应用可能需要比其他分组类型或应用更高准确度的加时间戳,并且因此需要更严格的空置条件。对于其他分组类型或应用,

更宽松的空置条件可能就足够了。由于性能下降通常随着空置条件的严格性而增长,因此这种自适应方法可以在加时间戳准确度和通信性能之间实现更好的折衷。

30.即使在存在具有大延时抖动的缓冲区(例如,几百纳秒或几微秒的数量级上)的情况下,本文描述的方法和装置也实现高度准确的加时间戳(例如,在几纳秒的数量级上)。

31.本文描述了所公开的技术的各种实现选项和使用情况。还解决了其中网络设备服务于多个主机的多主机配置的方面。

32.系统描述

33.图1是示意性地示出了根据本发明的实施例的以高准确度对出口分组加时间戳的网络设备20的框图。在本示例中,网络设备20是网络适配器,例如,以太网nic、infiniband

tm

主机通道适配器(hca)、数据处理单元(dpu-也称为“智能nic”)、支持网络的图形处理单元(gpu)、现场可编程门阵列(fpga)等。可替代地,网络设备20可以包括网络交换机或路由器、或能够进行网络通信的任何其他合适类型的设备。

34.网络设备20(在本示例中是网络适配器)包括用于连接到主机23的主机接口22、用于连接到网络28的至少一个端口24、用于处理出口(出站分组)的传输(tx)管线32、用于运行管理网络设备20的软件的处理器36以及加时间戳电路48。管线32包括多个处理级40和缓冲区44。为了清楚起见,已经从图中省略了网络设备20的与所公开的技术无关的其他可能元件,例如,用于从网络接收分组的接收(rx)管线。

35.tx管线32经由主机接口22接收分组以用于传输到网络28。管线32使用处理级40来处理分组,在本示例中为表示为级(stage)#1-级#4的四个级。可由级40应用的操作可包括例如将分组封装在vlan隧道报头中、使用ipsec加密分组、以及计算分组的以太网帧校验序列(fcs)并将该fcs附加到分组,仅举几例。在级#2与级#3之间,分组在缓冲区44中缓冲。在级#4之后,分组经由端口24(也称为出口端口)被传输到网络28。

36.在一些实施例中,加时间戳电路48利用当前时间(例如,一天中的时间、用于将网络28的各个元件同步到公共时基的网络时间、或任何其他合适的时间)对管线32中的至少一些分组加时间戳。应用于给定分组的时间戳旨在表示分组的出口时间,即分组离开网络设备的确切时间。加时间戳电路48可以从集成时钟(例如,ptp硬件时钟(phc))或者从任何其他合适的源获得当前时间。

37.在本示例中,加时间戳电路48在分组穿过管线32的级#2时对分组加时间戳。管线的这个级被称为“加时间戳点”。注意,缓冲区44位于加时间戳点的下游,即在加时间戳点与出口端口24之间。因此,缓冲区44的占用级别影响加时间戳点和出口端口24之间的延时,这进而影响时间戳的准确度。下文详细描述用于减轻此不期望作用的技术。

38.图1中所示的网络设备20的配置是纯粹为了概念清晰而描述的示例配置。在替代实施例中可以使用任何其他合适的配置。例如,管线32可包括任何合适类型的任何其他合适数量的处理级。管线32可包括多于一个的缓冲区44,其在加时间戳点的上游或下游。这样的缓冲区可以具有任何合适的类型和大小。加时间戳点可以位于管线的任何其他合适的级。当网络设备是交换机或路由器时,与网络适配器相反,主机接口22可以不存在。相反,网络设备可从另一源(例如,从入口端口)接收分组以进行传输。

39.网络设备20的各种元件可使用合适的硬件(诸如,在一个或更多个专用集成电路(asic)或现场可编程门阵列(fpga)中)、使用软件或使用硬件和软件元件的组合来实现。在

一些实施例中,处理器36包括通用处理器,所述通用处理器被编程为软件以执行本文所描述的功能。软件可以例如通过网络以电子形式下载到处理器,或者它可以替代地或附加地被提供和/或存储在非暂时性有形介质上,诸如磁性、光学或电子存储器。

40.准确加时间戳技术

41.如上所述,由于缓冲区44位于加时间戳点(级#2)和出端口24之间,所以加时间戳点与实际分组出口之间的延时取决于缓冲区的占用级别。在示例的实际实现方式中,此延时可以在100ns(针对空缓冲区)与2μs(针对满缓冲区)之间变化。在一些应用中,例如对于ptp分组的加时间戳,这种幅度的抖动是不可接受的。

42.在一些实施例中,加时间戳电路48通过确保对于需要被准确加时间戳的给定分组,缓冲区44在分组被加时间戳并在管线32中向下游发送时足够空,来克服缓冲区44的延时抖动。

43.在一些实施例中,当准备对给定分组加时间戳时,加时间戳电路48暂时中止管线32中的至少一些处理以排空缓冲区44。通常,处理在缓冲区44上游的处理级40中中止,并且处理在缓冲区44下游的处理级40中正常继续。在示例性实现方式中,加时间戳电路48中止管线中紧接在其之前的级(图1的示例中的级#2)的操作。结果,先前级的输出在管线中(例如,在各级之间的缓冲区中)累积。在极端情况下,缓冲空间可能耗尽,且管线的在缓冲区44上游的整个部分可能停顿。然而,这样的事件通常非常罕见。然而,更一般地,电路48可使用导致缓冲区44排空的任何合适形式的中止。

44.在一个实施例中,电路48仅中止要被加时间戳的给定分组的处理。在其他实施例中,中止所有未决分组的处理。在其他实施例中,中止对所选的分组子集的处理。例如,在它们不应被中止的意义上,一些分组类型可以被定义为关键的。非限制性示例是自主车辆网络中的“关键任务”分组。在这样的情况下,电路48可以仅中止未被定义为关键的分组的处理。

45.在中止分组处理之后,加时间戳电路48验证缓冲区是否满足关于缓冲区44定义的“空置条件”。空置条件通常被定义为使得当满足时,缓冲区44的延时抖动足够小从而实现所要求的加时间戳准确度。

46.在各个实施例中,加时间戳电路48可以验证各种空置条件。在一个实施例中,空置条件要求缓冲区44是完全空的。其他可能的空置条件可以要求缓冲区44的占用级别低于某个阈值、缓冲区44保持少于阈值数量的分组、缓冲区44保持少于阈值数据大小等。各种空置条件的阈值可以是固定的(例如,预定义的)或自适应的。

47.如上所述,在一些实施例中,空置条件可以是自适应的,例如,通过调整阈值或以任何其他适合的方式。自适应空置条件的一个示例场景涉及在以太网中使用停顿(pause)帧(有时也称为xon/xoff的机制)。通常,响应于从链路伙伴接收到pause帧,预期网络设备20延迟其传输,暂时增加分组在加时间戳点和线路上的出口之间经历的延迟。在一些实施例中,加时间戳电路48可以通过放松空置条件来对延迟的增加作出反应,以便确保被加时间戳的分组不会受到下游较大延迟的影响。

48.用于自适应空置条件的另一示例涉及运行时调谐。在一些实施例中,来自加时间戳点下游的管线级中的一个或更多个可测量分组在从加时间戳点到它们的出口的管线中花的典型的或最大时间量。在实施例中,加时间戳电路48可以(例如,在运行时连续地)调谐

空置条件,以确保在必要的最小时间量内阻塞管线。

49.在其他实施例中,加时间戳电路48可以将具有不同严格程度的不同空置条件应用于要求不同加时间戳准确度水平的不同分组。下面参照图3进一步阐述该类型的实施例。

50.在其他实施例中,取决于连接到端口24的网络链路的链路速度,加时间戳电路48可以应用不同的空置条件。例如,加时间戳电路48可以在10gbe链路上使用某种空置条件,在25gbe链路上使用不同的空置条件,并且在200gbe链路上使用另一种空置条件。

51.在各个实施例中,加时间戳电路48可以使用各种技术来评估缓冲区44是否满足空置条件。在一些实施例中,加时间戳电路48从缓冲区接收明确的填充状态指示。在其他实施例中,加时间戳电路48在管线中的处理被中止时等待某个持续时间。这个持续时间可以是固定的(例如,预定义的)或自适应的。还可以使用这两种技术的组合(明确的缓冲区状态指示加上等待时间)。所有这些技术在此被视为自适应空置条件的方式。

52.当缓冲区44满足空置条件时,可以安全地假设加时间戳点与出口端口之间的延时抖动较小。因此,在验证缓冲区44满足空置条件时,加时间戳电路48对给定的分组加时间戳,并且恢复管线32的正常处理。

53.在一些实施例中,除了验证空置条件之外,加时间戳电路48还将缓冲区44的空置程度报告给处理器36和/或主机23。

54.在一些实施例中,加时间戳电路48选择性地应用所公开的技术,即,仅应用于选定的分组。换言之,加时间戳电路48可以支持两种模式:正常模式和高准确度模式,在正常模式中,无论缓冲区44是否满足空置条件,分组都被加时间戳,而在高准确度模式中,仅当缓冲区44满足空置条件时,分组才被加时间戳。加时间戳电路可以仅将高准确度模式应用于选定的分组,例如,仅应用于ptp分组或其他时间同步分组。

55.在一些实施例中,加时间戳电路48可以基于识别哪些分组需要高准确度加时间戳和哪些分组不需要高准确度加时间戳的外部指示(例如,来自在处理器36中运行的可信软件)在模式之间进行选择。例如,加时间戳电路可以接收区分ptp分组和其他分组的指示。例如,处理器36可通过设置与分组相关联的元数据中的合适位来提供给定分组的指示。这种元数据可与分组一起穿过管线32。可替代地,可以使用元数据或其他形式中的任何其他合适形式的指示。进一步可替代地,加时间戳电路可以自主地识别需要高准确度加时间戳的分组。

56.可能影响加时间戳准确度的另一个因素是来自网络28的背压。换言之,即使缓冲区44满足空置条件,如果网络由于拥塞而向网络设备20施加背压,则分组仍可能停顿或受到高延时。因此,在一些实施例中,加时间戳电路48仅在端口44未受到来自网络的背压时应用高准确度模式。考虑背压的另一种可能的方式是如果存在背压则修改空置条件。例如,在存在来自网络的背压的情况下,电路48可以在对高准确度分组加时间戳之前等待延长的时间段。延长等待时间段增加了尽管背压但缓冲区44仍足够空的可能性。

57.在一些实施例中,当中止分组处理以便准确地对给定分组加时间戳时,加时间戳电路48应用限制管线32中的处理的暂时中止的程度的故障保护机制。这样的机制防止暂时中止引起过度的性能下降。电路48可以各种方式和使用各种标准来限制中止的程度。在示例实施例中,加时间戳电路48被配置有(固定的或自适应的)超时,即,允许分组处理中止的最大时间长度。在另一实施例中,电路48被配置有(固定的或自适应的)最大数据大小,其处

理被允许中止。最大数据大小可例如用分组的数量或位的数量来表示。还可以使用考虑时间和数据大小两者的混合标准。在一些实施例中,故障保护机制是可配置的。将最大超时或数据大小配置成无穷大等同于停用故障保护机制。

58.如果故障保护机制在准备对给定分组加时间戳时(例如,超过最大超时和/或最大数据大小)触发,则加时间戳电路48可采取任何合适的动作。例如,电路48可以恢复到正常准确度的加时间戳,即,对给定分组加时间戳,而不管是否满足空置条件。作为另一示例,电路48可放弃给定分组的传输,并向处理器36和/或主机23发出错误消息。

59.图2是示意性地示出了根据本发明的实施例的在网络设备20中对出口分组准确加时间戳的方法的流程图。该方法开始于网络设备20的tx管线32在tx处理步骤50接收和处理出口分组。作为管线中分组处理的一部分,出口分组在缓冲区44中缓冲。

60.在分组选择步骤54,加时间戳电路48选择要被高准确度加时间戳的分组。选定的分组可包括例如ptp分组。在中止步骤58,加时间戳电路48指示管线32中止在缓冲区44上游针对至少所选的分组执行的至少一些处理。由任何管线级40执行的任何种类的管线操作都可以被中止,例如,封装、加密、fcs计算等。

61.在空置验证步骤62,加时间戳电路48验证缓冲区44是否满足特定空置条件。空置条件可以被预定义或者可以动态地改变。一旦发现缓冲区44满足空置条件,在加时间戳步骤66,加时间戳电路48就对选定的分组加时间戳。然后,在恢复步骤70,加时间戳电路48恢复管线32的正常操作。

62.图2的流程是纯粹为了概念清晰而描述的示例流程。在替代实施例中,任何其他适合的流程可以用于实施所公开的技术。

63.图3是示出了根据本发明的实施例的在加时间戳准确度与空置条件严格性之间的示例关系的定性图表。图3的水平轴表示空置条件的严格性,越大的值对应于更严格的条件(例如,缓冲区完全空的要求,或更长的等待时间),越小的值对应于更宽松的条件。竖直轴表示加时间戳准确度,越大的值对应于更差的准确度(并因此时间戳中较高的时间抖动),而越小的值对应于更好的准确度(并因此较低的时间抖动)。

64.曲线图80示出了加时间戳准确度对空置条件的严格性的定性相关性。如所看到的,放宽空置条件导致更高的抖动,反之亦然。然而,典型地,存在对可实现的准确度的约束,即使空置条件变得非常严格。例如,一旦空置条件严格到足以以非常高的可能性排空缓冲区,进一步收紧该条件将在准确度上提供很少或没有额外的改进。

65.在各个实施例中,网络设备20可使用上述相关性来减少性能下降。在一些实施例中,加时间戳电路48可以调适空置条件以匹配某个分组或应用实际要求的加时间戳准确度。以这种方式,网络设备仅在实际需要而不总是需要时强制执行严格的空置条件,从而使性能下降最小化。

66.例如,在一些实施例中,当对与不同应用相关联的分组加时间戳时,加时间戳电路48可以应用在严格程度上不同的不同空置条件。另外地或可替代地,当对与给定应用相关联的不同分组加时间戳时,加时间戳电路48可以应用在严格程度上不同的不同空置条件。在一些实施例中,加时间戳电路可以接收指示空置条件所要求的严格程度的指示(例如,在与分组一起行进的元数据中)。在其他实施例中,加时间戳电路可以自主地决定所要求的严格性,例如,通过自主地识别与给定分组相关联的应用。

67.在一些实施例中,通过自适应地修改空置条件,加时间戳电路48调整加时间戳准确度,直至达到所期望的目标准确度。

68.具有可变延迟的处理级的准确加时间戳

69.以上描述主要涉及缓冲区,其具有可变占用级别并且因此具有可变延迟。然而,所公开的技术不限于缓冲区,且可与具有可变处理延迟的各个其他处理级一起使用。可变延迟处理级的非限制性示例是加密引擎。通常,尽管不是必须的,但对分组数据进行操作的处理级(与仅对分组报头进行操作相反)更可能具有大的延迟变化。

70.当可变延迟处理级位于tx管线32中加时间戳点下游时,加时间戳电路48可应用所公开的技术,类似于将其应用于缓冲区的方式。

71.在示例实施例中,当准备准确地对给定分组加时间戳时,加时间戳电路48暂时中止可变延迟级上游的tx管线中的至少一些分组的至少一些处理。然后,电路48检查可变延迟处理级是否满足空置条件。空置条件通常被设置为使得可变延迟处理级完成所有先前分组的处理,并且将因此以最小的已知延迟来延迟给定分组。

72.可以使用上述空置条件中的任一个,以及用于验证是否满足空置条件的上述技术中的任一个。

73.在示例实施例中,管线32中的每个可变延迟处理级被配置为当其完成处理并变为空闲时输出“完成”信号。加时间戳电路48验证空置条件的一种可能的方式是等待直到下游可变延迟级的所有“完成”输出都被设置。在其他实施例中,电路48可以仅检查“完成”信号的子集,或以任何其他方式使用“完成”信号,可能结合其他信息。

74.所公开的技术的另一优点是能够将时间戳插入到分组中,并且然后对包括时间戳的分组进行加密,并且仍然实现高的加时间戳准确度。由于加密级往往具有较大的延迟变化,在没有所公开的技术的情况下实现这个目标是不可能的,或者至少是高度挑战性的。

75.多主机的使用情况

76.在图1的实施例中,网络设备20服务于单个主机23。然而,在替代实施例中,网络设备20(在此示例中的网络适配器)可以服务于可以彼此独立地操作的多个主机23。具体地,网络设备可将所公开的加时间戳技术应用于源自多个不同主机的出口分组。

77.在一些实施例中,网络设备20中的加时间戳电路48对于不同的主机进行不同地操作。例如,加时间戳电路48可以针对不同的主机评估不同的空置条件(例如,每个主机可以具有其自身的空置条件),和/或针对不同的主机不同地验证空置条件。在示例实施例中,加时间戳电路48可以针对一个主机验证缓冲区44是空的,并且还等待定义的持续时间。对于第二主机,加时间戳电路48可验证缓冲区44为90%空,而不等待任何额外持续时间。对于第三主机,加时间戳电路48可完全停用高准确度的加时间戳。可替代地,可以使用任何其他适合的操作模式。

78.在一些实施例中,加时间戳电路48可以将优先级赋予选定主机而非其他主机,以便保证对源自该主机的分组进行高准确度加时间戳。例如,加时间戳电路48可以暂时停顿来自除了所选主机之外的所有主机的传输,并且在中止期间对来自选定主机的分组加时间戳。作为另一示例,电路48可以由于其他主机的准确加时间戳而禁止中止选定主机的(一些或全部)分组。这样的选择性操作对于其他主机可以是透明的。例如,当多主机配置中的主机之一用作ptp大师或以其他方式在网络中起到一些关键性作用时,该特征是有用的。

79.应当理解,上述实施例是以示例的方式引用的,并且本发明不限于在上文中具体示出和描述的内容。相反,本发明的范围包括在上文中描述的各种特征的组合和子组合,以及在阅读以上描述时本领域技术人员会想到的并且在现有技术中未公开的其变化和修改。通过引用结合在本专利申请中的文献被认为是本技术的组成部分,除了在这些并入的文献中以与本说明书中明确或隐含的定义相冲突的方式定义任何术语的程度上,仅应当考虑本说明书中的定义。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。