1.本发明实施例涉及集成芯片(integrated chip)及用以制造上述集成芯片的方法,特别涉及包含在铁电层下的第一金属层及第二金属层的集成芯片。

背景技术:

2.许多现代的电子装置包含电子存储器(electronic memory)。电子存储器可以为挥发性(volatile)存储器或是非易失性(non-volatile)存储器。非易失性存储器不需要供电也能存储数据,易失性存储器则需要供电才能存储数据。新世代电子存储器包含铁电式随机存取存储器(ferroelectric random-access memory(feram))、磁阻式随机存取存储器(magnetoresistive random-access memory(mram))、电阻式随机存取存储器(resistive random-access memory(rram))、相变随机存取存储器(phase-change random-access memory(pcram)),以及导电桥接随机存取存储器(conductive-bridging random-access memory(cbram))。

技术实现要素:

3.本发明实施例提供一种集成芯片,包含:基板、半导体层、一对源极/漏极、第一金属层、第二金属层,以及铁电层。半导体层位在基板上。该对源极/漏极沿着半导体层排列。第一金属层位在基板上。第二金属层位在第一金属层上。铁电层位在第二金属层上。第一金属层具有第一晶体方向,第二金属层具有与第一晶体方向不同的第二晶体方向。

4.本发明实施例提供一种集成芯片,包含:基板、半导体层、一对源极/漏极、第一金属层、第二金属层,以及铁电层。半导体层位在基板上。该对源极/漏极沿着半导体层排列。第一金属层位在基板上。第二金属层位在第一金属层上。铁电层位在第二金属层上。第二金属层具有[110]晶体方向。

[0005]

本发明实施例提供一种用以制造集成芯片的方法,包含:在基板上沉积半导体层;沿着半导体层形成一对源极/漏极;在基板上沉积第一金属层;在第一金属层上沉积第二金属层;以及在第二金属层上沉积铁电层。第二金属层具有[110]晶体方向。

附图说明

[0006]

本发明实施例阅读以下实施方式配合附带的附图能够最好的理解。应该注意的是,根据业界的标准做法,多个特征并未依照比例绘制。事实上,为了清楚的讨论,多个特征的尺寸(dimension)可以随意地增加或减少。

[0007]

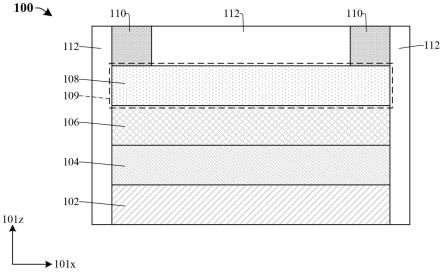

图la用以示意说明一些实施例中的一集成芯片的截面图,上述集成芯片包含一第一金属层、在上述第一金属层上的一第二金属层,以及在上述第二金属层上的一铁电层(ferroelectric layer)。

[0008]

图1b用以示意说明不同晶体方向(crystal orientation)的一些范例。

[0009]

图2用以示意说明图1a的上述集成芯片的一些实施例的截面图,其中上述集成芯

片还包含一绝缘层(insulator layer)。

[0010]

图3用以示意说明图2的上述集成芯片的一些实施例的截面图,其中上述集成芯片还包含一第三金属层及一第四金属层。

[0011]

图4用以示意说明图1a的上述集成芯片的一些实施例的截面图,其中上述集成芯片还包含一内连(interconnect)结构。

[0012]

图5用以示意说明图1a的上述集成芯片的一些实施例的截面图,其中上述第一金属层位在一基板(substrate)上。

[0013]

图6及图7用以示意说明一集成芯片的一些选择性的实施例的截面图,上述集成芯片包含一第一金属层、在上述第一金属层上的一第二金属层,以及在上述第二金属层上的一铁电层。

[0014]

图8到图19用以示意说明一集成芯片的制造方法的一些实施例的截面图,上述集成芯片包含一第一金属层、在上述第一金属层上的一第二金属层,以及在上述第二金属层上的一铁电层。

[0015]

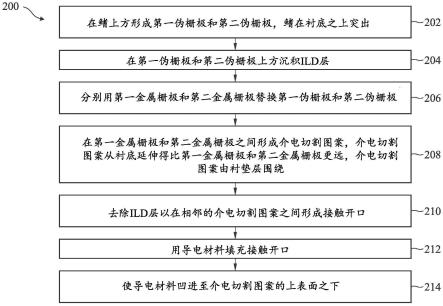

图20用以示意说明制造一集成芯片的方法的一些实施例的流程图,上述集成芯片包含一第一金属层、在上述第一金属层上的一第二金属层,以及在上述第二金属层上的一铁电层。

[0016]

图21到图30用以示意说明制造一集成芯片的方法的一些选择性的实施例的截面图,上述集成芯片包含一第一金属层、在上述第一金属层上的一第二金属层,以及在上述第二金属层上的一铁电层。

[0017]

图31用以示意说明制造一集成芯片的方法的一些选择性的实施例的流程图,上述集成芯片包含一第一金属层、在上述第一金属层上的一第二金属层,以及在上述第二金属层上的一铁电层。

[0018]

附图标记说明:

[0019]

100,200,300,400,500,600,700,800,900,1000,1100,1200,1300,1400,1500,1600,1700,1800,1900,2100,2200,2300,2400,2500,2600,2700,2800,2900,3000:截面图

[0020]

101x:x轴

[0021]

101y:y轴

[0022]

101z:z轴

[0023]

102,610,722:第一金属层

[0024]

104,612,724:第二金属层

[0025]

106,614,726:铁电层

[0026]

108,605,703:半导体层

[0027]

109,606,709:半导体通道

[0028]

110:源极/漏极结构

[0029]

112,404,504,604,622,626,702:介电层

[0030]

202,609:绝缘层

[0031]

302:第三金属层

[0032]

304:第四金属层

[0033]

402:金属接线

[0034]

406:内连结构

[0035]

408:扩散区

[0036]

502,602,701:基板

[0037]

608,704:源极区/漏极区

[0038]

616,728:第三金属层

[0039]

618,730:第四金属层

[0040]

620,710:间隔物

[0041]

620a:虚线

[0042]

624:源极/漏极接点

[0043]

628,714:第一金属接线

[0044]

630,716:第二金属接线

[0045]

706:栅极结构

[0046]

708:栅极介电层

[0047]

712:介电结构

[0048]

718:第三金属接线

[0049]

720:铁电存储堆叠

[0050]

1402,1602,2202,2602:遮罩(掩膜)层

[0051]

1604,2604:开口

[0052]

1702:金属层

[0053]

2000,3100:方法

[0054]

2002,2004,2006,2008,2010,2012,2014,2016,2018,2020,2022,3102,3104,3106,3108,3110,3112,3114,3116,3118,3120:操作

[0055]

2302:间隔物层

[0056]

2802:金属

具体实施方式

[0057]

以下提供多个不同的实施例或范例,以执行所提供的标的的不同特征。以下描述元件及排列(arrangement)的特定范例以简化本发明的实施例。这些范例当然仅是范例而不应该是限制。举例来说,在以下实施方式中的一第一特征在一第二特征之上的构成(formation),可以包含上述第一特征及上述第二特征直接接触(contact)构成的实施例,也可以包含额外特征在上述第一特征及上述第二特征之间构成的实施例,在这种情况下上述第一特征及上述第二特征并不会直接接触。此外,本说明书会在多个范例中重复参考编号及/或字母。这样的重复是为了简洁及清楚,本身并不用以决定多个实施例及/或配置之间的关系。

[0058]

此外,为了方便描述,空间相对关系用语(例如“以下”、“之下”、“低于”、“以上”、“高于”等)在此被用以描述如图所示的一个元件或特征与另一个元件或特征之间的关系。空间相对关系用语旨在包含使用中或操作中的装置除了图中所描述的方向以外的不同方向。装置可以在别的方向(旋转90度或在其他方向)且在此使用的空间相对关系用语可以做出相应的解读。

[0059]

一些集成芯片(integrated chip)包含存储器装置。举例来说,一些集成芯片包含feram的存储装置,并且feram的存储装置包含多个铁电式随机存取存储器(feram)存储单元(memory cell)。一些feram的存储单元包含在一基板上的一金属层、在上述金属层上的一铁电层、在上述铁电层上的一半导体层,以及在上述铁电层上的一对源极/漏极(source/drain)。一半导体通道沿着上述半导体层在上述源极/漏极之间延伸。上述金属层如同一个栅极(gate)电极一般运行,上述栅极电极以上述铁电层与上述半导体通道分离。在一些feram装置中,上述金属层以物理汽相沉积工艺(physical vapor deposition(pvd)process)(例如直流电溅镀工艺(direct current sputtering process))在上述基板上沉积(deposit),并具有[100]晶体方向。之后,在上述金属层上沉积上述铁电层。

[0060]

上述存储单元可以通过将电场施加于上述铁电层(例如通过施加电压跨接在上述铁电层上)进行写入。当电场施加于上述铁电层时,取决于所施加的电场的方向(例如取决于跨接在上述铁电层上施加的电压的正负),上述铁电层在一第一方向,或是在与上述第一方向相反的一第二方向上被极化(polarize)。极化的方向对应于上述存储单元的逻辑状态(例如上述第一方向对应于逻辑“0”,上述第二方向对应于逻辑“1”)。上述铁电层在上述第一方向上被极化时的极化电荷(polarization charge),与上述铁电层在上述第二方向上被极化时的极化电荷之间的差异对应于上述存储单元的存储窗口(memory window)。

[0061]

一些铁电层具有四种不同的晶相(crystal phase):斜方晶相(orthorhombic phase)、单斜晶相(monoclinic phase)、正方晶相(tetragonal phase),以及立方晶相(cubic phase)。在一些情况下,这些铁电层在斜方晶相时展现更大的极化(polarization)。因此,增加铁电层的斜方晶相(例如增加为斜方晶相的铁电层的容积分率(volumetric fraction))可以增加铁电层的极化。在一些情况下,可以通过在铁电层上施加拉张应力(tensile stress)增加其斜方晶相。举例来说,增加施加于铁电层的拉张应力(例如由相邻的层施加)可以增加为斜方晶相的铁电层的容积分率,也就是可以增加上述铁电层的极化。

[0062]

极化可以使用残余极化值(remnant polarization(2pr)value)量化。较大的极化可以对应于较大的存储窗口。较大的存储窗口可以对应于较佳的存储单元性能(例如较佳的读/写操作性能)。此外,较大的极化可以对应于较长的装置寿命。

[0063]

这些feram装置的挑战是铁电层的斜方晶相可能很低,因为具有[100]晶体方向的金属层只能在上述铁电层上施加些微的拉张应力。因此,上述铁电层的斜方晶相可能较少(例如为斜方晶相的铁电层的容积分率较少)。减少铁电层的斜方晶相会减少铁电层的极化(例如残余极化值)。因此,存储窗口及装置寿命也会减少。

[0064]

本发明的多个实施例有关于包含一存储单元的一集成芯片。上述存储单元包含一第一金属层及位在一铁电层下的一第二金属层,上述第二金属层用以提高上述集成芯片的性能。一半导体层位在一基板上。一对源极/漏极沿着上述半导体层排列。上述第一金属层位在上述基板上。上述第二金属层位在上述第一金属层上。上述铁电层位在上述第二金属层上。上述第二金属层具有[111]或[110]晶体方向。

[0065]

通过在上述集成芯片中的上述第一金属层上包含上述第二金属层,上述铁电层因此位在具有[111]或[110]晶体方向的上述第二金属层上,可以提高上述集成芯片的性能。举例来说,因为上述第二金属层具有[111]或[110]晶体方向,所以上述第二金属层可以增

加施加于上述铁电层的拉张应力。增加施加于上述铁电层的拉张应力可以增加上述铁电层的斜方晶相(例如可以增加为斜方晶相的上述铁电层的容积分率)。增加上述铁电层的斜方晶相可以增加上述铁电层的极化。增加上述铁电层的极化可以增加上述存储单元的存储窗口及存储器寿命。简而言之,通过在上述集成芯片中的上述铁电层下包含具有[111]或[110]晶体方向的上述第二金属层,可以提高上述存储单元的性能。

[0066]

图1a用以示意说明一集成芯片的一些实施例的一截面图100,上述集成芯片包含一第一金属层102、位在第一金属层102上的一第二金属层104,以及位在第二金属层104上的一铁电层106。

[0067]

第二金属层104位在第一金属层102的顶面(top surface)上。铁电层106位在第二金属层104的顶面上。一半导体层108位在铁电层106的顶面上。一对源极/漏极结构110沿着半导体层108排列。在一些实施例中,源极/漏极结构110位在半导体层108的顶面上,并且从侧面上来看(laterally)是分开的。一半导体通道109沿着半导体层108在源极/漏极结构110间延伸。一介电层(dielectric layer)112位在半导体层108的顶面上,并且在源极/漏极结构110之间排列。介电层112将源极/漏极结构110分开。

[0068]

在一些实施例中,介电层112位在第一金属层102、第二金属层104、铁电层106、半导体层108,以及源极/漏极结构110的两侧(opposite side)上(例如位在侧壁(sidewall)上)。在一些实施例中,铁电层106与第二金属层104直接接触。在一些实施例中,第一金属层102与第二金属层104构成栅极(gate electrode)。在一些实施例中,第一金属层102、第二金属层104、铁电层106、半导体层108以及源极/漏极结构110构成上述集成芯片的一存储单元。

[0069]

以上提到的各层具有沿着一z轴101z的高度、沿着与z轴101z垂直的一x轴101x的宽度、沿着与z轴101z及x轴101x垂直的一y轴(例如图1b中的y轴101y)的长度。举例来说,以上提到的各层可以具有平行于一x-y平面的顶面,上述x-y平面由x轴101x及上述y轴(图1b中的y轴101y)构成。

[0070]

第一金属层102具有一第一晶体方向。第二金属层104具有与上述第一晶体方向不同的一第二晶体方向。举例来说,第一金属层102具有[100]晶体方向,第二金属层104具有[111]或[110]晶体方向。在一些范例中,以上提到的晶体方向(例如[100]、[110]及[111])对应于米勒指数(miller indices)。

[0071]

通过在上述集成芯片中,包含在第一金属层102上的第二金属层104,使得铁电层106位在具有[111]或[110]晶体方向的第二金属层104上,可以提升上述集成芯片的性能。举例来说,因为第二金属层104具有[111]或[110]晶体方向,所以第二金属层104可以增加施加于铁电层106上的拉张应力。增加施加于铁电层106的拉张应力可以增加铁电层106的斜方晶相(例如可以增加为斜方晶相的铁电层106的容积分率)。增加铁电层106的斜方晶相可以增加铁电层106的极化,并因此增加存储单元的存储窗口及存储器寿命。因此,通过在上述集成芯片中包含具有[111]或[110]晶体方向的第二金属层104,可以提高上述集成芯片的性能。

[0072]

图1b就z轴101z、x轴101x及y轴101y示意说明以上提到的晶体方向(例如[100]、[110]及[111])的一些范例。在图1b中使用通用的立方体形状示意说明范例的晶格(crystal lattice)方向。在一些范例中,某一层的晶体方向是从上方沿一条垂直于第一金

属层102顶面的线向下看那一层进行描述。举例来说,第二金属层104的顶面平行于由x轴101x及y轴101y构成的x-y平面,第二金属层104的晶体方向可以是从第二金属层104的上方沿着z轴101z往下看进行描述。

[0073]

在一些范例中,某一层(例如第一金属层102或第二金属层104)的晶体方向可以使用x光绕射(x-ray diffraction)程序、进动电子绕射(precision electron diffraction)程序,或其他合适的程序决定。

[0074]

在一些实施例中,第一金属层102包含一第一金属,第二金属层104包含上述第一金属。在其他实施例中,第一金属层102包含一第一金属,第二金属层104包含与上述第一金属不同的一第二金属。在一些实施例中,第一金属层102与第二金属层104沿着晶界(grain boundary)彼此接触。

[0075]

在一些实施例中,第一金属层包含铂(platinum)、钛(titanium)、氮化钛(titanium nitride)、钽(tantalum)、氮化钽(tantalum nitride)、钨(tungsten)、铁(iron)、镍(nickel)、铍(beryllium)、铬(chromium)、钴(cobalt)、锑(antimony)、铱(iridium)、钼(molybdenum)、锇(osmium)、钍(thorium)、钒(vanadium)、以上金属的一些组合,或是一些其他合适的材料。在一些实施例中,第一金属层102可以具有大于15纳米(nanometer)、大于30纳米、大约30纳米到1微米(micrometer)、大于50纳米的厚度,或是其他合适的厚度。

[0076]

在一些实施例中,增加第一金属层102的厚度可以增加第一金属层102的热容量(thermal capacity)。增加第一金属层102的热容量可以对应于增加施加于铁电层106的拉张应力。因此,通过增加第一金属层102的厚度,可以进一步的增加铁电层106的极化。

[0077]

在一些实施例中,第二金属层104包含氮化钛或其他合适的材料。在一些实施例中,第二金属层104具有大约1纳米到100纳米的厚度,或是一些其他合适的厚度。在一些实施例中,铁电层106包含氧化铪锆(hafnium-zirconium-oxide)(例如hf

x

zr

1-x

oy)、掺杂(dope)钪(scandium)的氮化铝(aluminum nitride),或是一些其他合适的材料。在一些实施例中,铁电层106具有大约30纳米或更小的厚度,或是一些其他合适的厚度。

[0078]

在一些实施例中,半导体层108包含非晶相铟镓锌氧化物(amorphous indium-gallium-zinc-oxide)(例如a-igzo)、砷化镓(gallium arsenide)、氮化镓(gallium nitride)、砷化铝镓(aluminum gallium arsenide)、一些半导体化合物、非晶相硅(silicon)、多晶形(polycrystalline)硅、包含锡(tin)的一些铟镓锌氧化物化合物(compound),或是一些其他合适的材料。在一些实施例中,半导体层108具有大约3纳米到大约100纳米的厚度。

[0079]

在一些实施例中,源极/漏极结构110包含铝(aluminum)、钛、钽、钨、钌(ruthenium)、金(gold)、铜(copper)、一些其他合适的金属,或是一些其他合适的材料。在一些实施例中,介电层112包含二氧化硅(silicon dioxide)、氮化硅(silicon nitride),或是一些其他合适的介电质材料。

[0080]

图2用以示意说明图1a的上述集成芯片的一些实施例的截面图200,其中上述集成芯片还包含一绝缘层202。

[0081]

绝缘层202在铁电层106及半导体层108之间排列。绝缘层202位在铁电层106的顶面上,半导体层108位在绝缘层202的顶面上。

[0082]

在一些实施例中,绝缘层202包含二氧化硅、氮化硅、氧化铪(hafnium oxide)、掺杂硅的氧化铪,或是一些其他合适的材料。在一些实施例中,绝缘层202具有大约0.1纳米到10纳米,或是一些其他合适的厚度。

[0083]

图3用以示意说明图2的上述集成芯片的一些实施例的截面图300,其中上述集成芯片还包含一第三金属层302及一第四金属层304。

[0084]

第三金属层302及第四金属层304位在铁电层106及绝缘层202之间。第三金属层302位在铁电层106的顶面上。在一些实施例中,第三金属层302与铁电层106直接接触。第四金属层304位在第三金属层302的顶面上。绝缘层202位在第四金属层304的顶面上。在一些实施例中,第三金属层302与第四金属层304构成浮动电极(floating electrode)。

[0085]

在一些实施例中,第三金属层302具有[111]或[110]晶体方向。在一些实施例中,第二金属层104具有[110]晶体方向,第三金属层302具有[111]晶体方向,或是反过来。因为第三金属层302具有[111]或[110]晶体方向并且位在铁电层106之上,第三金属层302可以增加施加于铁电层106上的拉张应力。因此,可以进一步增加铁电层106的极化,并因此进一步增进上述集成芯片的性能。

[0086]

在一些实施例中,第三金属层302包含上述第二金属,或是不同于上述第二金属的一第三金属(例如第三金属层302可以包含与第二金属层104相同或不同的金属)。举例来说,在一些实施例中第三金属层302包含氮化钛或一些其他合适的材料。在一些实施例中,第三金属层302具有大约1纳米到100纳米的厚度,或是一些其他合适的厚度。

[0087]

在一些实施例中,第四金属层304包含上述第一金属,或是不同于上述第一金属的一第四金属(例如第四金属层304可以包含与第一金属层102相同或不同的金属)。举例来说,在一些实施例中第四金属层304包含铂、钛、氮化钛、钽、氮化钽、钨、铁、镍、铍、铬、钴、锑、铱、钼、锇、钍、钒、以上金属的一些组合,或是一些其他合适的材料。在一些实施例中,第四金属层304具有大于15纳米、大于30纳米、大约30纳米到1微米、大于50纳米的厚度,或是一些其他合适的厚度。

[0088]

在一些实施例,增加第四金属层304的厚度可以增加第四金属层304的热容量。增加第四金属层304的热容量可以对应于增加施加在铁电层106的拉张应力。因此,通过增加第四金属层304的厚度,可以进一步的增加铁电层106的极化。

[0089]

图4用以示意说明图1a的上述集成芯片的一些实施例的截面图400,其中上述集成芯片还包含一内连结构406。

[0090]

在一些实施例中,一对金属接线(wire)402位在介电层404中,并位在源极/漏极结构110上。内连结构406位在金属接线402上。内连结构406可以包含额外的金属接线(例如金属通孔(via)、金属线(line),或是相似物)。上述额外的金属导线可以经由金属接线402耦接源极/漏极结构110。

[0091]

在一些实施例中,在半导体层108中可以存在一对扩散(diffusion)区408,并且位于源极/漏极结构110的正下方。扩散区408可以是从源极/漏极结构110扩散到半导体层108中的金属构成的。因此,扩散区408可以包含来自半导体层108的半导体材料与来自源极/漏极结构110的金属材料的组合。

[0092]

图5用以示意说明图1a的上述集成芯片的一些实施例的截面图500,其中第一金属层102位在一基板502上。

[0093]

在一些实施例中,一介电层504位在基板502上,第一金属层102位在介电层504的顶面上。在一些实施例中,基板502包含硅或一些其他合适的材料,介电层504包含氧化硅、氮化硅,或是一些其他合适的材料。

[0094]

图6用以示意说明一集成芯片的一些选择性的实施例的截面图600,上述集成芯片包含一第一金属层610、位在第一金属层610上的一第二金属层612,以及位在第二金属层612上的一铁电层614。

[0095]

上述集成芯片包含位在一基板602上的一介电层604。一半导体层605位在介电层604的顶面上。一对源极区/漏极区608位在半导体层605中。源极区/漏极区608沿着半导体层605排列。源极区/漏极区608是半导体层605的掺杂区。源极区/漏极区608的掺杂类型可以与半导体层605的掺杂类型相反。一半导体通道606沿着半导体层605在源极区/漏极区608之间的部分延伸。一绝缘层609直接地位在半导体层605的顶面上。一第一金属层610位在绝缘层609的顶面上。一第二金属层612位在第一金属层610的顶面上。一铁电层614位在第二金属层612的顶面上。一第三金属层616位在铁电层614的顶面上。一第四金属层618位在第三金属层616的顶面上。间隔物(spacer)620排列在绝缘层609、第一金属层610、第二金属层612、铁电层614、第三金属层616,以及第四金属层618的相对的侧壁(sidewall)上。在一些实施例中,间隔物620包含介电质材料。

[0096]

介电层622位在源极区/漏极区608上。一对源极/漏极接点(contact)624位在介电层622内,并且位在源极区/漏极区608上。源极/漏极接点624垂直地沿着间隔物620的侧壁延伸通过介电层622。间隔物620将源极/漏极接点624与绝缘层609、第一金属层610、第二金属层612、铁电层614、第三金属层616,以及第四金属层618侧面上地(laterally)分开。

[0097]

一介电层626位在介电层622之上。多条第一金属接线628位在介电层626内,并且位在源极/漏极接点624上。一第二金属接线630位在介电层626内,并且位在第四金属层618上。

[0098]

如同对于图1a及图3所讨论的,第二金属层612及第三金属层616具有[110]或[111]晶体方向。因此,可以增加施加于铁电层614的拉张应力,并因此增加铁电层614的极化。此外,第一金属层610及第四金属层618可以具有相对较大的厚度(例如大于大约30纳米、大于大约50纳米,或类似的)。因此,可以进一步增加施加于铁电层614的拉张应力,并因此进一步增加铁电层614的极化。

[0099]

在一些实施例中,介电层604可以被称为缓冲层(buffer layer)、绝缘层609可以被称为隔离层(blocking layer)、第一金属层610及/或第二金属层612可以被称为浮动电极,以及第三金属层616及/或第四金属层618可以被称为栅极。

[0100]

图7用以示意说明一集成芯片的一些选择性的实施例的截面图700,上述集成芯片包含一第一金属层722、在第一金属层722上的一第二金属层724,以及在第二金属层724上的一铁电层726。

[0101]

上述集成芯片包含位在一基板701上的一介电层702,以及位在介电层702上的一半导体层703。一对源极区/漏极区704被布置在半导体层703中。源极区/漏极区704沿着半导体层703排列。源极区/漏极区704是半导体层703的掺杂区。源极区/漏极区704的掺杂类型可以与半导体层703的掺杂类型相反。一栅极(gate)结构706位在半导体层703之上,并且由一栅极介电层(gate dielectric layer)708垂直地与半导体层703分开。栅极结构706在

半导体层703之上于源极区/漏极区704之间延伸。一半导体通道709沿着半导体层703的顶面及栅极介电层708,在源极区/漏极区704之间延伸。在一些实施例中,多个间隔物710位在栅极结构706及栅极介电层708的相对的侧壁上。一介电结构712位在基板701上,包含一或多个介电层。一第一金属接线714穿过介电结构712垂直地延伸至源极区/漏极区704其中一者的顶面,一第二金属接线716穿过介电结构712垂直地延伸至另一个源极区/漏极区704的顶面。

[0102]

铁电存储堆叠(memory stack)720在基板701上,并且位在第二金属接线716的顶面上。铁电存储堆叠720位在介电结构712内,并且包含第一金属层722、位在第一金属层722上的第二金属层724、位在第二金属层724上的铁电层726、位在铁电层726上的一第三金属层728,以及位在第三金属层728上的一第四金属层730。

[0103]

一第三金属接线718位在第四金属层730上。在一些实施例中,第一金属接线714为位元线(bit line),第二金属接线716及第三金属接线718一起构成源线(source line),铁电存储堆叠720串联在第二金属接线716及第三金属接线718之间。在一些实施例中,一第四金属接线(图未示)耦接栅极结构706并且为字线(word line)。

[0104]

如同对于图1a、图3及图6所讨论的,第二金属层724及第三金属层728具有[110]或[111]晶体方向。因此,可以增加施加于铁电层726的拉张应力,并因此增加铁电层726的极化。此外,第一金属层722及第四金属层730可以具有相对较大的厚度(例如大于大约30纳米、大于大约50纳米,或类似的)。因此,可以进一步增加施加于铁电层726的拉张应力,并因此进一步增加铁电层726的极化。

[0105]

图8到图19用以示意说明一集成芯片的制造方法的实施例的截面图800到截面图1900,上述集成芯片包含第一金属层102、位在第一金属层102上的第二金属层104,以及位在第二金属层104上的铁电层106。虽然图8到图19描述了一种方法,但是可以理解图8到图19所公开的结构并不限于这一个方法,而是可以做为独立于方法之外的结构。

[0106]

如图8中的截面图800所示,在基板502上形成第一金属层102。在一些实施例中,在介电层504上沉积第一金属层102,介电层504位在基板502之上。在一些实施例中,第一金属层102是通过物理汽相沉积(pvd)工艺、化学汽相沉积(chemical vapor deposition(cvd))工艺、原子层沉积(atomic layer deposition(ald))工艺、脉冲激光沉积(pulsed laser deposition(pld))工艺,或是一些其他合适的工艺,在基板502上沉积铂、钛、氮化钛、钽、氮化钽、钨、铁、镍、铍、铬、钴、锑、铱、钼、锇、钍、钒、以上金属的一些组合,或是一些其他适合的材料所形成的。在一些实施例中,第一金属层102具有大于30纳米、大于50纳米,或是一些其他合适的厚度。

[0107]

如同图9的截面图900所示,在第一金属层102上形成第二金属层104。第二金属层104在第一金属层102上形成以具有[111]或[110]晶体方向。在一些实施例中,第二金属层104是通过等离子体加强原子层沉积(plasma-enhanced ald(peald))工艺、pld工艺,或是一些其他合适的工艺在第一金属层102上沉积氮化钛或一些其他合适的材料所形成的。在一些范例中,通过控制在peald工艺或pld工艺中所使用的能量,可以控制第二金属层104的晶体方向。在一些实施例中,上述能量可以介于大约500瓦特(watt)到大约2000瓦特之间,或是一些其他合适的区间之间。

[0108]

如同图10的截面图1000所示,在第二金属层104上形成铁电层106。在一些实施例

中,铁电层106是通过cvd工艺、pvd工艺、ald工艺,或是一些其他合适的工艺在第二金属层104上沉积氧化铪锆(例如hf

x

zr

1-x

oy)、掺杂钪的氮化铝,或是一些其他合适的材料所形成的。

[0109]

在一些实施例中,在铁电层106形成于第二金属层104上之后,执行退火(anneal)。举例来说,在铁电层106沉积完后,铁电层106、第二金属层104、第一金属层102、介电层504,以及基板502使用一第一退火工艺进行退火。举例来说,上述第一退火工艺可以包含快速热退火(rapid thermal anneal(rta))工艺(例如将多个层在摄氏(celsius)温度大约350度到700度(或一些其他合适的温度)的环境中,加热大约10秒到30秒(或一些其他合适的时间))、炉退火(furnace anneal)工艺(例如将多个层在摄氏(celsius)温度大约350度到700度(或一些其他合适的温度),加热大约30秒到5小时(或一些其他合适的时间)),或是一些其他合适的退火工艺。

[0110]

图11及图12示意说明用以制造上述集成芯片的方法的两个选择性的部分。

[0111]

如图11的截面图1100所示,在一些实施例中在铁电层106上形成绝缘层202。在一些实施例中,绝缘层202是通过cvd工艺、pvd工艺、ald工艺,或是一些其他合适的工艺在铁电层106上沉积二氧化硅、氮化硅、氧化铪、掺杂硅的氧化铪,或是一些其他合适的材料所形成的。

[0112]

如图12的截面图1200所示,在一些其他实施例中在铁电层106上形成第三金属层302、在第三金属层302上形成第四金属层304,以及在第四金属层304上形成绝缘层202。第三金属层302在铁电层106上形成以具有[111]或[110]晶体方向。

[0113]

在一些实施例中,第三金属层302是通过peald工艺、pld工艺,或是一些其他合适的工艺在铁电层106上沉积氮化钛或一些其他合适的材料所形成的。

[0114]

在一些实施例中,形成第四金属层304包含通过pvd工艺、cvd工艺、ald工艺、pld工艺,或是一些其他合适的工艺在第三金属层302上沉积铂、钛、氮化钛、钽、氮化钽、钨、铁、镍、铍、铬、钴、锑、铱、钼、锇、钍、钒、以上金属的一些组合,或是一些其他合适的材料。

[0115]

图13及接下来的图示在假设图11及图12中示意说明的工艺没有被执行的情况下进行说明。如图13的截面图1300所示,在铁电层106上形成半导体层108。在一些实施例中,半导体层108是通过cvd工艺、pvd工艺、ald工艺,或是一些其他合适的工艺在铁电层106上沉积非晶相铟镓锌氧化物(例如a-igzo)、砷化镓、氮化镓、砷化铝镓、一些半导体化合物、非晶相硅、多晶形硅、包含锡的一些铟镓锌氧化物化合物,或是一些其他合适的材料。

[0116]

在一些其他实施例中(例如在一些绝缘层202在铁电层106上形成(如图11所示)的实施例中),在绝缘层202上形成半导体层108,绝缘层202位在铁电层106上。

[0117]

在一些其他实施例中(例如一些在铁电层106上形成第三金属层302、在第三金属层302上形成第四金属层304,以及在第四金属层304上形成绝缘层202(如图12所示)的实施例),在绝缘层202上形成半导体层108,绝缘层202位在第三金属层302及第四金属层304之上。

[0118]

在一些实施例中,在半导体层108形成之后进行退火。举例来说,在半导体层108沉积之后,半导体层108、铁电层106、第二金属层104、第一金属层102、介电层504,以及基板502(可能包含第三金属层302、第四金属层304,及/或绝缘层202)使用一第二退火工艺进行退火。举例来说,第二退火工艺包含rta工艺、炉退火工艺,或一些其他合适的退火工艺。

[0119]

在一些实施例中,上述方法包含上述第一退火工艺,但不包含上述第二退火工艺。在一些其他的实施例中,上述方法包含上述第二退火工艺,但不包含上述第一退火工艺。在一些其他的实施例中,上述方法包含上述第一退火工艺及上述第二退火工艺。在一些范例中,上述第一退火工艺及/或上述第二退火工艺可以进一步增加施加于铁电层106的拉张应力,并因此可以增加铁电层106的极化。

[0120]

如图14的截面图1400所示,在基板502上形成一遮罩层(masking layer)1402。之后,利用遮罩层1402对半导体层108、铁电层106、第二金属层104,以及第一金属层102进行图案(pattern)化,以形成多层堆叠(multi-layer stack)。在一些实施例中,图案化的操作可以包含干式蚀刻(dry etching)工艺,例如反应离子蚀刻(reactive ion etching(rie))工艺、离子束蚀刻(ion beam etching(ibe))工艺,或是一些其他合适的工艺。在一些实施例中,遮罩层1402可以包含光刻胶光罩(photoresist mask,光刻胶掩膜)、硬遮罩(hard mask),或一些其他合适的遮罩。遮罩层1402可以在图案化完成后被移除。

[0121]

如图15的截面图1500所示,在基板502上形成介电层112,介电层112位在半导体层108的顶面上,以及半导体层108、铁电层106、第二金属层104及第一金属层102的相对的侧壁上。在一些实施例中,形成介电层112包含通过cvd工艺、pvd工艺、ald工艺,或是一些其他合适的工艺在基板502上沉积氧化硅、氮化硅,或是一些其他合适的材料。

[0122]

如图16的截面图1600所示,在基板502上形成一遮罩层1602。之后,利用遮罩层1602图案化介电层112,以在半导体层108上形成多个开口(opening)1604。开口1604使半导体层108顶面上的相对端的部分曝露出来。在一些实施例中,图案化操作可以包含干式蚀刻工艺,或是一些其他合适的工艺。在一些实施例中,遮罩层1602可以包含光刻胶光罩、硬遮罩,或一些其他合适的遮罩。遮罩层1602可以在图案化完成后被移除。

[0123]

如图17的截面图1700所示,在介电层112上及多个开口(图16的开口1604)中沉积一金属层1702,以在上述开口的位置形成源极/漏极结构110。在一些实施例中,金属层1702包含铝、钛、钽、钨、钌、金、铜,或是一些其他合适的金属,并且是通过cvd工艺、pvd工艺、ald工艺,或是一些其他合适的工艺所沉积的。

[0124]

如图18的截面图1800所示,在金属层(图17的金属层1702)及介电层112上执行平坦化(planarization)工艺。上述平坦化工艺移除位在介电层112上方的上述金属层。在一些实施例中,在执行上述平坦化工艺后,源极/漏极结构110的顶面及介电层112的顶面工艺可以是共面的(coplanar)。上述平坦化工艺更形成了源极/漏极结构110。在一些实施例中,举例来说上述平坦化工艺可以包含化学机械式平坦化(chemical mechanical planarization(cmp))或是一些其他合适的平坦化工艺。此外,半导体通道109可以沿着半导体层108在源极/漏极结构110之间的部分延伸。

[0125]

如图19的截面图1900所示,在源极/漏极结构110上形成内连结构406,内连结构406包含多条布置在一或多个介电层中的接线(例如金属线、金属通孔,或相似物)。在一些实施例中,形成内连结构406的操作包含一或多个介电质沉积工艺、一或多个介电层图案化工艺(dielectric patterning processe)、一或多个金属沉积工艺、一或多个平坦化工艺,及/或一些其他合适的工艺。

[0126]

图20用以示意说明制造一集成芯片的一方法2000的实施例的流程图,上述集成芯片包含一第一金属层、位在上述第一金属层上的一第二金属层,以及位在上述第二金属层

上的一铁电层。虽然方法2000在以下内容使用一系列的操作或事件进行描述或示意说明,应该理解操作或事件示意说明的顺序不应该用以做出限制。举例来说,一些操作可以以不同的顺序发生及/或与除去在此示意说明及/或描述的其他操作或事件同时发生。此外,不是所有示意说明的操作都一定需要执行在此描述的一或多个实施例和面向。此外,在此描述的一或多个操作可以以一或多个分开的操作及/或阶段执行。

[0127]

在操作2002中,在一基板上沉积一第一金属层。图8示意说明了对应于操作2002的一些实施例的截面图800。

[0128]

在操作2004中,在上述第一金属层上沉积具有[111]或[110]晶体方向的一第二金属层。图9示意说明了对应于操作2004的一些实施例的截面图900。

[0129]

在操作2006中,在上述第二金属层上沉积一铁电层。图10示意说明了对应于操作2006的一些实施例的截面图1000。

[0130]

在操作2008中,执行一第一退火工艺(例如对于图10所描述的内容)。

[0131]

在操作2010中,在上述铁电层上沉积一或多个额外的层(例如绝缘层、第三金属层,及/或第四金属层)。图11及图12示意说明了对应于操作2010的一些实施例的截面图1100及截面图1200。

[0132]

在操作2012中,在上述铁电层上沉积一半导体层。图13示意说明了对应于操作2012的一些实施例的截面图1300。

[0133]

在操作2014中,执行一第二退火工艺(例如对于图13所描述的内容)。

[0134]

在操作2016中,图案化上述半导体层、上述铁电层、上述第二金属层、上述第一金属层,以在上述基板上形成一多层堆叠。图14示意说明了对应于操作2016的一些实施例的截面图1400。

[0135]

在操作2018中,在上述半导体层上沉积一介电层。图15示意说明了对应于操作2018的一些实施例的截面图1500。

[0136]

在操作2020中,在上述介电层中形成一对源极/漏极结构,上述源极/漏极结构以上述介电层彼此分开。在一些情况下,半导体通道可以沿着上述半导体层在上述源极/漏极结构之间延伸的部分延伸。图16、图17及图18示意说明了对应于操作2020的一些实施例的截面图1600、截面图1700及截面图1800。

[0137]

在操作2022中,在上述源极/漏极结构上形成一内连结构。图19示意说明了对应于操作2022的一些实施例的截面图1900。

[0138]

图21到图30用以示意说明制造一集成芯片的方法的一些选择性的实施例的截面图2100到截面图3000,上述集成芯片包含第一金属层610、位在第一金属层610上的第二金属层612,以及位在第二金属层612上的铁电层614。虽然图21到图30描述了一种方法,但是可以理解图21到图30所公开的结构并不限于这一个方法,而是可以做为独立于方法之外的结构。

[0139]

如图21的截面图2100所示,在位于基板602上的介电层604上形成半导体层605。在半导体层605上形成绝缘层609。在绝缘层609上形成第一金属层610。在第一金属层610上形成第二金属层612。在第二金属层612上形成铁电层614。在铁电层614上形成第三金属层616。在第三金属层616上形成第四金属层618。

[0140]

在一些实施例中,半导体层605是通过cvd工艺、pvd工艺、ald工艺,或是其他合适

的工艺在介电层604上沉积非晶相铟镓锌氧化物(例如a-igzo)、砷化镓、氮化镓、砷化铝镓、一些半导体化合物、非晶相硅、多晶形硅、包含锡的一些铟镓锌氧化物化合物,或是一些其他合适的材料。在一些实施例中,绝缘层609是通过cvd工艺、pvd工艺、ald工艺,或是其他合适的工艺在半导体层605上沉积二氧化硅、氮化硅、氧化铪、掺杂硅的氧化铪,或是一些其他合适的材料所形成的。

[0141]

在一些实施例中,第一金属层610是通过cvd工艺、pvd工艺、ald工艺、pld工艺,或是一些其他合适的工艺,在绝缘层609上沉积铂、钛、氮化钛、钽、氮化钽、钨、铁、镍、铍、铬、钴、锑、铱、钼、锇、钍、钒、以上金属的一些组合,或是一些其他适合的材料所形成的。在一些实施例中,第一金属层610具有大于30纳米、大于50纳米,或是一些其他合适的厚度。

[0142]

第二金属层612在第一金属层610上形成,以具有晶体方向[111]或[110]。在一些实施例中,第二金属层612是通过peald工艺、pld工艺,或是一些其他合适的工艺在第一金属层610上沉积氮化钛或一些其他合适的材料所形成的。

[0143]

在一些实施例中,铁电层614是通过cvd工艺、pvd工艺、ald工艺,或是一些其他合适的工艺在第二金属层612上沉积氧化铪锆(例如hf

x

zr

1-x

oy)、掺杂钪的氮化铝,或是一些其他合适的材料所形成的。

[0144]

第三金属层616在铁电层614上形成,以具有[111]或[110]晶体方向。在一些实施例中,第三金属层616是通过peald工艺、pld工艺,或是一些其他合适的工艺在铁电层614上沉积氮化钛或一些其他合适的材料所形成的。

[0145]

在一些实施例中,第四金属层618是通过cvd工艺、pvd工艺、ald工艺、pld工艺,或是一些其他合适的工艺在第三金属层616上沉积铂、钛、氮化钛、钽、氮化钽、钨、铁、镍、铍、铬、钴、锑、铱、钼、锇、

[0146]

钍、钒、以上金属的一些组合,或是一些其他合适的材料所形成的。在一些实施例中,第四金属层618具有大于30纳米、大于50纳米,或是一些其他合适的厚度。

[0147]

如图22的截面图2200所示,在第四金属层618上形成一遮罩层2202。之后,图案化第四金属层618、第三金属层616、铁电层614、第二金属层612、第一金属层610,以及绝缘层609根据遮罩层2202,以形成多层堆叠。在一些实施例中,图案化的工艺可以包含干式蚀刻工艺,或是一些其他合适的工艺。在一些实施例中,遮罩层2202可以包含光刻胶光罩、硬遮罩,或一些其他合适的遮罩。遮罩层2202可以在图案化完成后被移除。

[0148]

在一些实施例中,在图案化完成后之后执行退火。举例来说,第一金属层610、第二金属层612、铁电层614、第三金属层616,以及第四金属层618使用rta工艺、炉退火工艺,或是一些其他合适的退火工艺进行退火。在一些范例中,上述退火可以增加施加于铁电层614的拉张应力,并因此可以增加铁电层614的极化。

[0149]

如图23的截面图2300所示,在第四金属层618的顶面、第四金属层618的侧壁、第三金属层616的侧壁、铁电层614的侧壁、第二金属层612的侧壁、第一金属层610的侧壁,以及半导体层605的顶面顺应性地(conformally)形成一间隔物层2302。在一些实施例中,间隔物层2302是通过cvd工艺、pvd工艺、ald工艺,或是一些其他合适的工艺在基板602上沉积二氧化硅、氮化硅,或是一些其他合适的材料所形成的。

[0150]

如图24的截面图2400所示,对间隔物层(图23之间隔物层2302)进行蚀刻(etch),以从上述间隔物层形成多个间隔物620。对间隔物层进行蚀刻会从第四金属层618的顶面及

半导体层605的部分顶面移除上述间隔物层。在一些实施例中,上述蚀刻包含干式蚀刻工艺,或是一些其他合适的工艺。在一些实施例中,间隔物620由于上述蚀刻而具有从间隔物620的侧壁延伸到沿第四金属层618的顶面的多个弧形表面(例如,如虚线620a所展示的)。

[0151]

如图25的截面图2500所示,在基板602上形成介电层622,介电层622位在半导体层605的顶面、间隔物620的侧壁、间隔物620的顶面,以及第四金属层618的顶面上。在一些实施例中,介电层622是通过cvd工艺、pvd工艺,或是一些其他合适的工艺在基板602上沉积二氧化硅、氮化硅,或是一些其他合适的材料所形成的。

[0152]

如图26的截面图2600所示,在介电层622上形成一遮罩层2602。之后,利用遮罩层2602图案化介电层622,以在介电层622上形成多个开口2604。开口2604使半导体层605的顶面的一部分曝露出来。在一些实施例中,图案化的工艺可以包含干式蚀刻工艺,或是一些其他合适的工艺。在一些实施例中,图案化的工艺可以包含干式蚀刻工艺,或是一些其他合适的工艺。在一些实施例中,遮罩层2602可以包含光刻胶光罩、硬遮罩,或一些其他合适的遮罩。遮罩层2602可以在图案化完成后被移除。

[0153]

如图27的截面图2700所示,通过掺杂半导体层605在开口2604之下的部分,在开口2604之下于半导体层605中形成一对源极区/漏极区608。在一些实施例中,源极区/漏极区608具有与半导体层605的掺杂类型相反的掺杂类型。在一些实施例中,源极区/漏极区608是通过氩(argon)、氢(hydrogen)、氮(nitrogen),或是氦(helium)等离子体处理(plasma treatment)工艺所形成的。在一些其他实施例中,源极区/漏极区608是通过离子注入(ion implantation)工艺或是一些其他合适的工艺所形成的。

[0154]

此外,半导体通道606可以沿着半导体层605在源极区/漏极区608之间延伸。半导体通道606在半导体层605于源极区/漏极区608之间延伸的中间部分延伸,并且半导体层605的上述中间部分在形成源极区/漏极区608时并没有被掺杂。

[0155]

如图28的截面图2800所示,在多个开口中(图27的开口2604)于基板602上沉积一金属2802,以在上述开口中形成一对源极/漏极接点624。在一些实施例中,金属2802包含铝、钛、钽、钨、钌、金、铜、一些其他合适的金属,或是一些其他合适的材料,并且是通过cvd工艺、pvd工艺、ald工艺,或是一些其他合适的工艺所沉积的。

[0156]

如图29的截面图2900所示,在金属(图28的金属2604)及介电层622上执行一平坦化工艺。在一些实施例中,也在间隔物620及第四金属层618上执行上述平坦化工艺。上述平坦化工艺可以从第四金属层618上移除上述金属及介电层622。在一些实施例中,源极/漏极接点624的顶面、介电层622的顶面、间隔物620的顶面,以及第四金属层618的顶面在执行上述平坦化工艺之后可以是共面的。举例来说,在一些实施例中上述平坦化工艺可以包含cmp或一些其他合适的工艺。

[0157]

如图30的截面图3000所示,在介电层626中形成多条第一金属接线628及第二金属接线630,第一金属接线628及第二金属接线630位在源极/漏极接点624及第四金属层618上。在一些实施例中,在介电层626中形成第一金属接线628及第二金属接线630包含在基板602上沉积介电层626(例如二氧化硅、氮化硅,或是一些其他合适的材料)、使介电层626图案化、在图案化完成的介电层626上沉积金属(铝、钛、钽、钨、钌、金、铜、一些其他合适的金属,或是一些其他合适的材料),以形成多条第一金属接线628及第二金属接线630,以及在上述金属及介电层626上执行平坦化工艺(例如cmp或是相似的工艺)。

[0158]

图31示意说明制造一集成芯片的方法3100的选择性的实施例的流程图,上述集成芯片包含一第一金属层、在上述第一金属层上的一第二金属层,以及在上述第二金属层上的一铁电层。虽然方法3100在以下内容使用一系列的操作或事件进行描述或示意说明,应该理解操作或事件示意说明的顺序不应该用以做出限制。举例来说,一些操作可以以不同的顺序发生及/或与除去在此示意说明及/或描述的其他操作或事件同时发生。此外,不是所有示意说明的操作都一定需要执行在此描述的一或多个实施例和面向。此外,在此描述的一或多个操作可以以一或多个分开的操作及/或阶段执行。

[0159]

在操作3102中,在位于一基板上的一介电层上沉积一半导体层;在上述半导体层上沉积一绝缘层;在上述绝缘层上沉积一第一金属层;在上述第一金属层上沉积一第二金属层;在上述第二金属层上沉积一铁电层;在上述铁电层上沉积一第三金属层;以及在上述第三金属层上沉积一第四金属层。上述第二金属层及上述第三金属层具有[111]或[110]晶体方向。图21示意说明对应于操作3102的一些实施例的截面图2100。

[0160]

在操作3104中,使上述第四金属层、上述第三金属层、上述铁电层、上述第二金属层、上述第一金属层,以及上述绝缘层图案化,以在上述半导体层上形成一多层堆叠。图22示意说明对应于操作3104的一些实施例的截面图2200。

[0161]

在操作3106中,执行退火(例如对于图22所描述的退火)。

[0162]

在操作3108中,在上述半导体层上、上述第四金属层上,以及沿着上述多层堆叠的侧壁沉积一间隔物层。图23示意说明对应于操作3108的一些实施例的截面图2300。

[0163]

在操作3110中,对上述间隔物层进行蚀刻以从上述间隔物层中形成多个间隔物。图24示意说明对应于操作3110的一些实施例的截面图2400。

[0164]

在操作3112中,在上述多层堆叠及上述半导体层上沉积一介电层。图25示意说明对应于操作3112的一些实施例的截面图2500。

[0165]

在操作3114中,对在上述多层堆叠的两侧的上述介电层进行图案化。图26示意说明对应于操作3114的一些实施例的截面图2600。

[0166]

在操作3116中,在上述介电层中形成源极区/漏极区。在一些情况下,一半导体通道沿着上述半导体层于上述源极区/漏极区之间延伸的部分延伸。图27示意说明对应于操作3116的一些实施例的截面图2700。

[0167]

在操作3118中,在上述介电层中于上述源极区/漏极区上形成源极/漏极接点。图28及图29示意说明对应于操作3118的一些实施例的截面图2800及截面图2900。

[0168]

在操作3120中,在上述源极/漏极接点上形成多条金属接线。图30示意说明对应于操作3120的一些实施例的截面图3000。

[0169]

因此,本发明实施例有关于一集成芯片及用以制造上述集成芯片的方法。上述集成芯片包含在铁电层下的第一金属层及第二金属层,以改善上述集成芯片的性能。

[0170]

因此,在一些实施例中本发明有关于集成芯片。上述集成芯片包含:基板、半导体层、一对源极/漏极、第一金属层,以及第二金属层。半导体层位于基板上。该对源极/漏极沿着半导体层排列。第一金属层位在基板上。第二金属层位在第一金属层上。铁电层位在第二金属层上。第一金属层具有第一晶体方向,第二金属层具有与第一晶体方向不同的第二晶体方向。

[0171]

在一些实施例中,第二晶体方向为[110]或[111]。

[0172]

在一些实施例中,集成芯片还包含:第三金属层、第四金属层,以及绝缘层。第三金属层位在铁电层上。第四金属层位在第三金属层上。绝缘层位在铁电层及半导体层之间。

[0173]

在一些实施例中,第三金属层具有第二晶体方向。

[0174]

在一些实施例中,第二金属层及第三金属层包含一第一金属。

[0175]

在一些实施例中,上述集成芯片还包含位在铁电层及半导体层之间的绝缘层。

[0176]

在一些实施例中,第一金属层及第二金属层包含第一金属。

[0177]

在一些实施例中,第一金属层与第二金属层沿着晶界彼此接触。

[0178]

在一些实施例中,铁电层与第二金属层接触。

[0179]

在一些实施例中,第一金属层具有大于50纳米的厚度。

[0180]

在其他实施例中,本发明实施例有关于集成芯片。上述集成芯片包含:基板、半导体层、一对源极/漏极、第一金属层、第二金属层,以及铁电层。半导体层位于基板上。该对源极/漏极沿着半导体层排列。第一金属层位在基板上。第二金属层位在第一金属层上。铁电层位在第二金属层上。第二金属层具有[110]晶体方向。

[0181]

在一些实施例中,第一金属层的晶体方向不同于第二金属层的[110]晶体方向。

[0182]

在一些实施例中,半导体层位在铁电层上,源极/漏极位在半导体层的顶面上。

[0183]

在一些实施例中,集成芯片还包含位于铁电层及半导体层之间的绝缘层。

[0184]

在一些实施例中,集成芯片还包含:第三金属层及第四金属层。第三金属层位于铁电层及绝缘层之间。第四金属层位于第三金属层及绝缘层之间。其中,第三金属层具有[110]晶体方向。

[0185]

在一些实施例中,半导体层位于铁电层及第一金属层下。其中源极/漏极是半导体层的多个掺杂区。其中集成芯片还包含:绝缘层、第三金属层,以及第四金属层。绝缘层位于第一金属层及半导体层之间。第三金属层位于铁电层上。第四金属层位于第三金属层上。其中,第三金属层具有[110]晶体方向。

[0186]

在一些实施例中,源极/漏极是半导体层的多个掺杂区,其中集成芯片还包含:栅极结构及介电结构。栅极结构在半导体层上且于源极/漏极之间延伸。介电结构位于基板上。其中,第一金属层、第二金属层,以及铁电层沉积在介电结构中。

[0187]

在另一些实施例中,本发明实施例有关于制造集成芯片的方法。上述方法包含在基板上沉积半导体层。沿着半导体层形成一对源极/漏极。在基板上沉积第一金属层。在第一金属层上沉积第二金属层。以及在第二金属层上沉积铁电层。第二金属层具有[110]晶体方向。

[0188]

在一些实施例中,上述方法还包含:对第二金属层及铁电层进行退火。

[0189]

在一些实施例中,上述方法还包含:在铁电层上沉积第三金属层,以及在第三金属层上沉积第四金属层。其中,第三金属层具有[110]晶体方向。

[0190]

以上内容概要地说明一些实施例的特征,使得本领域技术人员可以更好的理解本发明的内容。本领域技术人员应该了解他们可以容易地使用本发明作为基础,以设计或修改其他用以执行相同目的及/或达成以上提到的实施例的相同好处的工艺及结构。本领域技术人员也应该了解这样的相等结构并没有离开本发明的构思及范围,且本领域技术人员应该了解可以在此做出多个改变、取代,以及修改而不离开本发明的构思及范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。