1.本发明涉及电子元器件技术领域,尤其涉及一种耦合电感的制作方法及耦合电感。

背景技术:

2.一体成型电感主要包括磁芯本体和绕组本体,是由在绕组本体内埋入金属磁性粉末并压铸而成,其引脚为绕组本体的引出脚直接形成于磁芯本体表面两侧。但对于现有的双线圈 磁粉压制的一体成型耦合电感,则由于其粉体内为双线圈重叠结构,导致压制过程中成型压力较大,造成产品内线圈极易变形,从而导致产品短路和良率低等问题。

3.因此,亟需一种耦合电感的制作方法及耦合电感。

技术实现要素:

4.本发明的一个目的在于提供一种耦合电感的制作方法,可有效提高产品的制作合格率,同时保证产品的性能。

5.如上构思,本发明所采用的技术方案是:

6.耦合电感的制作方法,包括:

7.s1:将线圈绕组焊接于导线架的两侧;

8.s2:将焊接后的所述线圈绕组和所述导线架均放置于模压机内,并向所述线圈绕组内加入软磁磁芯粉料进行压制,以形成单侧电极一体成型电感;

9.s3:将所述单侧电极一体成型电感放入烘箱中进行烘烤;

10.s4:将烘烤后的所述单侧电极一体成型电感进行冷却,并裁切成为多个单颗电感,且在所述单颗电感除端子外的位置设置绝缘层;

11.s5:对喷涂后的所述单颗电感的所述端子进行折弯脚处理,且将每两个所述单颗电感沿所述线圈绕组的轴向相对贴合以形成一个耦合电感,所述耦合电感的两个所述单颗电感的所述端子位于同一侧。

12.可选地,所述导线架包括连接部和两列所述端子,两列所述端子分别设置于垂直所述连接部延伸方向的两侧,且每列所述端子包括沿所述连接部延伸方向间隔设置的n组所述端子,一组所述端子连接一个所述线圈绕组,以形成所述单侧电极一体成型电感,一个所述单侧电极一体成型电感包括2n个所述单颗电感。

13.可选地,在s2中,对所述单侧电极一体成型电感进行压制的温度为t,20℃≤t≤25℃,对所述单侧电极一体成型电感进行压制的压力为p,6nt≤p≤7nt。

14.可选地,在s2中,向每个所述线圈绕组中加入的软磁磁芯粉料的质量为m,0.7g≤m≤0.8g。

15.可选地,在s4中,所述单颗电感的绝缘层采用喷涂工艺形成,对所述单颗电感进行喷涂前需要对所述单颗电感的所述端子包覆高温保护层。

16.可选地,每两个所述单颗电感通过胶水组合成一个所述耦合电感。

17.可选地,还包括s6:对所述耦合电感进行烘烤,以使胶水固化。

18.可选地,每两个所述单颗电感通过卡扣组合成一个所述耦合电感,所述卡扣的两端分别抵接两个所述单颗电感相背离的一侧。

19.本发明的另一个目的在于提供一种耦合电感,其产品性能良好,产品制作合格率高。

20.如上构思,本发明所采用的技术方案是:

21.耦合电感,利用上述的耦合电感的制作方法制作而成。

22.可选地,所述耦合电感包括两个单颗电感,两个所述单颗电感沿自身线圈绕组的轴向相对贴合,且两个所述单颗电感的端子位于同一侧。

23.本发明的有益效果为:

24.本发明提出的耦合电感的制作方法,包括以下步骤:s1:将线圈绕组焊接于导线架的两侧;s2:将焊接后的线圈绕组和导线架均放置于模压机内,并向线圈绕组内加入软磁磁芯粉料进行压制,以形成单侧电极一体成型电感;s3:将单侧电极一体成型电感放入烘箱中进行烘烤;s4:将烘烤后的单侧电极一体成型电感进行冷却,并裁切成为多个单颗电感,且在单颗电感除端子外的位置设置绝缘层;s5:对喷涂后的单颗电感的端子进行折弯脚处理,且将每两个单颗电感沿线圈绕组的轴向相对贴合,以形成一个耦合电感,耦合电感的两个单颗电感的端子位于同一侧。因其无须同时对重叠结构的双线圈进行压制,可降低压制过程中所需的成型压力,同时避免双线圈一体成型耦合电感产品短路和线圈歪斜的问题,能够有效提高产品的制作合格率,同时保证产品的性能。

25.本发明提出的耦合电感,利用上述的耦合电感的制作方法制作而成,其产品性能良好,产品制作合格率高。

附图说明

26.图1是现有技术中支脚和线圈的连接示意图;

27.图2是本发明实施例提供的耦合电感的制作方法的流程图;

28.图3是本发明实施例提供的单侧电极一体成型电感的烘烤参数曲线图;

29.图4是本发明实施例提供的导线架的结构示意图;

30.图5是本发明实施例提供的导线架和线圈绕组的连接示意图;

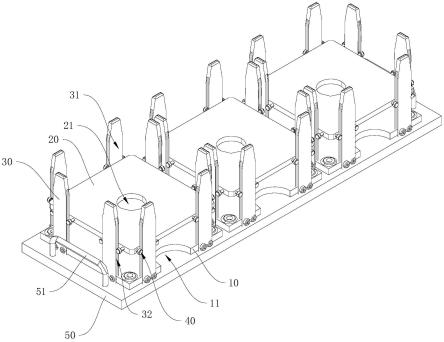

31.图6是本发明实施例提供的导线架和线圈绕组压制后的结构示意图;

32.图7是本发明实施例提供的单颗电感的结构示意图;

33.图8是本发明实施例提供的耦合电感的结构示意图。

34.11’、支脚;12’、电感线圈;

35.1、单侧电极一体成型电感;11、导线架;111、连接部;112、端子;12、线圈绕组;101、单颗电感;102、耦合电感。

具体实施方式

36.为使本发明解决的技术问题、采用的技术方案和达到的技术效果更加清楚,下面结合附图并通过具体实施方式来进一步说明本发明的技术方案。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便

于描述,附图中仅示出了与本发明相关的部分而非全部。

37.在本发明的描述中,除非另有明确的规定和限定,术语“相连”、“连接”、“固定”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

38.在本发明中,除非另有明确的规定和限定,第一特征在第二特征之“上”或之“下”可以包括第一和第二特征直接接触,也可以包括第一和第二特征不是直接接触而是通过它们之间的另外的特征接触。而且,第一特征在第二特征“之上”、“上方”和“上面”包括第一特征在第二特征正上方和斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”包括第一特征在第二特征正下方和斜下方,或仅仅表示第一特征水平高度小于第二特征。

39.在本实施例的描述中,术语“上”、“下”、“左”、“右”等方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述和简化操作,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”仅仅用于在描述上加以区分,并没有特殊的含义。

40.下面结合附图并通过具体实施方式来进一步说明本发明的技术方案。

41.如图2至图8所示,本实施例提供一种耦合电感的制作方法,能够有效提高产品的制作合格率,同时保证产品的性能。其具体步骤如下:

42.s1:将线圈绕组12焊接于导线架11的两侧;

43.s2:将焊接后的线圈绕组12和导线架11均放置于模压机内,并向线圈绕组12内加入软磁磁芯粉料进行压制,以形成单侧电极一体成型电感1;

44.s3:将单侧电极一体成型电感1放入烘箱中进行烘烤;

45.s4:将烘烤后的单侧电极一体成型电感1进行冷却,并裁切成为多个单颗电感101,且在单颗电感101除端子112外的位置设置绝缘层;

46.s5:对喷涂后的单颗电感101的端子112进行折弯脚处理,且将每两个单颗电感101沿线圈绕组12的轴向相对贴合,以形成一个耦合电感102,耦合电感102的两个单颗电感101的端子112位于同一侧。

47.上述方法通过先制作单颗电感101,而后再组合成耦合电感102,既可具有双线圈一体成型耦合电感的优势,而且因为无须同时对重叠结构的双线圈进行压制,还可降低压制过程中所需的成型压力,同时避免双线圈一体成型耦合电感产品短路和线圈歪斜的问题,以提高产线生产良率,降低设备成本。另外,单颗电感101的端子112位于同一侧,也为高质量的耦合电感102的制作提供了可能,可有效保证耦合电感102的产品性能。因为现有的一体式电感其端子112从两侧引出,这导致其无法将单颗电感101组合成耦合电感102使用,或者在组合后因耦合电感102的四个端子112不在同一平面,而无法焊接到pcb板上,而本实施例提供的单颗电感101在组合成耦合电感102后,其四个端子112均位于同一平面,可有效解决这一问题。

48.具体地,本实施中导线架11的结构如图4所示,导线架11包括连接部111和两列端子112,两列端子112分别设置于垂直连接部111延伸方向的两侧,且每列端子112包括沿连

接部111延伸方向间隔设置的n组端子112。如图5所示,一组端子112连接一个线圈绕组12,以形成单侧电极一体成型电感1,即一个单侧电极一体成型电感1包括2n个单颗电感101。相比于现有技术中如图1所示的支脚11’和电感线圈12’的连接结构,将线圈绕组12焊接在导线架11的两侧,除可为高质量组合式的耦合电感102的制作提供基础之外,还可提高导线架11的利用率以及产品成型产量,降低生产成本。优选地,导线架11为镀锡铜片。

49.本实施例提供的耦合电感的制作方法还进一步说明了耦合电感102在制作过程中的相关参数,以保证产品性能优越。

50.可选地,在s2中,向每个线圈绕组12中加入的软磁磁芯粉料的质量为m,0.7g≤m≤0.8g。

51.可选地,在s2中,对单侧电极一体成型电感1进行压制的温度为t,20℃≤t≤25℃,对单侧电极一体成型电感1进行压制的压力为p,6nt≤p≤7nt。

52.可选地,在s3中,对单侧电极一体成型电感1进行烘烤的温度和时间如图3中的曲线所示。

53.另外可知的,单颗电感101的端子112在电感中主要起导通线圈绕组12和电子元器件的作用,而单颗电感101上的绝缘层是采用喷涂工艺形成的,因此在对单颗电感101进行喷涂前需要对单颗电感101的端子112包覆高温保护层。优选地,高温保护层为包覆于端子112上的高温胶带。

54.进一步可选地,为使两个单颗电感101贴合成为一个耦合电感102,可采用如下方法对两个单颗电感101进行相对固定。

55.优选地,可将每两个单颗电感101通过胶水组合成一个耦合电感102。

56.或者是将每两个单颗电感101通过卡扣组合成一个耦合电感102,卡扣的两端分别抵接两个单颗电感101相背离的一侧。卡扣可为c字型,c字型的两端即为卡扣的抵接部,设置与两个单颗电感101的厚度之和相适配的卡扣,以使两个抵接部可与单颗电感101的外表面紧密接触,每个耦合电感102通过至少一个卡扣连接。

57.或者是可同时设置胶水和卡扣,以保证每两个单颗电感101相对固定的稳定性。

58.更进一步可选地,为增加产品稳定性,本实施例提供的耦合电感的制作方法还包括s6:对耦合电感102进行烘烤,以使胶水固化。即对于采用胶水组合形成的耦合电感102,可将其放入烘箱中进行烘干,以使胶水完全固化。优选地,烘箱设置温度范围为55℃-65℃,烘箱设置时间范围为15min-25min。

59.本实施例还提供利用如上耦合电感的制作方法制作而成的耦合电感102,其产品性能良好,产品制作合格率高。如图8所示,该耦合电感102包括两个单颗电感101,两个单颗电感101沿自身线圈绕组12的轴向相对贴合,且两个单颗电感101的端子112位于同一侧。另外,进一步提供利用如上耦合电感的制作方法制作而成的单颗电感101及耦合电感102的相关参数,以有效说明该耦合电感102既能够保证使用较少的空间,还能够保证所需的电感量,以满足精密集成电路的需求。

60.参照图7,本实施例的单颗电感101的制作标准为:单颗电感101的长度为a,7mm≤a≤7.5mm;单颗电感101的宽度为b,6.75mm≤b≤7.15mm;单颗电感101的厚度为c,c≤3.5mm;垂直端子112的延伸方向,端子112的宽度为d,1.4mm≤d≤1.8mm;沿端子112的延伸方向,端子112的末端(未连接单颗电感101的主体的一端)的折弯长度为e,1.3mm≤e≤1.9mm;相邻

两个端子112之间的间距为f,1.35mm≤f≤1.75mm。

61.而下表则进一步列举出制造过程中单颗电感101的具体尺寸参数,以说明如上耦合电感的制作方法在制造过程中可制造出符合要求的单颗电感101。其中,第1个单颗电感101的长度为7.22mm,宽度为6.94mm,厚度为3.38mm,端子112的宽度为1.62mm,端子112的末端的折弯长度为1.50mm,相邻两个端子112之间的间距为1.58mm。第2个单颗电感101的长度为7.30mm,宽度为6.92mm,厚度为3.40mm,端子112的宽度为1.63mm,端子112的末端的折弯长度为1.42mm,相邻两个端子112之间的间距为1.42mm。第3个单颗电感101的长度为7.28mm,宽度为6.99mm,厚度为3.31mm,端子112的宽度为1.60mm,端子112的末端的折弯长度为1.43mm,相邻两个端子112之间的间距为1.65mm。

62.no.abcdef17.226.943.381.621.501.5827.306.923.401.631.421.4237.286.993.311.601.431.65

63.进一步地,单颗电感101的性能参数标准为:单颗电感101的初始电感值为l1,8μh≤l1≤12μh,单颗电感101的通电后的电感值为l2,其通电电流为5.8a,则叠加变化率(l2/l1-1)≥-30%,直流电阻值dcr≤49.0mω。

64.而下表则进一步列举出上述三个单颗电感101的具体性能参数,其中,第1个单颗电感101的初始电感值为9.610μh,通电后的电感值为8.010μh,叠加变化率为-16.65%,直流电阻值dcr为31mω。第2个单颗电感101的初始电感值为9.330μh,通电后的电感值为7.740μh,叠加变化率为-17.04%,直流电阻值dcr为29mω。第3个单颗电感101的初始电感值为9.370μh,通电后的电感值为7.840μh,叠加变化率为-16.33%,直流电阻值dcr为32mω。

65.no.l1(μh)l2(μh)叠加变化率dcr(mω)19.6108.010-16.65%3129.3307.740-17.04%2939.3707.840-16.33%32

66.具体地,采用如上耦合电感的制作方法可制造x个单感电感101,并进一步得到x/2个耦合电感102,下表示例性的列出四个耦合电感102的性能和尺寸参数。

67.no.htl1l2叠加变化率dcr(mω)16.769.6108.010-16.65%3126.809.3307.740-17.04%2936.629.3707.840-16.33%3246.849.4907.850-17.28%34

68.参照图8所示,其中,第1个耦合电感102的主体(不包括端子112)的厚度ht为6.76mm,初始电感值l1为9.610μh,通电后的电感值l2为8.010μh。第2个耦合电感102的主体(不包括端子112)的厚度ht为6.80mm,初始电感值l1为9.330μh,通电后的电感值l2为7.740μh。第3个耦合电感102的主体(不包括端子112)的厚度ht为6.62mm,初始电感值l1为9.370μh,通电后的电感值l2为7.840μh。第4个耦合电感102的主体(不包括端子112)的厚度ht为

6.84mm,初始电感值l1为9.490μh,通电后的电感值l2为7.850μh。即通过检测可知,采用本实施例提供的耦合电感的制作方法制作的耦合电感102,符合精密集成电路对于耦合电感102的尺寸要求。

69.另外,第1个耦合电感102的叠加变化率为-16.65%;第2个耦合电感102的叠加变化率为-17.04%;第3个耦合电感102的叠加变化率为-16.33%;第4个耦合电感102的叠加变化率为-17.28%。耦合电感102的叠加变化率要求一般不小于-30%,即上述耦合电感102的叠加变化率同样满足本行业要求。

70.而第1个耦合电感102的直流电阻值dcr为31mω;第2个耦合电感102的直流电阻值dcr为29mω;第3个耦合电感102的直流电阻值dcr为32mω;第4个耦合电感102的直流电阻值dcr为34mω。耦合电感的直流电阻值dcr越小越好,一般不大于49.0mω,即上述耦合电感102的直流电阻值同样满足本行业要求。

71.以上实施方式只是阐述了本发明的基本原理和特性,本发明不受上述实施方式限制,在不脱离本发明精神和范围的前提下,本发明还有各种变化和改变,这些变化和改变都落入要求保护的本发明范围内。本发明要求保护范围由所附的权利要求书及其等效物界定。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。