具有高沟道迁移率的sicmosfet及其制备方法

技术领域

1.本发明涉及sicmosfet器件技术领域,具体涉及具有高沟道迁移率的sicmosfet及其制备方法。

背景技术:

2.碳化硅(sic)材料具有禁带宽度大、击穿场强高、介电常数小等独特的特性,使其在场效晶体管(mosfet)的应用方面倍受青睐,但是由于sic mosfet器件的沟道迁移率较低,导致严重限制了sicmosfet器件的发展。

技术实现要素:

3.本发明的目的是针对现有技术的缺陷,提供一种具有高沟道迁移率的sicmosfet及其制备方法,通过在sicmosfet内部形成由n型块和p型块组成的隔离层对氧化层进行阻挡,减少沟道受到的界面粗糙散射的影响,同时还可以在沟道处形成一电子通道,达到提升沟道迁移率的效果。

4.鉴于上述问题,本发明提出的技术方案是:

5.具有高沟道迁移率的sicmosfet,包括:衬底,所述衬底上方依次设有n-漂移层、n 漂移层和p 源区层,n-漂移层、所述n 漂移层和所述p 源区层的内部由内至外依次设有栅极、氧化层、n型块和p型块,所述n 源区层的顶部设有源极金属层,所述衬底下方设有漏极金属层。

6.为了更好的实现本发明技术方案,还采用了如下技术措施。

7.具有高沟道迁移率的sicmosfet的制备方法,包括以下步骤:

8.s1,在sic衬底的顶部依次通过外延工艺生成n-漂移区和n 漂移层;

9.s2,在所述n-漂移区和所述n 漂移层上蚀刻出一凹槽a,采用外延工艺在该凹槽a的内部生成sic层,并采用离子注入形成n型块;

10.s3,在所述n型块上蚀刻出一凹槽b,采用外延工艺在该凹槽b的内部生成sic层,并采用离子注入形成p型块;

11.s4,在n 漂移层的上方采用通过外延工艺生成p 源区层;

12.s5,将p 源区层的上方用于蚀刻工艺,蚀刻出一由所述p 源区层至所述n-漂移层的凹槽c,所述凹槽c依次贯穿所述p 源区层、n型块和n-漂移层;

13.s6,采用通过低压热壁化学气相沉积法在凹槽c的表面沉积一层氧化层;

14.s7,在所述氧化层上设置栅极;

15.s8,在所述n 源区层上设置源极金属层;

16.s9,采用机械减薄的方式去掉所述衬底,在所述n-漂移层的底部设置漏极金属层。

17.进一步的,所述步骤s1中,所述n-漂移区的厚度为10μm,掺杂浓度为1

×

10

14

cm-3

~2

×

10

14

cm-3

。

18.进一步的,所述步骤s1中,所述n 漂移层的厚度为5μm,掺杂浓度为1

×

10

17

cm-3

~2

×

10

17

cm-3

。

19.进一步的,所述p型块和所述n型块的深度、厚度以及采用的注入能量和注入剂量均完全一致。

20.进一步的,所述p 源区层的厚度为3μm。

21.进一步的,所述氧化层为sio2。

22.相对于现有技术而言,本发明的有益效果是:通过在sicmosfet内部形成由n型块和p型块组成的隔离层对氧化层进行阻挡,减少沟道受到的界面粗糙散射的影响,同时还可以在沟道处形成一电子通道,达到提升沟道迁移率的效果。

23.上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够更明显易懂,以下特举本发明的具体实施方式。

附图说明

24.图1为本发明实施例公开的制备sicmosfet器件的过程示意图1;

25.图2为本发明实施例公开的制备sicmosfet器件的过程示意图2;

26.图3为本发明实施例公开的制备sicmosfet器件的过程示意图3;

27.图4为本发明实施例公开的制备sicmosfet器件的过程示意图4;

28.图5为本发明实施例公开的制备sicmosfet器件的过程示意图5;

29.图6为本发明实施例公开的制备sicmosfet器件的过程示意图6;

30.图7为本发明实施例公开的制备sicmosfet器件的过程示意图7;

31.图8为本发明实施例公开的制备sicmosfet器件的过程示意图8;

32.图9为本发明实施例公开的制备sicmosfet器件的过程示意图9;

33.图10为本发明实施例公开的制备sicmosfet器件的过程示意图10;

34.图11为本发明实施例公开的具有高沟道迁移率的sicmosfet的制备方法的流程示意图。

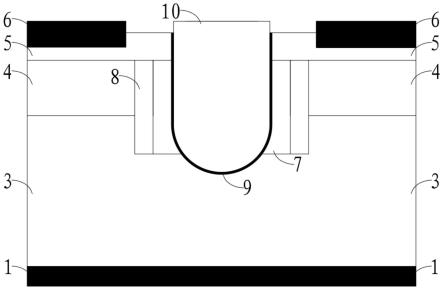

35.附图标记:1、漏极金属层;2、衬底;3、n、漂移层;4、p型阱;5、n 源区层;6、源极金属层;7、p型块;8、n型块;9、氧化层;10、栅极。

具体实施方式

36.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。

37.参照附图1-10所示,具有高沟道迁移率的sicmosfet,其包括衬底2,衬底2上方依次设有n3-漂移层、n3 漂移层和p 源区层,n3-漂移层、n3 漂移层和p 源区层的内部由内至外依次设有栅极10、氧化层9、n型块8和p型块7,n 源区层5的顶部设有源极金属层6,衬底2下方设有漏极金属层1。

38.参照附图1-11所示,本发明还提出具有高沟道迁移率的sicmosfet的制备方法,包括以下步骤:

39.s1,在sic衬底2的顶部依次通过外延工艺生成n3-漂移区和n3 漂移层;

40.具体的,如图1~3所示,在温度为1200℃,压力为210mbar的条件下,在sic衬底2的

上方首先通过外延工艺生成厚度为10μm的n3-漂移区,其中设置的掺杂浓度为1

×

10

14

cm-3

~2

×

10

14

cm-3

,然后,通过外延工艺在n3-漂移区的上方生成厚度为5μm的n3 漂移层,其中设置的掺杂浓度为1

×

10

17

cm-3

~2

×

10

17

cm-3

。

41.s2,在n3-漂移区和n3 漂移层上蚀刻出一凹槽a,采用外延工艺在该凹槽a的内部生成sic层,并采用离子注入形成n型块8;

42.具体的,如图4所示,通过光刻和刻蚀来形成凹槽a(未在附图4中进行标注),蚀刻完成后,通过外延工艺在凹槽a的内部生成未注入离子的sic层,先后采用500kev、400kev、300kev、200kev和100kev的注入能量,将注入剂量为5.6

×

10

13

cm-2

、4.51

×

10

13

cm-2

、3.82

×

10

13

cm-2

和2.77

×

10

13

cm-2

的离子注入到sic层中形成n型块8。

43.s3,在n型块8上蚀刻出一凹槽b,采用外延工艺在该凹槽b的内部生成sic层,并采用离子注入形成p型块7;

44.具体的,如图5所示,通过光刻和刻蚀来形成凹槽b(未在附图5中进行标注),蚀刻完成后,通过外延工艺在凹槽b的内部生成未注入离子的sic层,先后采用500kev、400kev、300kev、200kev和100kev的注入能量,将注入剂量为5.6

×

10

13

cm-2

、4.51

×

10

13

cm-2

、3.82

×

10

13

cm-2

和2.77

×

10

13

cm-2

的离子注入到sic层中形成n型块8。

45.s4,在n3 漂移层的上方采用通过外延工艺生成p 源区层;

46.具体的,如图6所示,p 源区层的厚度为3μm。

47.s5,将p 源区层的上方用于蚀刻工艺,蚀刻出一由p 源区层至n3-漂移层的凹槽c,凹槽c依次贯穿p 源区层、n型块8和n3-漂移层;

48.s6,采用通过低压热壁化学气相沉积法在凹槽c的表面沉积一层氧化层9;

49.具体的,如图7所示,通过低压热壁化学气相沉积法在凹槽c的内壁表面沉积一层厚度为0.45μm的sio2层。

50.s7,如图8所示,在氧化层9上设置栅极10;

51.s8,如图9所示,在n 源区层5上设置源极金属层6;

52.s9,如图10所示,采用机械减薄的方式去掉衬底2,在n3-漂移层的底部设置漏极金属层1。

53.本发明提供一种具有高沟道迁移率的sicmosfet,通过在sicmosfet内部形成由n型块8和p型块7组成的隔离层对氧化层9进行阻挡,减少沟道受到的界面粗糙散射的影响,同时还可以在沟道处形成一电子通道,达到提升沟道迁移率的效果。

54.显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。