一种pcie数据传输方法及相关装置

技术领域

1.本技术涉及计算机技术领域,特别涉及一种pcie数据传输方法、另一种pcie数据传输方法、两种pcie数据传输装置、计算设备以及计算机可读存储介质。

背景技术:

2.pcie(peripheral component interconnect express,高速串行计算机扩展总线标准)是一种常用的高速传输协议,通常用于主机与各种外部设备之间的数据传输,如pcie接口内存、网卡、gpu(graphics processing unit,图形处理器)、fpga(field programmable gate array,现场可编程逻辑门阵列)等一系列设备。在pcie与外部设备通信过程中,一般会使用dma(direct memory access,直接存储器访问)技术来进行数据的搬移。在数据搬移过程中,cpu(central processing unit,中央处理器)将总线控制权限交给dma控制器,dma控制器搬移完数据后上报中断给cpu。该过程可以释放cpu的压力,提高传输效率。

3.相关技术中,一般采用dma实现方式主要分为块dma、链式dma。但是,无论是块dma还是链式dma,在传输小包时,带宽利用率都会严重下降,造成极大的性能浪费。同时,频繁使用dma搬移小包数据还有可能导致cpu接收大量中断,极其容易导致主机挂死,降低数据传输的稳定性。

4.因此,如何提高带宽利用率,提高主机的运行可靠性是本领域技术人员关注的重点问题。

技术实现要素:

5.本技术的目的是提供一种pcie数据传输方法、另一种pcie数据传输方法、两种pcie数据传输装置、计算设备以及计算机可读存储介质,以提高pcie带宽的利用率,提高主机运行的可靠性。

6.为解决上述技术问题,本技术提供一种pcie数据传输方法,包括:判断待传输的pcie数据包的长度是否小于预设长度;若是,则通过基址寄存器的空间和协议转化器将所述pcie数据包进行数据传输;若否,则通过dma方式对所述pcie数据包进行数据读写。

7.可选的,通过基址寄存器的空间和协议转化器将所述pcie数据包进行数据传输,包括:当所述pcie数据包为写数据时,通过所述基址寄存器的空间向对应的地址写入所述pcie数据包;当所述pcie数据包为读数据时,通过所述基址寄存器的空间从对应的地址读取所述pcie数据包。

8.可选的,当所述pcie数据包为写数据时,通过所述基址寄存器的空间向对应的地址写入所述pcie数据包,包括:

当所述pcie数据包为写数据时,将所述pcie数据包写入所述基址寄存器的空间;将所述基址寄存器的空间中的所述pcie数据包放入写数据通道,并通过所述写数据通道将所述pcie数据包传输至对应的地址。

9.可选的,当所述pcie数据包为写数据时,将所述pcie数据包写入所述基址寄存器的空间,包括:当所述pcie数据包为写数据时,通过向写地址通道配置对应的地址;将所述pcie数据包写入所述基址寄存器的空间。

10.可选的,还包括:读取所述基址寄存器的空间的数据个数;当所述数据个数为零时,发送数据写入完成消息。

11.可选的,当所述pcie数据包为读数据时,通过所述基址寄存器的空间从对应的地址读取所述pcie数据包,包括:当所述pcie数据包为读数据时,控制读地址通道获取所述pcie数据包;将所述pcie数据包放入到所述基址寄存器的空间;将所述基址寄存器的空间中的所述pcie数据包返回至上位机。

12.可选的,当所述pcie数据包为读数据时,控制读地址通道获取所述pcie数据包,包括:当所述pcie数据包为读数据时,配置读数据的初始地址和总长度;基于所述读数据的初始地址和总长度控制读地址通道获取所述pcie数据包。

13.可选的,还包括:读取所述基址寄存器的空间的数据个数;当所述数据个数为零时,发送数据读取完成消息。

14.可选的,通过dma方式对所述pcie数据包进行数据读写,包括:通过块dma方式对所述pcie数据包进行数据读写。

15.可选的,通过dma方式对所述pcie数据包进行数据读写,包括:通过链式dma方式对所述pcie数据包进行数据读写。

16.可选的,判断待传输的pcie数据包的长度是否小于预设长度,包括:判断待传输的pcie数据包的长度是否小于dma传输的最小包长度。

17.可选的,判断待传输的pcie数据包的长度是否小于预设长度,包括:fpga设备判断待传输的pcie数据包的长度是否小于预设长度。

18.可选的,所述fpga设备的接口总线为标准axi总线。

19.本技术还提供一种pcie数据传输方法,包括:上位机设备向下位设备发送数据传输指令,以便所述下位设备判断所述数据传输指令对应的待传输的pcie数据包的长度是否小于预设长度;若是,则通过基址寄存器的空间和协议转化器将所述pcie数据包进行数据传输;若否,则通过dma方式对所述pcie数据包进行数据读写;返回传输完成消息;接收到所述传输完成消息。

20.本技术还提供一种pcie数据传输装置,包括:包长度判断模块,用于判断待传输的pcie数据包的长度是否小于预设长度;

小数据包传输模块,用于当所述pcie数据包的长度小于预设长度时,通过基址寄存器的空间和协议转化器将所述pcie数据包进行数据传输;大数据包传输模块,用于当所述pcie数据包的长度大于等于预设长度时,通过dma方式对所述pcie数据包进行数据读写。

21.本技术还提供一种pcie数据传输装置,包括:传输指令发送模块,用于向下位设备发送数据传输指令,以便所述下位设备判断所述数据传输指令对应的待传输的pcie数据包的长度是否小于预设长度;若是,则通过基址寄存器的空间和协议转化器将所述pcie数据包进行数据传输;若否,则通过dma方式对所述pcie数据包进行数据读写;返回传输完成消息;传输完成模块,用于接收到所述传输完成消息。

22.本技术还提供一种pcie外接设备,包括:pcie通信模块,用于实现与主机通信的物理链路层和协议层;总线协议互联模块,用于总线之间的互联;协议转化模块,用于将基址寄存器的空间的读写数据转化到dma读写数据接口;存储控制接口模块,用于将存储接口转化为标准axi总线接口。

23.可选的,所述协议转化模块,包括:寄存器控制模块,用于对基址寄存器的空间进行配置;写控制模块,用于控制写地址通道、写响应通道,以及将基址寄存器的空间中的数据放入写数据通道;读控制模块,用于控制读地址通道以及将读数据通道内数据放入到基址寄存器的空间中。

24.本技术还提供一种计算设备,包括:存储器,用于存储计算机程序;处理器,用于执行所述计算机程序时实现如上所述的pcie数据传输方法的步骤。

25.本技术还提供一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如上所述的pcie数据传输方法的步骤。

26.本技术所提供的一种pcie数据传输方法,包括:判断待传输的pcie数据包的长度是否小于预设长度;若是,则通过基址寄存器的空间和协议转化器将所述pcie数据包进行数据传输;若否,则通过dma方式对所述pcie数据包进行数据读写。

27.通过先判断待传输的pcie数据包的长度是否小于预设长度,如果小于预设长度则说明该数据包为小数据包,则通过基址寄存器的空间将该pcie数据包进行传输,而不采用dma的方式进行传输,当大于预设长度时,通过dma方式将pcie数据包进行数据读写,实现了对小数据包采用非dma的方式进行数据传输,避免了dma方式存在的问题,提高了数据传输的效率,降低了因多次大量dma请求存在的问题。提高了传输的稳定性。

28.本技术还提供另一种pcie数据传输方法、两种pcie数据传输装置、计算设备以及计算机可读存储介质,具有以上有益效果,在此不作赘述。

附图说明

29.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现

有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

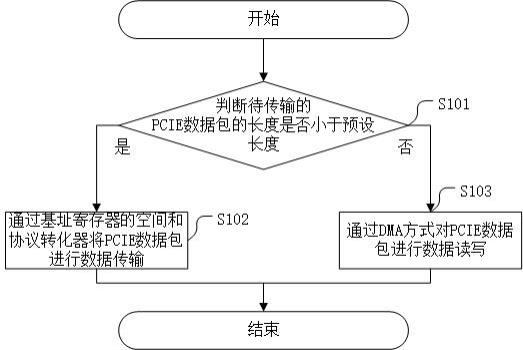

30.图1为本技术实施例所提供的一种pcie数据传输方法的流程图;图2为本技术实施例所提供的一种pcie数据传输方法的系统框图;图3为本技术实施例所提供的一种pcie数据传输方法的协议转化模块的结构示意图;图4为本技术实施例所提供的另一种pcie数据传输方法的流程图;图5为本技术实施例所提供的一种pcie数据传输装置的结构示意图;图6本技术实施例所提供的一种计算设备的结构示意图。

具体实施方式

31.本技术的核心是提供一种pcie数据传输方法、另一种pcie数据传输方法、两种pcie数据传输装置、计算设备以及计算机可读存储介质,以提高pcie带宽的利用率,提高主机运行的可靠性。

32.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

33.相关技术中,一般采用dma实现方式主要分为块dma、链式dma。但是,无论是块dma还是链式dma,在传输小包时,带宽利用率都会严重下降,造成极大的性能浪费。同时,频繁使用dma搬移小包数据还有可能导致cpu接收大量中断,极其容易导致主机挂死,降低数据传输的稳定性。

34.因此,本技术提供一种pcie数据传输方法,通过先判断待传输的pcie数据包的长度是否小于预设长度,如果小于预设长度则说明该数据包为小数据包,则通过基址寄存器的空间将该pcie数据包进行传输,而不采用dma的方式进行传输,当大于预设长度时,通过dma方式将pcie数据包进行数据读写,实现了对小数据包采用非dma的方式进行数据传输,避免了dma方式存在的问题,提高了数据传输的效率,降低了因多次大量dma请求存在的问题。提高了传输的稳定性。

35.以下通过一个实施例,对本技术提供的一种pcie数据传输方法进行说明。

36.请参考图1,图1为本技术实施例所提供的一种pcie数据传输方法的流程图。

37.本实施例中,该方法可以包括:s101,判断待传输的pcie数据包的长度是否小于预设长度;本步骤旨在判断待传输的pcie数据包的长度是否小于预设长度。也就是判断该pcie数据包是否为小数据包。

38.其中,预设长度可以是基于技术人员的经验设定,也可以基于历史的传输数据中存在大量请求的数据包大小进行设定。

39.进一步的,本步骤可以包括:判断待传输的pcie数据包的长度是否小于dma传输的最小包长度。

40.可见,本步骤可以包括判断待传输的pcie数据包的长度是否小于dma传输的最小包长度。其中,dma传输过程中存在按照固定的数据包长度进行数据搬运的过程。因此,存在多个不同长度的数据包大小,本可选方案中选择最小的包长度即可。

41.进一步的,本步骤可以包括:fpga设备判断待传输的pcie数据包的长度是否小于预设长度。

42.可见,本可选方案中主要是说明可以通过fpga设备判断待传输的pcie数据包的长度是否小于预设长度。其中,还可以是数字ic(integrated circuit,集成电路)。

43.其中,fpga设备的接口总线为标准axi(advanced extensible interface,一种总线协议)总线。

44.s102,若是,则通过基址寄存器的空间和协议转化器将pcie数据包进行数据传输;在s101的基础上,本步骤旨在通过基址寄存器的空间和协议转化器将pcie数据包进行数据传输。当该数据包的长度小于预设长度时,通过基址寄存器的空间和协议转化器将pcie数据包进行数据传输。也就是,采用设备中具备的基址寄存器的空间对数据包进行搬运。

45.其中,基址寄存器(bar,base address register,基地址寄存器)的空间用于下位设备的寄存器配置。

46.可见,通过本步骤可以直接采用下位设备中的基址寄存器的空间进行小数据的传输,而不用采用dma的方式进行传输,提高了数据传输的效率。

47.进一步的,本步骤可以包括:s1021,当pcie数据包为写数据时,通过基址寄存器的空间向对应的地址写入pcie数据包;s1022,当pcie数据包为读数据时,通过基址寄存器的空间从对应的地址读取pcie数据包。

48.可见,本可选方案主要是为了说明不同读写情况如何进行处理。本可选方案中,当pcie数据包为写数据时,通过基址寄存器的空间向对应的地址写入pcie数据包;当pcie数据包为读数据时,通过基址寄存器的空间从对应的地址读取pcie数据包。

49.其中,当写数据时,也就是将数据从基址寄存器的空间传输至对应的写数据通道。当读数据时,将数据从读数据通道传输至基址寄存器的空间。可见,该过程中通过基址寄存器的空间进行数据的搬运,而不需要采用dma等的方式进行数据传输。

50.进一步的,s1021可以包括:步骤1,当pcie数据包为写数据时,将pcie数据包写入基址寄存器的空间;步骤2,将基址寄存器的空间中的pcie数据包放入写数据通道,并通过写数据通道将pcie数据包传输至对应的地址。

51.可见,本可选方案主要是为了说明如何写数据。本可选方案中,当pcie数据包为写数据时,将pcie数据包写入基址寄存器的空间;将基址寄存器的空间中的pcie数据包放入写数据通道,并通过写数据通道将pcie数据包传输至对应的地址。

52.进一步的,该上一可选方案中的步骤1可以包括:步骤1,当pcie数据包为写数据时,通过向写地址通道配置对应的地址;步骤2,将pcie数据包写入基址寄存器的空间。

53.可见,本可选方案主要是为了说明如何写数据。本可选方案中,当pcie数据包为写数据时,通过向写地址通道配置对应的地址;将pcie数据包写入基址寄存器的空间。

54.进一步的,本实施例还可以包括:步骤1,读取基址寄存器的空间的数据个数;步骤2,当数据个数为零时,发送数据写入完成消息。

55.可见,本可选方案主要是为了说明如何写数据完成。本可选方案中,读取基址寄存器的空间的数据个数;当数据个数为零时,发送数据写入完成消息。

56.进一步的,s1022可以包括:步骤1,当pcie数据包为读数据时,控制读地址通道获取pcie数据包;步骤2,将pcie数据包放入到基址寄存器的空间;步骤3,将基址寄存器的空间中的pcie数据包返回至上位机。

57.可见,本可选方案主要是为了说明如何读数据。本可选方案中,当pcie数据包为读数据时,控制读地址通道获取pcie数据包;将pcie数据包放入到基址寄存器的空间;将基址寄存器的空间中的pcie数据包返回至上位机。

58.进一步的,上一可选方案中的步骤1可以包括:步骤1,当pcie数据包为读数据时,配置读数据的初始地址和总长度;步骤2,基于读数据的初始地址和总长度控制读地址通道获取pcie数据包。

59.可见,本可选方案主要是为了说明如何读数据。本可选方案中,当pcie数据包为读数据时,配置读数据的初始地址和总长度;基于读数据的初始地址和总长度控制读地址通道获取pcie数据包。

60.进一步的,本实施例还可以包括:步骤1,读取基址寄存器的空间的数据个数;步骤2,当数据个数为零时,发送数据读取完成消息。

61.可见,本可选方案主要是为了说明如何读数据完成。本可选方案中,读取基址寄存器的空间的数据个数;当数据个数为零时,发送数据读取完成消息。

62.s103,若否,则通过dma方式对pcie数据包进行数据读写。

63.在s101的基础上,本步骤旨在通过dma方式对pcie数据包进行数据读写。也就是,在其他情况下采用dma的方式进行数据传输,避免了对小数据包进行大量的请求。

64.进一步的,本步骤可以包括:通过块dma方式对pcie数据包进行数据读写。

65.可见,本可选方案中,通过块dma方式对pcie数据包进行数据读写。

66.其中,块dma方式的过程是每一次dma请求开始后,只能传输上位机的1个连续的物理内存块,如果要传输下一个内存块,则必须重新初始化内存并配置好dma寄存器,再次启动dma才可以完成。

67.进一步的,本步骤可以包括:通过链式dma方式对pcie数据包进行数据读写。

68.可见,本可选方案中,通过链式dma方式对pcie数据包进行数据读写。

69.其中,链式dma方式通过多个描述符把要传输的离散的物理内存块进行一个一个的描述并形成描述符表,把第1个描述符的地址装载到dma的描述符基址寄存器里面,然后

interconnect模块与axi-mm interconnect模块为axi协议互联模块,用于总线之间的互联,总线根据方向分为master与slave,图中m代表master,s代表slave;axi-lite2mm模块为协议转化模块,将axi-lite接口转化为axi-mm接口,目的是将bar空间寄存器读写数据统一到dma读写数据接口;ddr controller与ram controller为存储控制接口模块,目的是将存储接口转化为标准axi总线接口,方便系统集成。

80.请参考图3,图3为本技术实施例所提供的一种pcie数据传输方法的协议转化模块的结构示意图。

81.其中,axi-lite2mm模块可以参考图3。其中寄存器控制模块接口为axi-lite总线,该总线用于bar空间配置寄存器,该模块定义的寄存器如下: 表1 寄存器定义表其中,写控制模块主要作用是控制写地址通道、写响应通道,以及将wr_fifo中数据放入写数据通道。读控制模块主要作用是控制读地址通道以及将读数据通道内数据放入到rd_fifo中。

82.请参考图4,图4为本技术实施例所提供的另一种pcie数据传输方法的流程图。

83.基于上述模块说明,本实施例中的数据传输过程可以包括:步骤1,判断包长大小是否低于1024b,如果大于1024b,执行dma流程搬移数据,如果小于1024b,执行利用bar空间读写传输数据,即执行步骤2。

84.步骤2,判断读数据或者写数据,如果是上位机向设备写数据,执行步骤3.1至步骤3.4,如果是上位机读设备数据,执行步骤4.1至步骤4.3。

85.步骤3.1,配置向设备写入的存储初始地址,包括高32bit与低32bit,配置要写入的数据总长度。

86.步骤3.2,通过寄存器wr_data将上位机的数据写入到wr_fifo中,每写一次wr_data,对应数据就会写入wr_fifo中。

87.步骤3.3,使能wr_start寄存器,写控制模块会将wr_fifo中的数据放入axi-mm总线,直到将wr_fifo中的数据写入设备对应的存储地址中,此时也会控制写地址通道自动累

加地址以及处理写响应等。

88.步骤3.4,使能wr_start后可通过wr_fifo_num寄存器读取wr_fifo中数据个数,当数据个数为零时说明已经将所有数据放入axi-mm总线,数据写入结束。

89.步骤4.1,配置从设备存储读数据的初始地址,包括高32bit与低32bit,配置要读数据的总长度。

90.步骤4.2,使能wr_start寄存器,读控制模块会控制读地址通道自动累加地址读取axi-mm总线上数据,axi-mm总线将设备对应存储数据通过读数据通道返回,读控制模块将返回数据写入rd_fifo中。

91.步骤4.3,通过读取rd_data寄存器将rd_fifo中数据返回到上位机中,每读一次rd_data寄存器,就会有一个数据从rd_fifo中返回到上位机,读取对应长度数据即结束;此外,可通过rd_fifo_num寄存器验证是否读完。

92.其中,本实施例接口采用标准axi总线,将该设计与dma统一成axi-mm接口,方便系统级别集成、移植与维护。其中的传输方式无需pcie中断,避免大量上报中断导致主机挂死。同时,在数据量低于1024b以下时比单纯dma传输效率更高,经过实验验证,在传输数据低于1024b时,本设计的带宽是dma传输的1.5-20倍,数据量越小,本设计效率越高。

93.并且,少量数据传输过程中dma传输带宽不稳定,采用本设计可以保证少量数据传输过程中的带宽稳定性。

94.本实施例并不抛弃dma传输方式,而是在dma传输方式上做补充,仅在传输数据低于1024b时用本设计中bar空间寄存器读写的方式,克服dma传输方式中少量数据传输中带宽低、带宽不稳定以及中断上报多的问题。

95.可见,本实施例通过先判断待传输的pcie数据包的长度是否小于预设长度,如果小于预设长度则说明该数据包为小数据包,则通过基址寄存器的空间将该pcie数据包进行传输,而不采用dma的方式进行传输,当大于预设长度时,通过dma方式将pcie数据包进行数据读写,实现了对小数据包采用非dma的方式进行数据传输,避免了dma方式存在的问题,提高了数据传输的效率,降低了因多次大量dma请求存在的问题。提高了传输的稳定性。

96.下面对本技术实施例提供的pcie数据传输装置进行介绍,下文描述的pcie数据传输装置与上文描述的pcie数据传输方法可相互对应参照。

97.请参考图5,图5为本技术实施例所提供的一种pcie数据传输装置的结构示意图。

98.本实施例中,该装置可以包括:包长度判断模块100,用于判断待传输的pcie数据包的长度是否小于预设长度;小数据包传输模块200,用于当pcie数据包的长度小于预设长度时,通过基址寄存器的空间和协议转化器将pcie数据包进行数据传输;大数据包传输模块300,用于当pcie数据包的长度大于等于预设长度时,通过dma方式对pcie数据包进行数据读写。

99.可选的,该小数据包传输模块200,可以包括:写数据单元,用于当pcie数据包为写数据时,通过基址寄存器的空间向对应的地址写入pcie数据包;读数据单元,用于当pcie数据包为读数据时,通过基址寄存器的空间从对应的地址读取pcie数据包。

100.可选的,该写数据单元,具体用于当pcie数据包为写数据时,将pcie数据包写入基址寄存器的空间;将基址寄存器的空间中的pcie数据包放入写数据通道,并通过写数据通道将pcie数据包传输至对应的地址。

101.可选的,该当pcie数据包为写数据时,将pcie数据包写入基址寄存器的空间,可以包括:当pcie数据包为写数据时,通过向写地址通道配置对应的地址;将pcie数据包写入基址寄存器的空间。

102.可选的,该写数据单元,还包括:写数据完成单元,用于读取基址寄存器的空间的数据个数;当数据个数为零时,发送数据写入完成消息。

103.可选的,该读数据单元,具体用于当pcie数据包为读数据时,控制读地址通道获取pcie数据包;将pcie数据包放入到基址寄存器的空间;将基址寄存器的空间中的pcie数据包返回至上位机。

104.可选的,该当pcie数据包为读数据时,控制读地址通道获取pcie数据包,包括:当pcie数据包为读数据时,配置读数据的初始地址和总长度;基于读数据的初始地址和总长度控制读地址通道获取pcie数据包。

105.可选的,该读数据单元,还包括:读数据完成单元,用于读取基址寄存器的空间的数据个数;当数据个数为零时,发送数据读取完成消息。

106.可选的,该大数据包传输模块300,具体用于通过块dma方式对pcie数据包进行数据读写。

107.可选的,该大数据包传输模块300,具体用于通过链式dma方式对pcie数据包进行数据读写。

108.可选的,该包长度判断模块100,具体用于判断待传输的pcie数据包的长度是否小于dma传输的最小包长度。

109.本实施例中,还提供另一种pcie数据传输装置,可以包括:传输指令发送模块,用于向下位设备发送数据传输指令,以便下位设备判断数据传输指令对应的待传输的pcie数据包的长度是否小于预设长度;若是,则通过基址寄存器的空间和协议转化器将pcie数据包进行数据传输;若否,则通过dma方式对pcie数据包进行数据读写;返回传输完成消息;传输完成模块,用于接收到传输完成消息。

110.可见,本实施例通过先判断待传输的pcie数据包的长度是否小于预设长度,如果小于预设长度则说明该数据包为小数据包,则通过基址寄存器的空间将该pcie数据包进行传输,而不采用dma的方式进行传输,当大于预设长度时,通过dma方式将pcie数据包进行数据读写,实现了对小数据包采用非dma的方式进行数据传输,避免了dma方式存在的问题,提高了数据传输的效率,降低了因多次大量dma请求存在的问题。提高了传输的稳定性。

111.本技术还提供了一种计算设备,请参考图6,图6本技术实施例所提供的一种计算设备的结构示意图,该计算设备可包括:存储器,用于存储计算机程序;

处理器,用于执行计算机程序时可实现如上述任意一种pcie数据传输方法的步骤。

112.如图6所示,为计算设备的组成结构示意图,计算设备可以包括:处理器10、存储器11、通信接口12和通信总线13。处理器10、存储器11、通信接口12均通过通信总线13完成相互间的通信。

113.在本技术实施例中,处理器10可以为中央处理器(central processing unit,cpu)、特定应用集成电路、数字信号处理器、现场可编程门阵列或者其他可编程逻辑器件等。

114.处理器10可以调用存储器11中存储的程序,具体的,处理器10可以执行异常ip识别方法的实施例中的操作。

115.存储器11中用于存放一个或者一个以上程序,程序可以包括程序代码,程序代码包括计算机操作指令,在本技术实施例中,存储器11中至少存储有用于实现以下功能的程序:判断待传输的pcie数据包的长度是否小于预设长度;若是,则通过基址寄存器的空间和协议转化器将pcie数据包进行数据传输;若否,则通过dma方式对pcie数据包进行数据读写。

116.在一种可能的实现方式中,存储器11可包括存储程序区和存储数据区,其中,存储程序区可存储操作系统,以及至少一个功能所需的应用程序等;存储数据区可存储使用过程中所创建的数据。

117.此外,存储器11可以包括高速随机存取存储器,还可以包括非易失性存储器,例如至少一个磁盘存储器件或其他易失性固态存储器件。

118.通信接口12可以为通信模块的接口,用于与其他设备或者系统连接。

119.当然,需要说明的是,图6所示的结构并不构成对本技术实施例中计算设备的限定,在实际应用中计算设备可以包括比图6所示的更多或更少的部件,或者组合某些部件。

120.本技术还提供了一种计算机可读存储介质,该计算机可读存储介质上存储有计算机程序,计算机程序被处理器执行时可实现如上述任意一种pcie数据传输方法的步骤。

121.该计算机可读存储介质可以包括:u盘、移动硬盘、只读存储器(read-only memory,rom)、随机存取存储器(random access memory,ram)、磁碟或者光盘等各种可以存储程序代码的介质。

122.对于本技术提供的计算机可读存储介质的介绍请参照上述方法实施例,本技术在此不做赘述。

123.说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。对于实施例公开的装置而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

124.专业人员还可以进一步意识到,结合本文中所公开的实施例描述的各示例的单元及算法步骤,能够以电子硬件、计算机软件或者二者的结合来实现,为了清楚地说明硬件和软件的可互换性,在上述说明中已经按照功能一般性地描述了各示例的组成及步骤。这些功能究竟以硬件还是软件方式来执行,取决于技术方案的特定应用和设计约束条件。专业

技术人员可以对每个特定的应用来使用不同方法来实现所描述的功能,但是这种实现不应认为超出本技术的范围。

125.结合本文中所公开的实施例描述的方法或算法的步骤可以直接用硬件、处理器执行的软件模块,或者二者的结合来实施。软件模块可以置于随机存储器(ram)、内存、只读存储器(rom)、电可编程rom、电可擦除可编程rom、寄存器、硬盘、可移动磁盘、cd-rom、或技术领域内所公知的任意其它形式的存储介质中。

126.以上对本技术所提供的一种pcie数据传输方法、另一种pcie数据传输方法、两种pcie数据传输装置、计算设备以及计算机可读存储介质进行了详细介绍。本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想。应当指出,对于本技术领域的普通技术人员来说,在不脱离本技术原理的前提下,还可以对本技术进行若干改进和修饰,这些改进和修饰也落入本技术权利要求的保护范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。