1.本技术涉及显示技术领域,具体涉及一种显示面板。

背景技术:

2.随着多媒体的发展,显示装置变得越来越重要。在现有的显示面板中,为了提升高亮度显示和低亮度显示的均匀性,一般都采用两个复位信号的设计方式;但目前普遍的产品设计中,每个子像素分别采用不同的金属层设置两个复位信号的走线,从而会增加子像素的金属密度,因此会导致子像素更多的点线不良,并使得显示面板的指纹透过率性能降低。

3.有鉴于此,现有技术需要改进。

技术实现要素:

4.本技术提供一种显示面板,以降低子像素的金属密度。

5.本技术提供一种显示面板,其包括:

6.像素驱动电路,所述像素驱动电路呈阵列设置;

7.第一复位信号线,所述第一复位信号线沿行方向延伸;

8.第二复位信号线,所述第二复位信号线沿行方向延伸,所述第一复位信号线与所述第二复位信号线交替间隔设置;

9.多组像素驱动电路行单元,每组所述像素驱动电路行单元包括相邻的第一行像素驱动电路和第二行像素驱动电路;

10.在所述第一行像素驱动电路的区域中设有所述第一复位信号线和所述第二复位信号线中的一者;

11.在所述第二行像素驱动电路的区域中设有所述第一复位信号线和所述第二复位信号线中的另一者。

12.可选的,在本技术一些实施例中,在每组所述像素驱动电路行单元中,所述第一行像素驱动电路和所述第二行像素驱动电路分别与位于所述第一行像素驱动电路的区域中的所述第一复位信号线和所述第二复位信号线中的一者电连接;

13.所述第一行像素驱动电路和所述第二行像素驱动电路分别与位于所述第二行像素驱动电路的区域中的所述第一复位信号线和所述第二复位信号线中的另一者电连接。

14.可选的,在本技术一些实施例中,在每组所述像素驱动电路行单元中,所述第一复位信号线和所述第二复位信号线中的一者在所述显示面板上的正投影与所述第一行像素驱动电路在所述显示面板上的正投影相重叠。

15.可选的,在本技术一些实施例中,在每组所述像素驱动电路行单元中,所述第一复位信号线和所述第二复位信号线中的另一者在所述显示面板上的正投影与所述第二行像素驱动电路在所述显示面板上的正投影相重叠。

16.可选的,在本技术一些实施例中,所述显示面板还包括:

17.第一连接电极,在每组所述像素驱动电路行单元中,所述第一行像素驱动电路通过所述显示面板上的过孔与所述第一复位信号线和所述第二复位信号线中的一者电连接,所述第二行像素驱动电路通过所述第一连接电极与所述第一复位信号线和所述第二复位信号线中的一者电连接;

18.第二连接电极,在每组所述像素驱动电路行单元中,所述第二行像素驱动电路通过所述显示面板上的过孔与所述第一复位信号线和所述第二复位信号线中的另一者电连接,所述第一行像素驱动电路通过所述第二连接电极与所述第一复位信号线和所述第二复位信号线中的另一者电连接。

19.可选的,在本技术一些实施例中,在每列所述像素驱动电路的区域内设有一条所述第一连接电极和一条所述第二连接电极。

20.可选的,在本技术一些实施例中,所述像素驱动电路包括多组所述像素驱动电路列单元,每组所述像素驱动电路列单元包括相邻的两列所述像素驱动电路;

21.在每组所述像素驱动电路列单元的区域内设有两条所述第一连接电极以及一条所述第二连接电极,一条所述第二连接电极在所述显示面板的正投影分别与相邻的两列所述像素驱动电路在所述显示面板的正投影相重叠。

22.可选的,在本技术一些实施例中,两条所述第一连接电极以一条所述第二连接电极为对称轴镜像对称设置。

23.可选的,在本技术一些实施例中,所述显示面板还包括:

24.扫描信号线,所述扫描信号线沿行方向延伸;

25.发光信号驱动线,所述发光信号驱动线沿行方向延伸;

26.所述像素驱动电路分别与所述级扫描信号线以及所述发光信号驱动线电连接;

27.在每组所述像素驱动电路行单元的第一行像素驱动电路的区域中,所述第n-1级扫描信号线、所述第一复位信号线、所述发光信号驱动线和所述第n级扫描信号线沿列方向依次设置;

28.在每组所述像素驱动电路行单元的第二行像素驱动电路的区域中,所述第n-1级扫描信号线、所述第二复位信号线、所述发光信号驱动线和所述第n级扫描信号线沿列方向依次设置。

29.可选的,在本技术一些实施例中,所述像素驱动电路包括多组所述像素驱动电路列单元,每组所述像素驱动电路列单元包括相邻的两列所述像素驱动电路;所述显示面板还包括:

30.电源信号线,在每组所述像素驱动电路列单元中设有一条所述电源信号线,一条所述电源信号线在所述显示面板的正投影分别与相邻的两列所述像素驱动电路在所述显示面板的正投影相重叠。

31.可选的,在本技术一些实施例中,相邻的两列所述像素驱动电路镜像对称设置。

32.可选的,在本技术一些实施例中,所述像素驱动电路包括:

33.发光器件;

34.驱动晶体管,所述驱动晶体管的栅极与第一节点电连接,所述驱动晶体管的源极与第二节点电连接,所述第二节点与电源信号线电连接,所述驱动晶体管的漏极与第三节点电连接,所述发光器件的阳极与所述第三节点电连接;

35.第四晶体管,所述第四晶体管的栅极与第n-1级扫描信号线电连接,所述第四晶体管的源极与第一复位信号线电连接,所述第四晶体管的漏极与所述第一节点电连接;

36.第五晶体管,所述第五晶体管的栅极与所述第n-1级扫描信号线电连接,所述第五晶体管的源极与第二复位信号线电连接,所述第五晶体管的漏极与所述第三节点电连接。

37.可选的,在本技术一些实施例中,所述显示面板包括:

38.半导体层,所述半导体层包括有源部;

39.第一金属层,所述第一金属层包括栅极、扫描信号线以及发光信号驱动线;

40.第二金属层,所述第二金属层包括所述第一复位信号线以及所述第二复位信号线;

41.第三金属层,所述第三金属层包括源极、漏极以及电源信号线;

42.第四金属层,所述第四金属层包括数据信号线。

43.可选的,在本技术一些实施例中,所述第四金属层还包括所述第一连接电极和所述第二连接电极。

44.可选的,在本技术一些实施例中,所述第一连接电极在所述显示面板的正投影与所述驱动晶体管的栅极在所述显示面板的正投影不重叠。

45.可选的,在本技术一些实施例中,在每行像素驱动电路的区域中,所述第一连接电极包括第一直线段、第一斜线段、第二直线段和第二斜线段,所述第一直线段、所述第一斜线段、所述第二直线段和所述第二斜线段依次连接,所述第一直线段和所述第二直线段不同轴,所述第二直线段在所述显示面板的正投影与所述有源层在所述显示面板的正投影完全重叠。

46.可选的,在本技术一些实施例中,在每组像素驱动电路行单元中,所述电源信号线包括位于所述第一行像素驱动电路区域内的第三直线段和位于所述第二行像素驱动电路区域内的第四直线段,所述第三直线段通过第一曲线段与所述第四直线段相连接,所述第二连接电极在所述显示面板的正投影与所述第三直线段、所述第四直线段在所述显示面板的正投影相重叠;

47.所述第二连接电极在所述显示面板的正投影、所述第二复位信号线在所述显示面板的正投影和所述第一曲线段在所述显示面板的正投影不存在共同重叠的部分。

48.本技术提供一种显示面板,其包括像素驱动电路,所述像素驱动电路呈阵列设置;第一复位信号线,所述第一复位信号线沿行方向延伸;第二复位信号线,所述第二复位信号线沿行方向延伸,所述第一复位信号线与所述第二复位信号线交替间隔设置;多组像素驱动电路行单元,每组所述像素驱动电路行单元包括相邻的第一行像素驱动电路和第二行像素驱动电路;在所述第一行像素驱动电路的区域中设有所述第一复位信号线和所述第二复位信号线中的一者;在所述第二行像素驱动电路的区域中设有所述第一复位信号线和所述第二复位信号线中的另一者。本技术通过相邻的第一行像素驱动电路和第二行像素驱动电路共用一条所述第一复位信号线和所述第二复位信号线,从而降低子像素的金属密度,因此可以提高显示面板的指纹透过率性能,有利于实现高像素密度面板设计。

附图说明

49.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使

用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

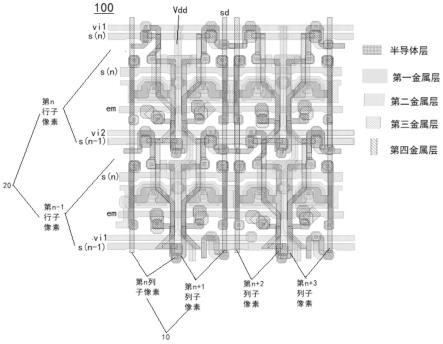

50.图1是本技术提供的显示面板的平面示意图;

51.图2是本技术提供的显示面板的像素驱动电路的示意图;

52.图3是本技术提供的显示面板的半导体层的平面示意图;

53.图4是本技术提供的显示面板的第一金属层的平面示意图;

54.图5是本技术提供的显示面板的第二金属层的平面示意图;

55.图6是本技术提供的显示面板的第三金属层的平面示意图;

56.图7是本技术提供的显示面板的第四金属层的平面示意图。

具体实施方式

57.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

58.在本技术的描述中,需要理解的是,术语“第一”和“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”和“第二”等的特征可以明示或者隐含地包括一个或者更多个特征,因此不能理解为对本技术的限制。

59.本技术所有实施例中采用的晶体管可以为薄膜晶体管或场效应管或其他特性相同的器件,由于这里采用的晶体管的源极、漏极是对称的,所以其源极、漏极是可以互换的。在本技术实施例中,为区分晶体管除栅极之外的两极,将其中一极称为源极,另一极称为漏极。按附图中的形态规定开关晶体管的中间端为栅极、信号输入端为源极、输出端为漏极。此外本技术实施例所采用的晶体管可以包括p型晶体管和/或n型晶体管两种,其中,p型晶体管在栅极为低电平时导通,在栅极为高电平时截止,n型晶体管为在栅极为高电平时导通,在栅极为低电平时截止。按附图中的形态规定晶体管的中间端为栅极、信号输入端为源极、输出端为漏极。

60.本技术提供一种显示面板,以下进行详细说明。需要说明的是,以下实施例的描述顺序不作为对本技术实施例优选顺序的限定。

61.需要说明的是,由于本技术采用的晶体管的源极、漏极是对称的,所以其源极、漏极是可以互换的。

62.请参阅图1,图1是本技术提供的显示面板100的平面示意图,图2是本技术提供的显示面板100的像素驱动电路的示意图。本技术提供一种显示面板100,其包括像素驱动电路101,所述像素驱动电路101呈阵列设置,其中相邻的两列所述像素驱动电路101镜像对称设置。

63.本技术通过将相邻的两列所述驱动电路镜像对称设置,从而降低子像素的金属密度,因此可以提高显示面板100的指纹透过率性能,有利于实现高像素密度面板设计。

64.请参考图1至图7,图3是本技术提供的显示面板100的半导体层的平面示意图,图4

是本技术提供的显示面板100的第一金属层的平面示意图,图5是本技术提供的显示面板100的第二金属层的平面示意图,图6是本技术提供的显示面板100的第三金属层的平面示意图,图7是本技术提供的显示面板100的第四金属层的平面示意图。

65.在一些实施例中,所述显示面板100还包括:

66.第一复位信号线vi1,所述第一复位信号线vi1沿行方向延伸,所述第一复位信号线vi1与所述像素驱动电路101电连接;

67.第二复位信号线vi2,所述第二复位信号线vi2沿行方向延伸,所述第二复位信号线vi2与所述像素驱动电路101电连接。

68.也即是本技术的所述像素驱动电路101设有两条复位信号线。

69.进一步地,在一些实施例中,所述显示面板100还包括:多组所述像素驱动电路101行单元20,每组所述像素驱动电路101行单元20包括相邻的第一行像素驱动电路101和第二行像素驱动电路101;

70.在所述第一行像素驱动电路的区域中设有所述第一复位信号线vi1和所述第二复位信号线vi2中的一者;

71.在所述第二行像素驱动电路的区域中设有所述第一复位信号线vi1和所述第二复位信号线vi2中的另一者。

72.也即是,本技术在每两行所述像素驱动电路101上只设有一条所述第一复位信号线vi1,有利于降低第一复位信号线vi1的数量,从而可以降低显示面板100的金属密度;本技术在每两行所述像素驱动电路101上只设有一条所述第二复位信号线vi2,有利于降低第二复位信号线vi2的数量,从而可以降低显示面板100的金属密度。因此可以提高显示面板的指纹透过率性能,有利于实现高像素密度面板设计。

73.具体地,在一些实施例中,在每组所述像素驱动电路行单元20的第一行像素驱动电路的区域中设有一条所述第一复位信号线vi1或第二复位信号线vi2;

74.在每组所述像素驱动电路行单元20的第二行像素驱动电路的区域中设有一条所述第二复位信号线vi2或第一复位信号线vi1。

75.在一些实施例中,在每组所述像素驱动电路行单元20中,所述第一复位信号线vi1和所述第二复位信号线vi2中的一者在所述显示面板100上的正投影与每组所述像素驱动电路101行单元中的第一行像素驱动电路101在所述显示面板100上的正投影相重叠,所述第一复位信号线vi1和所述第二复位信号线vi2中的另一者在所述显示面板100上的正投影与每组所述像素驱动电路101行单元中的第二行像素驱动电路101在所述显示面板100上的正投影相重叠。所述第一复位信号线vi1和所述第二复位信号线vi2分别与像素驱动电路101重叠设置,有利于降低显示面板的金属密度。

76.进一步地,所述显示面板100还包括:

77.第一连接电极30,在每组所述像素驱动电路行单元20中,所述第一行像素驱动电路101通过所述显示面板上的过孔与所述第一复位信号线vi1和所述第二复位信号线vi2中的一者电连接,所述第二行像素驱动电路101通过所述第一连接电极30与所述第一复位信号线vi1和所述第二复位信号线vi2中的另一者电连接;

78.第二连接电极40,在每组所述像素驱动电路行单元20中,所述第二行像素驱动电路101通过所述显示面板上的过孔与所述第一复位信号线vi1和所述第二复位信号线vi2中

的另一者电连接,所述第一行像素驱动电路通过所述第二连接电极40与所述第一复位信号线vi1和所述第二复位信号线vi2中的另一者电连接。

79.具体地,在一些实施例中,所述第一复位信号线vi1设在每组所述像素驱动电路101行单元中的第一行像素驱动电路101的区域范围内,而且每组所述像素驱动电路101行单元中的第二行像素驱动电路101通过所述第一连接电极30与所述第一复位信号线vi1电连接。所述第二复位信号线vi2设在每组所述像素驱动电路101行单元中的第二行像素驱动电路101的区域范围内,而且每组所述像素驱动电路101行单元中的第一行像素驱动电路101通过所述第二连接电极40与所述第二复位信号线vi2电连接。

80.进一步地,在一些实施例中,在每列所述像素驱动电路的区域内设有一条所述第一连接电极30和一条所述第二连接电极40。

81.也即是,在每列所述像素驱动电路区域内的第二行像素驱动电路101都通过所述第一连接电极30与所述第一复位信号线vi1电连接,在每列所述像素驱动电路区域内的第一行像素驱动电路101都通过所述第二连接电极40与所述第二复位信号线vi2电连接。

82.进一步地,在一些实施例中,所述像素驱动电路101包括多组所述像素驱动电路101列单元10,每组所述像素驱动电路101列单元10包括相邻的两列所述像素驱动电路101;

83.在每组所述像素驱动电路101列单元10的区域内设有两条所述第一连接电极30以及一条所述第二连接电极40,一条所述第二连接电极40在所述显示面板的正投影分别与相邻的两列所述像素驱动电路101在所述显示面板的正投影相重叠。

84.也即是,在每组所述像素驱动电路101列单元10中,相邻的两列所述像素驱动电路101与同一条所述第二连接电极40电连接,可以减少第二连接电极40的设置,有利于降低显示面板的像素密度。而且一条所述第二连接电极40在所述显示面板的正投影分别与相邻的两列所述像素驱动电路101在所述显示面板的正投影相重叠,相邻的两列所述像素驱动电路101可以直接通过显示面板上的过孔与同一条所述第二连接电极40连接。具体地,在2

×

2矩阵的所述像素驱动电路101包括一组所述像素驱动电路101列单元10,则位于所述像素驱动电路101列单元10的所述第二行像素驱动电路101上的两个像素驱动电路101分别通过两条所述第一连接电极30与所述第一复位信号线vi1电连接。而位于所述像素驱动电路101列单元10的所述第一行像素驱动电路101上的两个像素驱动电路101分别通过一条所述第二连接电极40与所述第二复位信号线vi2电连接。

85.在一些实施例中,在每组所述像素驱动电路101列单元10的区域内的所述第一连接电极30可以镜像对称设置,也可以采用不对称设置的结构。当在每组所述像素驱动电路101列单元10中,两条所述第一连接电极30以一条所述第二连接电极40为对称轴镜像对称设置,一条所述第二连接电极40位于相邻的两列所述像素驱动电路的中间位置。所述第一连接电极30和所述第二连接电极40镜像对称设置有利于节省空间,从而降低显示面板100的金属密度。

86.在一些实施例中,所述显示面板100还包括:

87.扫描信号线;

88.发光信号驱动线em;

89.所述像素驱动电路101分别与所述级扫描信号线以及所述发光信号驱动线em电连接;

90.在每组所述像素驱动电路行单元20的第一行像素驱动电路的区域中,所述第n-1级扫描信号线s(n-1)、所述第一复位信号线vi1、所述发光信号驱动线em和所述第n级扫描信号线s(n)沿列方向依次设置;

91.在每组所述像素驱动电路行单元20的第二行像素驱动电路的区域中,所述第n-1级扫描信号线s(n-1)、所述第二复位信号线vi2、所述发光信号驱动线em和所述第n级扫描信号线s(n)沿列方向依次设置。

92.也即是,本技术在相邻两行所述像素驱动电路101中,在其中一行所述像素驱动电路101的区域中,所述第n-1级扫描信号线s(n-1)、所述第一复位信号线vi1、所述发光信号驱动线em和所述第n级扫描信号线s(n)沿列方向依次设置,而在另一行所述像素驱动电路101的区域中,所述第n-1级扫描信号线s(n-1)、所述第二复位信号线vi2、所述发光信号驱动线em和所述第n级扫描信号线s(n)沿列方向依次设置,因此在相邻两行所述像素驱动电路101的区域中沿行方向的线对称设置,因此可以使得相邻两行所述像素驱动电路101受到信号的影响相等,有利于提高显示面板100的显示均匀性。

93.在一些实施例中,所述像素驱动电路101包括多组所述像素驱动电路101列单元10,每组所述像素驱动电路101列单元10包括相邻的两列所述像素驱动电路101;所述显示面板100还包括:

94.电源信号线vdd,在每组所述像素驱动电路列单元10中设有一条所述电源信号线vdd,一条所述电源信号线vdd在所述显示面板的正投影分别与相邻的两列所述像素驱动电路101在所述显示面板的正投影相重叠。

95.另外,所述电源信号线vdd沿列方向延伸。本技术将每组所述像素驱动电路101列单元10的两列所述像素驱动电路101分别与同一条所述电源信号线vdd电连接,有利于降低电源信号线vdd的数量,从而可以降低显示面板100的金属密度。

96.请参考图2,在一些实施例中,所述像素驱动电路101包括:

97.发光器件d;

98.驱动晶体管t1,所述驱动晶体管t1的栅极与第一节点1电连接,所述驱动晶体管t1的源极与第二节点2电连接,所述第二节点与电源信号线vdd电连接,所述驱动晶体管t1的漏极与第三节点3电连接,所述发光器件d的阳极与所述第三节点3电连接;

99.第四晶体管t4,所述第四晶体管t4的栅极与第n-1级扫描信号线s(n-1)电连接,所述第四晶体管t4的源极与第一复位信号线vi1电连接,所述第四晶体管t4的漏极与所述第一节点1电连接;其中,所述第四晶体管t4可以为双栅极晶体管,也可以为单栅极晶体管,而在本实施例中,所述第四晶体管t4为双栅极晶体管;

100.第五晶体管t5,所述第五晶体管t5的栅极与所述第n-1级扫描信号线s(n-1)电连接,所述第五晶体管t5的源极与第二复位信号线vi2电连接,所述第五晶体管t5的漏极与所述第三节点3电连接。

101.进一步地,所述像素驱动电路101还包括:

102.存储电容c,所述存储电容c的一端与所述第一节点1电连接,所述存储电容c的另一端与所述电源信号线vdd电连接;

103.第二晶体管t2,所述第二晶体管t2的栅极与第n级扫描信号线s(n)电连接,所述第二晶体管t2的源极与数据信号线sd电连接,所述第二晶体管t2的漏极与所述第一节点1电

连接;

104.第三晶体管t3,所述第三晶体管t3的栅极与发光信号驱动线em电连接,所述第三晶体管t3的源极与电源信号线vdd,所述第三晶体管t3的漏极与所述第二节点2电连接;

105.进一步地,在一些实施例中,所述像素驱动电路101还包括:

106.第六晶体管t6,所述第六晶体管t6的栅极与所述第n级扫描信号线s(n)电连接,所述第六晶体管t6的源极与所述第一节点1电连接,所述第六晶体管t6的漏极与所述驱动晶体管t1的漏极电连接。其中,所述第六晶体管t6可以为双栅极晶体管,也可以为单栅极晶体管,而在本实施例中,所述第六晶体管t6为双栅极晶体管。

107.进一步地,在一些实施例中,所述像素驱动电路101还包括:

108.第七晶体管t7,所述第七晶体管t7的栅极与所述发光信号驱动线em电连接,所述第七晶体管t7的源极与所述驱动晶体管t1的漏极电连接,所述第七晶体管t7的漏极与所述第三节点3电连接。

109.请参考图1至图7,在一些实施例中,所述显示面板100包括:

110.半导体层50,所述半导体层50包括有源部51;

111.第一金属层60,所述第一金属层60包括栅极、扫描信号线、发光信号驱动线em以及所述存储电容c的第一极板c1;其中,所述驱动晶体管t1的栅极与所述存储电容c的第一极板c1的相重叠;

112.第二金属层70,所述第二金属层70包括所述第一复位信号线vi1、所述第二复位信号线vi2以及所述存储电容c的第二极板c2;

113.第三金属层80,所述第三金属层80包括源极81、漏极82以及电源信号线vdd;

114.第四金属层90,所述第四金属层90包括第一连接电极30、第二连接电极40及数据信号线sd。进一步地,所述半导体层50和所述第一金属层60之间设有第一绝缘层,所述第一金属层60和所述第二金属层70之间设有第二绝缘层,所述第二金属层70和所述第三金属层80之间设有第三绝缘层,所述第三金属层80和所述第四金属层90之间设有第四绝缘层,所述第一连接电极30通过所述第四绝缘层上的开孔与所述第四晶体管t4的源极电连接,所述第二连接电极40通过所述第四绝缘层上的开孔与与所述第五晶体管t5的源极电连接。

115.进一步地,请参考图1和图7,所述第一连接电极30在所述显示面板的正投影与所述驱动晶体管t1的栅极在所述显示面板的正投影不重叠。由于所述驱动晶体管t1的栅极处的电压比较敏感,为了减少走线对所述驱动晶体管t1的栅极处的电压的影响,本技术将所述第一连接电极30在所述显示面板的正投影与所述驱动晶体管的栅极在所述显示面板的正投影设置为不重叠,以避免电压信号的串扰。

116.具体地,在每行像素驱动电路的区域中,所述第一连接电极30包括第一直线段31、第一斜线段32、第二直线段33和第二斜线段34,所述第一直线段31、所述第一斜线段32、所述第二直线段33和所述第二斜线段34依次连接,所述第一直线段31和所述第二直线段33不同轴,所述第二直线段33在所述显示面板的正投影与所述有源层在所述显示面板的正投影完全重叠。所述第一连接电极30采用多条线段的相连接的方式,以达到所述第一连接电极30在所述显示面板的正投影与所述驱动晶体管t1的栅极在所述显示面板的正投影不重叠,同时所述第二直线段33在所述显示面板的正投影与所述有源层在所述显示面板的正投影完全重叠,可以对有源层起到屏蔽的作用,以减少其他信号对有源层的影响。

117.请参考图1和图6,在一些实施例中,在每组像素驱动电路行单元20中,所述电源信号线vdd包括位于所述第一行像素驱动电路区域内的第三直线段l1和位于所述第二行像素驱动电路区域内的第四直线段l2,所述第三直线段l1通过第一曲线段l3与所述第四直线段l2相连接,所述第二连接电极40在所述显示面板的正投影与所述第三直线段l1、所述第四直线段l2在所述显示面板的正投影相重叠;

118.所述第二连接电极40在所述显示面板的正投影、所述第二复位信号线vi2在所述显示面板的正投影和所述第一曲线段l3在所述显示面板的正投影不存在共同重叠的部分。本技术通过将所述第二连接电极在所述显示面板的正投影与所述第三直线段、所述第四直线段在所述显示面板的正投影相重叠,从而可以节省空间,有利于提高像素开口率,另外,所述第二连接电极在所述显示面板的正投影、所述第二复位信号线在所述显示面板的正投影和所述第一曲线段在所述显示面板的正投影不存在共同重叠的部分,因此所述第二连接电极可以在所述第一曲线段覆盖的区域通过显示面板上的过孔直接与所述第二复位信号线连接,有利于减少走线设置。

119.以上对本技术实施例所提供的一种显示面板100进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想;同时,对于本领域的技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处,综上,本说明书内容不应理解为对本技术的限制。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。