技术特征:

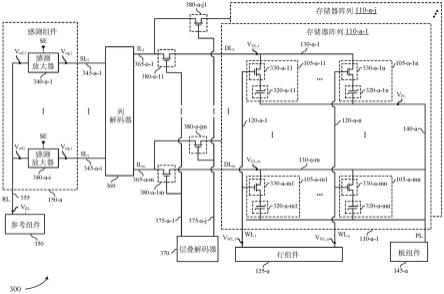

1.一种设备,其包括:感测组件,其可操作用于感测存储器裸片的存储器单元;所述存储器裸片的第一列解码器,其可操作以与所述感测组件耦合;所述存储器裸片的第二列解码器,其可操作以与所述感测组件耦合;第一存储器阵列,其与所述存储器裸片的衬底上面的第一层级相关联,所述第一存储器阵列包括所述存储器单元的第一子组及第一多个数字线,每一第一数字线可操作以经由所述第一层级的相应第一晶体管与所第一列解码器耦合;第二存储器阵列,其与所述存储器裸片的所述衬底上面的第二层级相关联,所述第二存储器阵列包括所述存储器单元的第二子组及第二多个数字线,每一数字线可操作以经由所述第二层级的相应第二晶体管与所述第一列解码器耦合;第三存储器阵列,其与所述第一层级相关联,所述第三存储器阵列包括所述存储器单元的第三子组及第三多个数字线,每一数字线可操作以经由所述第一层级的相应第三晶体管与所述第二列解码器耦合;及第四存储器阵列,其与所述第二层级相关联,所述第四存储器阵列包括所述存储器单元的第四子组及第四多个数字线,每一第四数字线可操作以经由所述第二层级的相应第四晶体管与所述第二列解码器耦合。2.根据权利要求1所述的设备,其进一步包括:多个第一导体,每一第一导体与所述第一层级的所述第一晶体管中的一个、所述第二层级的所述第二晶体管中的一个及所述第一列解码器耦合;及多个第二导体,每一第二导体与所述第一层级的所述第三晶体管中的一个、所述第二层级的所述第四晶体管中的一个及所述第二列解码器耦合。3.根据权利要求1所述的设备,其中:所述第一晶体管中的每一个包括所述第一层级的相应沟道部分;所述第二晶体管中的每一个包括所述第二层级的相应沟道部分;所述第三晶体管中的每一个包括所述第一层级的相应沟道部分;且所述第四晶体管中的每一个包括所述第二层级的相应沟道部分。4.根据权利要求3所述的设备,其进一步包括:所述第一层级的一或多个第一栅极导体,每一第一栅极导体可操作以调制所述第一晶体管中的每一个的所述沟道部分的导电性;所述第二层级的一或多个第二栅极导体,每一第二栅极导体可操作以调制所述第二晶体管中的每一个的所述沟道部分的导电性;所述第一层级的一或多个第三栅极导体,每一第三栅极导体可操作以调制所述第三晶体管中的每一个的所述沟道部分的导电性;且所述第二层级的一或多个第四栅极导体,每一第四栅极导体可操作以调制所述第四晶体管中的每一个的所述沟道部分的导电性。5.根据权利要求3所述的设备,其中:所述第一晶体管中每一个的所述沟道部分包括与所述第一多个数字线中的所述相应数字线接触的相应一组一或多个第一半导体立柱;所述第二晶体管中每一个的所述沟道部分包括与所述第二多个数字线中的所述相应

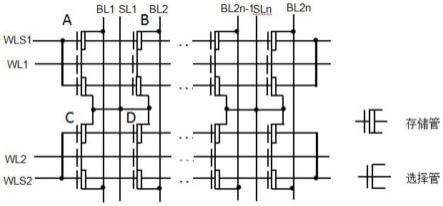

数字线接触的相应一组一或多个第二半导体立柱;所述第三晶体管中每一个的所述沟道部分包括与所述第三多个数字线中的所述相应数字线接触的相应一组一或多个第三半导体立柱;且所述第四晶体管中每一个的所述沟道部分包括与所述第四多个数字线中的所述相应数字线接触的相应一组一或多个第四半导体立柱。6.根据权利要求5所述的设备,其中:所述存储器单元的所述第一子组的每一存储器单元与相应第五晶体管相关联,所述第五晶体管可操作以将所述存储器单元与所述第一多个数字线中的数字线耦合,所述第五晶体管中的每一个包括相应沟道部分,所述沟道部分包括相应一组一或多个第五半导体立柱;所述存储器单元的所述第二子组的每一存储器单元与相应第六晶体管相关联,所述第六晶体管可操作以将所述存储器单元与所述第二多个数字线中的数字线耦合,所述第六晶体管中的每一个包括相应沟道部分,所述沟道部分包括相应一组一或多个第六半导体立柱;所述存储器单元的所述第三子组的每一存储器单元与相应第七晶体管相关联,所述第七晶体管可操作以将所述存储器单元与所述第三多个数字线中的数字线耦合,所述第七晶体管中的每一个包括相应沟道部分,所述沟道部分包括相应一组一或多个第七半导体立柱;且所述存储器单元的所述第四子组的每一存储器单元与相应第八晶体管相关联,所述第八晶体管可操作以将所述存储器单元与所述第四多个数字线中的数字线耦合,所述第八晶体管中的每一个包括相应沟道部分,所述沟道部分包括相应一组一或多个第八半导体立柱。7.根据权利要求6所述的设备,其中:所述第一半导体立柱、所述第三半导体立柱、所述第五半导体立柱及所述第七半导体立柱沿着相对于所述衬底的高度维度重叠,且所述第二半导体立柱、所述第四半导体立柱、所述第六半导体立柱及所述第八半导体立柱沿着相对于所述衬底的所述高度维度重叠。8.根据权利要求1所述的设备,其进一步包括:所述第一层级的多个第五晶体管,每一第五晶体管可操作以将所述存储器单元的所述第一子组的相应存储器单元与所述第一多个数字线中的数字线耦合;所述第二层级的多个第六晶体管,每一第六晶体管可操作以将所述存储器单元的所述第二子组的相应存储器单元与所述第二多个数字线中的数字线耦合;所述第一层级的多个第七晶体管,每一第七晶体管可操作以将所述存储器单元的所述第三子组的相应存储器单元与所述第三多个数字线中的数字线耦合;及所述第二层级的多个第八晶体管,每一第八晶体管可操作以将所述存储器单元的所述第四子组的相应存储器单元与所述第四多个数字线中的数字线耦合。9.根据权利要求8所述的设备,其进一步包括:多个字线导体,每一字线导体可操作以激活所述多个第五晶体管的相应行、激活所述多个第六晶体管的相应行、激活所述多个第七晶体管的相应行以及激活所述多个第八晶体

管的相应行。10.根据权利要求8所述的设备,其进一步包括:多个第一字线导体,每一第一字线导体可操作以激活所述多个第一晶体管的相应行及激活所述多个第六晶体管的相应行;及多个第二字线导体,每一第二字线导体可操作以激活所述多个第七晶体管的相应行及激活所述多个第八晶体管的相应行。11.根据权利要求1所述的设备,其中所述第一列解码器及所述第二列解码器各自包括相应多个晶体管,所述相应多个晶体管中的每一晶体管包括至少部分地由所述衬底的经掺杂部分形成的相应沟道部分。12.根据权利要求1所述的设备,其中:所述存储器单元的所述第一子组位于所述存储器单元的所述第二子组与所述衬底之间;且所述存储器单元的所述第三子组位于所述存储器单元的所述第四子组与所述衬底之间。13.根据权利要求1所述的设备,其进一步包括:一或多个开关组件,所述开关组件可操作以将所述第一列解码器或所述第二列解码器中的一个与所述感测组件耦合及将所述第一列解码器或所述第二列解码器中的另一个与所述感测组件隔离。14.一种方法,其包括:形成感测组件,所述感测组件可操作用于感测存储器裸片的存储器单元;形成所述存储器裸片的第一列解码器,所述第一列解码器可操作以与所述感测组件耦合;形成所述存储器裸片的第二列解码器,所述第二列解码器可操作以与所述感测组件耦合;形成第一存储器阵列,所述第一存储器阵列与所述存储器裸片的衬底上面的第一层级相关联,所述第一存储器阵列包括所述存储器单元的第一子组及第一多个数字线,每一数字线可操作以经由所述第一层级的相应第一晶体管与所第一列解码器耦合;形成第二存储器阵列,所述第二存储器阵列与所述存储器裸片的所述衬底上面的第二层级相关联,所述第二存储器阵列包括所述存储器单元的第二子组及第二多个数字线,每一数字线可操作以经由所述第二层级的相应第二晶体管与所述第一列解码器耦合;形成第三存储器阵列,所述第三存储器阵列与所述第一层级相关联,所述第三存储器阵列包括所述存储器单元的第三子组及第三多个数字线,每一数字线可操作以经由所述第一层级的相应第三晶体管与所述第二列解码器耦合;及形成第四存储器阵列,所述第四存储器阵列与所述第二层级相关联,所述第四存储器阵列包括所述存储器单元的第四子组及第四多个数字线,每一数字线可操作以经由所述第二层级的相应第四晶体管与所述第二列解码器耦合。15.根据权利要求14所述的方法,其进一步包括:形成多个第一导体,每一第一导体与所述第一层级的所述第一晶体管中的一个、所述第二层级的所述第二晶体管中的一个及所述第一列解码器耦合;及

形成多个第二导体,每一第二导体与所述第一层级的所述第三晶体管中的一个、所述第二层级的所述第四晶体管中的一个及所述第二列解码器耦合。16.根据权利要求14所述的方法,其进一步包括:至少部分地基于将多晶半导体沉积在所述第一层级中的所述衬底上方而形成所述第一晶体管中的每一个的沟道部分;至少部分地基于将所述多晶半导体沉积在所述第二层级中的所述衬底上方而形成所述第二晶体管中的每一个的沟道部分;至少部分地基于将多晶半导体沉积在所述第一层级中的所述衬底上方而形成所述第三晶体管中的每一个的沟道部分;及至少部分地基于将所述多晶半导体沉积在所述第二层级中的所述衬底上方而形成所述第四晶体管中的每一个的沟道部分。17.一种方法,其包括:识别存储器裸片的第一存储器阵列的存储器单元行以用于存取操作,所述存储器裸片包括:位于所述存储器裸片的衬底上面的第一层级中的所述第一存储器阵列,位于所述衬底上面的第二层级中的所述存储器裸片的第二存储器阵列,位于所述第一层级中的所述存储器裸片的第三存储器阵列,及位于所述第二层级中的所述存储器裸片的第四存储器阵列;及至少部分地基于所述识别而将所述存储器单元行与所述存储器裸片的感测组件耦合,其中将所述存储器单元行与所述感测组件耦合包括:至少部分地基于激活所述第一层级的多个第一晶体管而将所述存储器单元行与所述第一层级的多个数字线耦合;至少部分地基于激活所述第一层级的多个第二晶体管,将所述多个数字线与列解码器耦合;及将所述列解码器与所述感测组件耦合。18.根据权利要求17所述的方法,其进一步包括:至少部分地基于所述识别而将所述第二存储器阵列的第二存储器单元行与所述列解码器隔离,其中所述将所述第二存储器单元行与所述列解码器隔离包括:至少部分地基于激活所述第二层级的多个第三晶体管而将所述第二存储器单元行与所述第二层级的第二多个数字线耦合;及至少部分地基于去激活所述第二层级的多个第四晶体管而将所述第二多个数字线与所述列解码器隔离。19.根据权利要求17所述的方法,其进一步包括:至少部分地基于所述识别而将所述第三存储器阵列的第三存储器单元行与所述感测组件隔离,其中所述将所述第三存储器单元行与所述感测组件隔离包括:至少部分地基于激活所述第一层级的多个第五晶体管而将所述第三存储器单元行与所述第一层级的第三多个数字线耦合;至少部分地基于去激活所述第二层级的多个第六晶体管,将所述第三多个数字线与第二列解码器耦合;及将所述第二列解码器与所述感测组件隔离。

20.根据权利要求17所述的方法,其进一步包括:至少部分地基于所述识别而将所述第四存储器阵列的第四存储器单元行与所述感测组件隔离,其中所述将所述第四存储器单元行与所述感测组件隔离包括:至少部分地基于激活所述第二层级的多个第七晶体管而将所述第四存储器单元行与所述第二层级的第四多个数字线耦合;至少部分地基于去激活所述第二层级的多个第八晶体管而将所述第四多个数字线与第二列解码器隔离;及将所述第二列解码器与所述感测组件隔离。

技术总结

本申请案是针对存储器装置中的薄膜晶体管层叠选择。存储器装置可包含布置在形成于衬底上方的层叠堆叠中的存储器阵列,及分布在所述层之间以利用共用的基于衬底的电路系统的层叠选择组件。例如,所述堆叠的每一存储器阵列可包含对应层叠的一组数字线,及可操作以将所述组数字线与在多个层叠之间共享的列解码器耦合的层叠选择电路系统。为了存取一个层叠上的所选择存储器阵列的存储器单元,可各自激活对应于所述存储器阵列的所述层叠选择电路系统,而可去激活对应于另一层叠上的非所选择存储器阵列的所述层叠选择电路系统。所述层叠选择电路系统,例如晶体管,可利用薄膜制造技术,例如用于形成垂直晶体管的各种技术。例如用于形成垂直晶体管的各种技术。例如用于形成垂直晶体管的各种技术。

技术研发人员:D

受保护的技术使用者:美光科技公司

技术研发日:2022.05.12

技术公布日:2022/11/22

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。