针对处理器板级调试的开发系统

1.本专利是从在先申请的申请号为201811526758.3,申请日为2018.12.13的专利中分出来的子专利,要求享有相应优先权。

技术领域

2.本发明涉及处理器设计技术领域,尤其涉及一种针对处理器板级调试的开发系统。

背景技术:

3.随着芯片制造工艺的不断升级和市场需求不断的提高,芯片的设计复杂度越来越大,工作频率越来越高。芯片在流片后,不可避免的都会出现一些功能性的问题。仅从测试的结果分析可能出现的硬件问题,是几乎不可能做到的事情。尤其是对于处理器来说,更是这样。虽然处理器架构会定义一些debug的功能,但是这些功能起作用的前提是处理器没有硬件问题,它们所要debug的对象是软件而非硬件。如果硬件自身出了问题,这些功能就没有用处了。

4.目前,arm公司在其最新的处理器上提出了ela(embedded logic analyzer,嵌入式逻辑分析仪)的方法,其能够通过触发事件将处理器内部的信号存储在sram(staticrandom access memory,静态随机存取存储器)中。这个方案有两方面缺点:一是ela的面积较大,而且对处理器的时序收敛及后端布局布线都会造成一定的障碍;二是需要精确知道触发条件,这个在实际的silicon debug(板级调试)中是不容易做到的事情。因此实际项目中有效利用率并不高。

技术实现要素:

5.本发明提供的针对处理器板级调试的开发系统及方法,能够高效地定位处理器内的硬件问题,且面积极小,易于实现。

6.第一方面,本发明提供一种针对处理器板级调试的开发系统,所述系统包括调试器工具和调试接入端口dap,其中,

7.所述dap,与所述调试器工具连接,且通过高级外设总线apb访问处理器中与调试相关的寄存器;

8.所述调试器工具,用于通过所述dap直接将处理器内部的状态读出到上位机;

9.所述处理器包括多个处理器核和一个二级缓存控制l2c模块,每个处理器核包括取指单元ifu模块、数据处理单元dpu模块、读写处理单元lsu模块和内存管理单元mmu模块,可利用的域分别分布到处理器核的模块内以及l2c模块内。

10.可选地,所述dpu模块,用于管理处理器核内指令的执行过程;

11.所述ifu模块,用于管理处理器核内指令的取指操作,将dbg相关的寄存器和pmu寄存器中部分的自定义域分布其中,收集ifu内对板级调试的重要信号,生成ifu auxiliarydebug registers;

12.所述lsu模块,用于管理处理器核内load/store指令的执行过程,将dbg相关的寄存器和pmu寄存器中部分的自定义域分布其中,收集lsu内对板级调试的重要信号,生成lsuauxiliary debug registers;

13.所述mmu模块,用于管理处理器核内页表转换过程,将dbg相关的寄存器和pmu寄存器中部分的自定义域分布其中,收集mmu内对板级调试的重要信号,生成mmu auxiliarydebug registers。

14.可选地,所述l2c模块包括cti模块和l2c auxiliary debug registers模块,其中,

15.所述cti模块,用于产生触发事件,包含armv8-a架构已定义的cti oldregisters,但包含自定义域;

16.所述l2c auxiliary debug registers模块,用于利用cti的自定义域,收集l2c内对板级调试的重要信号。

17.可选地,所述dpu模块包括dbg old registers模块、pmu old registers模块和auxiliary debug registers模块,其中,

18.所述dbg old registers模块,是armv8-a架构已定义的dbg相关的寄存器,不包含自定义域;

19.所述pmu old registers模块,是armv8-a架构已定义的pmu相关的寄存器,不包含自定义域;

20.所述auxiliary debug registers模块,利用dbg寄存器和pmu寄存器中部分的自定义域,收集dpu模块内对板级调试的重要信号。

21.第二方面,本发明提供一种针对处理器板级调试的开发方法,包括:

22.配置调试器工具,通过地址选择处理器内相关的寄存器;

23.调试器工具将指令传递给调试接入端口后,通过调试接入端口选择处理器内相应的32-bit寄存器;

24.将处理器内2-bit寄存器的结果通过调试接入端口返回给调试器工具。

25.第三方面,本发明提供一种针对处理器板级调试的开发系统,处理器的处理器核包括jtag控制模块以及ifu、dpu、lsu和mmu组成模块,其中,

26.所述jtag控制模块包括测试访问端口tap和jtag链,通过jtag链,将处理器核内重要的信号读出来;

27.所述jtag控制模块,基于标准的jtag协议,内部实现了状态机、dr寄存器及ir寄存器,dr寄存器用于保存所要导出的信号,ir寄存器用于选择导出哪些信号;

28.所述ifu、dpu、lsu和mmu组成模块,分别将其内部重要信号分成以32-bit宽为单位的多组,通过复用器输出给jtag链;

29.处理器核内的jtag接口与处理器核外的soc上的jtag相连,最终将调试信号导出到芯片外。

30.第四方面,本发明提供一种针对处理器板级调试的开发系统,处理器的处理器核包括总线接口单元和多个系统寄存器,其中,

31.所述总线接口单元,用于与外界进行交互,在其与外界接口上有读地址、读请求类型、写地址和写请求类型信号;

32.第一自定义系统寄存器,设定读地址区间的最低地址;

33.第二自定义系统寄存器,设定读地址区间的最高地址;

34.第三自定义系统寄存器,当读地址在所述第一自定义系统寄存器和所述第二自定义系统寄存器区间时,抓取读请求的类型;

35.第四自定义系统寄存器,设定写地址区间的最低地址;

36.第五自定义系统寄存器,设定写地址区间的最高地址;

37.第六自定义系统寄存器,当写地址在所述第四自定义系统寄存器和所述第五自定义系统寄存器区间时,抓取写请求的类型。

38.可选地,读请求类型和写请求类型的寄存器不能够复位。

39.可选地,读请求类型和写请求类型寄存器设置有抓取标志位,所述标志位在每次设置地址寄存器时自动清零,在抓取所要监测的地址时置为1。

40.本发明实施例提供的针对处理器板级调试的开发系统及方法,在处理器设计中加入板级调试辅助设计,为处理器流片后提供高效的调试手段,能够帮助定位处理器内的硬件问题,尤其对于死锁及存储器异常访问有较大帮助。本发明提出的方法易于实现,面积较小,对于处理器的时序收敛及布局布线影响不大。本发明提出的方法能够直接结合芯片的调试器工具,方便调试。

附图说明

41.图1为本发明一实施例针对处理器板级调试的开发系统的结构示意图;

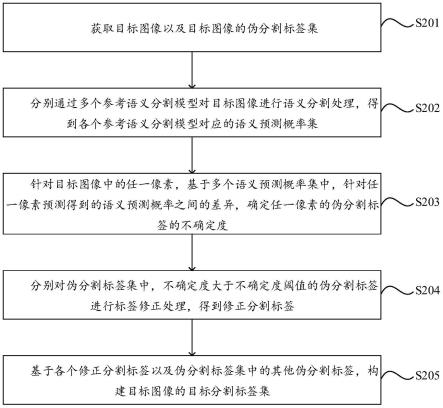

42.图2为本发明另一实施例针对处理器板级调试的开发系统的结构示意图;

43.图3为本发明再一实施例针对处理器板级调试的开发系统的结构示意图。

具体实施方式

44.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

45.本发明实施例提供的针对处理器板级调试的开发系统及方法,包含了几种不同的子方法。下面对这些子方法分别进行阐述。

46.(1)利用architecture debug寄存器的自定义域来监测处理器内部状态

47.armv8-a架构定义了architecture debug的架构框架,其中定义了externaldebug(dbg)寄存器、performance monitor unit(pmu,性能监控单元)寄存器和crosstrigger interface(cti,交叉触发接口)寄存器等。架构上对于这些寄存器的一些域定义为implementation defined(自定义),意味着可以自行定义,可以利用的数量如表1所示(以单处理器核为单位)。

48.表1

49.寄存器数量pmu224x32-bit=7168-bitdbg96x32-bit=3072-bit

cti32x32-bit=1024-bit

50.可以利用这些域监测处理器内部的信号。并且,可以利用现有的debugger tool(调试器工具)直接将处理器内部的状态读出到上位机,结构框图如图1所示。一般情况下,处理器会由多个core(处理器核)和一个l2c(二级缓存控制模块)组成,为了便于阐述,图1中仅包含了一个core和l2c,将core分成ifu(instruction fetch unit,取指单元)、dpu(data processing unit,数据处理单元)、lsu(load/store unit,读写处理单元)和mmu(memory management unit,内存管理单元)四个模块。然后将可以利用的域分别分布到core内模块内和l2c内。

51.dpu模块101,主要负责管理core内指令的执行过程,本身包含了dbg o1dregisters模块102和pmu old registers模块103。在加入辅助调试设计后,又包含了auxiliary debug registers模块104。

52.dbg old registers模块102,是armv8-a架构已定义的dbg相关的寄存器,不包含implementation defined域。

53.pmu old registers模块103,是armv8-a架构已定义的pmu相关的寄存器,不包含implementation defined域。

54.auxiliary debug registers模块104,利用dbg寄存器和pmu寄存器中部分的implementation defined的域,收集dpu模块内对板级调试的重要信号。

55.ifu模块105,负责管理core内指令的取指操作,将dbg相关的寄存器和pmu寄存器中部分的implementation defined域分布其中,收集ifu内对板级调试的重要信号,生成ifu auxiliary debug registers(辅助调试寄存器)。

56.lsu模块106,负责管理core内load/store指令执行过程,将dbg相关的寄存器和pmu寄存器中部分的implementation defined域分布其中,收集lsu内对板级调试的重要信号,生成lsu auxiliary debug registers。

57.mmu模块107,负责管理core内页表转换过程,将dbg相关的寄存器和pmu寄存器中部分的implementation defined域分布其中,收集mmu内对板级调试的重要信号,生成mmuauxiliary debug registers。

58.cti模块108,负责产生debug trigger(触发事件),本身包含了armv8-a架构已定义的cti old registers,但不包含implementation defined域。

59.l2c auxiliary debug registers模块109,是利用cti的implementationdefined域,收集l2c内对板级调试的重要信号。之所以让l2c选择cti的寄存器,原因是cti一般都与l2c在一个power domain(电源域)下。

60.dap模块110,是标准的debug access port(调试接入端口),一方面可以连接debugger tool,另一方面可以通过apb(advanced peripheral bus,高级外设总线)访问debug相关的寄存器。

61.debugger tool模块111,其可为通用的调试工具,比如目前常用的trace-32和ds-5等。

62.进行板级调试的步骤如下所示:

63.首先,配置debugger tool,通过地址选择相关的寄存器。

64.然后,debugger tool将指令传递给dap,通过dap选择相应的32-bit寄存器。

65.最后,将32-bit寄存器的结果通过dap返回给debugger。

66.(2)利用jtag,将处理器内部重要信号导出的方法

67.在core内部集成tap(test access port,测试访问端口)控制器,通过jtag链,将core内重要的信号读出来,结构图如图2所示。

68.jtag control模块301,基于标准的jtag协议,内部实现了状态机、dr寄存器及ir寄存器。dr寄存器用来保存所要导出的信号,ir寄存器用来选择导出哪些信号。

69.ifu、dpu、lsu和mmu组成模块302,分别将其内部重要信号分成以32-bit宽为单位的几组,通过mux输出给jtag链。

70.core内的jtag接口可以与core外的soc上的jtag相连,最终可以将debug信号导出到芯片外。

71.(3)抓取处理器内部speculative memory访问的方法

72.speculative执行是处理器设计中常用的方法,能够显著提升处理器的性能。但是speculative memory访问,有可能会访问到系统上不允许访问的区域,这样会造成不可预知的问题。为了能够快速定位此类问题,可以在处理器内定义一些系统寄存器,可以设定要监测的区域地址范围,和记录访问这段地址空间请求的详细信息。具体在core内的实现访问如图3所示。

73.bus interface unit模块401,是core内与外界进行交互的总线接口模块,在其与外界接口上有读地址、读请求类型、写地址和写请求类型等信号。

74.sys reg0自定义系统寄存器402,设定读地址区间的最低地址。

75.sys reg1自定义系统寄存器403,设定读地址区间的最高地址。

76.sys reg2自定义系统寄存器404,如果读地址在402和403区间,则抓取读请求的类型,如表2所示。此寄存器在捕捉到所监测地址后,只能被更新一次。

77.表2

[0078][0079]

sys reg3自定义系统寄存器405,设定写地址区间的最低地址。

[0080]

sys reg4自定义系统寄存器406,设定写地址区间的最高地址。

[0081]

sys reg5自定义系统寄存器407,如果写地址在405和406区间,则抓取写请求的类型,如表3所示。此寄存器在捕捉到所监测地址后,只能被更新一次。

[0082]

表3

[0083][0084]

自定义的系统寄存器设计需要遵循如下的原则:

[0085]

1、读请求类型和写请求类型的寄存器不能够复位。这样可以在系统hang住时,通过复位处理器来获得读写请求类型。

[0086]

2、请求类型和写请求类型寄存器要设置抓取标志位。此标志位在每次设置地址寄存器时会自动清零,在抓取所要监测的地址时置为1。

[0087]

本发明实施例提供的针对处理器板级调试的开发系统及方法,在处理器设计中加入板级调试辅助设计,为处理器流片后提供高效的调试手段,能够帮助定位处理器内的硬件问题,尤其对于死锁及存储器异常访问有较大帮助。本发明提出的方法易于实现,面积较小,对于处理器的时序收敛及布局布线影响不大。本发明提出的方法能够直接结合芯片的调试器工具,方便调试。

[0088]

本领域普通技术人员可以理解实现上述方法实施例中的全部或部分流程,是可以通过计算机程序来指令相关的硬件来完成,所述的程序可存储于一计算机可读取存储介质中,该程序在执行时,可包括如上述各方法的实施例的流程。其中,所述的存储介质可为磁碟、光盘、只读存储记忆体(read-only memory,rom)或随机存储记忆体(random accessmemory,ram)等。

[0089]

以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应该以权利要求的保护范围为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。